Strain Modulation of Selectively and/or Globally Grown Ge Layers

Abstract

:1. Introduction

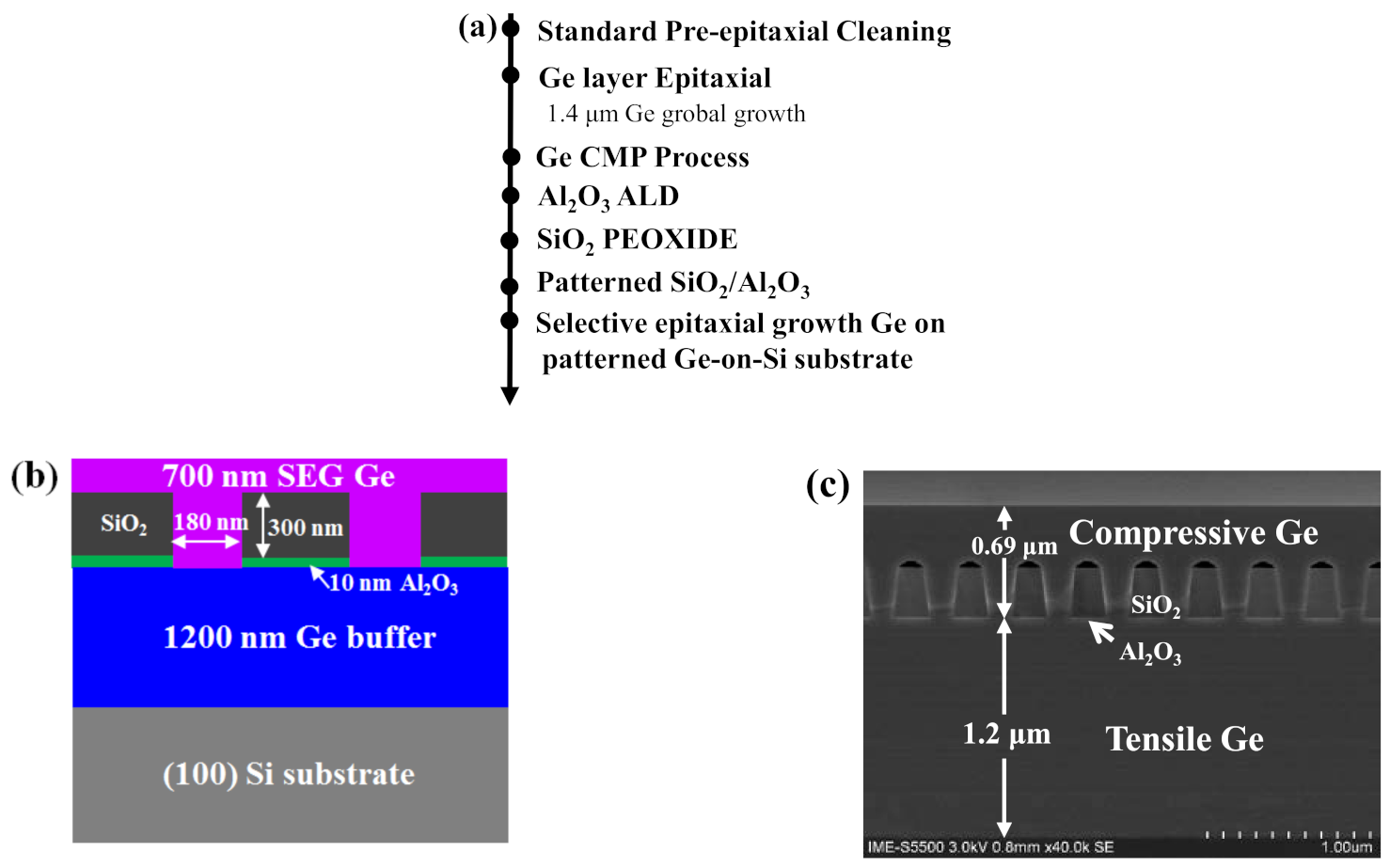

2. Materials and Methods

3. Results and Discussion

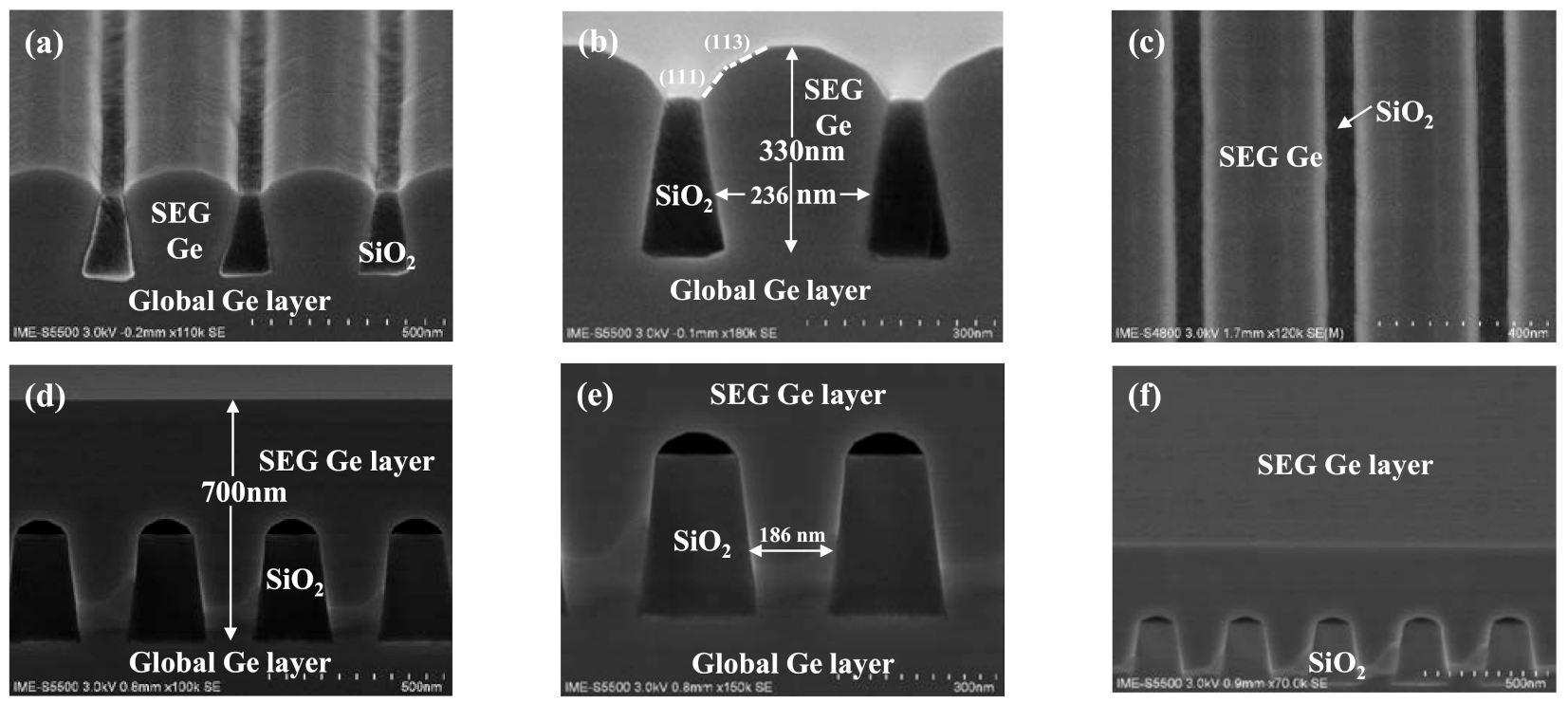

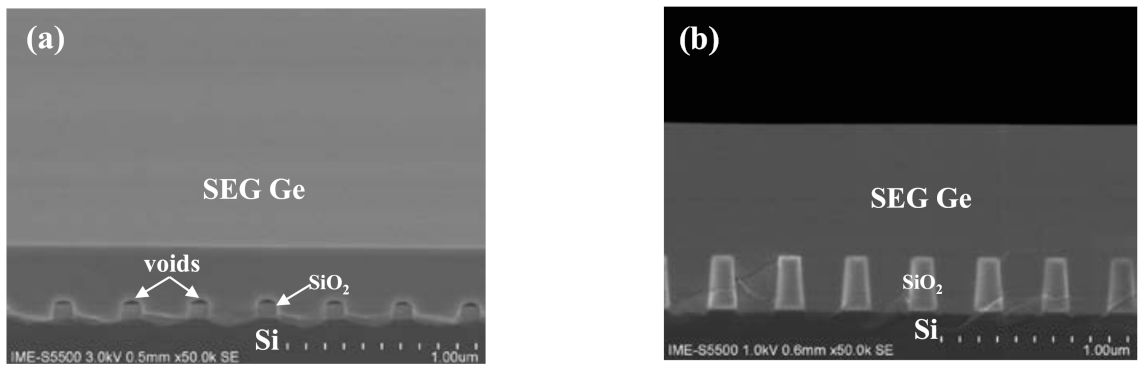

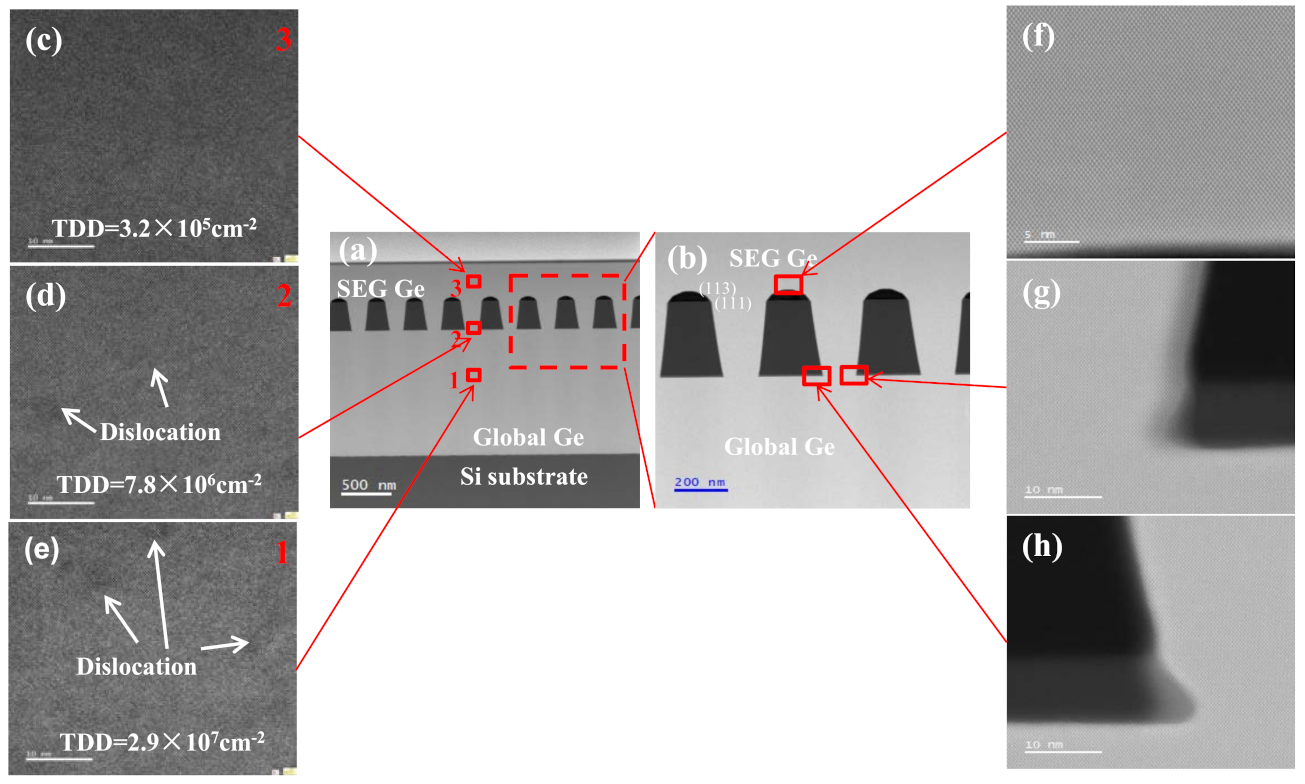

3.1. Growth Mechanism

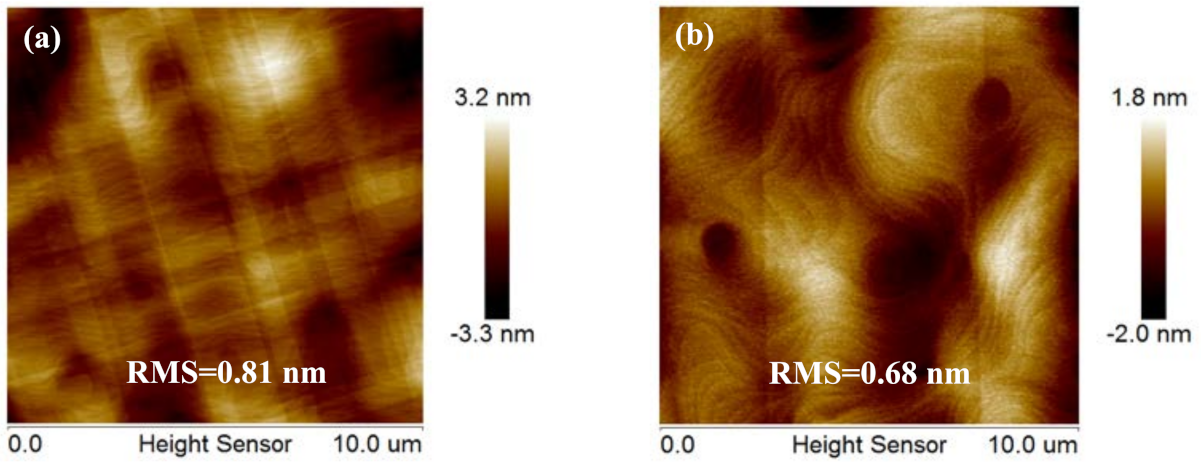

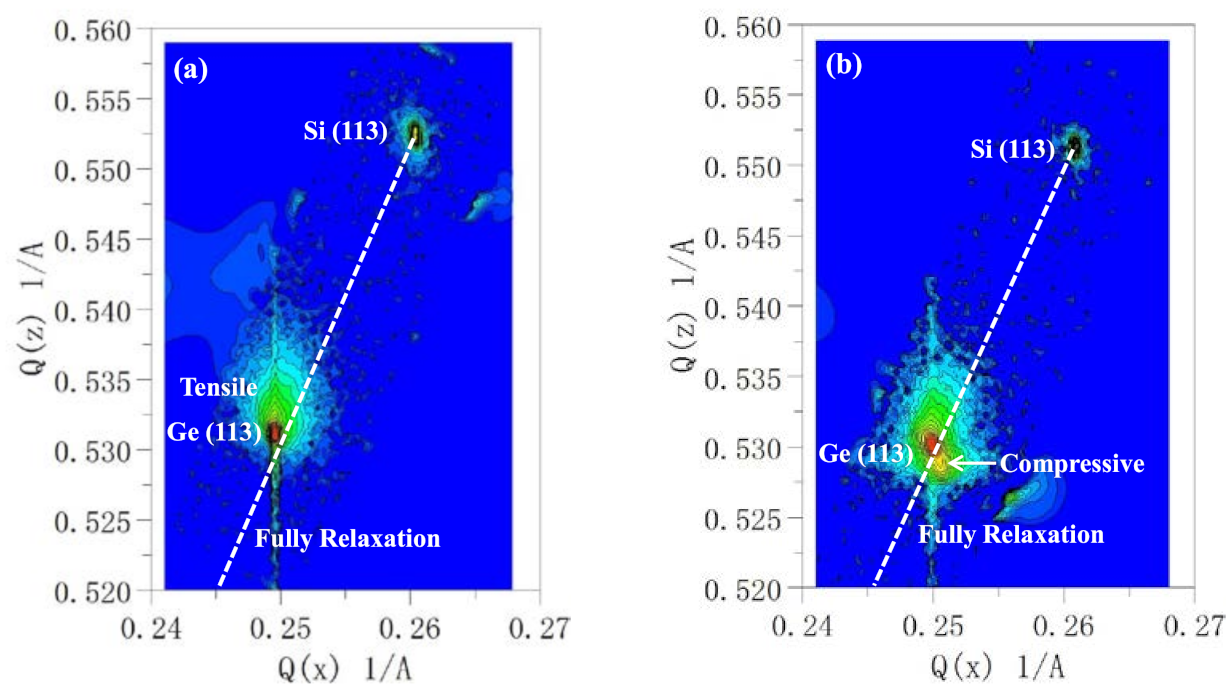

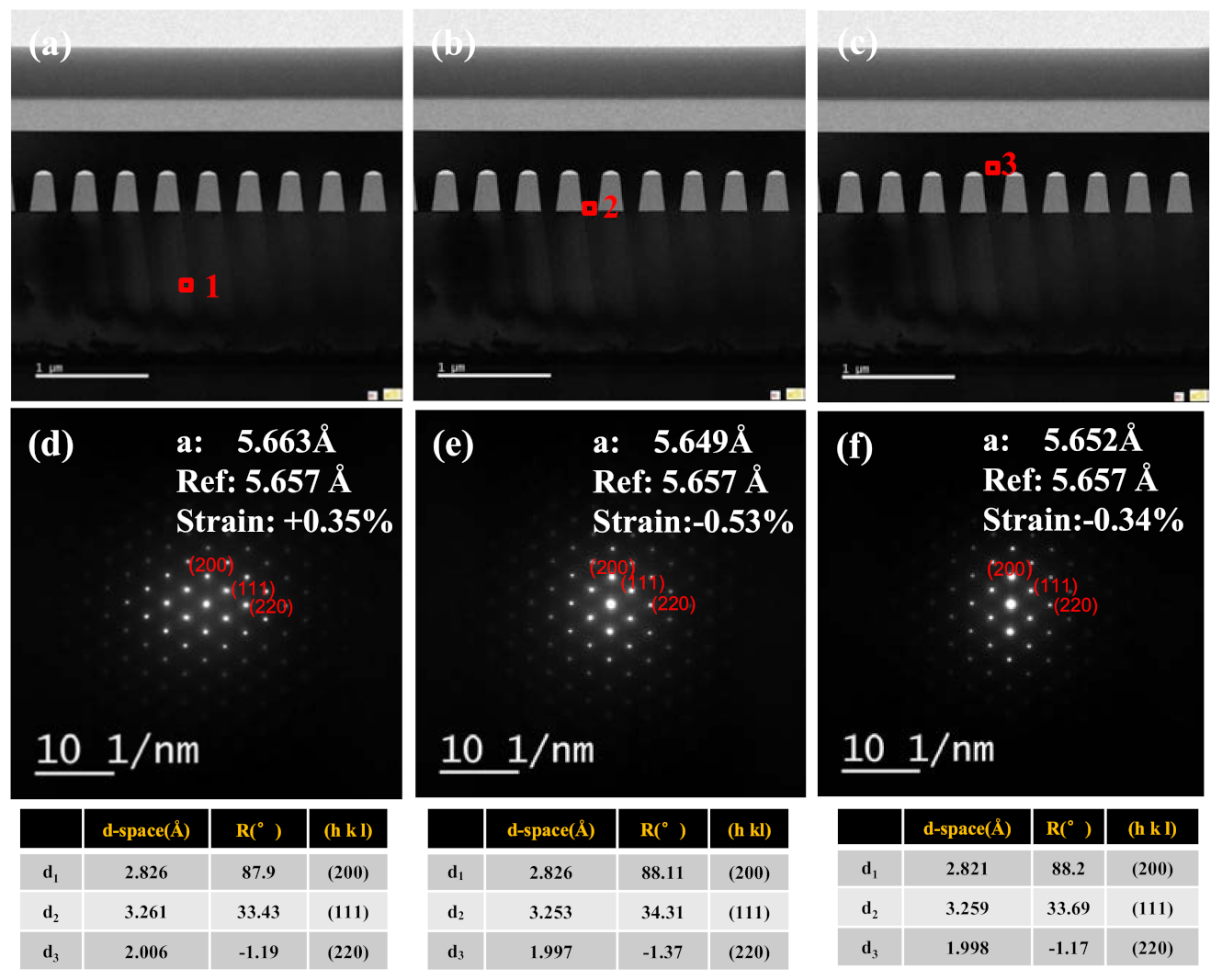

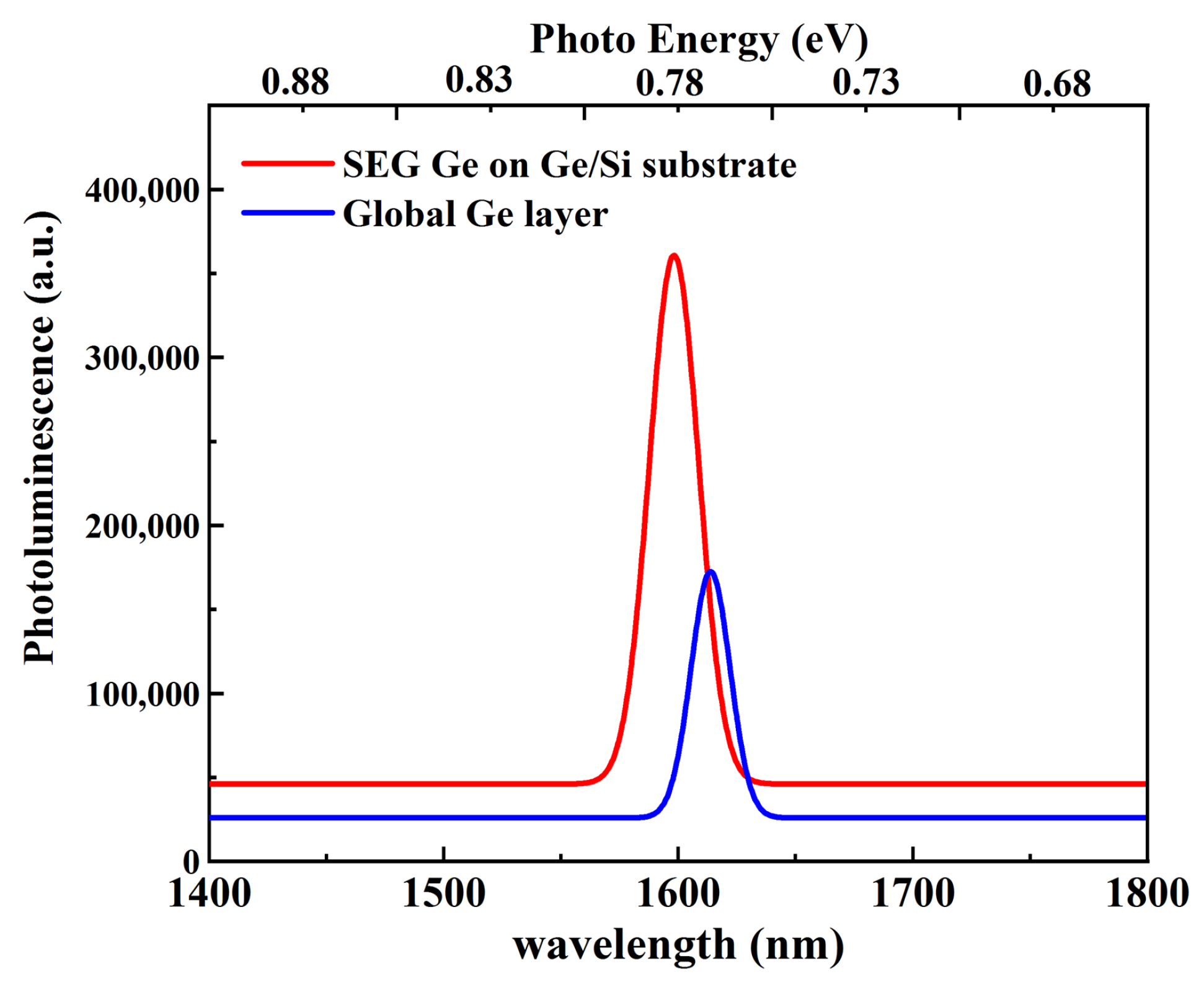

3.2. Strain Characterization

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Radamson, H.H.; Zhu, H.; Wu, Z.; He, X.; Lin, H.; Liu, J.; Xiang, J.; Kong, Z.; Xiong, W.; Li, J.; et al. State of the Art and Future Perspectives in Advanced CMOS Technology. Nanomaterials 2020, 10, 1555. [Google Scholar] [CrossRef] [PubMed]

- Radamson, H.H.; Zhang, Y.; He, X.; Cui, H.; Li, J.; Xiang, J.; Liu, J.; Gu, S.; Wang, G. The Challenges of Advanced CMOS Process from 2D to 3D. Appl. Sci. 2017, 7, 1047. [Google Scholar] [CrossRef]

- Radamson, H. Monolithic Nanoscale Photonics-Electronics Integration in Silicon and Other Group IV Elements; Academic Press: Cambridge, MA, USA; Elsevier BV: Amsterdam, The Netherlands, 2015; ISBN 978-012-419-975-0. [Google Scholar]

- Bao, S.; Kim, D.; Onwukaeme, C.; Gupta, S.; Saraswat, K.; Lee, K.H.; Kim, Y.; Min, D.; Jung, Y.; Qiu, H.; et al. Low-threshold optically pumped lasing in highly strained germanium nanowires. Nat. Commun. 2017, 8, 1–7. [Google Scholar] [CrossRef]

- Elbaz, A.; El Kurdi, M.; Aassime, A.; Sauvage, S.; Checoury, X.; Sagnes, I.; Bœuf, F.; Boucaud, P. Solving thermal issues in tensile-strained Ge microdisks. Opt. Express 2018, 26, 28376–28384. [Google Scholar] [CrossRef] [PubMed]

- Zhao, X.; Moeen, M.; Toprak, M.S.; Wang, G.; Luo, J.; Ke, X.; Li, Z.; Liu, D.; Wang, W.; Zhao, C.; et al. Design impact on the performance of Ge PIN photodetectors. J. Mater. Sci. Mater. Electron. 2019, 31, 18–25. [Google Scholar] [CrossRef]

- Michel, J.; Liu, J.; Kimerling, L.C. High-performance Ge-on-Si photodetectors. Nat. Photon 2010, 4, 527–534. [Google Scholar] [CrossRef]

- Gupta, S.; Srinivasan, S.A.; Pantouvaki, M.; Chen, H.; Verheyen, P.; Lepage, G.; Van Thourhout, D.; Roelkens, G.; Saraswat, K.; Absil, P.; et al. 50 GHz Ge Waveguide Electro-Absorption Modulator Integrated in a 220nm SOI Photonics Platform. In Proceedings of the Optical Fiber Communication Conference Postdeadline Papers; The Optical Society: Washington, DC, USA, 2015; p. Tu2A.4. [Google Scholar]

- Fujikata, J.; Noguchi, M.; Kawashita, K.; Katamawari, R.; Takahashi, S.; Nishimura, M.; Ono, H.; Shimura, D.; Takahashi, H.; Haegashi, H.; et al. High-speed Ge/Si electro-absorption optical modulator in C-band operation-wavelength. Opt. Express 2020, 28, 33123–33134. [Google Scholar] [CrossRef]

- Wang, G. Investigation on SiGe Selective Epitaxy for Source and Drain Engineering in 22 nm CMOS Technology Node and Beyond; Springer Nature: Singapore, 2019; Volume 9. [Google Scholar] [CrossRef]

- Zhou, J.; Wu, J.; Han, G.; Kanyang, R.; Peng, Y.; Li, J.; Wang, H.; Liu, Y.; Zhang, J.; Sun, Q.-Q.; et al. Frequency dependence of performance in Ge negative capacitance PFETs achieving sub-30 mV/decade swing and 110 mV hysteresis at MHz. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 4–6 December 2017; pp. 15.5.1–15.5.4. [Google Scholar] [CrossRef]

- Zhou, J.; Han, G.; Li, J.; Peng, Y.; Liu, Y.; Zhang, J.; Sun, Q.-Q.; Zhang, D.W.; Hao, Y. Comparative Study of Negative Capacitance Ge pFETs With HfZrOxPartially and Fully Covering Gate Region. IEEE Trans. Electron Devices 2017, 64, 4838–4843. [Google Scholar] [CrossRef]

- Brammertz, G.; Caymax, M.; Meuris, M.; Heyns, M.; Mols, Y.; DeGroote, S.; Leys, M. GaAs on Ge for CMOS. Thin Solid Films 2008, 517, 148–151. [Google Scholar] [CrossRef]

- Du, Y.; Xu, B.; Wang, G.; Gu, S.; Li, B.; Kong, Z.; Yu, J.; Bai, G.; Li, J.; Wang, W.; et al. Growth of high-quality epitaxy of GaAs on Si with engineered Ge buffer using MOCVD. J. Mater. Sci. Mater. Electron. 2021, 32, 6425–6437. [Google Scholar] [CrossRef]

- Kohen, D.; Bao, S.; Lee, K.H.; Lee, K.E.K.; Tan, C.S.; Yoon, S.F.; Fitzgerald, E.A. The role of AsH3 partial pressure on anti-phase boundary in GaAs-on-Ge grown by MOCVD—Application to a 200mm GaAs virtual substrate. J. Cryst. Growth 2015, 421, 58–65. [Google Scholar] [CrossRef]

- Loo, R.; Wang, G.; Orzali, T.; Waldron, N.; Merckling, C.; Leys, M.R.; Richard, O.; Bender, H.; Eyben, P.; Vandervorst, W.; et al. Selective Area Growth of InP on On-Axis Si(001) Substrates with Low Antiphase Boundary Formation. J. Electrochem. Soc. 2012, 159, H260–H265. [Google Scholar] [CrossRef]

- Merckling, C.; Waldron, N.; Jiang, S.; Guo, W.; Richard, O.; Douhard, B.; Moussa, A.; Vanhaeren, D.; Bender, H.; Collaert, N.; et al. Selective area growth of InP in shallow trench isolation on large scale Si(001) wafer using defect confinement technique. J. Appl. Phys. 2013, 114, 033708. [Google Scholar] [CrossRef]

- Zhou, Y.; Miao, Y.; Ojo, S.; Tran, H.; Abernathy, G.; Grant, J.M.; Amoah, S.; Salamo, G.; Du, W.; Liu, J.; et al. Electrically injected GeSn lasers on Si operating up to 100 K. Optica 2020, 7, 924. [Google Scholar] [CrossRef]

- Miao, Y.; Wang, Y.; Hu, H.; Liu, X.; Su, H.; Zhang, J.; Yang, J.; Tang, Z.; Wu, X.; Song, J.; et al. Characterization of crystalline GeSn layer on tensile-strained Ge buffer deposited by magnetron sputtering. Mater. Sci. Semicond. Process. 2018, 85, 134–140. [Google Scholar] [CrossRef]

- Radamson, H.H.; Noroozi, M.; Jamshidi, A.; Thompson, P.E.; Östling, M. Strain Engineering in GeSnSi Materials. ECS Trans. 2013, 50, 527–531. [Google Scholar] [CrossRef]

- Zhang, J.; Chen, X.; Wang, J.A.; Chen, G.B.; Tang, Z.H.; Tan, K.Z.; Cui, W. Growth of high quality Ge-on-Si layer by using an ultra-thin LT-Si buffer in RPCVD. IOP Conf. Ser. Mater. Sci. Eng. 2019, 1, 504. [Google Scholar] [CrossRef]

- Chen, D.; Xue, Z.; Wei, X.; Wang, G.; Ye, L.; Zhang, M.; Wang, D.; Liu, S. Ultralow temperature ramping rate of LT to HT for the growth of high quality Ge epilayer on Si (100) by RPCVD. Appl. Surf. Sci. 2014, 299, 1–5. [Google Scholar] [CrossRef]

- Chong, H.; Wang, Z.; Chen, C.; Xu, Z.; Wu, K.; Wu, L.; Xu, B.; Ye, H. Optimization of hetero-epitaxial growth for the threading dislocation density reduction of germanium epilayers. J. Cryst. Growth 2018, 488, 8–15. [Google Scholar] [CrossRef]

- Du, Y.; Kong, Z.; Toprak, M.; Wang, G.; Miao, Y.; Xu, B.; Yu, J.; Li, B.; Lin, H.; Han, J.; et al. Investigation of the Heteroepitaxial Process Optimization of Ge Layers on Si (001) by RPCVD. Nanomaterials 2021, 11, 928. [Google Scholar] [CrossRef] [PubMed]

- Lee, K.H.; Bao, S.; Wang, B.; Wang, C.; Yoon, S.F.; Michel, J.; Fitzgerald, E.A.; Tan, C.S. Reduction of threading dislocation density in Ge/Si using a heavily As-doped Ge seed layer. AIP Adv. 2016, 6, 025028. [Google Scholar] [CrossRef]

- Chen, D.; Wei, X.; Xue, Z.; Bian, J.; Wang, G.; Zhang, M.; Di, Z.; Liu, S. Ultrathin low temperature Si0.75Ge0.25/Si buffer layer for the growth of high quality Ge epilayer on Si (100) by RPCVD. J. Cryst. Growth 2014, 386, 38–42. [Google Scholar] [CrossRef]

- Skibitzki, O.; Zoellner, M.H.; Rovaris, F.; Schubert, M.A.; Yamamoto, Y.; Persichetti, L.; Di Gaspare, L.; De Seta, M.; Gatti, R.; Montalenti, F.; et al. Reduction of threading dislocation density beyond the saturation limit by optimized reverse grading. Phys. Rev. Mater. 2020, 4, 103403. [Google Scholar] [CrossRef]

- Nayfeh, A.; Chui, C.O.; Saraswat, K.C.; Yonehara, T. Effects of hydrogen annealing on heteroepitaxial-Ge layers on Si: Surface roughness and electrical quality. Appl. Phys. Lett. 2004, 85, 2815–2817. [Google Scholar] [CrossRef] [Green Version]

- Hartmann, J.; Abbadie, A.; Barnes, J.; Fédéli, J.; Billon, T.; Vivien, L. Impact of the H2 anneal on the structural and optical properties of thin and thick Ge layers on Si; Low temperature surface passivation of Ge by Si. J. Cryst. Growth 2010, 312, 532–541. [Google Scholar] [CrossRef]

- Liu, Z.; Hao, X.; Ho-Baillie, A.; Tsao, C.-Y.; Green, M.A. Cyclic thermal annealing on Ge/Si(100) epitaxial films grown by magnetron sputtering. Thin Solid Films 2015, 574, 99–102. [Google Scholar] [CrossRef]

- Yu, H.-Y.; Park, J.-H.; Okyay, A.K.; Saraswat, K.C. Selective-Area High-Quality Germanium Growth for Monolithic Integrated Optoelectronics. IEEE Electron Device Lett. 2012, 33, 579–581. [Google Scholar] [CrossRef] [Green Version]

- Radamson, H.H.; Kolahdouz, M. Selective epitaxy growth of Si1−xGex layers for MOSFETs and FinFETs. J. Mater. Sci. Mater. Electron. 2015, 26, 4584–4603. [Google Scholar] [CrossRef]

- Wang, G.L.; Moeen, M.; Abedin, A.; Kolahdouz, M.; Luo, J.; Qin, C.L.; Zhu, H.L.; Yan, J.; Yin, H.Z.; Li, J.F.; et al. Optimization of SiGe selective epitaxy for source/drain engineering in 22 nm node complementary metal-oxide semiconductor (CMOS). J. Appl. Phys. 2013, 114, 123511. [Google Scholar] [CrossRef]

- Sammak, A.; De Boer, W.; Nanver, L.K. Ge-on-Si: Single-Crystal Selective Epitaxial Growth in a CVD Reactor. ECS Trans. 2013, 50, 507–512. [Google Scholar] [CrossRef] [Green Version]

- Yako, M.; Ishikawa, Y.; Abe, E.; Wada, K. Defects and their reduction in Ge selective epitaxy and coalescence layer on Si with semicylindrical voids on SiO2 masks. IEEE J. Sel. Top. Quantum Electron. 2018, 24, 1. [Google Scholar] [CrossRef]

- McMahon, W.E.; Vaisman, M.; Zimmerman, J.D.; Tamboli, A.C.; Warren, E.L. Perspective: Fundamentals of coalescence-related dislocations, applied to selective-area growth and other epitaxial films. APL Mater. 2018, 6, 120903. [Google Scholar] [CrossRef]

- Bharathan, J.; Narayan, J.; Rozgonyi, G.; Bulman, G.E. Defect Characterization in Ge/(001)Si Epitaxial Films Grown by Reduced-Pressure Chemical Vapor Deposition. J. Electron. Mater. 2013, 42, 2888–2896. [Google Scholar] [CrossRef]

- Radamson, H.; Joelsson, K.; Ni, W.-X.; Hultman, L.; Hansson, G. Characterization of highly boron-doped Si, Si1 − xGex and Ge layers by high-resolution transmission electron microscopy. J. Cryst. Growth 1995, 157, 80–84. [Google Scholar] [CrossRef]

- Hansson, G.V.; Radamsson, H.H.; Ni, W.-X. Strain and relaxation in Si-MBE structures studied by reciprocal space mapping using high resolution X-ray diffraction. J. Mater. Sci. Mater. Electron. 1995, 6, 292–297. [Google Scholar] [CrossRef]

| Sample | Strain Calculated by HRXRD | Strain Calculated by TEM | Ge PL Position | Extracted TDD in Ge by TEM (cm−2) |

|---|---|---|---|---|

| Global Ge | +0.25% | +0.35% | 0.768 eV | 2.9 × 107 |

| SEG Ge | +0.25% −0.12% | +0.35% −0.34% | 0.781 eV | 3.2 × 105 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Du, Y.; Wang, G.; Miao, Y.; Xu, B.; Li, B.; Kong, Z.; Yu, J.; Zhao, X.; Lin, H.; Su, J.; et al. Strain Modulation of Selectively and/or Globally Grown Ge Layers. Nanomaterials 2021, 11, 1421. https://doi.org/10.3390/nano11061421

Du Y, Wang G, Miao Y, Xu B, Li B, Kong Z, Yu J, Zhao X, Lin H, Su J, et al. Strain Modulation of Selectively and/or Globally Grown Ge Layers. Nanomaterials. 2021; 11(6):1421. https://doi.org/10.3390/nano11061421

Chicago/Turabian StyleDu, Yong, Guilei Wang, Yuanhao Miao, Buqing Xu, Ben Li, Zhenzhen Kong, Jiahan Yu, Xuewei Zhao, Hongxiao Lin, Jiale Su, and et al. 2021. "Strain Modulation of Selectively and/or Globally Grown Ge Layers" Nanomaterials 11, no. 6: 1421. https://doi.org/10.3390/nano11061421