Selective Overview of 3D Heterogeneity in CMOS

Abstract

:1. Introduction

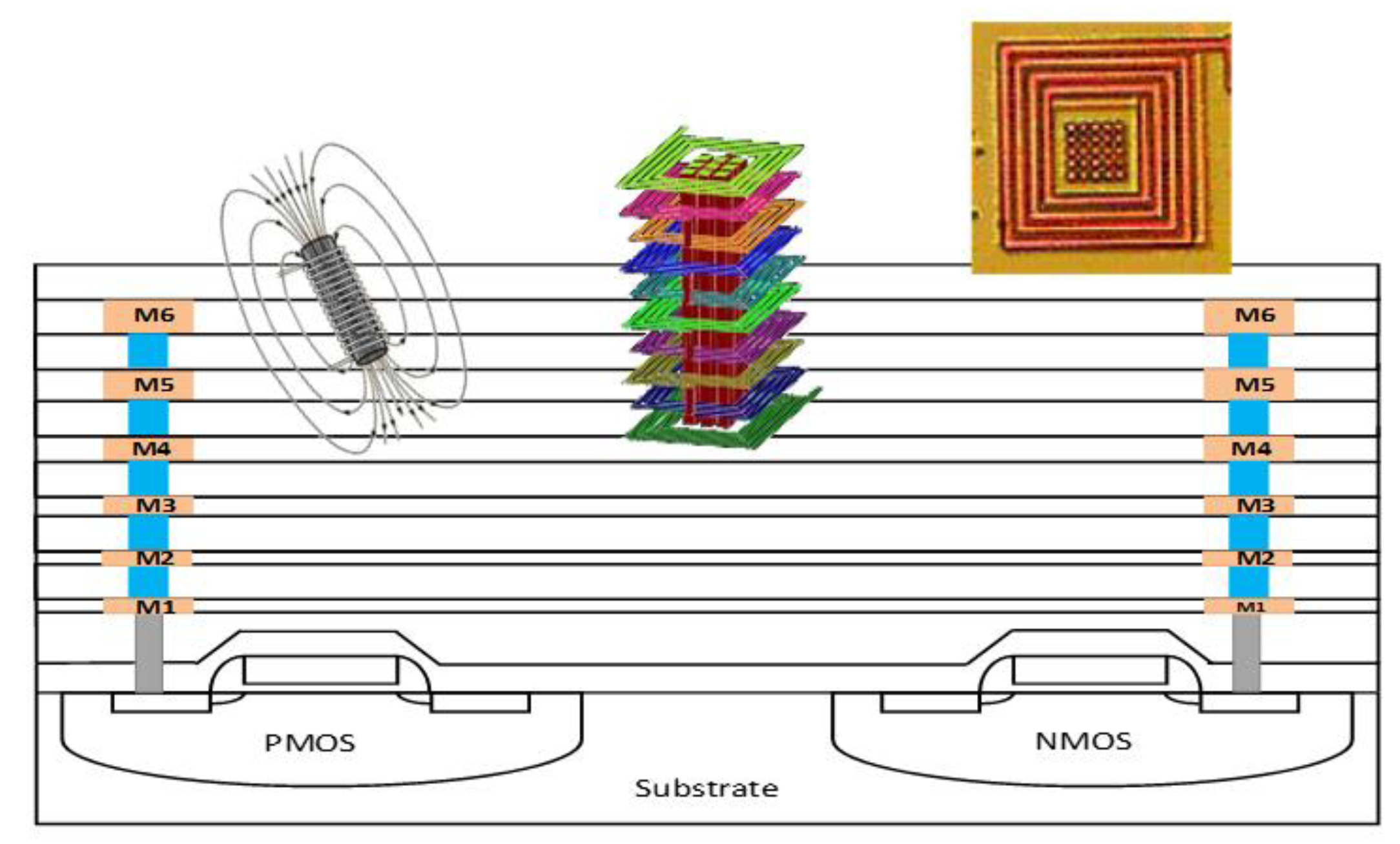

2. Stacked-Via Vertical Magnetic-Cored Inductor

3. In-BEOL Metal Wall Flying Crosstalk Isolation Structure

4. Graphene NEMS ESD-Protection Structure

5. In-BEOL Nano-Crossbar Array ESD-Protection Structure

6. Graphene Interconnects for on-Chip ESD-Protection Circuits

7. Conclusions

Author Contributions

Funding

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Brattain, W.H. Entry of 15 December 1947, Laboratory Notebook, Case 38139-7; Bell Laboratories Archives: Murray Hill, NJ, USA, 1947. [Google Scholar]

- Shockley, W. Circuit Element Utilizing Semiconductor Material. U.S. Patent 2,569,347A, 25 September 1951. (filed 26 June 1948). [Google Scholar]

- Shockley, W. Semiconductor Amplifier. U.S. Patent 2,502,488A, 4 April 1950. [Google Scholar]

- Kilby, J.S. Miniaturized Electronic Circuits. U.S. Patent 3,138,743, 23 June 1964. (filed 6 February 1959). [Google Scholar]

- Noyce, R.N. Semiconductor Device-and-Lead Structure. U.S. Patent 2,981,877A, 25 April 1961. (filed 23 July 1959). [Google Scholar]

- Wanlass, F.M. Low Stand-By Power Complementary Field Effect Circuitry. U.S. Patent 3,356,858, 5 December 1967. [Google Scholar]

- Moore, G.E. Cramming more components onto integrated circuits. Electronics 1965, 38, 114–117. [Google Scholar] [CrossRef]

- HIR—Heterogeneous Integration Roadmap; 2019 Edition; IEEE HIR Committee: Manhattan, NY, USA, 2019.

- IRDS—International Roadmap for Devices and Systems; 2021 Update; IEEE IRDS Committee: Manhattan, NY, USA, 2021.

- ITRS—International Technology Roadmap for Semiconductors; 2015 Edition; SIA ITRS Committee: Manhattan, NY, USA, 2015.

- Jiang, H.; Wang, Y.; Yeh, J.-A.; Tien, N.C. On-Chip Spiral Inductors Suspended over Deep Copper-Lined Cavities. IEEE Trans. Microw. Theory Tech. 2000, 48, 2415–2423. [Google Scholar] [CrossRef] [Green Version]

- Korenivski, V. GHz magnetic film inductors. J. Magn. Magn. Mater. 2000, 215–216, 800–806. [Google Scholar] [CrossRef]

- Wang, A. Compact Inductor with Stacked Via Magnetic Cores for Integrated Circuits. U.S. Patent No. 7,262,680, 28 August 2007. [Google Scholar]

- Long, H.; Feng, Z.; Feng, H.; Wang, A.; Ren, T.; Bao, J.; Liu, F.; Yang, C.; Zhang, X. A New Modeling Technique for Simulating 3D Arbitrary Conductor-Magnet Structures for RFIC Applications. IEEE Tans. Electron. Devices 2005, 52, 1354–1363. [Google Scholar] [CrossRef]

- Yang, C.; Liu, F.; Ren, T.; Liu, L.; Wang, A.Z. On-Chip Integrated Inductors with Ferrite Thin-films for RF IC. In Proceedings of the Tech Digest of the 2006 International Electron Devices Meeting, San Francisco, CA, USA, 11–13 December 2006; pp. 225–228. [Google Scholar]

- Yang, C.; Liu, F.; Ren, T.-L.; Liu, L.-T.; Chen, G.; Guan, X.-K.; Wang, A.; Yue, Z.-X. Ferrite-Partially-Filled on-Chip RF Inductor Fabricated Using Low-Temperature Nano-Powder-Mixed-Photoresist Filling Technique for Standard CMOS. In Proceedings of the Tech Digest of the 2007 IEEE International Electron Devices Meeting, Washington, DC, USA, 10–12 December 2007; pp. 1038–1040. [Google Scholar]

- Yang, C.; Liu, F.; Ren, T.; Liu, L.; Chen, G.; Guan, X.; Wang, A.; Feng, H. Ferrite-Integrated on-Chip Inductors for RF ICs. IEEE Electron. Device Lett. 2007, 28, 652–655. [Google Scholar] [CrossRef]

- Yang, C.; Liu, F.; Wang, X.; Zhan, J.; Wang, A.; Ren, T.-L.; Liu, L.-T.; Long, H.; Wu, Z.; Li, X. Investigation of on-Chip Soft-Ferrite-Integrated Inductors for RF ICs—Part I: Design and Simulation. IEEE Trans. Electron. Devices 2009, 56, 3133–3140. [Google Scholar] [CrossRef]

- Yang, C.; Liu, F.; Wang, X.; Zhan, J.; Wang, A.; Ren, T.-L.; Liu, L.-T.; Long, H.; Wu, Z.; Li, X. Investigation of on-Chip Soft-Ferrite-Integrated Inductors for RF ICs—Part II: Experiments. IEEE Trans. Electron. Devices 2009, 56, 3141–3148. [Google Scholar] [CrossRef]

- Zhan, J.; Wang, X.; Fang, Q.; Shi, Z.; Yang, Y.; Ren, T.-L.; Wang, A.; Cheng, Y.; Li, X.; Yang, C. Stacked-Spiral RF Inductors with Fully-Filled Vertical Nano-Particle Magnetic Core. In Proceedings of the 2012 IEEE Radio Frequency Integrated Circuits Symposium, Montreal, QC, Canada, 17–19 June 2012; pp. 367–370. [Google Scholar]

- Zhan, J.; Yang, C.; Wang, X.; Zhang, F.; Ren, T.L.; Wang, A.; Yang, Y.; Liu, L.T.; Yang, L.W.; Yue, Z.X. Stacked-Spiral RF Inductor with Vertical Nano-Powder-Magnetic-Core in CMOS. IEEE Microw. Wirel. Compon. Lett. 2012, 22, 29–31. [Google Scholar] [CrossRef]

- Ni, Z.; Zhan, J.; Fang, Q.; Wang, X.; Shi, Z.; Yang, Y.; Ren, T.-L.; Wang, A.; Cheng, Y.; Gao, J.; et al. Design and Analysis of Vertical Nanoparticles- Magnetic-Cored Inductors for RF ICs. IEEE Trans. Electron Devices 2013, 60, 1427–1435. [Google Scholar] [CrossRef]

- Cai, H.-L.; Yang, Y.; Qi, N.; Chen, X.; Tian, H.; Song, Z.; Xu, Y.; Zhou, C.-J.; Zhan, J.; Wang, A.; et al. A 2.7-mW 1.36–1.86-GHz LC-VCO with a FOM of 202 dBc/Hz Enabled by a 26%-Size-Reduced Nano-Particle-Magnetic-Enhanced Inductor. IEEE Trans. Microw. Theory Tech. 2014, 62, 1221–1228. [Google Scholar] [CrossRef]

- Ma, R.; Lu, F.; Chen, Q.; Wang, C.; Liu, F.; Zou, W.; Wang, A. A 2.22–2.92 GHz LC-VCO demonstrated with an integrated magnetic-enhanced inductor in 180nm SOI CMOS. In Proceedings of the 2016 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), San Francisco, CA, USA, 22–24 May 2016; pp. 110–113. [Google Scholar] [CrossRef]

- Blalack, T.; Leclercq, Y.; Yue, C.P. On-chip RF isolation techniques. In Proceedings of the Bipolar/BiCMOS Circuits and Technology Meeting, Minneapolis, MN, USA, 1 October 2002; pp. 205–211. [Google Scholar]

- Su, D.K.; Loinaz, M.J.; Masui, S.; Wooley, B.A. Experimental results and modeling techniques for substrate noise in mixed-signal integrated circuits. IEEE J. Solid-State Circuits 1993, 28, 420–430. [Google Scholar] [CrossRef]

- Connell, L.; Hollenbeck, N.; Bushman, M.; McCarthy, D.; Bergstedt, S.; Cieslak, R. A CMOS broadband tuner IC. In Proceedings of the 2002 IEEE International Solid-State Circuits Conference. Digest of Technical Papers (Cat. No.02CH37315), San Francisco, CA, USA, 7 February 2002; pp. 400–476. [Google Scholar]

- Yue, C.P.; Wong, S.S. On-chip spiral inductors with patterned ground shields for Si-based RF ICs. IEEE J. Solid-State Circuits 1998, 33, 420–430. [Google Scholar] [CrossRef]

- Ben Ali, K.; Neve, C.R.; Gharsallah, A.; Raskin, J.-P. Ultrawide Frequency Range Crosstalk Into Standard and Trap-Rich High Resistivity Silicon Substrates. IEEE Trans. Electron Devices 2011, 58, 4258–4264. [Google Scholar] [CrossRef]

- Neve, C.R.; Raskin, J.-P. RF Harmonic Distortion of CPW Lines on HR-Si and Trap-Rich HR-Si Substrates. IEEE Trans. Electron Devices 2012, 59, 924–932. [Google Scholar] [CrossRef]

- Pham, N.; Ng, K.; Bartek, M.; Sarro, P.; Rejaei, B.; Burghartz, J. A micromachining post-process module for RF silicon technology. In Proceedings of the Tech Digest of the International Electron Devices Meeting 2000, San Francisco, CA, USA, 10–13 December 2000; pp. 481–484. [Google Scholar]

- Stefanou, S.; Hamel, J.S.; Baine, P.; Bain, M.; Armstrong, B.; Gamble, H.; Kraft, M.; Kemhadjian, H. Ultralow Silicon Substrate Noise Crosstalk Using Metal Faraday Cages in an SOI Technology. IEEE Trans. Electron Devices 2004, 51, 486–491. [Google Scholar] [CrossRef]

- Lu, F. System on Chip Design Integrated with Visible Light Communication and Multi-Mode Multi-Band Radio-Frequency Front End. Ph.D. Thesis, University of California, Riverside, CA, USA, 2017. [Google Scholar]

- Lu, F.; Chen, Q.; Wang, C.; Zhang, F.; Li, C.; Ma, R.; Wang, X.S.; Wang, A. In-Die Through-BEOL Metal Wall for Noise Isolation in 180-nm FD-SOI CMOS. IEEE Electron Device Lett. 2017, 38, 630–632. [Google Scholar] [CrossRef]

- Wang, C.; Chen, Q.; Lu, F.; Li, C.; Zhang, F.; Wang, A. Blocking Flying Crosstalk in BEOL Validated in Antenna Switches in 45-nm SOI CMOS. IEEE Microw. Wirel. Components Lett. 2018, 28, 1005–1007. [Google Scholar] [CrossRef]

- Wang, A. Practical ESD Protection Design; Wiley-IEEE Press: New York, NY, USA, 2022; ISBN -13 978-1119850403. [Google Scholar]

- Zhan, R.; Feng, H.; Wu, Q.; Xie, H.; Guan, X.; Chen, G.; Wang, A. ESDInspector: A New Layout-Level ESD Protection Circuitry Design Verification Tool Using a Smart-Parametric Checking Mechanism. IEEE Trans. Comput. Des. Integr. Circuits Syst. 2004, 23, 1421–1428. [Google Scholar] [CrossRef]

- Lin, L.; Wang, X.; Tang, H.; Fang, Q.; Zhao, H.; Wang, A.; Zhan, R.; Xie, H.; Gill, C.; Zhao, B.; et al. Whole-Chip ESD Protection Design Verification by CAD. In Proceedings of the 2009 31st EOS/ESD Symposium, Anaheim, CA, USA, 30 August–4 September 2009; pp. 28–37. [Google Scholar]

- Pan, Z.; Li, C.; Hao, W.; Li, X.; Wang, A. ESD Protection Designs: Topical Overview and Perspective. In IEEE Transactions on Device and Materials Reliability; IEEE: Manhattan, NY, USA, 2022. [Google Scholar] [CrossRef]

- Wang, A.; Feng, H.; Zhan, R.; Xie, H.; Chen, G.; Wu, Q.; Guan, X.; Wang, Z.; Zhang, C. A Review on RF ESD Protection Design. IEEE Trans. Electron Devices 2005, 52, 1304–1311. [Google Scholar] [CrossRef]

- Lu, F.; Ma, R.; Dong, Z.; Wang, L.; Zhang, C.; Wang, C.; Chen, Q.; Wang, X.S.; Zhang, F.; Li, C.; et al. A Systematic Study of ESD Protection Co-Design with High-Speed and High-Frequency ICs in 28 nm CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 2016, 63, 1746–1757. [Google Scholar] [CrossRef]

- Wang, X.S.; Lu, F.; Zhang, C.; Dong, Z.; Wang, L.; Ma, R.; Shi, Z.; Wang, A.; Chang, M.-C.F.; Wang, D.; et al. Concurrent Design Analysis of High-Linearity SP10T Switch With 8.5 kV ESD Protection. IEEE J. Solid-State Circuits 2014, 49, 1927–1941. [Google Scholar] [CrossRef]

- Ma, R.; Chen, Q.; Zhang, W.; Lu, F.; Wang, C.; Wang, A.; Xie, Y.-H.; Tang, H. A Dual-Polarity Graphene NEMS Switch ESD Protection Structure. IEEE Electron Device Lett. 2016, 37, 674–676. [Google Scholar] [CrossRef]

- Li, C.; Chen, Q.; Ng, J.; Zhang, F.; Wang, H.; Di, M.; Pan, Z.; Wu, T.; Zhang, K.; Xie, X.; et al. Design, Fabrication and Characterization of Single-Crystalline Graphene gNEMS ESD Switches for Future ICs. IEEE Trans. Device Mater. Reliab. 2021, 21, 331–337. [Google Scholar] [CrossRef]

- Geim, A.K.; Novoselov, K.S. The rise of graphene. Nat. Mater. 2007, 6, 183–191. [Google Scholar] [CrossRef]

- Castro Neto, A.H.; Guinea, F.; Peres, N.M.R.; Novoselov, K.S.; Geim, A.K. The electronic properties of graphene. Rev. Mod. Phys. 2009, 81, 109–162. [Google Scholar] [CrossRef] [Green Version]

- Bunch, J.S.; van der Zande, A.M.; Verbridge, S.S.; Frank, I.W.; Tanenbaum, D.M.; Parpia, J.M.; Craighead, H.G.; McEuen, P.L. Electromechanical Resonators from Graphene Sheets. Science 2007, 315, 490–493. [Google Scholar] [CrossRef] [Green Version]

- Lin, L.; Zhang, L.; Wang, X.; Liu, J.; Zhao, H.; Tang, H.; Fang, Q.; Shi, Z.; Wang, A.; Huang, R.; et al. Novel Nanophase-Switching ESD Protection. IEEE Electron Device Lett. 2011, 32, 378–380. [Google Scholar] [CrossRef]

- Wang, L.; Wang, X.; Shi, Z.; Ma, R.; Liu, J.; Dong, Z.; Zhang, C.; Lin, L.; Zhao, H.; Zhang, L.; et al. Dual-direction nano crossbar array ESD protection structures. IEEE Electron. Device Lett. 2013, 34, 111–113. [Google Scholar] [CrossRef]

- Chen, Q.; Ma, R.; Zhang, W.; Lu, F.; Wang, C.; Liang, Q.; Zhang, F.; Li, C.; Tang, H.; Xie, Y.H.; et al. Systematic characterization of graphene ESD interconnects for on-chip ESD protection. IEEE Trans. Electron. Devices 2016, 63, 3205–3212. [Google Scholar] [CrossRef]

- Chen, Q.; Li, C.; Lu, F.; Wang, C.; Zhang, F.; Wu, T.; Xie, X.; Zhang, K.; Li, X.; Ng, J.; et al. Characterization of single-crystalline graphene ESD interconnects. In Proceedings of the 2017 IEEE 12th International Conference on ASIC (ASICON), Guiyang, China, 25–28 October 2017; pp. 977–980. [Google Scholar]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, C.; Pan, Z.; Li, X.; Hao, W.; Miao, R.; Wang, A. Selective Overview of 3D Heterogeneity in CMOS. Nanomaterials 2022, 12, 2340. https://doi.org/10.3390/nano12142340

Li C, Pan Z, Li X, Hao W, Miao R, Wang A. Selective Overview of 3D Heterogeneity in CMOS. Nanomaterials. 2022; 12(14):2340. https://doi.org/10.3390/nano12142340

Chicago/Turabian StyleLi, Cheng, Zijin Pan, Xunyu Li, Weiquan Hao, Runyu Miao, and Albert Wang. 2022. "Selective Overview of 3D Heterogeneity in CMOS" Nanomaterials 12, no. 14: 2340. https://doi.org/10.3390/nano12142340