Low-Power Complementary Inverter Based on Graphene/Carbon-Nanotube and Graphene/MoS2 Barristors

Abstract

:1. Introduction

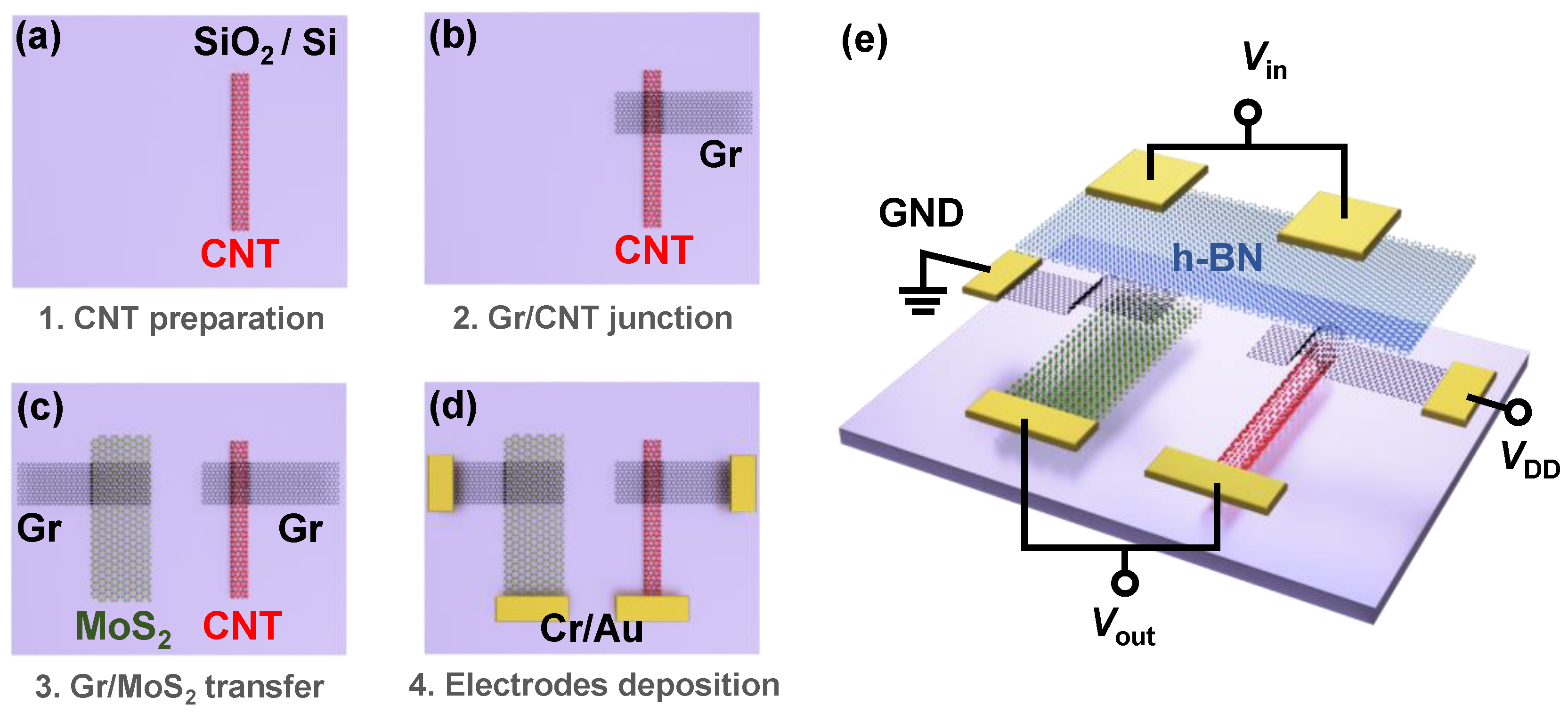

2. Materials and Experimental

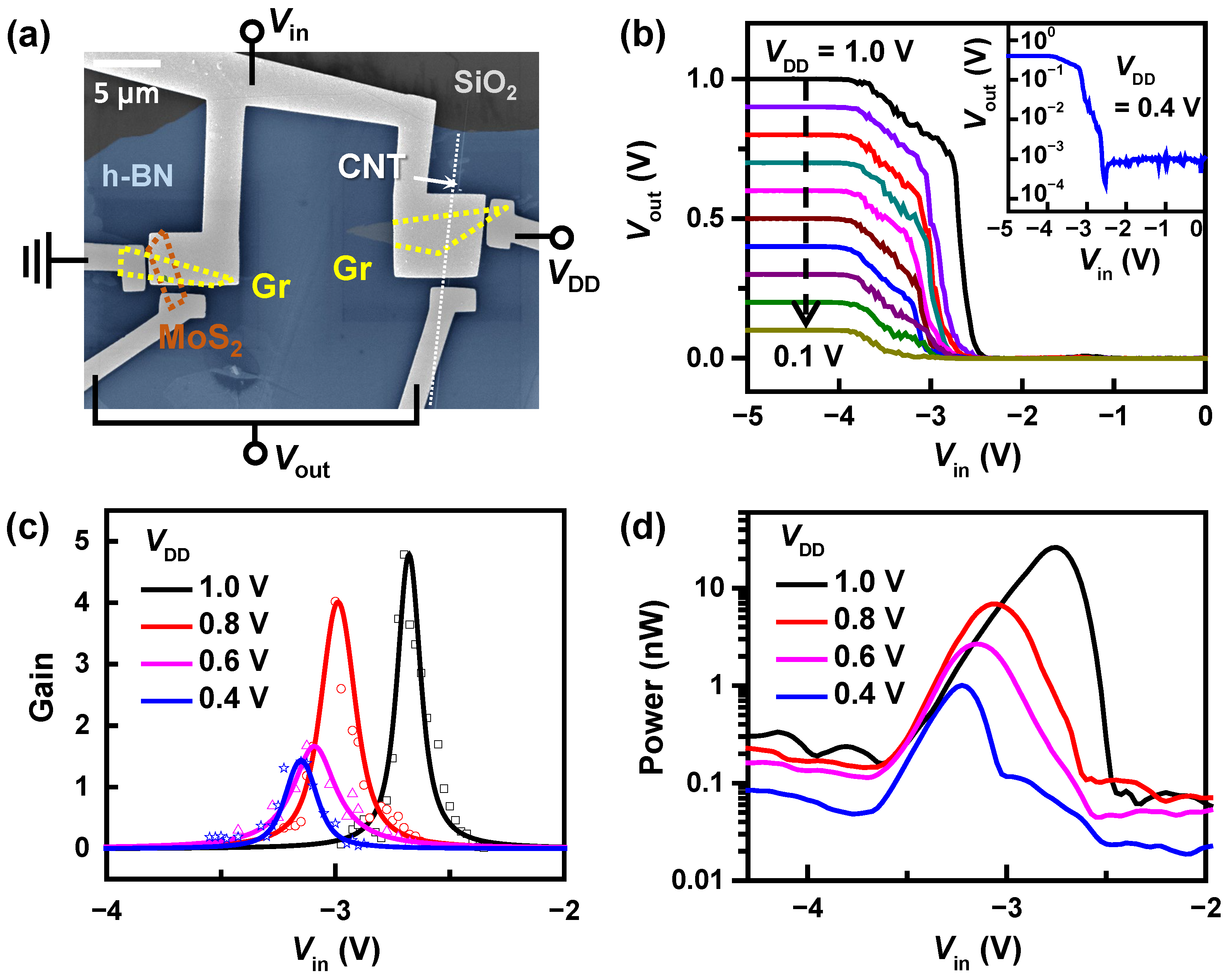

3. Results

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Solomon, P. Device innovation and material challenges at the limits of CMOS technology. Annu. Rev. Mater. Sci. 2000, 30, 681–697. [Google Scholar] [CrossRef]

- Che, Y.; Chen, H.; Gui, H.; Liu, J.; Liu, B.; Zhou, C. Review of carbon nanotube nanoelectronics and macroelectronics. Semicond. Sci. Technol. 2014, 29, 073001. [Google Scholar] [CrossRef]

- Novoselov, K.S.; Colombo, L.; Gellert, P.; Schwab, M.; Kim, K. A roadmap for graphene. Nature 2012, 490, 192–200. [Google Scholar] [CrossRef] [PubMed]

- Manzeli, S.; Ovchinnikov, D.; Pasquier, D.; Yazyev, O.V.; Kis, A. 2D transition metal dichalcogenides. Nat. Rev. Mater. 2017, 2, 17033. [Google Scholar] [CrossRef]

- Zhan, B.; Li, C.; Yang, J.; Jenkins, G.; Huang, W.; Dong, X. Graphene field-effect transistor and its application for electronic sensing. Small 2014, 10, 4042–4065. [Google Scholar] [CrossRef]

- Banszerus, L.; Schmitz, M.; Engels, S.; Dauber, J.; Oellers, M.; Haupt, F.; Watanabe, K.; Taniguchi, T.; Beschoten, B.; Stampfer, C. Ultrahigh-mobility graphene devices from chemical vapor deposition on reusable copper. Sci. Adv. 2015, 1, e1500222. [Google Scholar] [CrossRef] [Green Version]

- Kim, B.J.; Jang, H.; Lee, S.K.; Hong, B.H.; Ahn, J.H.; Cho, J.H. High-performance flexible graphene field effect transistors with ion gel gate dielectrics. Nano Lett. 2010, 10, 3464–3466. [Google Scholar] [CrossRef] [Green Version]

- Yun, J.M.; Park, S.; Hwang, Y.H.; Lee, E.S.; Maiti, U.; Moon, H.; Kim, B.H.; Bae, B.S.; Kim, Y.H.; Kim, S.O. Complementary p-and n-type polymer doping for ambient stable graphene inverter. ACS Nano 2014, 8, 650–656. [Google Scholar] [CrossRef]

- Yang, X.; Li, B. Monolayer MoS2 for nanoscale photonics. Nanophotonics 2020, 9, 1557–1577. [Google Scholar] [CrossRef] [Green Version]

- Ben Amara, I.; Ben Salem, E.; Jaziri, S. Optoelectronic response and excitonic properties of monolayer MoS2. J. Appl. Phys. 2016, 120, 051707. [Google Scholar] [CrossRef]

- Wang, H.; Yu, L.; Lee, Y.H.; Shi, Y.; Hsu, A.; Chin, M.L.; Li, L.J.; Dubey, M.; Kong, J.; Palacios, T. Integrated circuits based on bilayer MoS2 transistors. Nano Lett. 2012, 12, 4674–4680. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Chee, S.S.; Seo, D.; Kim, H.; Jang, H.; Lee, S.; Moon, S.P.; Lee, K.H.; Kim, S.W.; Choi, H.; Ham, M.H. Lowering the Schottky barrier height by graphene/Ag electrodes for high-mobility MoS2 field-effect transistors. Adv. Mater. 2019, 31, 1804422. [Google Scholar] [CrossRef] [PubMed]

- Iqbal, M.W.; Iqbal, M.Z.; Khan, M.F.; Shehzad, M.A.; Seo, Y.; Park, J.H.; Hwang, C.; Eom, J. High-mobility and air-stable single-layer WS2 field-effect transistors sandwiched between chemical vapor deposition-grown hexagonal BN films. Sci. Rep. 2015, 5, 10699. [Google Scholar] [CrossRef] [Green Version]

- Fathipour, S.; Ma, N.; Hwang, W.; Protasenko, V.; Vishwanath, S.; Xing, H.; Xu, H.; Jena, D.; Appenzeller, J.; Seabaugh, A. Exfoliated multilayer MoTe2 field-effect transistors. Appl. Phys. Lett. 2014, 105, 192101. [Google Scholar] [CrossRef] [Green Version]

- Yoo, H.; Hong, S.; On, S.; Ahn, H.; Lee, H.K.; Hong, Y.K.; Kim, S.; Kim, J.J. Chemical doping effects in multilayer MoS2 and its application in complementary inverter. ACS Appl. Mater. Interfaces 2018, 10, 23270–23276. [Google Scholar] [CrossRef]

- Tosun, M.; Chuang, S.; Fang, H.; Sachid, A.B.; Hettick, M.; Lin, Y.; Zeng, Y.; Javey, A. High-gain inverters based on WSe2 complementary field-effect transistors. ACS Nano 2014, 8, 4948–4953. [Google Scholar] [CrossRef] [PubMed]

- Luo, W.; Zhu, M.; Peng, G.; Zheng, X.; Miao, F.; Bai, S.; Zhang, X.A.; Qin, S. Carrier modulation of ambipolar few-layer MoTe2 transistors by MgO surface charge transfer doping. Adv. Funct. Mater. 2018, 28, 1704539. [Google Scholar] [CrossRef]

- He, Q.; Liu, Y.; Tan, C.; Zhai, W.; Nam, G.h.; Zhang, H. Quest for p-type two-dimensional semiconductors. ACS Nano 2019, 13, 12294–12300. [Google Scholar] [CrossRef]

- Yang, H.; Heo, J.; Park, S.; Song, H.J.; Seo, D.H.; Byun, K.E.; Kim, P.; Yoo, I.; Chung, H.J.; Kim, K. Graphene barristor, a triode device with a gate-controlled Schottky barrier. Science 2012, 336, 1140–1143. [Google Scholar] [CrossRef] [Green Version]

- Jahangir, I.; Uddin, M.A.; Singh, A.K.; Koley, G.; Chandrashekhar, M. Richardson constant and electrostatics in transfer-free CVD grown few-layer MoS2/graphene barristor with Schottky barrier modulation >0.6eV. Appl. Phys. Lett. 2017, 111, 142101. [Google Scholar] [CrossRef]

- You, Y.G.; Park, D.H.; Lee, J.H.; Choi, I.; Shin, D.H.; Jo, S.I.; Jeong, G.H.; Campbell, E.E.; Hodge, S.A.; Ferrari, A.C.; et al. p-Type Schottky Junction Devices Based on Graphene and a Semiconducting Carbon Nanotube; Konkuk University: Seoul, Korea, 2022; (Submitted). [Google Scholar]

- Durrer, L.; Helbling, T.; Zenger, C.; Jungen, A.; Stampfer, C.; Hierold, C. SWNT growth by CVD on Ferritin-based iron catalyst nanoparticles towards CNT sensors. Sens. Actuators B Chem. 2008, 132, 485–490. [Google Scholar] [CrossRef]

- Durrer, L.; Greenwald, J.; Helbling, T.; Muoth, M.; Riek, R.; Hierold, C. Narrowing SWNT diameter distribution using size-separated ferritin-based Fe catalysts. Nanotechnology 2009, 20, 355601. [Google Scholar] [CrossRef] [PubMed]

- Jiao, L.; Fan, B.; Xian, X.; Wu, Z.; Zhang, J.; Liu, Z. Creation of nanostructures with poly (methyl methacrylate)-mediated nanotransfer printing. J. Am. Chem. Soc. 2008, 130, 12612–12613. [Google Scholar] [CrossRef] [PubMed]

- Bandow, S.; Asaka, S.; Saito, Y.; Rao, A.M.; Grigorian, L.; Richter, E.; Eklund, P.C. Effect of the growth temperature on the diameter distribution and chirality of single-wall carbon nanotubes. Phys. Rev. Lett. 1998, 80, 3779–3782. [Google Scholar] [CrossRef]

- Park, D.H.; Cho, Y.J.; Lee, J.H.; Choi, I.; Jhang, S.H.; Chung, H.J. The evolution of surface cleanness and electronic properties of graphene field-effect transistors during mechanical cleaning with atomic force microscopy. Nanotechnology 2019, 30, 394003. [Google Scholar] [CrossRef]

- Sinha, D.; Lee, J.U. Ideal graphene/silicon Schottky junction diodes. Nano Lett. 2014, 14, 4660–4664. [Google Scholar] [CrossRef] [Green Version]

- Riel, H.; Wernersson, L.E.; Hong, M.; Del Alamo, J.A. III–V compound semiconductor transistors—From planar to nanowire structures. Mrs Bull. 2014, 39, 668–677. [Google Scholar] [CrossRef] [Green Version]

- Das, T.; Chen, X.; Jang, H.; Oh, I.K.; Kim, H.; Ahn, J.H. Highly flexible hybrid CMOS inverter based on Si nanomembrane and molybdenum disulfide. Small 2016, 12, 5720–5727. [Google Scholar] [CrossRef]

- Du, W.; Jia, X.; Cheng, Z.; Xu, W.; Li, Y.; Dai, L. Low-power-consumption CMOS inverter array based on CVD-grown p-MoTe2 and n-MoS2. Iscience 2021, 24, 103491. [Google Scholar] [CrossRef]

- Heo, S.; Lee, H.I.; Lee, H.; Kim, S.M.; Kim, K.; Kim, Y.J.; Kim, S.Y.; Kim, J.H.; Yoon, M.H.; Lee, B.H. Very-low-temperature integrated complementary graphene-barristor-based inverter for thin-film transistor applications. Ann. Der Phys. 2018, 530, 1800224. [Google Scholar] [CrossRef]

- Liang, S.; Zhang, Z.; Si, J.; Zhong, D.; Peng, L.M. High-performance carbon-nanotube-based complementary field-effect-transistors and integrated circuits with yttrium oxide. Appl. Phys. Lett. 2014, 105, 063101. [Google Scholar] [CrossRef]

- Yeh, C.H.; Liang, Z.Y.; Lin, Y.C.; Chen, H.C.; Fan, T.; Ma, C.H.; Chu, Y.H.; Suenaga, K.; Chiu, P.W. Graphene–transition metal dichalcogenide heterojunctions for scalable and low-power complementary integrated circuits. ACS Nano 2020, 14, 985–992. [Google Scholar] [CrossRef] [PubMed]

- Tian, H.; Tan, Z.; Wu, C.; Wang, X.; Mohammad, M.A.; Xie, D.; Yang, Y.; Wang, J.; Li, L.J.; Xu, J.; et al. Novel field-effect Schottky barrier transistors based on graphene-MoS2 heterojunctions. Sci. Rep. 2014, 4, 5951. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Shim, J.; Park, J.H. Optimization of graphene-MoS2 barristor by 3-aminopropyltriethoxysilane (APTES). Org. Electron. 2016, 33, 172–177. [Google Scholar] [CrossRef]

- Cho, A.J.; Park, K.C.; Kwon, J.Y. A high-performance complementary inverter based on transition metal dichalcogenide field-effect transistors. Nanoscale Res. Lett. 2015, 10, 1–6. [Google Scholar] [CrossRef] [Green Version]

- Yu, W.J.; Li, Z.; Zhou, H.; Chen, Y.; Wang, Y.; Huang, Y.; Duan, X. Vertically stacked multi-heterostructures of layered materials for logic transistors and complementary inverters. Nat. Mater. 2013, 12, 246–252. [Google Scholar] [CrossRef] [Green Version]

- Das, S.; Dubey, M.; Roelofs, A. High gain, low noise, fully complementary logic inverter based on bi-layer WSe2 field effect transistors. Appl. Phys. Lett. 2014, 105, 083511. [Google Scholar] [CrossRef]

- Kim, S.Y.; Hwang, J.; Kim, Y.J.; Hwang, H.J.; Son, M.; Revannath, N.; Ham, M.H.; Cho, K.; Lee, B.H. Threshold voltage modulation of a graphene–ZnO barristor using a polymer doping process. Adv. Electron. Mater. 2019, 5, 1800805. [Google Scholar] [CrossRef]

- Huang, J.; Somu, S.; Busnaina, A. A molybdenum disulfide/carbon nanotube heterogeneous complementary inverter. Nanotechnology 2012, 23, 335203. [Google Scholar] [CrossRef]

- Wang, J.; Guo, X.; Yu, Z.; Ma, Z.; Liu, Y.; Lin, Z.; Chan, M.; Zhu, Y.; Wang, X.; Chai, Y. Low-power complementary inverter with negative capacitance 2D semiconductor transistors. Adv. Funct. Mater. 2020, 30, 2003859. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Shin, D.-H.; You, Y.G.; Jo, S.I.; Jeong, G.-H.; Campbell, E.E.B.; Chung, H.-J.; Jhang, S.H. Low-Power Complementary Inverter Based on Graphene/Carbon-Nanotube and Graphene/MoS2 Barristors. Nanomaterials 2022, 12, 3820. https://doi.org/10.3390/nano12213820

Shin D-H, You YG, Jo SI, Jeong G-H, Campbell EEB, Chung H-J, Jhang SH. Low-Power Complementary Inverter Based on Graphene/Carbon-Nanotube and Graphene/MoS2 Barristors. Nanomaterials. 2022; 12(21):3820. https://doi.org/10.3390/nano12213820

Chicago/Turabian StyleShin, Dong-Ho, Young Gyu You, Sung Il Jo, Goo-Hwan Jeong, Eleanor E. B. Campbell, Hyun-Jong Chung, and Sung Ho Jhang. 2022. "Low-Power Complementary Inverter Based on Graphene/Carbon-Nanotube and Graphene/MoS2 Barristors" Nanomaterials 12, no. 21: 3820. https://doi.org/10.3390/nano12213820

APA StyleShin, D.-H., You, Y. G., Jo, S. I., Jeong, G.-H., Campbell, E. E. B., Chung, H.-J., & Jhang, S. H. (2022). Low-Power Complementary Inverter Based on Graphene/Carbon-Nanotube and Graphene/MoS2 Barristors. Nanomaterials, 12(21), 3820. https://doi.org/10.3390/nano12213820