Investigation on Recrystallization Channel for Vertical C-Shaped-Channel Nanosheet FETs by Laser Annealing

Abstract

:1. Introduction

2. Materials and Methods

3. Results and Discussion

3.1. Key Process Module—Si Cap Deposition and Pre-Clean

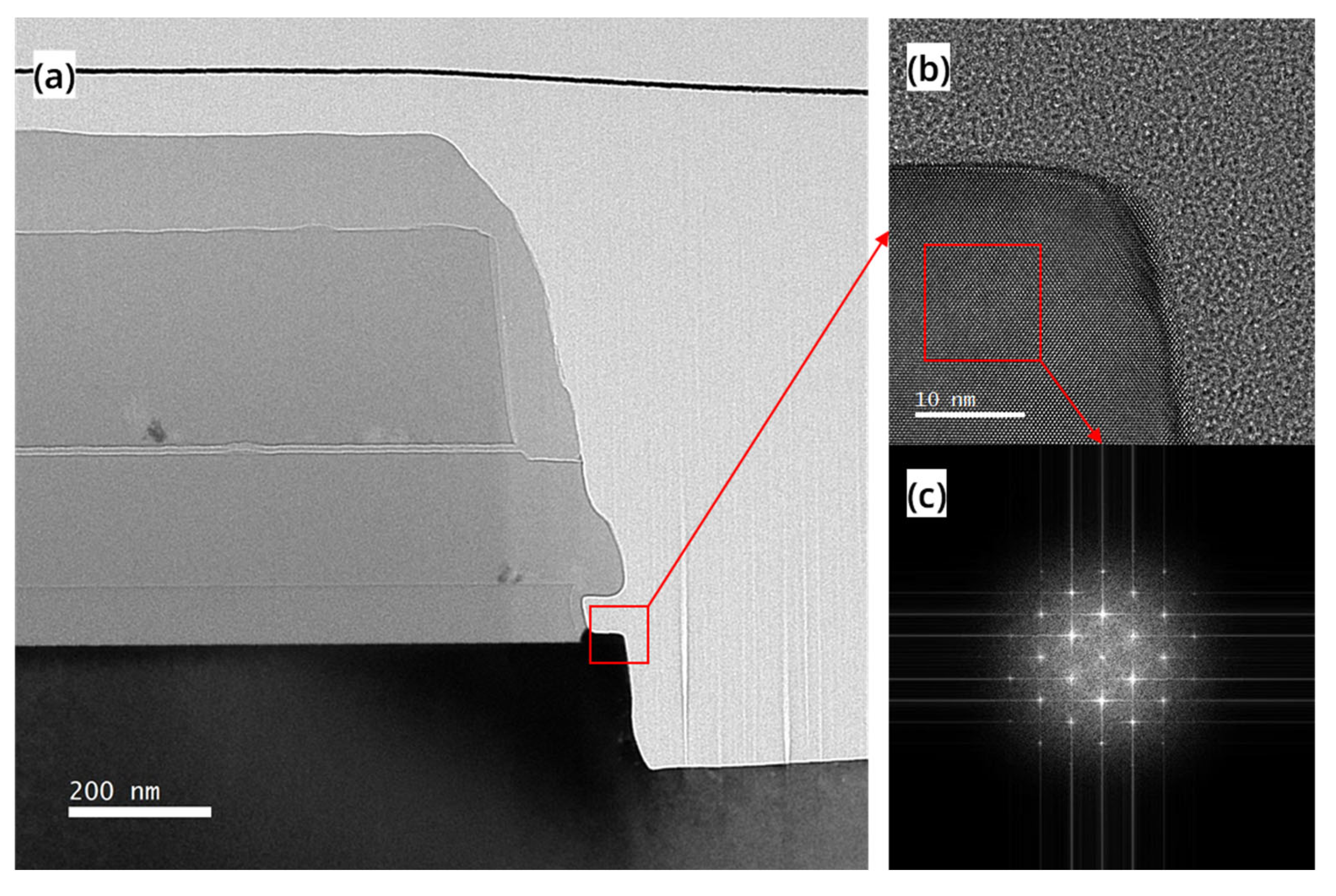

3.2. Structure of RC-Channel

3.3. Characterization and Materials Analysis of the Device

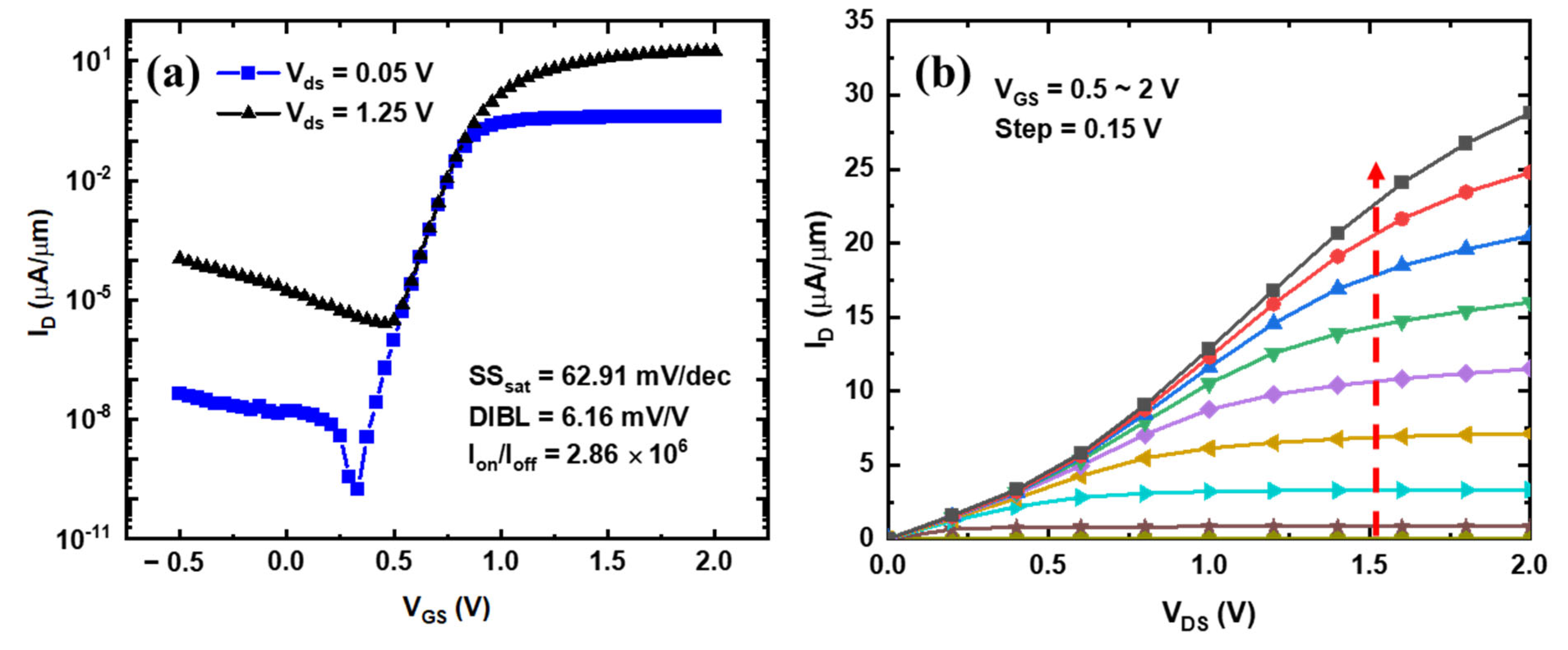

3.4. Electrical Properties of the Device

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Chang, C.-H.; Chang, V.S.; Pan, K.H.; Lai, K.T.; Lu, J.H.; Ng, J.A.; Chen, C.Y.; Wu, B.F.; Lin, C.J.; Liang, C.S. Critical Process Features Enabling Aggressive Contacted Gate Pitch Scaling for 3 nm CMOS Technology and Beyond. In Proceedings of the 2022 International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2022; IEEE: Piscataway, NJ, USA, 2022; pp. 27.1.1–27.1.4. [Google Scholar]

- Lee, S.-Y.; Kim, S.-M.; Yoon, E.-J.; Oh, C.-W.; Chung, I.; Park, D.; Kim, K. A Novel Multibridge-Channel MOSFET (MBCFET): Fabrication Technologies and Characteristics. IEEE Trans. Nanotechnol. 2003, 2, 253–257. [Google Scholar] [CrossRef]

- Bae, G.; Bae, D.-I.; Kang, M.; Hwang, S.M.; Kim, S.S.; Seo, B.; Kwon, T.Y.; Lee, T.J.; Moon, C.; Choi, Y.M. 3nm GAA Technology Featuring Multi-Bridge-Channel FET for Low Power and High Performance Applications. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; IEEE: Piscataway, NJ, USA, 2018. Session 28, No. 7. [Google Scholar]

- Gupta, A.; Pedreira, O.V.; Arutchelvan, G.; Zahedmanesh, H.; Devriendt, K.; Mertens, H.; Tao, Z.; Ritzenthaler, R.; Wang, S.; Radisic, D. Buried Power Rail Integration with FinFETs for Ultimate CMOS Scaling. IEEE Trans. Electron Devices 2020, 67, 5349–5354. [Google Scholar] [CrossRef]

- Gupta, A.; Mertens, H.; Tao, Z.; Demuynck, S.; Bömmels, J.; Arutchelvan, G.; Devriendt, K.; Pedreira, O.V.; Ritzenthaler, R.; Wang, S. Buried Power Rail Integration with Si FinFETs for CMOS Scaling beyond the 5 nm Node. In Proceedings of the 2020 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 16–19 June 2020; IEEE: Piscataway, NJ, USA, 2020; pp. 1–2. [Google Scholar]

- Gupta, A.; Pedreira, O.V.; Tao, Z.; Mertens, H.; Radisic, D.; Jourdan, N.; Devriendt, K.; Heylen, N.; Wang, S.; Chehab, B. Buried Power Rail Scaling and Metal Assessment for the 3 nm Node and Beyond. In Proceedings of the 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 12–18 December 2020; IEEE: Piscataway, NJ, USA, 2020; pp. 20–23. [Google Scholar]

- Prasad, D.; Nibhanupudi, S.T.; Das, S.; Zografos, O.; Chehab, B.; Sarkar, S.; Baert, R.; Robinson, A.; Gupta, A.; Spessot, A. Buried Power Rails and Back-Side Power Grids: Arm® CPU Power Delivery Network Design beyond 5nm. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; IEEE: Piscataway, NJ, USA, 2019. Session 19, No. 1. [Google Scholar]

- Hossen, M.O.; Chava, B.; Van der Plas, G.; Beyne, E.; Bakir, M.S. Power Delivery Network (PDN) Modeling for Backside-PDN Configurations With Buried Power Rails and μTSVs. IEEE Trans. Electron Devices 2019, 67, 11–17. [Google Scholar] [CrossRef]

- Song, K.-W.; Kim, J.-Y.; Yoon, J.-M.; Kim, S.; Kim, H.; Chung, H.-W.; Kim, H.; Kim, K.; Park, H.-W.; Kang, H.C. A 31 Ns Random Cycle VCAT-Based 4F ^{2} DRAM With Manufacturability and Enhanced Cell Efficiency. IEEE J. Solid-State Circuits 2010, 45, 880–888. [Google Scholar] [CrossRef]

- Lee, S.-W.; Kim, S.-Y.; Hwang, K.-M.; Jin, I.K.; Hur, J.; Kim, D.-H.; Son, J.W.; Kim, W.-K.; Choi, Y.-K. A Comprehensive Study of a Single-Transistor Latch in Vertical Pillar-Type FETs with Asymmetric Source and Drain. IEEE Trans. Electron Devices 2018, 65, 5208–5212. [Google Scholar] [CrossRef]

- Cho, Y.; Choi, P.; Hyeon, Y.; Song, J.; Hwang, Y.; Choi, B. Novel Band-to-Band Tunneling Body Contact (BTBC) Structure to Suppress the Floating-Body Effect in a Vertical-Cell DRAM. IEEE Electron Device Lett. 2018, 39, 1860–1863. [Google Scholar] [CrossRef]

- Cho, Y.S.; Choi, P.H.; Kim, K.H.; Park, J.M.; Hwang, Y.S.; Hong, H.S.; Lee, K.P.; Choi, B.D. Stretched Tunnelling Body Contact Structure for Suppressing the FBE in a Vertical Cell DRAM. Electron. Lett. 2019, 55, 1252–1253. [Google Scholar] [CrossRef]

- Cho, Y.; Kim, H.; Jung, K.; Kim, B.; Hwang, Y.; Hong, H.; Choi, B. Suppression of the Floating-Body Effect of Vertical-Cell DRAM with the Buried Body Engineering Method. IEEE Trans. Electron Devices 2018, 65, 3237–3242. [Google Scholar] [CrossRef]

- Schmidt, V.; Riel, H.; Senz, S.; Karg, S.; Riess, W.; Gösele, U. Realization of a Silicon Nanowire Vertical Surround-Gate Field-Effect Transistor. Small 2006, 2, 85–88. [Google Scholar] [CrossRef] [PubMed]

- Goldberger, J.; Hochbaum, A.I.; Fan, R.; Yang, P. Silicon Vertically Integrated Nanowire Field Effect Transistors. Nano Lett. 2006, 6, 973–977. [Google Scholar] [CrossRef]

- Jagannathan, H.; Anderson, B.; Sohn, C.-W.; Tsutsui, G.; Strane, J.; Xie, R.; Fan, S.; Kim, K.I.; Song, S.; Sieg, S. Vertical-Transport Nanosheet Technology for CMOS Scaling beyond Lateral-Transport Devices. In Proceedings of the 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 11–16 December 2021; IEEE: Piscataway, NJ, USA, 2021. Session 26, No. 1. [Google Scholar]

- Tsutsui, G.; Song, S.; Strane, J.; Xie, R.; Qin, L.; Zhang, C.; Schmidt, D.; Fan, S.; Hong, B.; Jung, Y. Hardware Based Performance Assessment of Vertical-Transport Nanosheet Technology; IEEE International Electron Devices Meeting: San Francisco CA, USA, 2022. [Google Scholar]

- Zhang, Y.; Ai, X.; Yin, X.; Zhu, H.; Yang, H.; Wang, G.L.; Li, J.J.; Du, A.Y.; Li, C.; Huang, W.X. Vertical Sandwich GAA FETs with Self-Aligned High-k Metal Gate Made by Quasi Atomic Layer Etching Process. IEEE Trans. Electron Devices 2021, 68, 2604–2610. [Google Scholar] [CrossRef]

- Yin, X.; Zhang, Y.; Zhu, H.; Wang, G.L.; Li, J.J.; Du, A.Y.; Li, C.; Zhao, L.H.; Huang, W.X.; Yang, H. Vertical Sandwich Gate-All-around Field-Effect Transistors with Self-Aligned High-k Metal Gates and Small Effective-Gate-Length Variation. IEEE Electron Device Lett. 2019, 41, 8–11. [Google Scholar] [CrossRef]

- Li, C.; Zhu, H.; Zhang, Y.; Yin, X.; Jia, K.; Li, J.; Wang, G.; Kong, Z.; Du, A.; Yang, T. Selective Digital Etching of Silicon–Germanium Using Nitric and Hydrofluoric Acids. ACS Appl. Mater. Interfaces 2020, 12, 48170–48178. [Google Scholar] [CrossRef] [PubMed]

- Li, C.; Zhu, H.; Zhang, Y.; Wang, Q.; Yin, X.; Li, J.; Wang, G.; Kong, Z.; Ai, X.; Xie, L. First Demonstration of Novel Vertical Gate-All-around Field-Effect-Transistors Featured by Self-Aligned and Replaced High-κ Metal Gates. Nano Lett. 2021, 21, 4730–4737. [Google Scholar] [CrossRef] [PubMed]

- Xiao, Z.R.; Zhu, H.L.; Wang, Q.; Chen, Z.; Liu, Z.Y.; Zhang, Y.K.; Yan, Z.J.; Shi, Y.F.; Zhou, N.; Li, J.J.; et al. Vertical N-Type and P-Type Nanosheet FETs With C-Shaped Channel. IEEE Trans. Electron Devices 2023, 70, 1380–1385. [Google Scholar] [CrossRef]

- Xiao, Z.R.; Wang, Q.; Zhu, H.L.; Chen, Z.; Zhang, Y.K.; Li, J.J.; Zhou, N.; Gao, J.F.; Ai, X.Z.; Lu, S.S.; et al. Vertical C-Shaped-Channel Nanosheet FETs Featured With Precise Control of Both Channel-Thickness and Gate-Length. IEEE Electron Device Lett. 2022, 43, 1183–1186. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, Z.; Zhu, H.; Wang, G.; Wang, Q.; Xiao, Z.; Zhang, Y.; Liu, J.; Lu, S.; Du, Y.; Yu, J.; et al. Investigation on Recrystallization Channel for Vertical C-Shaped-Channel Nanosheet FETs by Laser Annealing. Nanomaterials 2023, 13, 1786. https://doi.org/10.3390/nano13111786

Chen Z, Zhu H, Wang G, Wang Q, Xiao Z, Zhang Y, Liu J, Lu S, Du Y, Yu J, et al. Investigation on Recrystallization Channel for Vertical C-Shaped-Channel Nanosheet FETs by Laser Annealing. Nanomaterials. 2023; 13(11):1786. https://doi.org/10.3390/nano13111786

Chicago/Turabian StyleChen, Zhuo, Huilong Zhu, Guilei Wang, Qi Wang, Zhongrui Xiao, Yongkui Zhang, Jinbiao Liu, Shunshun Lu, Yong Du, Jiahan Yu, and et al. 2023. "Investigation on Recrystallization Channel for Vertical C-Shaped-Channel Nanosheet FETs by Laser Annealing" Nanomaterials 13, no. 11: 1786. https://doi.org/10.3390/nano13111786

APA StyleChen, Z., Zhu, H., Wang, G., Wang, Q., Xiao, Z., Zhang, Y., Liu, J., Lu, S., Du, Y., Yu, J., Xiong, W., Kong, Z., Du, A., Yan, Z., & Zheng, Y. (2023). Investigation on Recrystallization Channel for Vertical C-Shaped-Channel Nanosheet FETs by Laser Annealing. Nanomaterials, 13(11), 1786. https://doi.org/10.3390/nano13111786