1. Introduction

Silicon (Si) has been widely used in electronics due to its abundance, low cost for processing, and versatile properties. However, the electrical properties of intrinsic silicon limit its use and doping has been generally adopted to change the conductivity by the intentional introduction of substitutional impurities into the silicon lattice [

1]. This approach allowed the formation of

pn junctions as part of the design of a variety of electronic devices, such as

npn or

pnp transistors, as well as tunnel diodes or

pn/

pin diodes. As Moore’s law [

2] approaches the end of line, with the critical dimensions of transistors becoming 10 nm or less, the requirements imposed on the

pn junctions, in terms of doping concentration and junction abruptness, become limiting factors in the design and fabrication of nanoscale devices [

3,

4].

Recently, junctionless transistors [

5] have been proposed and demonstrated to overcome the technological challenges imposed by the necessity to control the doping profile in nanoscale. Such junctionless transistors have a relatively simple design, with uniform doping at high concentration across the channel. The high conductance due to the heavy

n-type (or

p-type) doping can be controlled because the channel is a nanowire, and the surrounding gate can deplete such a Si channel [

6]. In state-of-the-art junctionless transistors, full depletion corresponds to the off-state [

7]. In nanoscale transistors doped with lower concentrations, it has been reported that even individual dopants can control the low-temperature transport as quantum dots (QDs), either for donors [

8,

9,

10,

11,

12,

13] or for acceptors [

14,

15]. Under such conditions, doping with one type of dopant has been shown to have an impact on optoelectronics from diverse aspects [

16], including for single-photon detection [

17].

The directions outlined above illustrate the importance of both types of doping (

n-type or

p-type), as well as the relevance of the high doping concentration. So far, however, codoping has been rarely considered as a significant technology for applications in electronics, and then mainly because donors and acceptors facing each other in

pn junctions are expected to induce resonant tunneling current [

18]. Mostly, codoping found applications in the fields of photonics and optoelectronics [

19,

20]. Considering the interactions between donors and acceptors, it can be implied that codoping can be a valuable process to consider for tuning the electrical properties of nanoscale Si. There are different elements that can be used as dopants in Si, such as phosphorus (P), arsenic (As), antimony (Sb), and bismuth (Bi) as donors and, respectively, boron (B), aluminum (Al), gallium (Ga), and indium (In) as acceptors [

21]. It is generally accepted that P and B are technologically suitable as dopants in Si due to their relatively shallow ground-state energy states and controllability of diffusion. In fact, it is well known that, by controlling the concentration and distribution of impurities (P donors and B acceptors), the electrical conductivity and refractive index of Si can be tailored for specific applications [

22]. Codoping Si with P and B dopants has also been shown to enhance the carrier mobility, dramatically modify the recombination rate, and improve the light absorption and emission properties of Si-based devices [

23].

Beyond these effects of codoping on the macroscopic properties of Si, its effect on the microscopic potential landscape in nanoscale devices can be even more dramatic. Due to the inherent randomness of dopant distribution, clusters of donors and/or acceptors can induce local potential wells. These potential wells work as quantum dots (QDs) capturing charges and mediating transport of carriers one by one. A critical effect in such devices is the compensation between donors and acceptors, which may allow the formation of clusters (i.e., QDs) even though doping concentrations of both types of dopants are high [

24].

Here, we provide a perspective on the importance of codoping in promoting single-charge tunneling transport in nanoscale Si devices. This article considers two fundamental devices, diodes and transistors, focusing on devices fabricated in thin silicon-on-insulator (SOI) layers, presenting few results that can be related to codoping. The aim is to open new pathways for implementing codoping as a key technology in future nanoscale devices, enhancing single-charge tunneling features specifically induced by codoping itself.

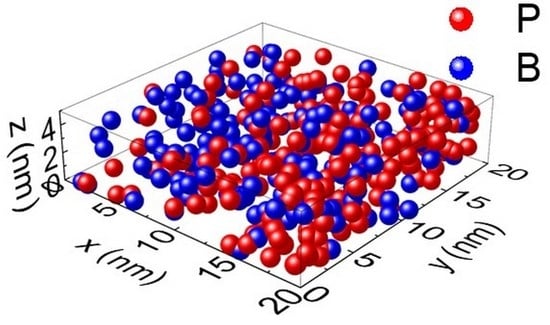

Figure 1 shows an overview of the space defined by the two doping concentrations,

ND and

NA, ranging from 10

17 cm

−3 (corresponding to inter-dopant distances on the order of 20 nm) to more than 10

20 cm

−3 (close to the solid solubility limits, corresponding to inter-dopant distances on the order of 2 nm). Assuming that this space is defined in a thin nanoscale Si layer, one can delineate several regimes that reveal different natures of dopants: (i) “atom” nature, where each individual dopant-atom is practically isolated from the others—at low concentrations, well below the metal-insulator transition (MIT) [

25,

26]; (ii) “molecule” nature, where several dopants can be found coupling to each other into “clusters” (with molecule-like behavior)—at medium concentrations, slightly below or above MIT [

27,

28]; (iii) “domain” nature, where a larger number of dopants dominantly define

n-type or

p-type zones (domains) [

29] due to the uncorrelated distribution of opposite-polarity dopants—at higher concentrations, approaching the solid-solubility limits. The mid-line in this space corresponds to the full (complete) compensation. As one deviates from the mid-line, a quasi-compensated (or partially compensated) regime can be expected [

30,

31,

32]. When the concentrations are strongly imbalanced, Si can be simply treated as

n or

p, with only minor disturbance from the opposite-polarity dopants.

A few results will be provided for different devices with codoped active areas, simply to illustrate the emergence of such natures in single-charge tunneling transport.

2. Fabrication of Codoped Nanoscale-Si Devices

In order to explore the effects of codoping on nanoscale devices, SOI substrates provide the most suitable platform because the top Si layer can be scaled down in all three dimensions. Thinning down, either intentionally by sacrificial oxidation and etching, or as a natural result of device processing, can allow the formation of films in the range of 10 ± 5 nm with relative ease. It should be noted, however, that flatness must be preserved if the effect of dopants must be clearly distinguished from the accidental effect of roughness in the formation of QDs [

33,

34]. Lateral dimensions (width and length) of the active regions can be defined by techniques such as electron beam lithography (EBL), with precision on the order of several tens of nm or less. Similarly to the point made above, line edge roughness (LER) must be controlled to avoid fluctuations that can result in the accidental formation of an undulated potential landscape [

35].

In this work, we will overview results obtained from different types of codoped devices, but the SOI platform and the basic fabrication steps are common to all. Therefore, a typical fabrication flow will be described in the following.

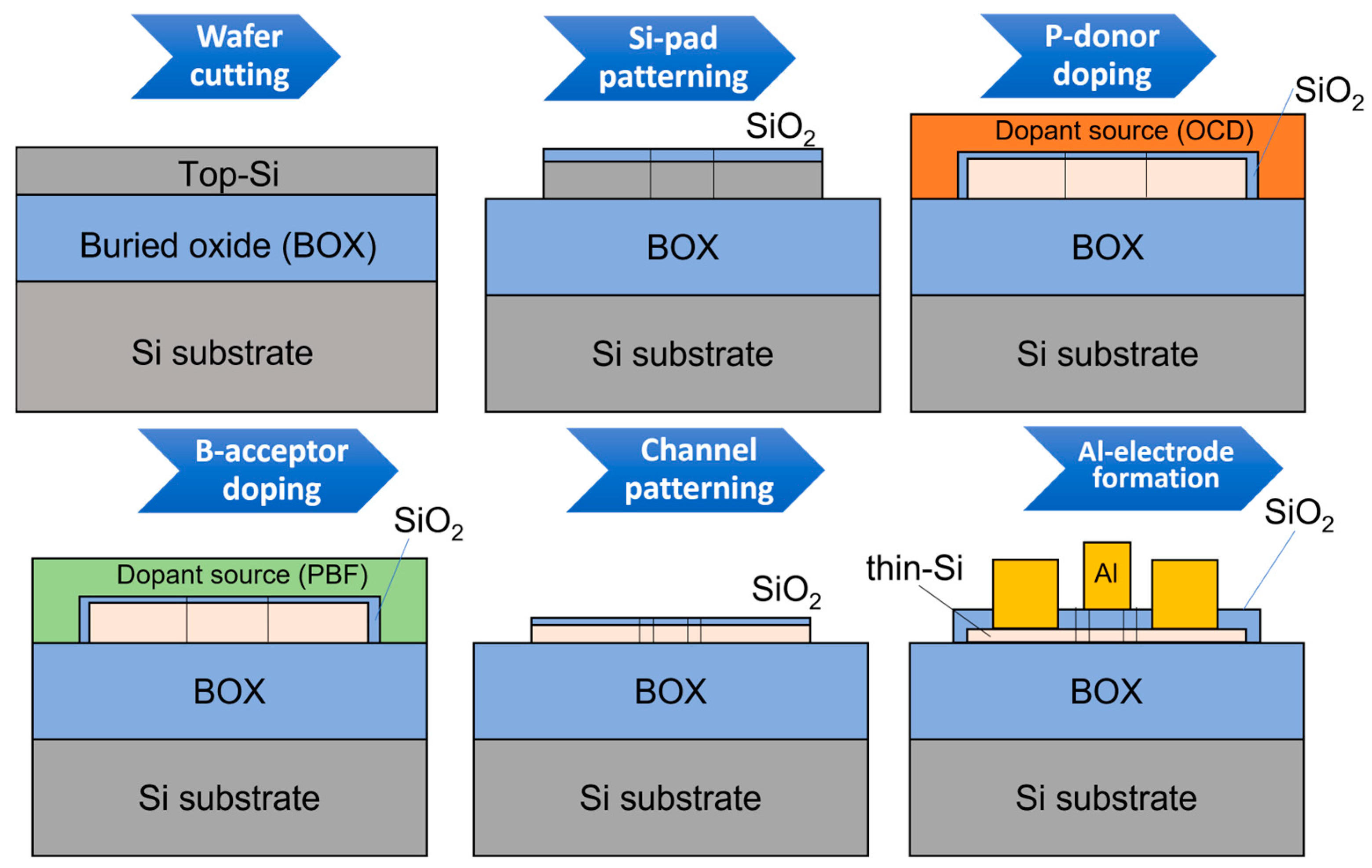

Figure 2 illustrates schematically the main fabrication steps for SOI devices, either SOI lateral

pn (and

pin) diodes or codoped SOI field-effect transistors (SOI-FETs).

As shown in

Figure 2, fabrication starts from SOI layers with thicknesses in the range of 50–70 nm and with a buried oxide (BOX) with thickness in the range of 150–200 nm. The substrate is weakly-doped

p-type Si(100) with a concentration

NA ≈ 1.5 × 10

15 cm

−3. In most cases, the BOX film is sufficiently thick to ensure electrical isolation of the top Si(100) layer from the substrate, so that the transport through the top layer is independent of substrate Si (unless specifically used as a back gate). The SOI layer is thinned down to the target starting thickness by sacrificial oxidation (typically, dry oxidation at 900–950 °C for 10–20 min, resulting in oxide layers of thicknesses on the order of 10 nm), followed by etching in a diluted-HF solution. This process is expected to induce minimum roughness since only a few nm of the Si layer are consumed during every sacrificial-oxidation step. Large Si pads are then defined for making the contacts for metal electrodes. In our recent fabrication approach, it is at this stage that doping processes are introduced because of the ease of observation and the final step is reserved for the fine patterning of the active area of the devices, after doping.

There are two types of doping that are successively done:

n-type (with P-donors from spin-coated solution, OCD59230, containing P

2O

5) and

p-type (with B-acceptors from another spin-coated solution, PBF6M-10, containing B

2O

3). The order in which these doping processes are done can be arbitrary, but it also depends on the amount of thermal budget that dopants will be subjected to. Typically, higher temperatures are required for doping P-donors than for doping B-acceptors at comparable concentrations, which means that carrying out the B-doping first will expose the B-acceptors to a significant thermal budget during the P-doping process. Although this is less important when codoped transistors (basically, junctionless) are formed, this extended diffusion length is detrimental for the formation of abrupt

pn junctions. Therefore, a usual sequence starts with P-doping, followed by B-doping. Before both doping processes, an ultrathin layer of SiO

2 (~1.0 ± 0.5 nm) is thermally grown by dry oxidation at 650 °C for 10 min in order to further protect the SOI surface from direct exposure to the doping source, which may induce unnecessary roughness. In addition, masks are used to protect the regions of SOI that are not supposed to be doped, as follows: (i) a SiO

2 mask of 10–30 nm against P-doping; (ii) a Si

3N

4 mask of 10–20 nm against B-doping. These masks allow the formation of

pn junctions, consistent with conventional processes in very large-scale integration (VLSI) technology [

36].

For both types of doping, a two-step process is used. First, after spin-coating the doping solution onto the SOI surface, protected by the ultrathin SiO2 layer, pre-deposition is carried out at 600 °C for 30 min in N2 atmosphere for P-doping and, respectively, in O2 atmosphere for B-doping. Pre-deposition for B-doping is done in O2 atmosphere in the present samples in order to allow the removal (burning) of the solvent from the spin-coated PBF film, which contains a polymer. Second, drive-in is carried out at temperatures ranging from 800 °C to 1050 °C for various times. Both drive-in time and temperature affect significantly the doping concentration, so they are chosen based on systematic testing. After the completion of the doping process, the surface is cleaned by sequences of H2SO4:H2O2 (4:1) and diluted HF, HF:DIW, deionized water (1:20) solutions. Measurements of thickness are taken with a thickness monitor (FE-3000, Otsuka Electronics) and resistivity is measured at room temperature by a four-point probe technique (K-705RS, Kyowa Riken). These measurements (on reference samples) allow the estimation of the doping concentrations to be within about ±20% of the average value.

It is important to note, at this stage, that the drive-in time must be short enough to ensure abrupt junctions (in the case when pn diodes are fabricated), but also long enough to ensure that dopants diffuse all the way to the bottom of the SOI layer (usually a few tens of nm). A suitable compromise must be achieved by testing, with secondary ion mass spectrometry (SIMS) as a powerful evaluation technique for addressing this issue.

Once codoping is completed, the fabrication flow proceeds to nano-patterning. For that, a thin SiO2 film is grown, and thin resist is spin-coated onto the surface. An EBL exposure with low current and high resolution is used to define the patterns, and reactive ion etching (RIE) is used to etch away the unwanted Si film after careful development of the resist. Since RIE etching preserves the abruptness of the side walls, without introducing large LER (and without directly affecting the top SOI surface), it can be assumed that this step can be sufficiently controlled to maintain roughness within reasonable limits.

The final stages of the fabrication simply aim to passivate the surfaces appropriately, to form the gate oxide, if necessary, and to define the metal electrodes. Gate oxide is also formed by dry oxidation (at least the first few nm), in order to preserve the quality of the Si/SiO2 interface. This step is usually followed by annealing in H2:N2 forming gas for passivating some amount of the dangling bonds present at the interface. Electrodes are defined by a lift-off process, in two steps, first to open the contact holes to make ohmic contacts, and second to deposit Al (typically, with a thickness in the range of 200–300 nm) by vacuum evaporation. The lift-off process is completed by acetone spray.

A simplified device structure is shown in

Figure 3a. Scanning electron microscope (SEM) images of the central region of each device (transistor and diode) are shown in

Figure 3b,c.

Figure 3b shows a

p+n+ diode formed in a 1-µm-long SOI nanowire (with both

ND and

NA on the order of 10

20 cm

−3, but

ND >

NA).

Figure 3c shows a codoped SOI-FET (before gate formation) with a short and narrow channel (

W,

L on the order of ~50 nm). It can be observed from these images that edges and surfaces look smooth enough to assume that roughness does not dramatically affect the electrical characteristics.

Electrical characterization is carried out in a vacuum chamber of a probing system, using semiconductor precision parameter analyzer (typically Keysight, B1500A). Measurements are mostly carried out at low temperatures (T ≈ 8.5 ± 0.5 K), with a noise level on the order of 10~100 fA. In this work, only low-temperature results will be displayed.

4. Discussion and Outlook

In the preceding sections, the fabrication steps of codoped nanoscale SOI devices were presented in parallel for both diodes and transistors. The processes used for the two types of devices are basically the same, except for the need for doping masks when forming pn (and pin) diodes and, respectively, of the addition of a top gate for the case of SOI-FETs. This work suggests that a comparison between the two types of devices, when fabricated using such similar techniques, can allow a deeper understanding of the physics of codoping, observed by quantum tunneling either from single-band transport or band-to-band transport. Most importantly for the purpose expressed in this work, the single-charge tunneling mechanism can be evaluated (in particular at low temperature) in nanoscale depletion layers of p+n+ diodes or nanoscale channels of transistors.

The data shown in

Figure 4, for a

p+n+ diode, are an example of a device that works basically as an Esaki (tunnel) diode, exhibiting NDC (and excess current features) in the forward-bias region, as well as high BTBT current in the reverse-bias region. These are telltale signatures of the Esaki diodes [

45,

46]. It has also been reported that the phonon-assisted BTBT is preserved even in nanowire Esaki diodes [

47]. In our previous work on

p+n+ diodes of comparable dimensions to the ones presented here, we reported that, despite the fact that quantum confinement in the thin SOI layers starts to be observed as discrete energy states, phonons are still contributing significantly to BTBT transport [

39,

40]. These results suggest that Si preserves its indirect-bandgap nature in such dimensions (still larger than 10 nm), while effects of dielectric and quantum confinement on the band nature and dopant states would be expected in much smaller scales (<10 nm) [

48]. Despite this typical behavior, applying

Vsub as a back gate opens a (low-current) gap at low biases, as shown in

Figure 5 and, more clearly, in the stability diagram plotted in

Figure 6. Two main reasons can be considered for such a gap.

First, this can be due to an increase in the resistance of the top-Si film since

Vsub is a macroscopic gate, affecting a wider area in the top-Si layer, not only the depletion layer. At least, it is reasonable to assume that different polarities of

Vsub can induce the accumulation or the depletion of electrons or holes in different parts of the diode. The region that is most likely to be affected by

Vsub is the codoped (overlap) region, which is located to the right of the

pn junction itself, since this region must be thinner and narrower due to the double-doping process. In addition, the effective doping concentration is also lower (if assumed to be |

ND −

NA|) as compared to the non-overlapped parts of the leads. Since this region is effectively

n-type (

ND >

NA for this case), negative

Vsub would induce the depletion of electrons, thus increasing the resistance. This may reasonably explain the sudden change occurring at large negative

Vsub, although the change is rather systematic (linear) up to that point (see

Figure 5a]. For positive

Vsub, electrons are accumulated in this region, making it less resistive and, thus, allowing higher currents to flow. Although this is generally consistent with the observation in

Figure 6, this model cannot explain the diamond-shaped regions clearly noticeable in the positive-

Vsub regime (see

Figure 5b and

Figure 6).

Therefore, a second and more likely explanation for the peculiar evolution of the low-bias gap is the phenomenon of Coulomb blockade, which assumes that one (or just a few) QDs significantly control BTBT transport at such low biases [

40]. As assumed in our previous works, it is more likely that clusters of P-donors (“molecule”-like structures or even nanoscale “domains”) are formed near the

n-type edge of the depletion layer. This is due to the fact that

ND is higher than

NA, thus favoring such

n-type cluster formation. Assuming this model, the

Vsub effect can be explained as follows. At negative

Vsub, the donor-cluster working as a QD is empty (no electrons are trapped into it), which is consistent with the general situation in a depletion layer (no captured carriers, in principle). As

Vsub is increased in the negative direction, the gap broadens rapidly because larger and larger

Vp would be needed to realign the QD’s ground state into the BTBT transport window to allow the current to start again. At positive

Vsub, however, electrons can be added one by one into the QD(s) and BTBT transport becomes dominated by Coulomb blockade. The observation of only two Coulomb diamonds (and even these with some sub-structure) is reasonable considering the large electric field present across the depletion layer; such a condition may only allow the addition of two electrons before the tunnel barrier becomes negligible. The critical tunnel barrier is likely on the side towards the

n-lead.

In reality, there may be contributions from both models described above. However, Coulomb blockade and single-charge tunneling remain the only phenomena that can reasonably explain the diamond-shaped regions. To fully clarify the impact of the design parameters, in particular the role of codoping, in defining the QDs that allow SET transport, further study is necessary by gradually changing the device dimensions, doping concentrations, lengths of the overlapped region, and temperature. This remains as a future study.

The codoped SOI-FETs (practically designed as codoped junctionless transistors) are a more straightforward case of study because transport does not involve both conduction and valence bands. As such, the indirect-bandgap nature of Si does not have to be specifically considered in the interpretation of transport. However, it should be noted that the distributions of P-donors and B-acceptors are most likely not correlated to each other, meaning that there could be preferential positions for opposite-polarity dopants (near interfaces or, respectively, within the nanowires), which would allow the formation of

n-type paths and

p-type paths within the same channel. To elucidate such a possibility, further study is needed, involving tuning of the vertical electric field (e.g., using both

Vsub and

VG in an appropriate configuration) [

49]. This study also remains to be reported later.

Here, we focus on the electrical characteristics presented in

Figure 7, in comparison with a Coulomb-blockade simulation result, and on the stability diagram shown in

Figure 8. These results illustrate that nanoscale codoped SOI-FETs can contain in their channels one (or just a few) QD(s) that provide a platform for the observation of SET transport. There are also several possibilities to explain the occurrence of the QDs in such channels.

First, one can expect that high doping with both P-donors and B-acceptors, combined with the patterning-induced fine roughness (surface roughness and/or line edge roughness) of the nanoscale-channel can create potential undulations within the channel. Such potential undulations have been reported to work as QDs when the surface was intentionally roughened by chemical processing [

33,

34] or unintentional lack of control. Some degree of roughness was observed indeed in several devices from this batch, but mostly in the devices with longer channels, in which unavoidable process fluctuations can introduce some modulation of the nanowire thickness and/or width. However, the devices presented here have very short channels (nominally designed as point contacts), which drastically minimizes the impact of such roughness. Furthermore, the patterning and doping processes were carried out with specific care to protect the top surface and side walls of the nanostructures, as described earlier.

Therefore, a more reasonable explanation for the formation of the QDs is the random distribution of dopants within the Si nanoscale channel. In our previous work [

41], we illustrated statistically that even highly-doped channels may contain isolated QDs (i.e., with the “metallic” conduction paths cut off) due to the combined effect of the randomness of the dopant distribution and nanoscale dimensionality of the channel. In that case, P-donors were the only dopants introduced in the channel, at a concentration comparable to the one used in the codoped SOI-FETs. Considering that, in these codoped SOI-FETs, a significant fraction of the P-donors is effectively compensated by the B-acceptors (here, introduced in a ratio of roughly 1:3~1:4), the probability of finding isolated QDs in the codoped channels is enhanced. This can explain the larger yield of SET devices observed in the codoped-transistor batch.

Returning to the analysis of the periods between consecutive current peaks (ascribed to two different QDs, as described earlier in

Figure 7), one can evaluate the gate capacitances

CG and then the area of the QDs as seen from the gate. Assuming a simple parallel-plate model, with

CG = ε

0ε

oxA/

tox (ε

0—vacuum permittivity; ε

ox = 3.9—relative permittivity of SiO

2;

A—area of the QD;

tox = 10 nm—gate oxide thickness), the areas of the two QDs are estimated to be approximately 700 nm

2 (for the smaller QD) and 1300 nm

2 (for the larger QD). The values are acceptable to fit into the nanoscale channel, estimated from the SEM image (as shown in

Figure 3c) to have dimensions of roughly

L ≈ 100 ± 20 nm and

W ≈ 30 ± 10 nm.

Full elucidation of the role of the counter-dopants (here, B-acceptors) in the formation of the QDs cannot be expected only from electrical characterization. Techniques that can map the surface potential of the codoped nanoscale channels, such as Kelvin probe force microscopy (KPFM) [

50,

51], are promising for revealing the domain formation in such channels, providing further insights into the interplay between donors and acceptors under different biasing. Further exploration of this interplay in codoped transistors can be done by changing systematically the channel dimensions (not only width and length, but also thickness), doping concentrations, processing conditions, and, eventually, by introducing selective nanoscale doping to enhance the controllability of the QD formation. This work aims to trigger more interest in these directions of research in the future.

The experimental results presented in this work provide examples of what phenomena can be revealed in codoped devices, illustrating the potential of codoped thin (and ultrathin) layers of Si (here, SOI) as a platform for observation and analysis of single-charge tunneling functionalities. It is worth noting that the study can be scaled down to the fundamental analysis of the interplay between one P-donor and one B-acceptor (or just a few atoms of each type) by first-principles simulations. Such analyses have been carried out extensively for Si nanocrystals [

52,

53,

54] mainly with the aim of demonstrating their applicability to enhancing photoluminescence (PL). Only recently, studies have started to explore the effects of different configurations of counter-dopants in nanowire transistors [

55]. It is expected that research at such fundamental level can reveal exciting new physics arising from the atomic-level counterparts of the nanoscopic devices presented here, diodes and transistors.

5. Conclusions

In summary, this work provided a brief overview of the fabrication and low-temperature operation of codoped silicon nanodevices (doped with both P-donors and B-acceptors), with a few experimental results demonstrating the potential for single-electron (single-charge) tunneling functionalities. The low-dimensional devices can be formed using CMOS-compatible techniques in silicon-on-insulator (SOI) films, with comparable processes for the formation of SOI diodes and SOI transistors. Codoping plays a key role either in the depletion layer (in the case of diodes) or in the nanoscale (point-contact-design) channel (in the case of transistors).

SOI pn diodes with high doping can behave, basically, as Esaki diodes at low temperature, but they are also sensitive to the substrate voltage. The dependence on Vsub reveals in some devices the opening of Coulomb diamonds, which suggests that single-charge tunneling may occur in such devices. Codoped SOI transistors are designed practically as junctionless transistors, but their low-temperature characteristics clearly exhibit single-electron tunneling features (current peaks and Coulomb diamonds in the stability diagram). The interpretation is straightforward based on the orthodox theory of Coulomb blockade, suggesting that such codoped channels are promising platforms to observe and analyze single-electron tunneling functionalities based on dopants.

Further developments in the ability to engineer the electronic properties of codoped silicon at the nanoscale will open new opportunities for studying in more depth quantum phenomena, such as single-electron tunneling. It is important to note that, while this article provides a glimpse into the capabilities of codoped silicon nanodevices, further systematic studies are required to fully understand and harness their potential. Future research efforts should focus on exploring the underlying mechanisms of single-electron tunneling in codoped silicon, as well as on optimizing device fabrication techniques for improving device yield.

In conclusion, the experimental results presented here highlight the exciting possibilities that codoped silicon nanodevices hold for fundamental physics exploration. Continued research in this field will contribute to the advancement of nanoelectronics and pave the way for donor-acceptor-based functionalities and novel device architectures.