Graphene Oxide-Based Memristive Logic-in-Memory Circuit Enabling Normally-Off Computing

Abstract

:1. Introduction

2. Materials and Methods

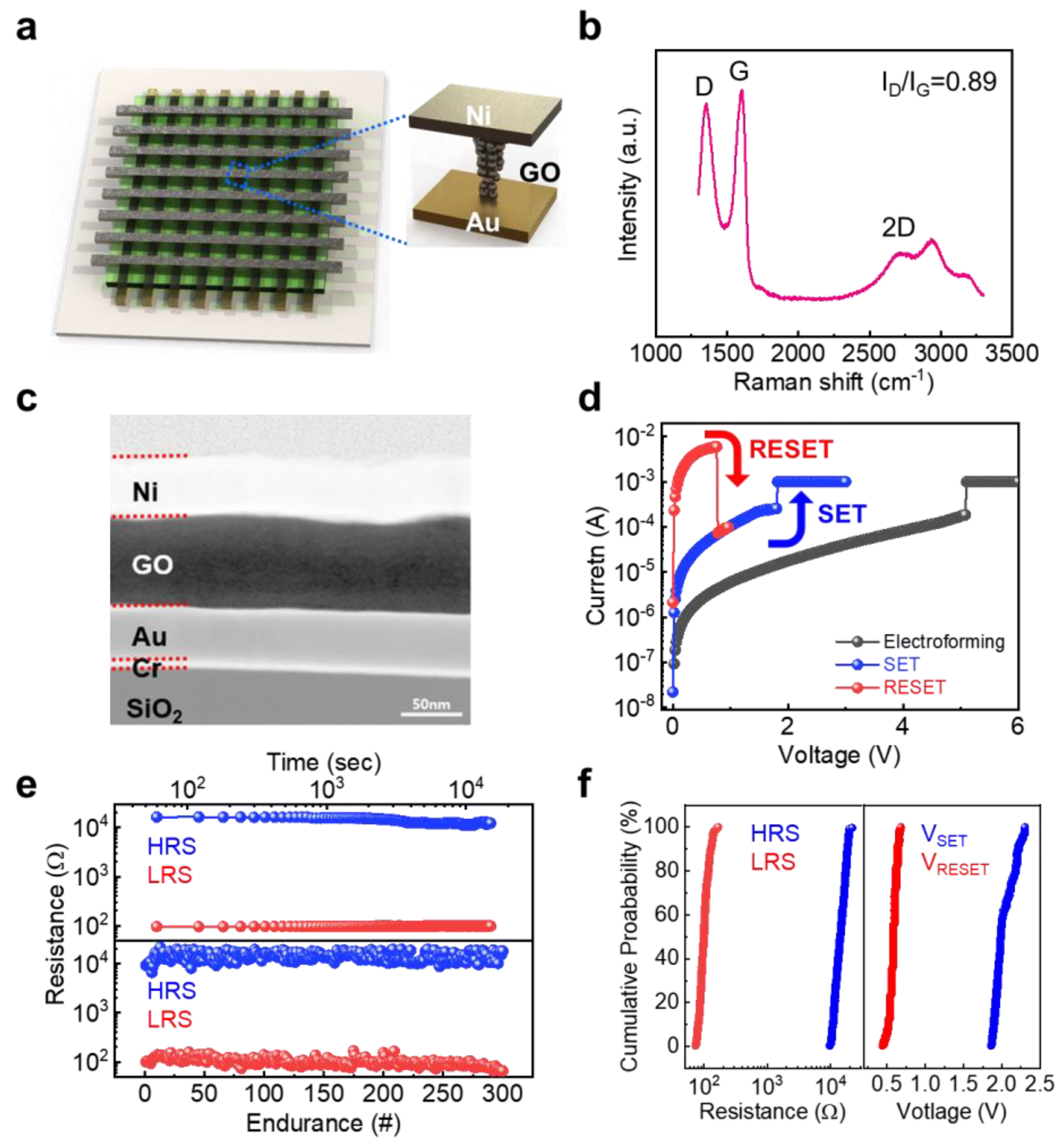

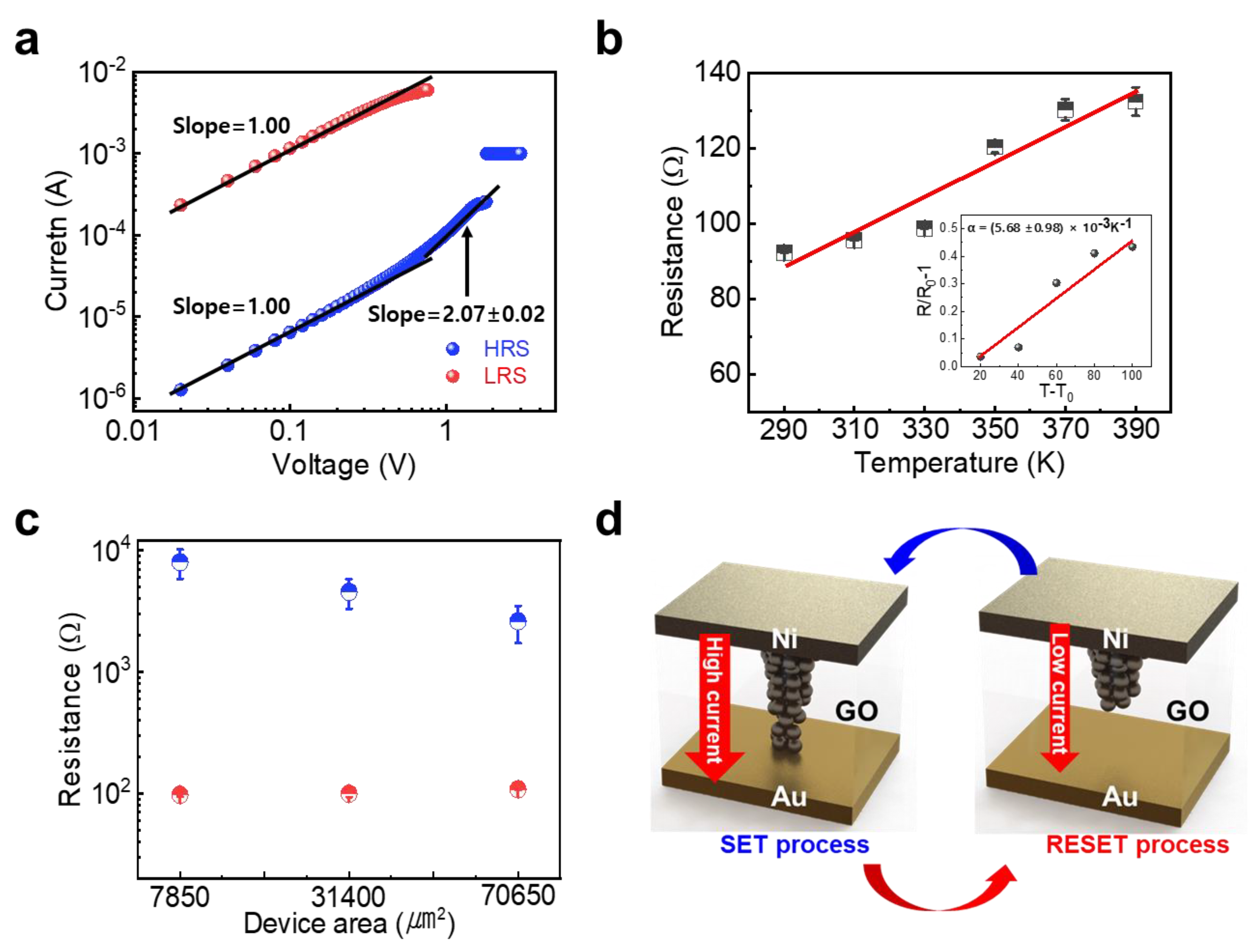

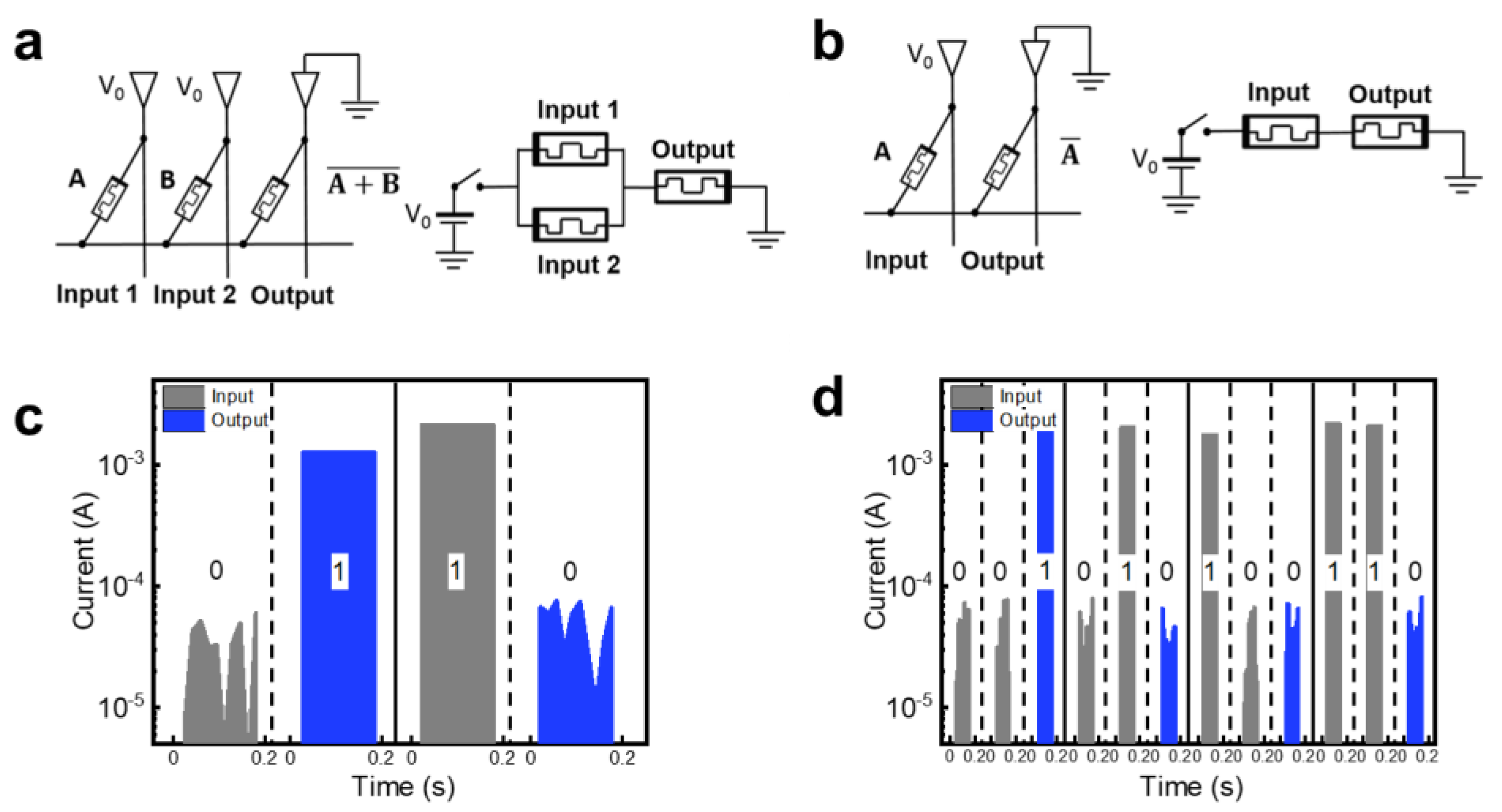

3. Results and Discussion

4. Conclusions

Supplementary Materials

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Zhang, Y.; Qu, P.; Ji, Y.; Zhang, W.; Gao, G.; Wang, G.; Song, S.; Li, G.; Chen, W.; Zheng, W.; et al. A system hierarchy for brain-inspired computing. Nature 2020, 586, 378–384. [Google Scholar] [CrossRef]

- Stone, H.S. A Logic-in-Memory Computer. IEEE Trans. Comput. 1970, 100, 73–78. [Google Scholar] [CrossRef]

- Kautz, W.H. Cellular Logic-in-Memory Arrays. IEEE Trans. Comput. 1969, C-18, 719. [Google Scholar] [CrossRef]

- Ghose, S.; Boroumand, A.; Kim, J.S.; Gomez-Luna, J.; Mutlu, O. Processing-in-memory: A workload-driven perspective. IBM J. Res. Dev. 2019, 63, 3:1–3:19. [Google Scholar] [CrossRef]

- Rupp, K.; Selberherr, S. The Economic Limit to Moore’s Law. IEEE Trans. Semicond. Manuf. 2011, 24, 1–4. [Google Scholar] [CrossRef]

- Borghetti, J.; Snider, G.S.; Kuekes, P.J.; Yang, J.J.; Stewart, D.R.; Williams, R.S. ‘Memristive’ switches enable ‘stateful’ logic operations via material implication. Nature 2010, 464, 873–876. [Google Scholar] [CrossRef]

- Talati, N.; Gupta, S.; Mane, P.; Kvatinsky, S. Logic Design Within Memristive Memories Using Memristor-Aided loGIC (MAGIC). IEEE Trans. Nanotechnol. 2016, 15, 635–650. [Google Scholar] [CrossRef]

- Kvatinsky, S.; Satat, G.; Wald, N.; Friedman, E.G.; Kolodny, A.; Weiser, U.C. Memristor-Based Material Implication (IMPLY) Logic: Design Principles and Methodologies. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2014, 22, 2054–2066. [Google Scholar] [CrossRef]

- Shin, S.; Kim, K.; Kang, S.-M. Reconfigurable Stateful NOR Gate for Large-Scale Logic-Array Integrations. IEEE Trans. Circuits Syst. II Exp. Briefs 2011, 58, 442–446. [Google Scholar] [CrossRef]

- Kvatinsky, S.; Belousov, D.; Liman, S.; Satat, G.; Wald, N.; Friedman, E.G.; Kolodny, A.; Weiser, U.C. MAGIC—Memristor-Aided Logic. IEEE Trans. Circuits Syst. II Exp. Briefs 2014, 61, 895–899. [Google Scholar] [CrossRef]

- Sun, X.; Li, G.; Ding, L.; Yang, N.; Zhang, W. Unipolar memristors enable “stateful” logic operations via material implication. Appl. Phys. Lett. 2011, 99, 072101. [Google Scholar] [CrossRef]

- Chua, L.O. Memristor—The missing circuit element. IEEE Trans. Circuit Theory 1971, 18, 507–519. [Google Scholar] [CrossRef]

- Chua, L.O.; Kang, S.M. Memristive devices and systems. Proc. IEEE 1976, 64, 209–223. [Google Scholar] [CrossRef]

- Strukov, D.B.; Snider, G.S.; Stewart, D.R.; Williams, R.S. The missing memristor found. Nature 2008, 453, 80–83. [Google Scholar] [CrossRef]

- Jang, B.C.; Yang, S.Y.; Seong, H.; Kim, S.K.; Choi, J.; Im, S.G.; Choi, S.-Y. Zero-static-power nonvolatile logic-in-memory circuits for flexible electronics. Nano Res. 2017, 10, 2459–2470. [Google Scholar] [CrossRef]

- Siemon, A.; Menzel, S.; Waser, R.; Linn, E. A Complementary Resistive Switch-Based Crossbar Array Adder. IEEE J. Emerg. Sel. Top. Circuits Syst. 2015, 5, 64–74. [Google Scholar] [CrossRef]

- Breuer, T.; Siemon, A.; Linn, E.; Menzel, S.; Waser, R.; Rana, V. A HfO2-Based Complementary Switching Crossbar Adder. Adv. Electron. Mater. 2015, 1, 1500138. [Google Scholar] [CrossRef]

- Adam, G.C.; Hoskins, B.D.; Prezioso, M.; Strukov, D.B. Optimized stateful material implication logic for three-dimensional data manipulation. Nano Res. 2016, 9, 3914–3923. [Google Scholar] [CrossRef]

- Liu, B.; Zhao, Y.; Verma, D.; Wang, L.A.; Liang, H.; Zhu, H.; Li, L.J.; Hou, T.H.; Lai, C.S. Bi2O2Se-Based Memristor-Aided Logic. ACS Appl. Mater. Interfaces 2021, 13, 15391–15398. [Google Scholar] [CrossRef]

- Hoffer, B.; Rana, V.; Menzel, S.; Waser, R.; Kvatinsky, S. Experimental Demonstration of Memristor-Aided Logic (MAGIC) Using Valence Change Memory (VCM). IEEE Trans. Electron Devices 2020, 67, 3115–3122. [Google Scholar] [CrossRef]

- Liu, J.; Yin, Z.; Cao, X.; Zhao, F.; Wang, L.; Huang, W.; Zhang, H. Fabrication of flexible, all-reduced graphene oxide non-volatile memory devices. Adv. Mater. 2013, 25, 233–238. [Google Scholar] [CrossRef] [PubMed]

- Chen, Y.; Zhang, B.; Liu, G.; Zhuang, X.; Kang, E.T. Graphene and its derivatives: Switching ON and OFF. Chem. Soc. Rev. 2012, 41, 4688–4707. [Google Scholar] [CrossRef] [PubMed]

- Castro Neto, A.H.; Guinea, F.; Peres, N.M.R.; Novoselov, K.S.; Geim, A.K. The electronic properties of graphene. Rev. Mod. Phys. 2009, 81, 109–162. [Google Scholar] [CrossRef]

- Bessonov, A.A.; Kirikova, M.N.; Petukhov, D.I.; Allen, M.; Ryhanen, T.; Bailey, M.J. Layered memristive and memcapacitive switches for printable electronics. Nat. Mater. 2015, 14, 199–204. [Google Scholar] [CrossRef]

- Huh, W.; Lee, D.; Lee, C.H. Memristors Based on 2D Materials as an Artificial Synapse for Neuromorphic Electronics. Adv. Mater. 2020, 32, e2002092. [Google Scholar] [CrossRef]

- Lee, H.S.; Sangwan, V.K.; Rojas, W.A.G.; Bergeron, H.; Jeong, H.Y.; Yuan, J.; Su, K.; Hersam, M.C. Dual-Gated MoS2 Memtransistor Crossbar Array. Adv. Funct. Mater. 2020, 30. [Google Scholar] [CrossRef]

- Shen, Y.; Zheng, W.; Zhu, K.; Xiao, Y.; Wen, C.; Liu, Y.; Jing, X.; Lanza, M. Variability and Yield in h-BN-Based Memristive Circuits: The Role of Each Type of Defect. Adv. Mater. 2021, 33, e2103656. [Google Scholar] [CrossRef]

- Knobloch, T.; Illarionov, Y.Y.; Ducry, F.; Schleich, C.; Wachter, S.; Watanabe, K.; Taniguchi, T.; Mueller, T.; Waltl, M.; Lanza, M.; et al. The performance limits of hexagonal boron nitride as an insulator for scaled CMOS devices based on two-dimensional materials. Nat. Electron. 2021, 4, 98–108. [Google Scholar] [CrossRef]

- Chen, S.; Mahmoodi, M.R.; Shi, Y.; Mahata, C.; Yuan, B.; Liang, X.; Wen, C.; Hui, F.; Akinwande, D.; Strukov, D.B.; et al. Wafer-scale integration of two-dimensional materials in high-density memristive crossbar arrays for artificial neural networks. Nat. Electron. 2020, 3, 638–645. [Google Scholar] [CrossRef]

- Zhou, Y.; Liu, D.; Wang, J.; Cheng, Z.; Liu, L.; Yang, N.; Liu, Y.; Xia, T.; Liu, X.; Zhang, X.; et al. Black Phosphorus Based Multicolor Light-Modulated Transparent Memristor with Enhanced Resistive Switching Performance. ACS Appl. Mater. Interfaces 2020, 12, 25108–25114. [Google Scholar] [CrossRef]

- Han, S.T.; Hu, L.; Wang, X.; Zhou, Y.; Zeng, Y.J.; Ruan, S.; Pan, C.; Peng, Z. Black Phosphorus Quantum Dots with Tunable Memory Properties and Multilevel Resistive Switching Characteristics. Adv. Sci. 2017, 4, 1600435. [Google Scholar] [CrossRef] [PubMed]

- Kim, S.K.; Kim, J.Y.; Jang, B.C.; Cho, M.S.; Choi, S.-Y.; Lee, J.Y.; Jeong, H.Y. Conductive Graphitic Channel in Graphene Oxide-Based Memristive Devices. Adv. Funct. Mater. 2016, 26, 7406–7414. [Google Scholar] [CrossRef]

- Kim, S.; Jung, H.J.; Kim, J.C.; Lee, K.S.; Park, S.S.; Dravid, V.P.; He, K.; Jeong, H.Y. In Situ Observation of Resistive Switching in an Asymmetric Graphene Oxide Bilayer Structure. ACS Nano 2018, 12, 7335–7342. [Google Scholar] [CrossRef]

- Johra, F.T.; Lee, J.-W.; Jung, W.-G. Facile and safe graphene preparation on solution based platform. J. Ind. Eng. Chem. 2014, 20, 2883–2887. [Google Scholar] [CrossRef]

- Jang, B.C.; Seong, H.; Kim, J.Y.; Koo, B.J.; Kim, S.K.; Yang, S.Y.; Im, S.G.; Choi, S.-Y. Ultra-low power, highly uniform polymer memory by inserted multilayer graphene electrode. 2D Materials 2015, 2, 044013. [Google Scholar] [CrossRef]

- Rose, A. Space-Charge-Limited Currents in Solids. Phys. Rev. 1955, 97, 1538–1544. [Google Scholar] [CrossRef]

- Yang, Y.C.; Pan, F.; Liu, Q.; Liu, M.; Zeng, F. Fully Room-Temperature-Fabricated Nonvolatile Resistive Memory for Ultrafast and High-Density Memory Application. Nano Lett. 2009, 9, 1636–1643. [Google Scholar] [CrossRef]

- Ju Yun, M.; Kim, H.-D.; Geun Kim, T. Improved resistive-switching characteristics observed in Pt embedded nickel-nitride films prepared by radio-frequency magnetron sputtering. J. Vac. Sci. Technol. B 2013, 31, 060601. [Google Scholar] [CrossRef]

- Nam, V.B.; Lee, D. Evaluation of Ni-Based Flexible Resistance Temperature Detectors Fabricated by Laser Digital Pattering. Nanomaterials 2021, 11, 576. [Google Scholar] [CrossRef]

- Fantini, A.; Goux, L.; Redolfi, A.; Degraeve, R.; Kar, G.; Chen, Y.Y.; Jurczak, M. Lateral and vertical scaling impact on statistical performances and reliability of 10nm TiN/Hf(Al)O/Hf/TiN RRAM devices. In Proceedings of the 2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers, Honolulu, HI, USA, 9–12 June 2014; p. 1. [Google Scholar]

- Matsunaga, S.; Hayakawa, J.; Ikeda, S.; Miura, K.; Endoh, T.; Ohno, H.; Hanyu, T. MTJ-Based Nonvolatile Logic-in-Memory Circuit, Future Prospects and Issues. In Proceedings of the 2009 Design, Automation & Test in Europe Conference & Exhibition, Nice, France, 20–24 April 2009; pp. 433–435. [Google Scholar]

- Bae, H.; Jang, B.C.; Park, H.; Jung, S.H.; Lee, H.M.; Park, J.Y.; Jeon, S.B.; Son, G.; Tcho, I.W.; Yu, K.; et al. Functional Circuitry on Commercial Fabric via Textile-Compatible Nanoscale Film Coating Process for Fibertronics. Nano Lett. 2017, 17, 6443–6452. [Google Scholar] [CrossRef]

- Louis, J.; Hoffer, B.; Kvatinsky, S. Performing Memristor-Aide Logic (MAGIC) using STT-MRAM. In Proceedings of the 26th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Genoa, Italy, 27–29 November 2019; pp. 787–790. [Google Scholar]

- Kim, Y.S.; Son, M.W.; Song, H.; Park, J.; An, J.; Jeon, J.B.; Kim, G.Y.; Son, S.; Kim, K.M. Stateful In-Memory Logic System and Its Practical Implementation in a TaOx-Based Bipolar-Type Memristive Crossbar Array. Adv. Intell. Syst. 2020, 2, 1900156. [Google Scholar] [CrossRef] [Green Version]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, Y.; Jeon, S.-B.; Jang, B.C. Graphene Oxide-Based Memristive Logic-in-Memory Circuit Enabling Normally-Off Computing. Nanomaterials 2023, 13, 710. https://doi.org/10.3390/nano13040710

Kim Y, Jeon S-B, Jang BC. Graphene Oxide-Based Memristive Logic-in-Memory Circuit Enabling Normally-Off Computing. Nanomaterials. 2023; 13(4):710. https://doi.org/10.3390/nano13040710

Chicago/Turabian StyleKim, Yeongkwon, Seung-Bae Jeon, and Byung Chul Jang. 2023. "Graphene Oxide-Based Memristive Logic-in-Memory Circuit Enabling Normally-Off Computing" Nanomaterials 13, no. 4: 710. https://doi.org/10.3390/nano13040710