Memristor-Based Signal Processing for Compressed Sensing

Abstract

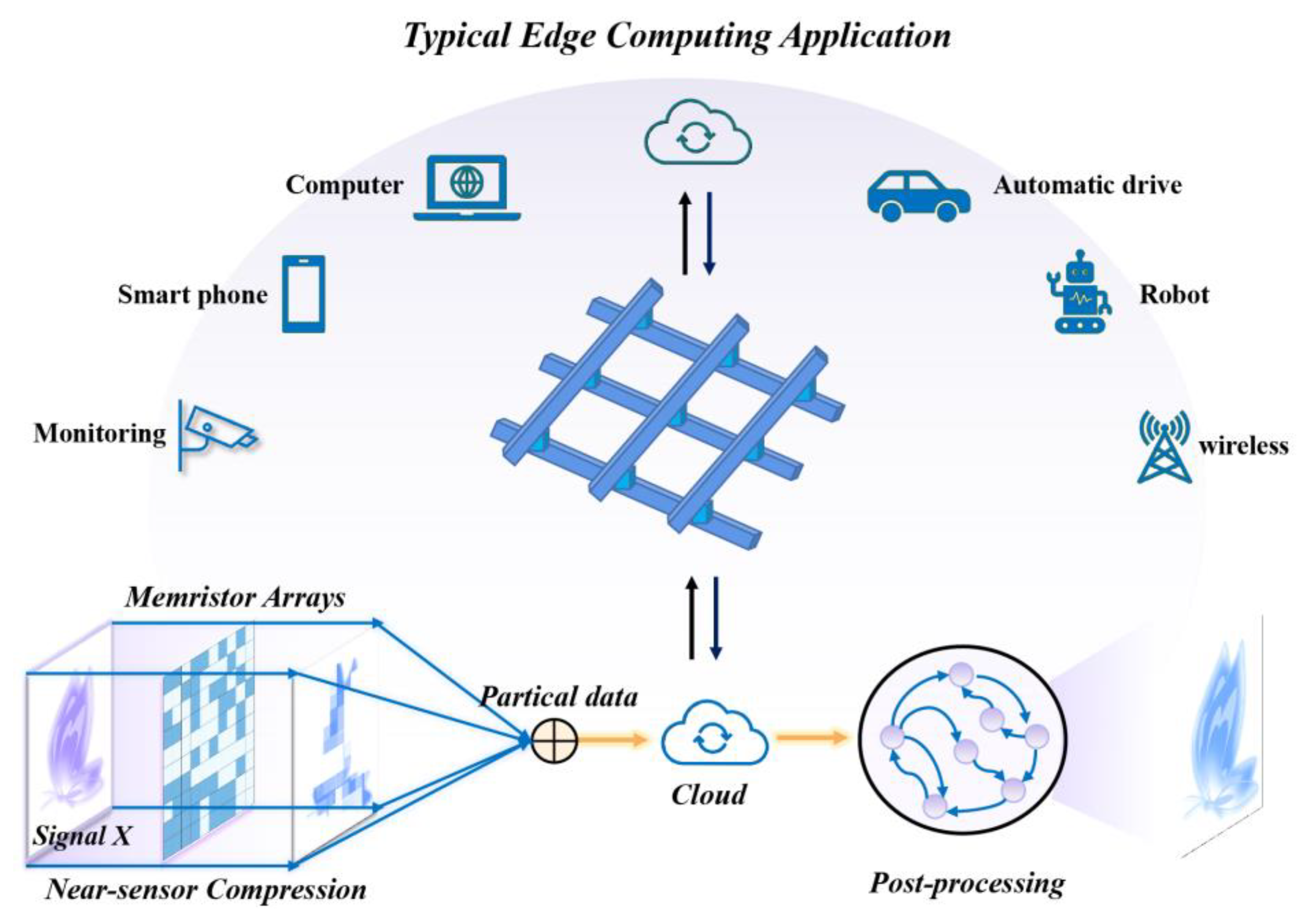

1. Introduction

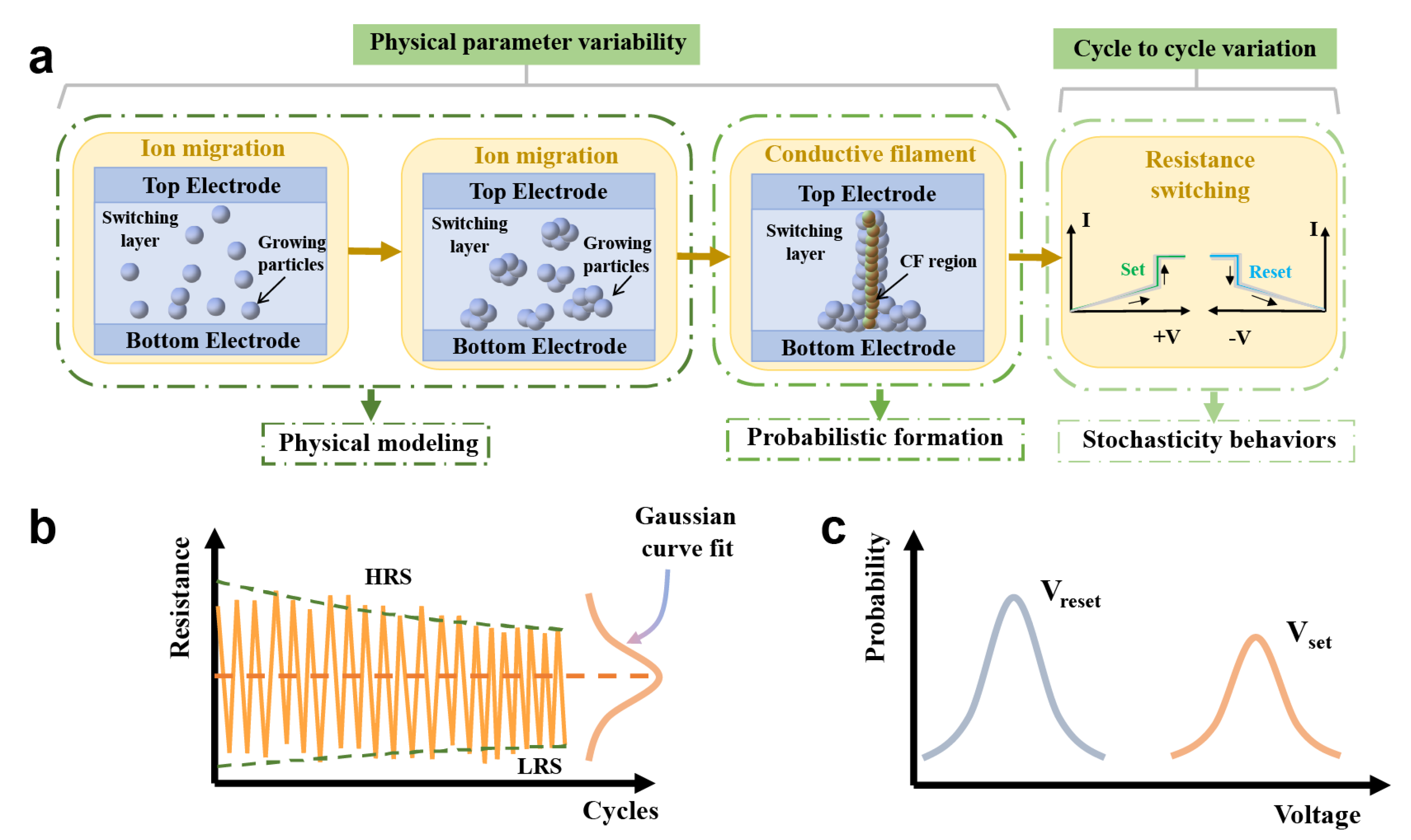

2. Investigation of Memristor Inherent Variation

2.1. Inherent Variation Metrics Study

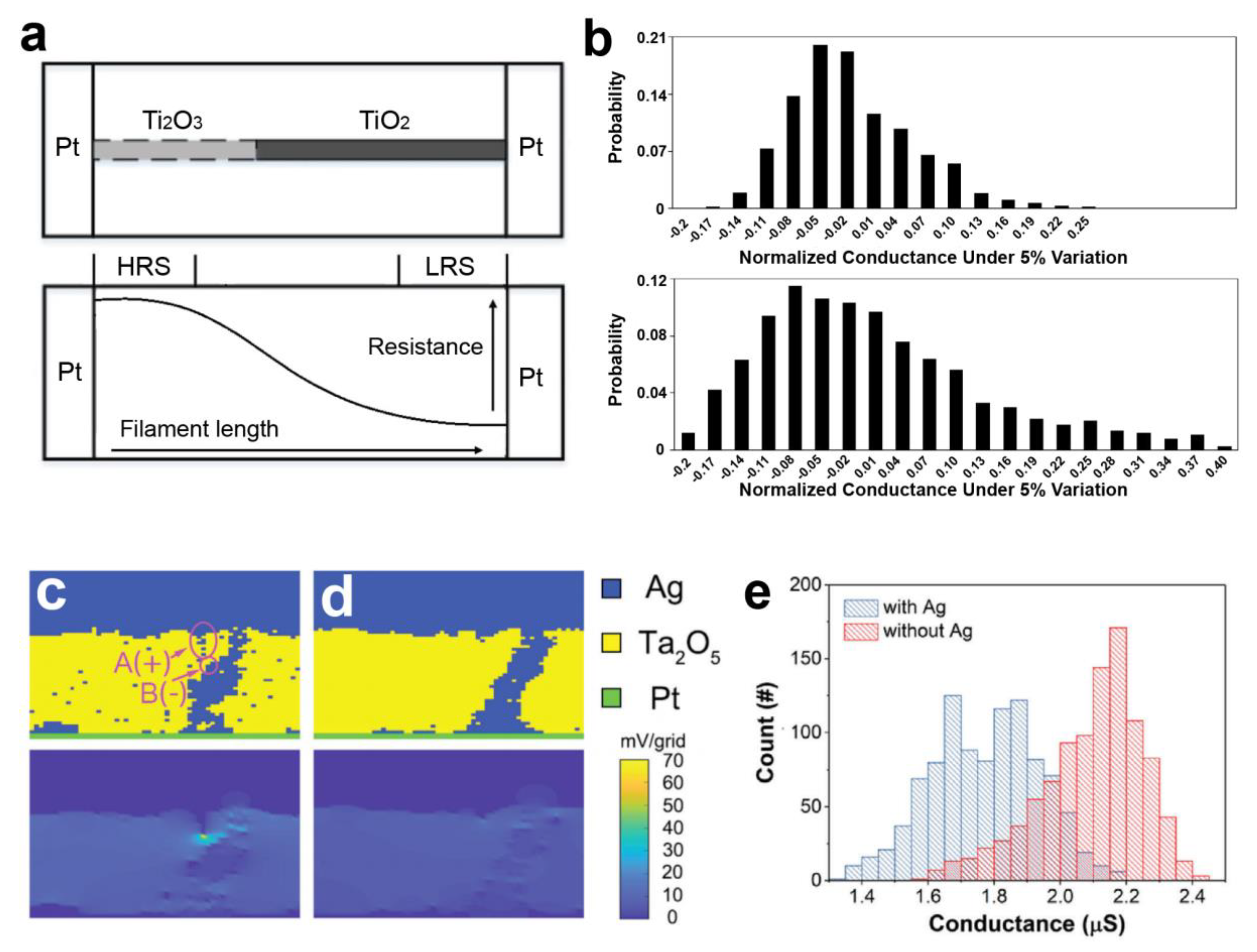

2.2. Conductive Filament Mechanism

2.2.1. Electrochemical Metallization Mechanism (ECM)

2.2.2. Valence Change Mechanism (VCM)

2.2.3. Phase-Change Mechanism (PCM)

2.3. Physical Model for Stochasticity Distributions

3. Memristor Crossbar Arrays for Matrix-Vector Multiplication

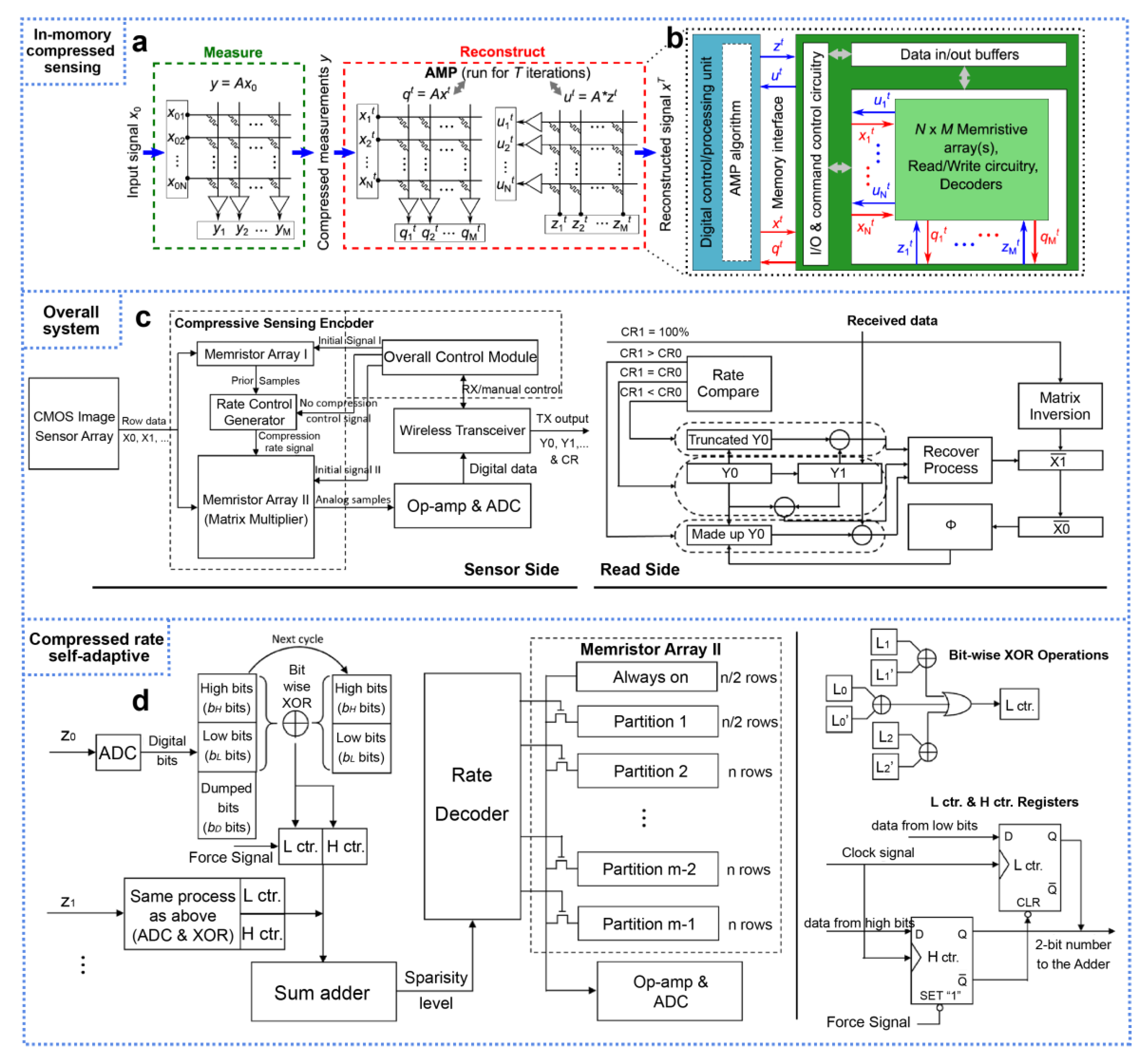

4. Memristor Arrays for Compressed Sensing

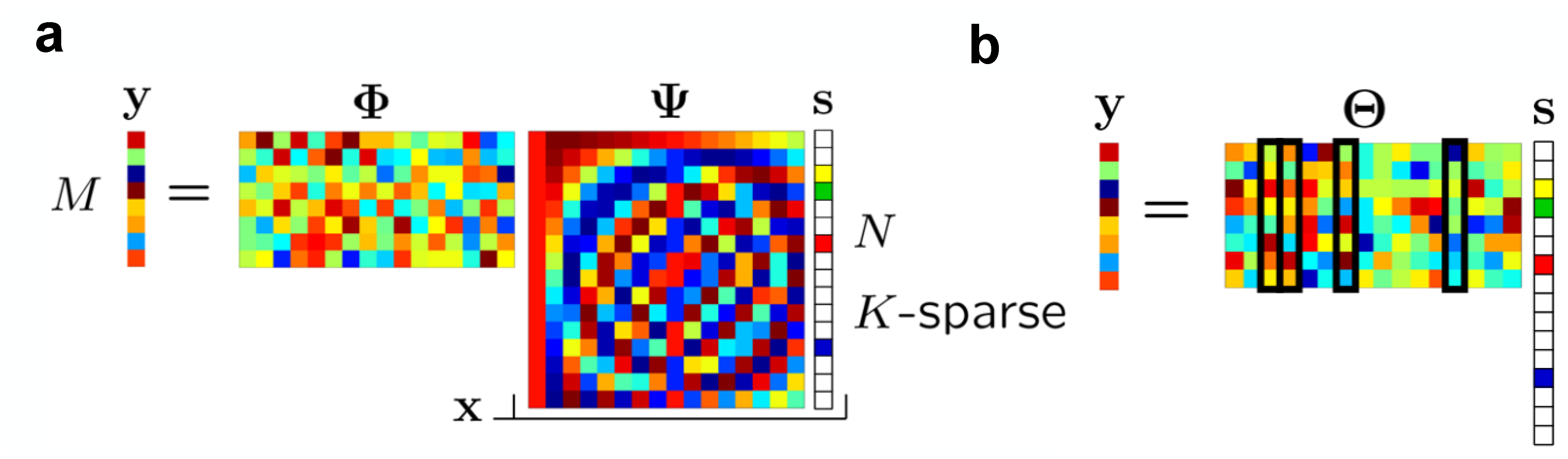

4.1. Compressed Sensing

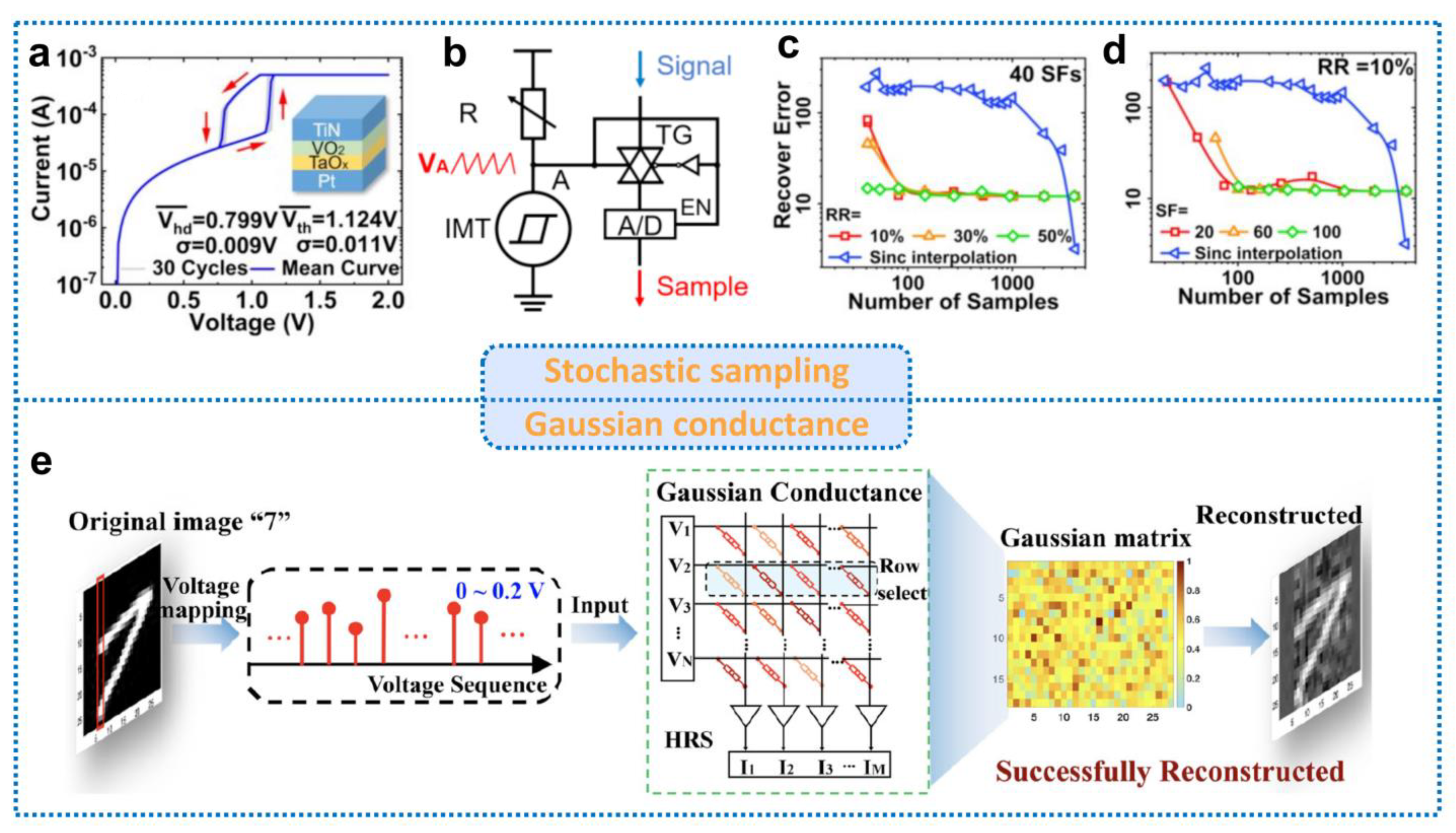

4.2. Non-Volatile Memristor for Compressed Sensing

4.3. Volatile Memristor for Compressed Sensing

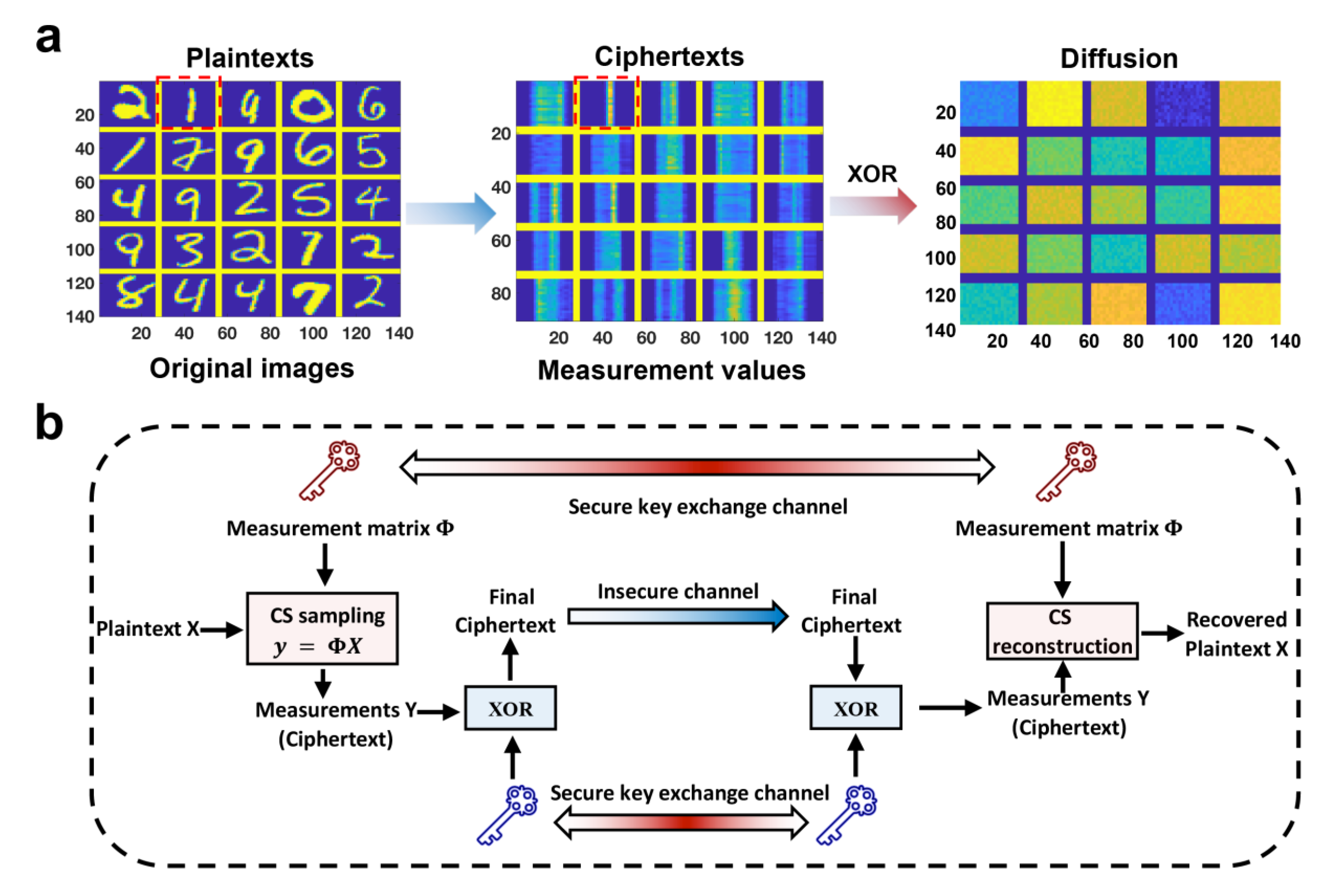

5. All-in-One Memristor-Based Compression and Cryptosystem

6. Conclusions and Prospect

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Hittinger, E.; Jaramillo, P. Internet of Things: Energy boon or bane? Science 2019, 364, 326–328. [Google Scholar] [CrossRef] [PubMed]

- Wang, R.; Wang, S.; Liang, K.; Xin, Y.; Li, F.; Cao, Y.; Lv, J.; Liang, Q.; Peng, Y.; Zhu, B.; et al. Bio-Inspired In-Sensor Compression and Computing Based on Phototransistors. Small 2022, 18, 2201111. [Google Scholar] [CrossRef] [PubMed]

- Zhou, F.; Chai, Y. Near-sensor and in-sensor computing. Nat. Electron. 2020, 3, 664–671. [Google Scholar] [CrossRef]

- Baraniuk, R.G. Compressive Sensing [Lecture Notes]. IEEE Signal Process. Mag. 2007, 24, 118–121. [Google Scholar] [CrossRef]

- Candes, E.J.; Tao, T. Near-Optimal Signal Recovery from Random Projections: Universal Encoding Strategies? IEEE Trans. Inf. Theory 2006, 52, 5406–5425. [Google Scholar] [CrossRef]

- Xia, Q.; Yang, J.J. Memristive crossbar arrays for brain-inspired computing. Nat. Mater. 2019, 18, 309–323. [Google Scholar] [CrossRef]

- Oh, I.; Pyo, J.; Kim, S. Resistive Switching and Synaptic Characteristics in ZnO/TaON-Based RRAM for Neuromorphic System. Nanomaterials 2022, 12, 2185. [Google Scholar] [CrossRef]

- Chen, L.L.; Ma, Z.Y.; Leng, K.M.; Chen, T.; Hu, H.S.; Yang, Y.; Li, W.; Xu, J.; Xu, L.; Chen, K.J. Artificial Synapse Consisted of TiSbTe/SiCx:H Memristor with Ultra-high Uniformity for Neuromorphic Computing. Nanomaterials 2022, 12, 2110. [Google Scholar] [CrossRef]

- Lin, J.F.; Liu, H.X.; Wang, S.L.; Wang, D.; Wu, L. The Image Identification Application with HfO2-Based Replaceable 1T1R Neural Networks. Nanomaterials 2022, 12, 1075. [Google Scholar] [CrossRef]

- Ryu, H.; Kim, S. Pseudo-Interface Switching of a Two-Terminal TaOx/HfO(2)Synaptic Device for Neuromorphic Applications. Nanomaterials 2020, 10, 1550. [Google Scholar] [CrossRef]

- Li, C.; Hu, M.; Li, Y.; Jiang, H.; Ge, N.; Montgomery, E.; Zhang, J.; Song, W.; Dávila, N.; Graves, C.E.; et al. Analogue signal and image processing with large memristor crossbars. Nat. Electron. 2018, 1, 52–59. [Google Scholar] [CrossRef]

- Li, C.; Belkin, D.; Li, Y.; Yan, P.; Hu, M.; Ge, N.; Jiang, H.; Montgomery, E.; Lin, P.; Wang, Z.; et al. Efficient and self-adaptive in situ learning in multilayer memristor neural networks. Nat. Commun. 2018, 9, 2385. [Google Scholar] [CrossRef] [PubMed]

- Li, C.; Wang, Z.; Rao, M.; Belkin, D.; Song, W.; Jiang, H.; Yan, P.; Li, Y.; Lin, P.; Hu, M.; et al. Long short-term memory networks in memristor crossbar arrays. Nat. Mach. Intell. 2019, 1, 49–57. [Google Scholar] [CrossRef]

- Hu, M.; Graves, C.E.; Li, C.; Li, Y.; Ge, N.; Montgomery, E.; Davila, N.; Jiang, H.; Williams, R.S.; Yang, J.J.; et al. Memristor-Based Analog Computation and Neural Network Classification with a Dot Product Engine. Adv. Mater. 2018, 30, 1705914. [Google Scholar] [CrossRef]

- Sheridan, P.M.; Cai, F.; Du, C.; Ma, W.; Zhang, Z.; Lu, W.D. Sparse coding with memristor networks. Nat. Nanotechnol. 2017, 12, 784–789. [Google Scholar] [CrossRef] [PubMed]

- Chen, A.; Lin, M.-R.C. Variability of resistive switching memories and its impact on crossbar array performance. In Proceedings of the 2011 International Reliability Physics Symposium, Monterey, CA, USA, 10–14 April 2011. [Google Scholar]

- Prezioso, M.; Merrikh-Bayat, F.; Hoskins, B.D.; Adam, G.C.; Likharev, K.K.; Strukov, D.B. Training and operation of an integrated neuromorphic network based on metal-oxide memristors. Nature 2015, 521, 61–64. [Google Scholar] [CrossRef]

- Gao, B.; Bi, Y.; Chen, H.-Y.; Liu, R.; Huang, P.; Chen, B.; Liu, L.; Liu, X.; Yu, S.; Wong, H.S.P.; et al. Ultra-Low-Energy Three-Dimensional Oxide-Based Electronic Synapses for Implementation of Robust High-Accuracy Neuromorphic Computation Systems. ACS Nano 2014, 8, 6998–7004. [Google Scholar] [CrossRef]

- Joksas, D.; Freitas, P.; Chai, Z.; Ng, W.H.; Buckwell, M.; Li, C.; Zhang, W.D.; Xia, Q.; Kenyon, A.J.; Mehonic, A. Committee machines—A universal method to deal with non-idealities in memristor-based neural networks. Nat. Commun. 2020, 11, 4273. [Google Scholar]

- Lastras-Montaño, M.A.; Cheng, K.-T. Resistive random-access memory based on ratioed memristors. Nat. Electron. 2018, 1, 466–472. [Google Scholar] [CrossRef]

- Yu, S.; Gao, B.; Fang, Z.; Yu, H.; Kang, J.; Wong, H.-S.P. A Low Energy Oxide-Based Electronic Synaptic Device for Neuromorphic Visual Systems with Tolerance to Device Variation. Adv. Mater. 2013, 25, 1774–1779. [Google Scholar] [CrossRef]

- Zhao, M.; Gao, B.; Tang, J.; Qian, H.; Wu, H. Reliability of analog resistive switching memory for neuromorphic computing. Appl. Phys. Rev. 2020, 7, 011301. [Google Scholar] [CrossRef]

- Song, B.; Cao, R.R.; Xu, H.; Liu, S.; Liu, H.J.; Li, Q.J. A HfO2/SiTe Based Dual-Layer Selector Device with Minor Threshold Voltage Variation. Nanomaterials 2019, 9, 408. [Google Scholar] [CrossRef] [PubMed]

- Rajendran, B.; Breitwisch, M.; Lee, M.H.; Burr, G.W.; Shih, Y.H.; Cheek, R.; Schrott, A.; Chen, C.F.; Joseph, E.; Dasaka, R.; et al. Dynamic Resistance—A Metric for Variability Characterization of Phase-Change Memory. IEEE Electron Device Lett. 2009, 30, 126–129. [Google Scholar] [CrossRef]

- Cheng, B.; Emboras, A.; Salamin, Y.; Ducry, F.; Ma, P.; Fedoryshyn, Y.; Andermatt, S.; Luisier, M.; Leuthold, J. Ultra compact electrochemical metallization cells offering reproducible atomic scale memristive switching. Commun. Phys. 2019, 2, 28. [Google Scholar] [CrossRef]

- Waser, R.; Aono, M. Nanoionics-based resistive switching memories. Nat. Mater. 2007, 6, 833–840. [Google Scholar] [CrossRef]

- Naous, R.; Al-Shedivat, M.; Salama, K.N. Stochasticity Modeling in Memristors. IEEE Trans. Nanotechnol. 2016, 15, 15–28. [Google Scholar] [CrossRef]

- Gao, L.; Ren, Q.; Sun, J.; Han, S.-T.; Zhou, Y. Memristor modeling: Challenges in theories, simulations, and device variability. J. Mater. Chem. C 2021, 9, 16859–16884. [Google Scholar] [CrossRef]

- Liu, B.; Chang, Y.-F.; Li, J.; Liu, X.; Wang, L.A.; Verma, D.; Liang, H.; Zhu, H.; Zhao, Y.; Li, L.-J.; et al. Bi2O2Se-Based True Random Number Generator for Security Applications. ACS Nano 2022, 16, 6847–6857. [Google Scholar] [CrossRef]

- Ding, Q.; Jiang, H.; Li, J.; Liu, C.; Yu, J.; Chen, P.; Zhao, Y.; Ding, Y.; Gong, T.; Yang, J. Unified 0.75 pJ/Bit TRNG and Attack Resilient 2F 2/Bit PUF for Robust Hardware Security Solutions with 4-layer Stacking 3D NbOx Threshold Switching Array. In Proceedings of the 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 13–15 December 2021. [Google Scholar]

- Tuma, T.; Pantazi, A.; Le Gallo, M.; Sebastian, A.; Eleftheriou, E. Stochastic phase-change neurons. Nat. Nanotechnol. 2016, 11, 693–699. [Google Scholar] [CrossRef]

- Szot, K.; Speier, W.; Bihlmayer, G.; Waser, R. Switching the electrical resistance of individual dislocations in single-crystalline SrTiO3. Nat. Mater. 2006, 5, 312–320. [Google Scholar] [CrossRef]

- Yan, X.; Zhao, J.; Liu, S.; Zhou, Z.; Liu, Q.; Chen, J.; Liu, X.Y. Memristor with Ag-Cluster-Doped TiO2 films as artificial synapse for neuroinspired computing. Adv. Funct. Mater. 2018, 28, 1705320. [Google Scholar] [CrossRef]

- Zhao, M.; Wang, S.; Li, D.; Wang, R.; Li, F.; Wu, M.; Liang, K.; Ren, H.; Zheng, X.; Guo, C. Silk protein based volatile threshold switching memristors for neuromorphic computing. Adv. Electron. Mater. 2022, 8, 2101139. [Google Scholar] [CrossRef]

- Herpers, A.; Lenser, C.; Park, C.; Offi, F.; Borgatti, F.; Panaccione, G.; Menzel, S.; Waser, R.; Dittmann, R. Spectroscopic Proof of the Correlation between Redox-State and Charge-Carrier Transport at the Interface of Resistively Switching Ti/PCMO Devices. Adv. Mater. 2014, 26, 2730–2735. [Google Scholar] [CrossRef]

- Kinoshita, K.; Tamura, T.; Aoki, M.; Sugiyama, Y.; Tanaka, H. Bias polarity dependent data retention of resistive random access memory consisting of binary transition metal oxide. Appl. Phys. Lett. 2006, 89, 103509. [Google Scholar] [CrossRef]

- Wong, H.-S.P.; Lee, H.-Y.; Yu, S.; Chen, Y.-S.; Wu, Y.; Chen, P.-S.; Lee, B.; Chen, F.T.; Tsai, M.-J. Metal–oxide RRAM. Proc. IEEE 2012, 100, 1951–1970. [Google Scholar] [CrossRef]

- Worledge, D.C.; Gajek, M.; Abraham, D.W.; Brown, S.; Gaidis, M.C.; Hu, G.; Nowak, J.; Sullivan, E.J.O.; Robertazzi, R.P.; Sun, J.Z.; et al. Recent Advances in Spin Torque MRAM. In Proceedings of the 2012 4th IEEE International Memory Workshop, Milan, Italy, 20–23 May 2012. [Google Scholar]

- Zhang, T.; Yang, K.; Xu, X.; Cai, Y.; Yang, Y.; Huang, R. Memristive Devices and Networks for Brain-Inspired Computing. Phys. Status Solidi Rapid Res. Lett. 2019, 13, 1900029. [Google Scholar] [CrossRef]

- Waser, R.; Dittmann, R.; Staikov, G.; Szot, K. Redox-Based Resistive Switching Memories—Nanoionic Mechanisms, Prospects, and Challenges. Adv. Mater. 2009, 21, 2632–2663. [Google Scholar] [CrossRef]

- Valov, I.; Waser, R.; Jameson, J.R.; Kozicki, M.N. Electrochemical metallization memories—Fundamentals, applications, prospects. Nanotechnology 2011, 22, 254003. [Google Scholar] [CrossRef]

- Akinaga, H.; Shima, H. Resistive Random Access Memory (ReRAM) Based on Metal Oxides. Proc. IEEE 2010, 98, 2237–2251. [Google Scholar] [CrossRef]

- Lee, J.; Lu, W.D. On-Demand Reconfiguration of Nanomaterials: When Electronics Meets Ionics. Adv. Mater. 2018, 30, 1702770. [Google Scholar] [CrossRef]

- Wong, H.-S.P.; Raoux, S.; Kim, S.; Liang, J.; Reifenberg, J.P.; Rajendran, B.; Asheghi, M.; Goodson, K.E. Phase Change Memory. Proc. IEEE 2010, 98, 2201–2227. [Google Scholar] [CrossRef]

- Wang, Z.; Rao, M.; Midya, R.; Joshi, S.; Jiang, H.; Lin, P.; Song, W.; Asapu, S.; Zhuo, Y.; Li, C.; et al. Threshold Switching of Ag or Cu in Dielectrics: Materials, Mechanism, and Applications. Adv. Funct. Mater. 2018, 28, 1704862. [Google Scholar] [CrossRef]

- Valov, I.; Kozicki, M.N. Cation-based resistance change memory. J. Phys. D 2013, 46, 074005. [Google Scholar] [CrossRef]

- Yang, Y.; Gao, P.; Gaba, S.; Chang, T.; Pan, X.; Lu, W. Observation of conducting filament growth in nanoscale resistive memories. Nat. Commun. 2012, 3, 732. [Google Scholar] [CrossRef] [PubMed]

- Song, J.; Woo, J.; Prakash, A.; Lee, D.; Hwang, H. Threshold selector with high selectivity and steep slope for cross-point memory array. IEEE Electron Device Lett. 2015, 36, 681–683. [Google Scholar] [CrossRef]

- Chen, J.-Y.; Hsin, C.-L.; Huang, C.-W.; Chiu, C.-H.; Huang, Y.-T.; Lin, S.-J.; Wu, W.-W.; Chen, L.-J. Dynamic Evolution of Conducting Nanofilament in Resistive Switching Memories. Nano Lett. 2013, 13, 3671–3677. [Google Scholar] [CrossRef] [PubMed]

- Sun, K.; Chen, J.; Yan, X. The Future of Memristors: Materials Engineering and Neural Networks. Adv. Funct. Mater. 2021, 31, 2006773. [Google Scholar] [CrossRef]

- Kuzum, D.; Jeyasingh, R.G.; Lee, B.; Wong, H.-S.P. Nanoelectronic programmable synapses based on phase change materials for brain-inspired computing. Nano Lett. 2012, 12, 2179–2186. [Google Scholar] [CrossRef]

- Wentzcovitch, R.M.; Schulz, W.W.; Allen, P.B. VO2: Peierls or Mott-Hubbard? A view from band theory. Phys. Rev. Lett. 1994, 72, 3389. [Google Scholar] [CrossRef]

- Liu, R.; Wu, H.; Pang, Y.; Qian, H.; Yu, S. Experimental Characterization of Physical Unclonable Function Based on 1 kb Resistive Random Access Memory Arrays. IEEE Electron Device Lett. 2015, 36, 1380–1383. [Google Scholar] [CrossRef]

- Gao, L.; Chen, P.-Y.; Liu, R.; Yu, S. Physical unclonable function exploiting sneak paths in resistive cross-point array. IEEE Trans. Electron Devices 2016, 63, 3109–3115. [Google Scholar] [CrossRef]

- Liu, R.; Wu, H.; Pang, Y.; Qian, H.; Yu, S. A highly reliable and tamper-resistant RRAM PUF: Design and experimental validation. In Proceedings of the 2016 IEEE International Symposium on Hardware Oriented Security and Trust (HOST), McLean, VA, USA, 3–5 May 2016. [Google Scholar]

- Park, J.; Lee, Y.; Jeong, H.; Choi, S. Neural network physically unclonable function: A trainable physically unclonable function system with unassailability against deep learning attacks using memristor array. Adv. Intell. Syst. 2021, 3, 2100111. [Google Scholar] [CrossRef]

- John, R.A.; Shah, N.; Vishwanath, S.K.; Ng, S.E.; Febriansyah, B.; Jagadeeswararao, M.; Chang, C.-H.; Basu, A.; Mathews, N. Halide perovskite memristors as flexible and reconfigurable physical unclonable functions. Nat. Commun. 2021, 12, 3681. [Google Scholar] [CrossRef] [PubMed]

- Zhang, R.; Jiang, H.; Wang, Z.; Lin, P.; Zhuo, Y.; Holcomb, D.; Zhang, D.; Yang, J.; Xia, Q. Nanoscale diffusive memristor crossbars as physical unclonable functions. Nanoscale 2018, 10, 2721–2726. [Google Scholar] [CrossRef] [PubMed]

- Pang, Y.; Gao, B.; Lin, B.; Qian, H.; Wu, H. Memristors for hardware security applications. Adv. Electron. Mater. 2019, 5, 1800872. [Google Scholar] [CrossRef]

- Mazady, A.; Anwar, M. Memristor: Part I—The Underlying Physics and Conduction Mechanism. IEEE Trans. Electron Devices 2014, 61, 1054–1061. [Google Scholar] [CrossRef]

- Qian, F.; Gong, Y.; Huang, G.; Ahi, K.; Anwar, M.; Wang, L. A memristor-based compressive sensing architecture. In Proceedings of the 2016 IEEE/ACM International Symposium on Nanoscale Architectures (NANOARCH), Beijing, China, 18–20 July 2016. [Google Scholar]

- Naous, R.; AlShedivat, M.; Neftci, E.; Cauwenberghs, G.; Salama, K.N. Memristor-based neural networks: Synaptic versus neuronal stochasticity. AIP Adv. 2016, 6, 111304. [Google Scholar] [CrossRef]

- Wang, W.; Zhou, G.; Wang, Y.; Yan, B.; Sun, B.; Duan, S.; Song, Q. Multiphotoconductance levels of the organic semiconductor of polyimide-based memristor induced by interface charges. J. Phys. Chem. Lett. 2022, 13, 9941–9949. [Google Scholar] [CrossRef]

- Nili, H.; Adam, G.C.; Hoskins, B.; Prezioso, M.; Kim, J.; Mahmoodi, M.R.; Bayat, F.M.; Kavehei, O.; Strukov, D.B. Hardware-intrinsic security primitives enabled by analogue state and nonlinear conductance variations in integrated memristors. Nat. Electron. 2018, 1, 197–202. [Google Scholar] [CrossRef]

- Suri, M.; Bichler, O.; Querlioz, D.; Palma, G.; Vianello, E.; Vuillaume, D.; Gamrat, C.; DeSalvo, B. CBRAM devices as binary synapses for low-power stochastic neuromorphic systems: Auditory (cochlea) and visual (retina) cognitive processing applications. In Proceedings of the 2012 International Electron Devices Meeting, San Francisco, CA, USA, 10–13 December 2012. [Google Scholar]

- Huang, H.M.; Xiao, Y.; Yang, R.; Yu, Y.T.; He, H.K.; Wang, Z.; Guo, X. Implementation of dropout neuronal units based on stochastic memristive devices in neural networks with high classification accuracy. Adv. Sci. 2020, 7, 2001842. [Google Scholar] [CrossRef]

- Chen, Q.; Zhang, Y.; Liu, S.; Han, T.; Chen, X.; Xu, Y.; Meng, Z.; Zhang, G.; Zheng, X.; Zhao, J. Switchable perovskite photovoltaic sensors for bioinspired adaptive machine vision. Adv. Intell. Syst. 2020, 2, 2000122. [Google Scholar] [CrossRef]

- Wang, W.; Covi, E.; Milozzi, A.; Farronato, M.; Ricci, S.; Sbandati, C.; Pedretti, G.; Ielmini, D. Neuromorphic motion detection and orientation selectivity by volatile resistive switching memories. Adv. Intell. Syst. 2021, 3, 2000224. [Google Scholar] [CrossRef]

- Chu, M.; Kim, B.; Park, S.; Hwang, H.; Jeon, M.; Lee, B.H.; Lee, B.-G. Neuromorphic hardware system for visual pattern recognition with memristor array and CMOS neuron. IEEE Trans. Ind. Electron. 2014, 62, 2410–2419. [Google Scholar] [CrossRef]

- Zhong, Y.; Tang, J.; Li, X.; Gao, B.; Qian, H.; Wu, H. Dynamic memristor-based reservoir computing for high-efficiency temporal signal processing. Nat. Commun. 2021, 12, 408. [Google Scholar] [CrossRef] [PubMed]

- Zidan, M.A.; Jeong, Y.; Lee, J.; Chen, B.; Huang, S.; Kushner, M.J.; Lu, W.D. A general memristor-based partial differential equation solver. Nat. Electron. 2018, 1, 411–420. [Google Scholar] [CrossRef]

- Sun, Z.; Pedretti, G.; Ambrosi, E.; Bricalli, A.; Wang, W.; Ielmini, D. Solving matrix equations in one step with cross-point resistive arrays. Proc. Natl. Acad. Sci. USA 2019, 116, 4123–4128. [Google Scholar] [CrossRef]

- Prezioso, M.; Kataeva, I.; Merrikh-Bayat, F.; Hoskins, B.; Strukov, D. Modeling and implementation of firing-rate neuromorphic-network classifiers with bilayer Pt/Al2O3/TiO2x/Pt Memristors. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015. [Google Scholar]

- Lim, D.-H.; Wu, S.; Zhao, R.; Lee, J.-H.; Jeong, H.; Shi, L. Spontaneous sparse learning for PCM-based memristor neural networks. Nat. Commun. 2021, 12, 319. [Google Scholar] [CrossRef]

- Wang, K.; Hu, Q.; Gao, B.; Lin, Q.; Zhuge, F.-W.; Zhang, D.-Y.; Wang, L.; He, Y.-H.; Scheicher, R.H.; Tong, H. Threshold switching memristor-based stochastic neurons for probabilistic computing. Mater. Horizons 2021, 8, 619–629. [Google Scholar] [CrossRef]

- Wang, C.; Liang, S.-J.; Wang, C.-Y.; Yang, Z.-Z.; Ge, Y.; Pan, C.; Shen, X.; Wei, W.; Zhao, Y.; Zhang, Z. Scalable massively parallel computing using continuous-time data representation in nanoscale crossbar array. Nat. Nanotechnol. 2021, 16, 1079–1085. [Google Scholar] [CrossRef]

- Donoho, D.L. Compressed sensing. IEEE Trans. Inf. Theory 2006, 52, 1289–1306. [Google Scholar] [CrossRef]

- Jerri, A.J. The Shannon sampling theorem—Its various extensions and applications: A tutorial review. Proc. IEEE 1977, 65, 1565–1596. [Google Scholar] [CrossRef]

- Nakos, V.; Song, Z. Stronger L2/L2 compressed sensing; without iterating. In Proceedings of the 51st Annual ACM SIGACT Symposium on Theory of Computing, New York, NY, USA, 23–26 June 2019. [Google Scholar]

- Qian, F.; Gong, Y.; Wang, L. A memristor based image sensor exploiting compressive measurement for low-power video streaming. In Proceedings of the 2017 IEEE International Symposium on Circuits and Systems (ISCAS), Baltimore, MD, USA, 28–31 May 2017. [Google Scholar]

- Zhang, B.; Uysal, N.; Ewetz, R. Computational restructuring: Rethinking image processing using memristor crossbar arrays. In Proceedings of the 2020 Design, Automation & Test in Europe Conference & Exhibition (DATE), Grenoble, France, 9–13 March 2020. [Google Scholar]

- Ankit, A.; Hajj, I.E.; Chalamalasetti, S.R.; Ndu, G.; Foltin, M.; Williams, R.S.; Faraboschi, P.; Hwu, W.-M.W.; Strachan, J.P.; Roy, K. PUMA: A programmable ultra-efficient memristor-based accelerator for machine learning inference. In Proceedings of the Twenty-Fourth International Conference on Architectural Support for Programming Languages and Operating Systems, Providence, RI, USA, 13–17 April 2019. [Google Scholar]

- Tsaig, Y.; Donoho, D.L. Extensions of compressed sensing. Signal Process. 2006, 86, 549–571. [Google Scholar] [CrossRef]

- Candès, E.J.; Wakin, M.B. An introduction to compressive sampling. IEEE Signal Process. Mag. 2008, 25, 21–30. [Google Scholar] [CrossRef]

- Arjoune, Y.; Kaabouch, N.; El Ghazi, H.; Tamtaoui, A. A performance comparison of measurement matrices in compressive sensing. Int. J. Commun. Syst. 2018, 31, e3576. [Google Scholar] [CrossRef]

- Wang, Y.; Li, X.; Yu, H.; Ni, L.; Yang, W.; Weng, C.; Zhao, J. Optimizing Boolean embedding matrix for compressive sensing in RRAM crossbar. In Proceedings of the 2015 IEEE/ACM International Symposium on Low Power Electronics and Design (ISLPED), Rome, Italy, 22–24 July 2015. [Google Scholar]

- Cambareri, V.; Mangia, M.; Pareschi, F.; Rovatti, R.; Setti, G. Low-complexity multiclass encryption by compressed sensing. IEEE Trans. Signal Process. 2015, 63, 2183–2195. [Google Scholar] [CrossRef]

- Le Gallo, M.; Sebastian, A.; Cherubini, G.; Giefers, H.; Eleftheriou, E. Compressed sensing with approximate message passing using in-memory computing. IEEE Trans. Electron Devices 2018, 65, 4304–4312. [Google Scholar] [CrossRef]

- Qian, F.; Gong, Y.; Wang, L. A memristor-based compressive sampling encoder with dynamic rate control for low-power video streaming. ACM J. Emerg. Technol. Comput. Syst. 2020, 16, 1–16. [Google Scholar] [CrossRef]

- Bao, L.; Wang, Z.; Wang, B.; Liu, K.; Bai, G.; Yu, Z.; Kang, J.; Ling, Y.; Wu, L.; Chen, Q. Tunable Stochastic Oscillator Based on Hybrid VO2/TaOx Device for Compressed Sensing. IEEE Electron Device Lett. 2020, 42, 102–105. [Google Scholar] [CrossRef]

- Wang, R.; Wang, S.; Xin, Y.; Cao, Y.; Liang, Y.; Peng, Y.; Feng, J.; Li, Y.; Lv, L.; Ma, X. All-in-One Compression and Encryption Engine Based on Flexible Polyimide Memristor. Small Sci. 2023. [Google Scholar] [CrossRef]

- Zhang, L.Y.; Wong, K.-W.; Zhang, Y.; Zhou, J. Bi-level protected compressive sampling. IEEE Trans. Multimed. 2016, 18, 1720–1732. [Google Scholar] [CrossRef]

- Bianchi, T.; Bioglio, V.; Magli, E. Analysis of one-time random projections for privacy preserving compressed sensing. IEEE Trans. Inf. Forensics Secur. 2015, 11, 313–327. [Google Scholar] [CrossRef]

- Shannon, C.E. Communication Theory of Secrecy Systems. Bell Syst. Tech. J. 1949, 28, 656–715. [Google Scholar] [CrossRef]

- Rachlin, Y.; Baron, D. The secrecy of compressed sensing measurements. In Proceedings of the 46th Annual Allerton Conference on Communication, Control, and Computing, Monticello, IL, USA, 23–26 September 2008. [Google Scholar]

- Xue, L.; Wang, Y.; Wang, Z. Secure image block compressive sensing using complex Hadamard measurement matrix and bit-level XOR. IET Inf. Secur. 2022, 16, 417–431. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, R.; Zhang, W.; Wang, S.; Zeng, T.; Ma, X.; Wang, H.; Hao, Y. Memristor-Based Signal Processing for Compressed Sensing. Nanomaterials 2023, 13, 1354. https://doi.org/10.3390/nano13081354

Wang R, Zhang W, Wang S, Zeng T, Ma X, Wang H, Hao Y. Memristor-Based Signal Processing for Compressed Sensing. Nanomaterials. 2023; 13(8):1354. https://doi.org/10.3390/nano13081354

Chicago/Turabian StyleWang, Rui, Wanlin Zhang, Saisai Wang, Tonglong Zeng, Xiaohua Ma, Hong Wang, and Yue Hao. 2023. "Memristor-Based Signal Processing for Compressed Sensing" Nanomaterials 13, no. 8: 1354. https://doi.org/10.3390/nano13081354

APA StyleWang, R., Zhang, W., Wang, S., Zeng, T., Ma, X., Wang, H., & Hao, Y. (2023). Memristor-Based Signal Processing for Compressed Sensing. Nanomaterials, 13(8), 1354. https://doi.org/10.3390/nano13081354