Enhancing the Stability and Mobility of TFTs via Indium–Tungsten Oxide and Zinc Oxide Engineered Heterojunction Channels Annealed in Oxygen Ambient

Abstract

:1. Introduction

2. Materials and Methods

2.1. Material Specifications

2.2. AOS Structure and Transistor Fabrication Process

2.3. Characterization Method

3. Results and Discussion

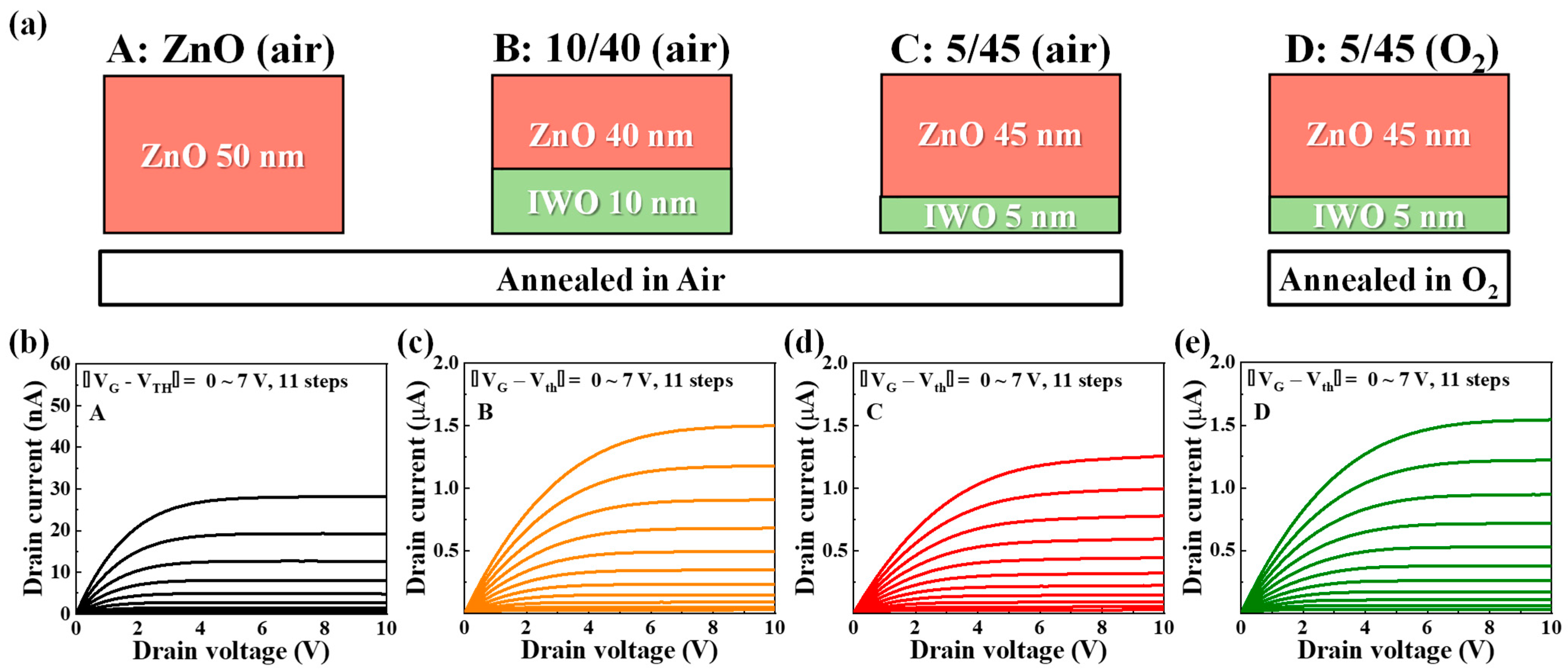

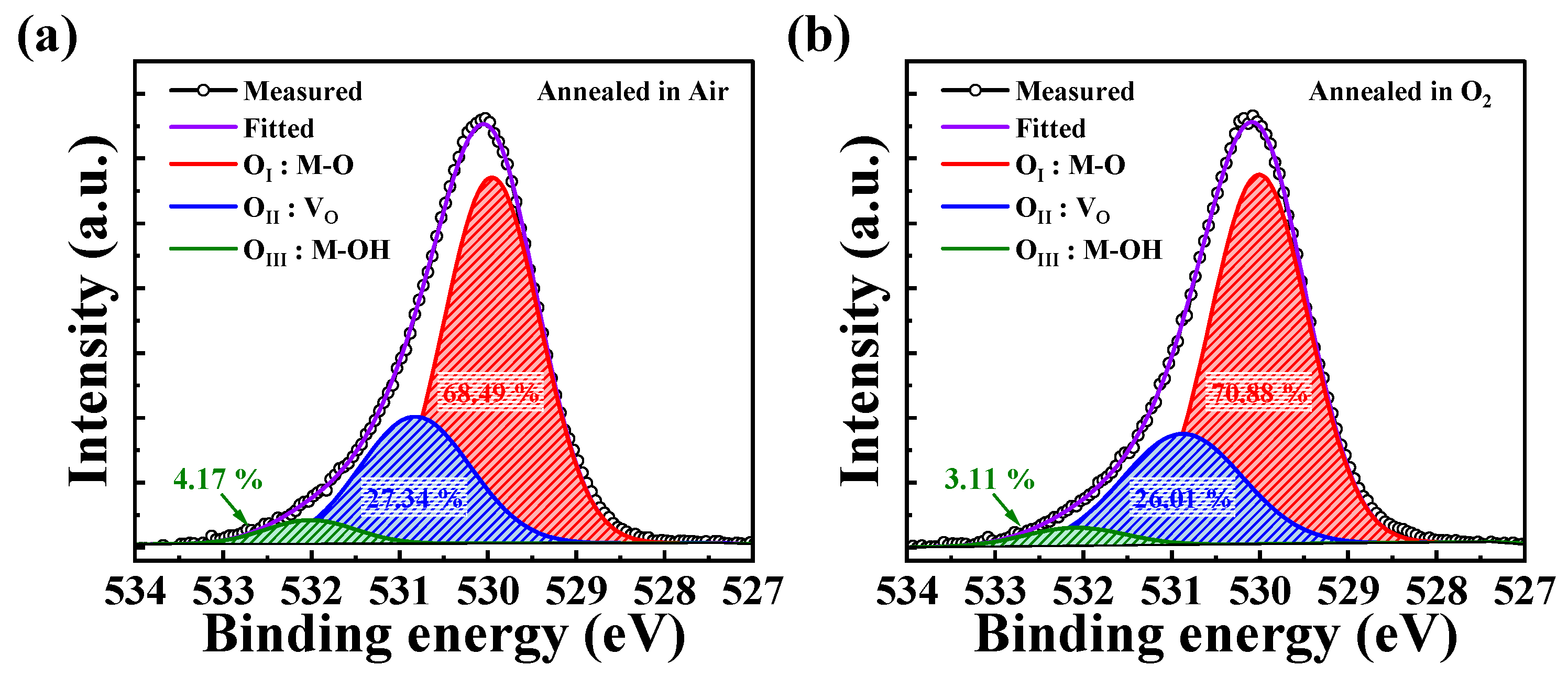

3.1. Improvement in the Electron Mobility of Engineered Heterojunction AOS

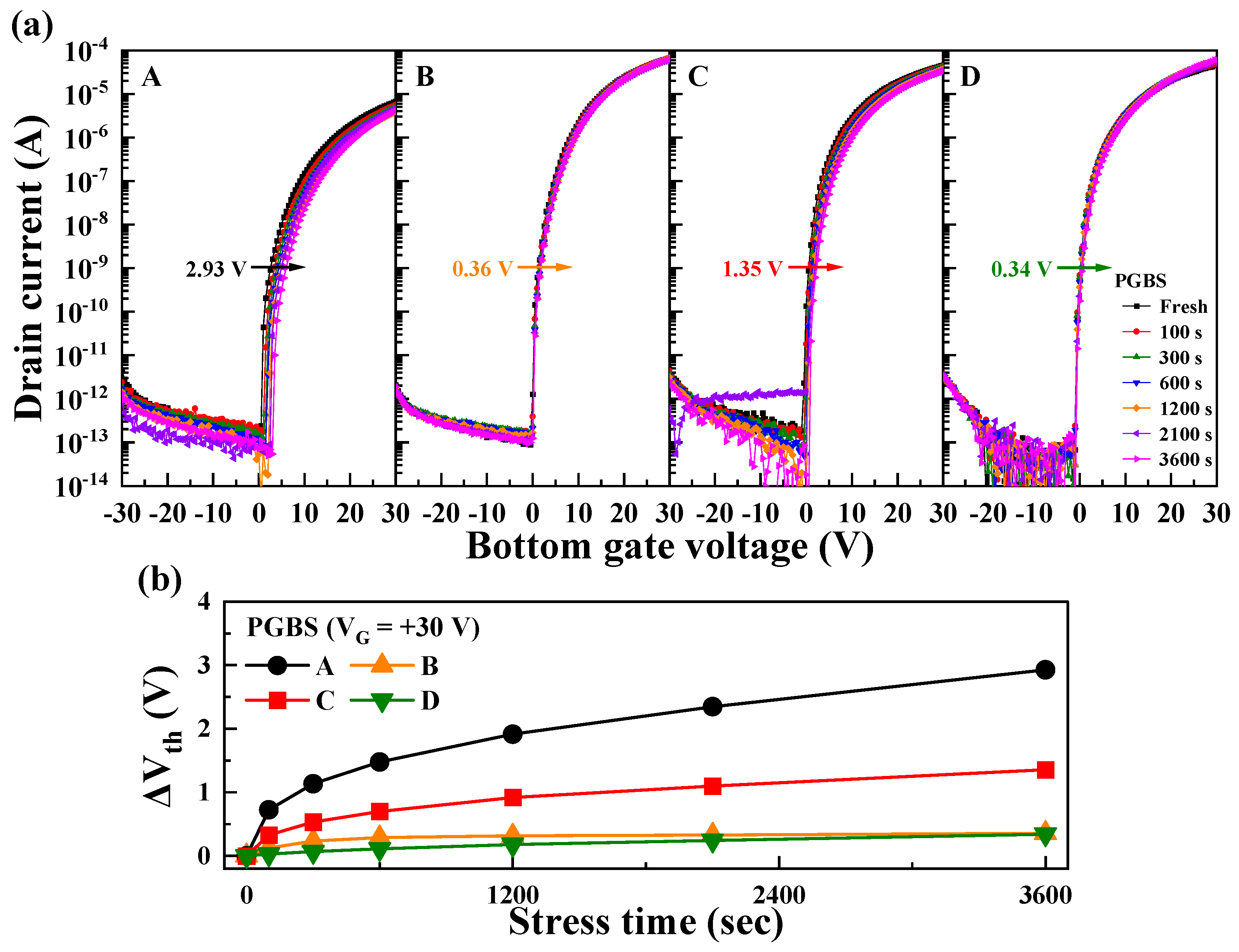

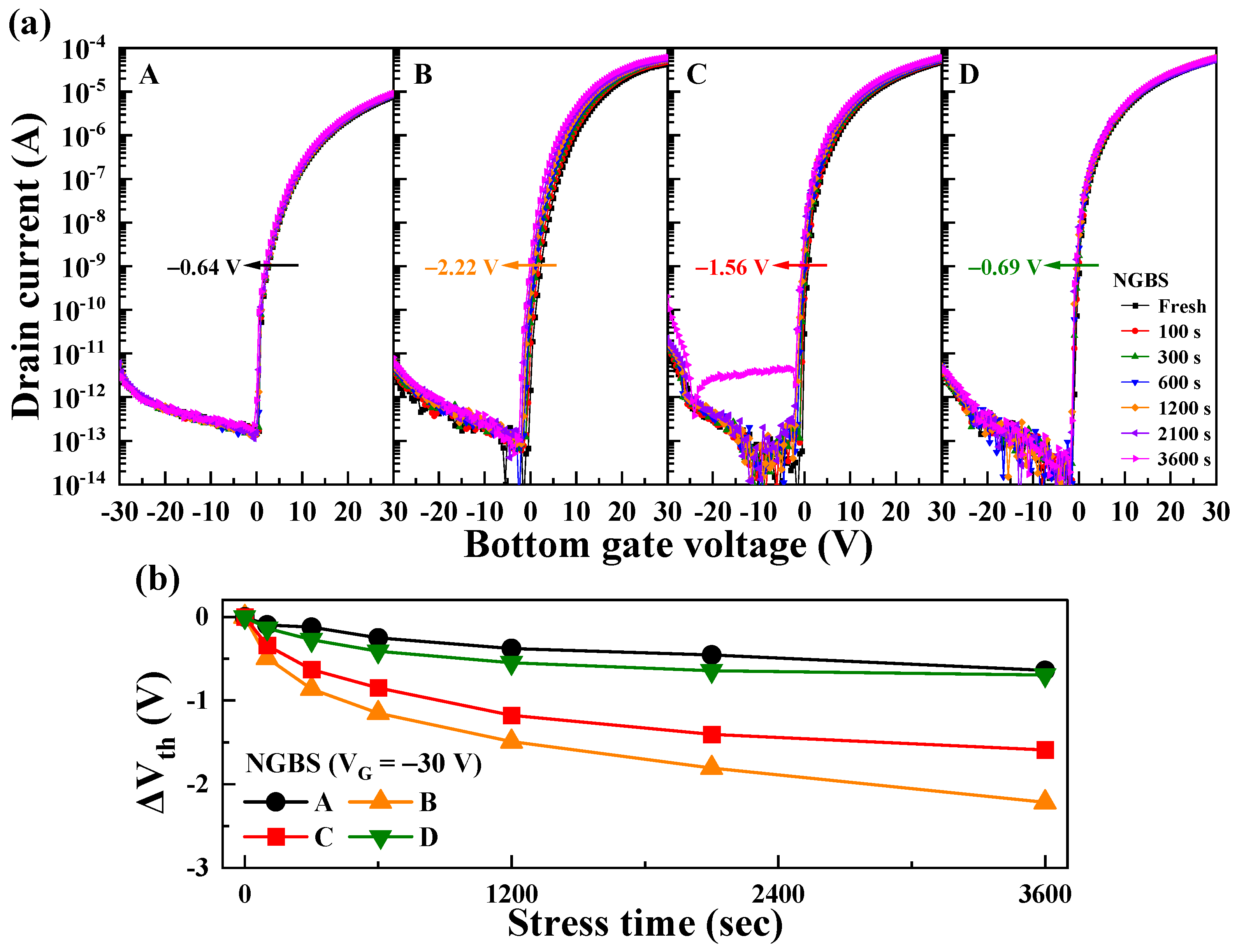

3.2. Stability of Heterojunction AOS under Gate Bias Stress

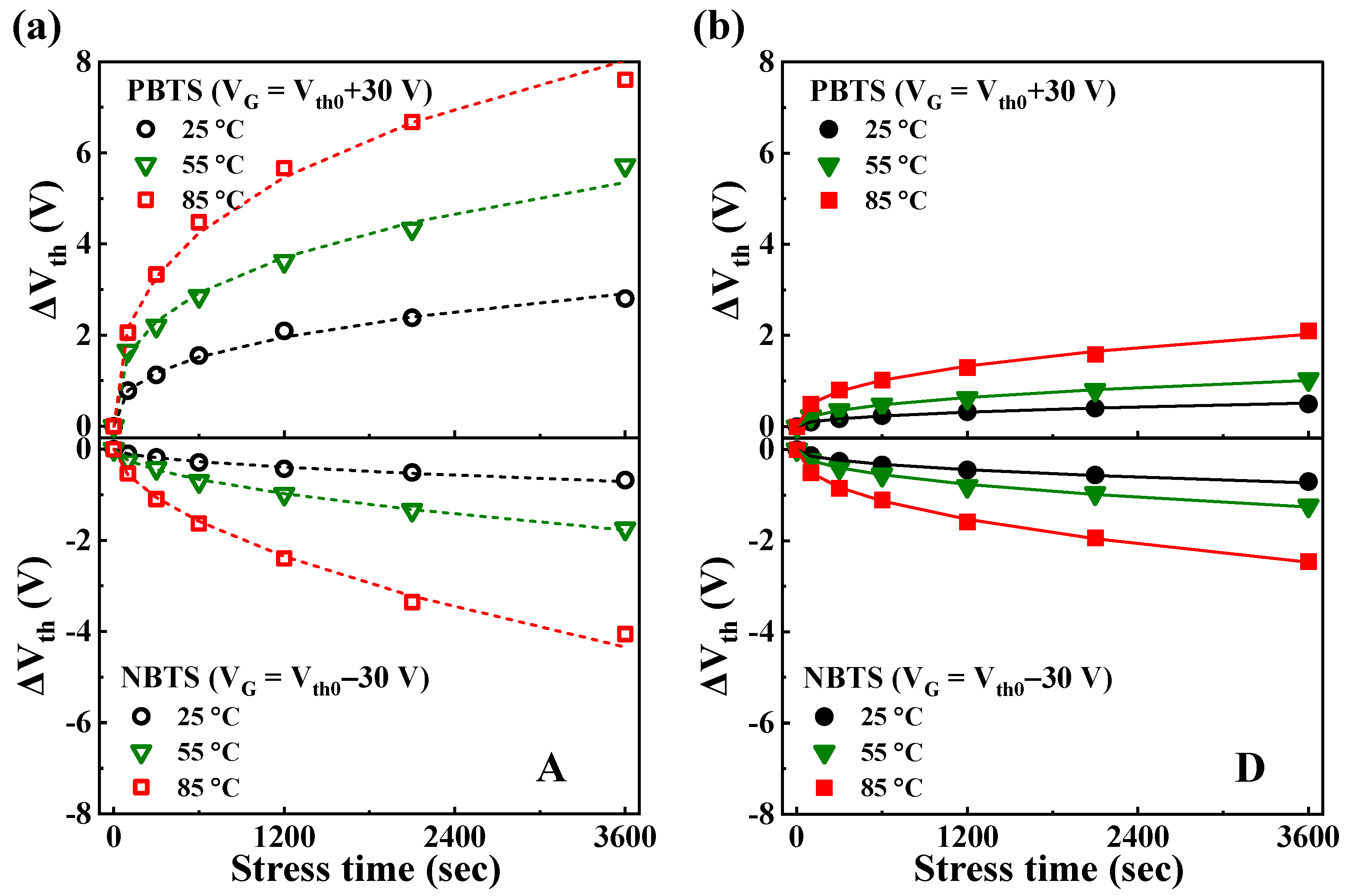

3.3. Reliability Evaluation of Heterojunction Channel under Bias Temperature Stress

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Kamiya, T.; Nomura, K.; Hosono, H. Present status of amorphous in-Ga-Zn-O thin-film transistors. Sci. Technol. Adv. Mater. 2010, 11, 044305. [Google Scholar] [CrossRef] [PubMed]

- Fortunato, E.; Barquinha, P.; Martins, R. Oxide semiconductor thin-film transistors: A review of recent advances. Adv. Mater. 2012, 24, 2945–2986. [Google Scholar] [CrossRef] [PubMed]

- Yabuta, H.; Sano, M.; Abe, K.; Aiba, T.; Den, T.; Kumomi, H.; Nomura, K.; Kamiya, T.; Hosono, H. High-mobility thin-film transistor with amorphous InGaZnO4 channel fabricated by room temperature rf-magnetron sputtering. Appl. Phys. Lett. 2006, 89, 112123. [Google Scholar] [CrossRef]

- Nathan, A.; Lee, S.; Jeon, S.; Robertson, J. Amorphous oxide semiconductor TFTs for displays and imaging. J. Display Technol. 2014, 10, 917–927. [Google Scholar] [CrossRef]

- Petti, L.; Münzenrieder, N.; Vogt, C.; Faber, H.; Büthe, L.; Cantarella, G.; Bottacchi, F.; Anthopoulos, T.D.; Tröster, G. Metal oxide semiconductor thin-film transistors for flexible electronics. Appl. Phys. Rev. 2016, 3, 021303. [Google Scholar] [CrossRef]

- Shi, J.; Zhang, J.; Yang, L.; Qu, M.; Qi, D.C.; Zhang, K.H.L. Wide bandgap oxide semiconductors: From materials physics to optoelectronic devices. Adv. Mater. 2021, 33, e2006230. [Google Scholar] [CrossRef] [PubMed]

- Fortunato, E.M.; Barquinha, P.M.; Pimentel, A.C.M.B.G.; Gonçalves, A.M.; Marques, A.J.; Pereira, L.M.; Martins, R.F. Fully transparent ZnO thin-film transistor produced at room temperature. Adv. Mater. 2005, 17, 590–594. [Google Scholar] [CrossRef]

- Park, S.H.K.; Hwang, C.S.; Ryu, M.; Yang, S.; Byun, C.; Shin, J.; Lee, J.I.; Lee, K.; Oh, M.S.; Im, S. Transparent and Photo-stable ZnO Thin-film Transistors to Drive an Active Matrix Organic-Light- Emitting-Diode Display Panel. Adv. Mater. 2009, 21, 678–682. [Google Scholar] [CrossRef]

- Zhang, L.; Zhang, H.; Bai, Y.; Ma, J.W.; Cao, J.; Jiang, X.; Zhang, Z.L. Enhanced performances of ZnO-TFT by improving surface properties of channel layer. Solid State Commun. 2008, 146, 387–390. [Google Scholar] [CrossRef]

- Chauhan, R.N.; Tiwari, N.; Shieh, H.P.D.; Liu, P.T. Electrical performance and stability of tungsten indium zinc oxide thin-film transistors. Mater. Lett. 2018, 214, 293–296. [Google Scholar] [CrossRef]

- Chauhan, R.N.; Tiwari, N.; Liu, P.T.; Shieh, H.P.D.; Kumar, J. Silicon induced stability and mobility of indium zinc oxide based bilayer thin film transistors. Appl. Phys. Lett. 2016, 109, 202107. [Google Scholar] [CrossRef]

- Choi, J.Y.; Heo, K.; Cho, K.S.; Hwang, S.W.; Chung, J.; Kim, S.; Lee, B.H.; Lee, S.Y. Effect of Si on the energy band gap modulation and performance of silicon indium zinc oxide thin-film transistors. Sci. Rep. 2017, 7, 15392. [Google Scholar] [CrossRef] [PubMed]

- Park, H.W.; Song, A.; Choi, D.; Kim, H.J.; Kwon, J.Y.; Chung, K.B. Enhancement of the device performance and the stability with a homojunction-structured tungsten indium zinc oxide thin film transistor. Sci. Rep. 2017, 7, 11634. [Google Scholar] [CrossRef] [PubMed]

- Park, J.S.; Maeng, W.J.; Kim, H.S.; Park, J.S. Review of recent developments in amorphous oxide semiconductor thin-film transistor devices. Thin Solid Films 2012, 520, 1679–1693. [Google Scholar] [CrossRef]

- Itagaki, N.; Iwasaki, T.; Kumomi, H.; Den, T.; Nomura, K.; Kamiya, T.O.S.H.I.O.; Hosono, H. Zn–In–O based thin-film transistors: Compositional dependence. Phys. Status Solidi (a) 2008, 205, 1915–1919. [Google Scholar] [CrossRef]

- Shiah, Y.S.; Sim, K.; Shi, Y.; Abe, K.; Ueda, S.; Sasase, M.; Kim, J.; Hosono, H. Mobility–stability trade-off in oxide thin-film transistors. Nat. Electron. 2021, 4, 800–807. [Google Scholar] [CrossRef]

- Paine, D.C.; Yaglioglu, B.; Beiley, Z.; Lee, S. Amorphous IZO-based transparent thin film transistors. Thin Solid Films 2008, 516, 5894–5898. [Google Scholar] [CrossRef]

- Lee, E.; Benayad, A.; Shin, T.; Lee, H.; Ko, D.S.; Kim, T.S.; Son, K.S.; Ryu, M.; Jeon, S.; Park, G.S. Nanocrystalline ZnON.; High mobility and low band gap semiconductor material for high performance switch transistor and image sensor application. Sci. Rep. 2014, 4, 4948. [Google Scholar] [CrossRef] [PubMed]

- Lee, B.H.; Sohn, A.; Kim, S.; Lee, S.Y. Mechanism of carrier controllability with metal capping layer on amorphous oxide SiZnSnO semiconductor. Sci. Rep. 2019, 9, 886. [Google Scholar] [CrossRef]

- Zhang, X.; Lee, H.; Kwon, J.H.; Kim, E.J.; Park, J. Low-concentration indium doping in solution-processed zinc oxide films for thin-film transistors. Materials 2017, 10, 880. [Google Scholar] [CrossRef]

- Barquinha, P.; Gonçalves, G.; Pereira, L.; Martins, R.; Fortunato, E. Effect of annealing temperature on the properties of IZO films and IZO based transparent TFTs. Thin Solid Films 2007, 515, 8450–8454. [Google Scholar] [CrossRef]

- Lee, J.; Chung, D.S. Heterojunction oxide thin film transistors: A review of recent advances. J. Mater. Chem. C 2023, 11, 5241–5256. [Google Scholar] [CrossRef]

- Furuta, M.; Koretomo, D.; Magari, Y.; Aman, S.G.M.; Higashi, R.; Hamada, S. Heterojunction channel engineering to enhance performance and reliability of amorphous In–Ga–Zn–O thin-film transistors. Jpn. J. Appl. Phys. 2019, 58, 090604. [Google Scholar] [CrossRef]

- Liang, K.; Wang, Y.; Shao, S.; Luo, M.; Pecunia, V.; Shao, L.; Zhao, J.; Chen, Z.; Mo, L.; Cui, Z. High-performance metal-oxide thin-film transistors based on inkjet-printed self-confined bilayer heterojunction channels. J. Mater. Chem. C 2019, 7, 6169–6177. [Google Scholar] [CrossRef]

- Khim, D.; Lin, Y.H.; Nam, S.; Faber, H.; Tetzner, K.; Li, R.; Zhang, Q.; Li, J.; Zhang, X.; Anthopoulos, T.D. Modulation-doped In2O3/ZnO heterojunction transistors processed from solution. Adv. Mater. 2017, 29, 1605837. [Google Scholar] [CrossRef] [PubMed]

- AlGhamdi, W.S.; Fakieh, A.; Faber, H.; Lin, Y.H.; Lin, W.Z.; Lu, P.Y.; Liu, C.H.; Salama, K.N.; Anthopoulos, T.D. Impact of layer thickness on the operating characteristics of In2O3/ZnO heterojunction thin-film transistors. Appl. Phys. Lett. 2022, 121, 233503. [Google Scholar] [CrossRef]

- Li, Q.; Dong, J.; Han, D.; Wang, Y. Effects of channel thickness on electrical performance and stability of high-performance InSnO Thin-Film Transistors. Membranes 2021, 11, 929. [Google Scholar] [CrossRef] [PubMed]

- Koretomo, D.; Hashimoto, Y.; Hamada, S.; Miyanaga, M.; Furuta, M. Influence of a SiO2 passivation on electrical properties and reliability of In–W–Zn–O thin-film transistor. Jpn. J. Appl. Phys. 2019, 58, 018003. [Google Scholar] [CrossRef]

- Minutolo, P.; Gambi, G.; D’Alessio, A. The optical band gap model in the interpretation of the UV-visible absorption spectra of rich premixed flames. Symp. (Int.) Combust. 1996, 26, 951–957. [Google Scholar] [CrossRef]

- Zhou, X.; Han, D.; Dong, J.; Li, H.; Yi, Z.; Zhang, X.; Wang, Y. The effects of post annealing process on the electrical performance and stability of Al-Zn-O thin-film transistors. IEEE Electron Device Lett. 2020, 41, 569–572. [Google Scholar] [CrossRef]

- Yang, H.; Zhou, X.; Lu, L.; Zhang, S. Investigation to the carrier transport properties in heterojunction-channel amorphous oxides thin-film transistors using dual-gate bias. IEEE Electron Device Lett. 2022, 44, 68–71. [Google Scholar] [CrossRef]

- Rhee, J.; Choi, S.; Kang, H.; Kim, J.Y.; Ko, D.; Ahn, G.; Jung, H.; Choi, S.J.; Myong Kim, D.M.; Kim, D.H. The electron trap parameter extraction-based investigation of the relationship between charge trapping and activation energy in IGZO TFTs under positive bias temperature stress. Solid State Electron. 2018, 140, 90–95. [Google Scholar] [CrossRef]

- Kim, M.H.; Park, J.W.; Lim, J.H.; Choi, D.K. The effect of hydrogen on the device stability of amorphous. InGaZnO Thin-Film Transistors under Positive Bias with Various Temperature Stresses. Phys. Status Solidi (a) 2019, 216, 1900297. [Google Scholar] [CrossRef]

- Chong, E.; Chun, Y.S.; Lee, S.Y. Effect of trap density on the stability of SiInZnO thin-film transistor under temperature and bias-induced stress. Electrochem. Solid-State Lett. 2011, 14, H96. [Google Scholar] [CrossRef]

- Bediako, D.K.; Rezaee, M.; Yoo, H.; Larson, D.T.; Zhao, S.Y.F.; Taniguchi, T.; Watanabe, K.; Brower-Thomas, T.L.; Kaxiras, E.; Kim, P. Heterointerface effects in the electrointercalation of van der Waals heterostructures. Nature 2018, 558, 425–429. [Google Scholar] [CrossRef] [PubMed]

- Ji, X.; Yuan, Y.; Yin, X.; Yan, S.; Xin, Q.; Song, A. High-performance thin-film transistors with sputtered IGZO/Ga₂O₃ Heterojunction. IEEE Trans. Electron Devices 2022, 69, 6783–6788. [Google Scholar] [CrossRef]

- Kim, H.; Gilmore, C.M.; Piqué, A.; Horwitz, J.S.; Mattoussi, H.; Murata, H.; Kafafi, Z.H.; Chrisey, D.B. Electrical, optical, and structural properties of indium-tin-oxide thin films for organic light-emitting devices. J. Appl. Phys. 1999, 86, 6451–6461. [Google Scholar] [CrossRef]

- Tauc, J.; Grigorovici, R.; Vancu, A. Optical properties and electronic structure of amorphous germanium. Phys. Status Solidi (b) 1966, 15, 627–637. [Google Scholar] [CrossRef]

- Lee, M.; Jo, J.W.; Kim, Y.J.; Choi, S.; Kwon, S.M.; Jeon, S.P.; Facchetti, A.; Kim, Y.H.; Park, S.K. Corrugated heterojunction metal-oxide thin-film transistors with high electron mobility via vertical interface manipulation. Adv. Mater. 2018, 30, e1804120. [Google Scholar] [CrossRef] [PubMed]

- Khim, D.; Lin, Y.H.; Anthopoulos, T.D. Impact of layer configuration and doping on electron transport and bias stability in heterojunction and superlattice metal oxide transistors. Adv. Funct. Mater. 2019, 29, 1902591. [Google Scholar] [CrossRef]

- Li, Z.; Hao, Y.; Zhang, C.; Xu, Y.; Zhang, J.; Cheng, Y.; Chen, D.; Feng, Q.; Xu, S.; Zhang, Y.; et al. Flexible solar-blind Ga2O3 ultraviolet photodetectors with high responsivity and photo-to-dark current ratio. IEEE Photonics J. 2019, 11, 6803709. [Google Scholar] [CrossRef]

- Faber, H.; Das, S.; Lin, Y.H.; Pliatsikas, N.; Zhao, K.; Kehagias, T.; Dimitrakopulos, G.; Amassian, A.; Patsalas, P.A.; Anthopoulos, T.D. Heterojunction oxide thin-film transistors with unprecedented electron mobility grown from solution. Sci. Adv. 2017, 3, e1602640. [Google Scholar] [CrossRef] [PubMed]

- Lin, Y.H.; Faber, H.; Labram, J.G.; Stratakis, E.; Sygellou, L.; Kymakis, E.; Hastas, N.A.; Li, R.; Zhao, K.; Amassian, A.; et al. High Electron mobility thin-film transistors based on solution-processed semiconducting metal oxide heterojunctions and quasi-superlattices. Adv. Sci. 2015, 2, 1500058. [Google Scholar] [CrossRef] [PubMed]

- Wang, B.S.; Li, Y.S.; Cheng, I.C. Mobility enhancement in RF-sputtered MgZnO/ZnO heterostructure thin-film transistors. IEEE Trans. Electron Devices 2016, 63, 1545–1549. [Google Scholar] [CrossRef]

- Kwon, S.; Bang, S.; Lee, S.; Jeon, S.; Jeong, W.; Kim, H.; Gong, S.C.; Chang, H.J.; Park, H.H.; Jeon, H. Characteristics of the ZnO thin film transistor by atomic layer deposition at various temperatures. Semicond. Sci. Technol. 2009, 24, 035015. [Google Scholar] [CrossRef]

- Conley, J.F. Instabilities in amorphous oxide semiconductor thin-film transistors. IEEE Trans. Device Mater. Reliab. 2010, 10, 460–475. [Google Scholar] [CrossRef]

- Cho, I.T.; Lee, J.M.; Lee, J.H.; Kwon, H.I. Charge trapping and detrapping characteristics in amorphous. InGaZnO TFTs under static and dynamic stresses. Semicond. Sci. Technol. 2008, 24, 015013. [Google Scholar] [CrossRef]

- Powell, M.J. The physics of amorphous-silicon thin-film transistors. IEEE Trans. Electron Devices 1989, 36, 2753–2763. [Google Scholar] [CrossRef]

- Park, J.; Rim, Y.S.; Li, C.; Wu, J.; Goorsky, M.; Streit, D. Defect-induced instability mechanisms of sputtered amorphous indium tin zinc oxide thin-film transistors. J. Appl. Phys. 2018, 123, 161568. [Google Scholar] [CrossRef]

- Jeong, J.K. Photo-bias instability of metal oxide thin film transistors for advanced active matrix displays. J. Mater. Res. 2013, 28, 2071–2084. [Google Scholar] [CrossRef]

- Kim, Y.; Kim, S.; Kim, W.; Bae, M.; Jeong, H.K.; Kong, D.; Choi, S.; Kim, D.M.; Kim, D.H. Amorphous InGaZnO Thin-Film Transistors—Part II: Modeling and Simulation of Negative Bias Illumination Stress-Induced Instability. IEEE Trans. Electron Devices 2012, 59, 2699–2706. [Google Scholar] [CrossRef]

- Chen, X.; Wan, J.; Wu, H.; Liu, C. ZnO bilayer thin film transistors using H2O and O3 as oxidants by atomic layer deposition. Acta Mater. 2020, 185, 204–210. [Google Scholar] [CrossRef]

- Park, B.; Nam, S.; Kang, Y.; Jeon, S.P.; Jo, J.W.; Park, S.K.; Kim, Y.H. Cation doping strategy for improved carrier mobility and stability in metal-oxide Heterojunction thin-film transistors. Mater. Today Electron. 2024, 8, 100090. [Google Scholar] [CrossRef]

- Seul, H.J.; Cho, J.H.; Hur, J.S.; Cho, M.H.; Cho, M.H.; Ryu, M.T.; Jeong, J.K. Improvement in carrier mobility through band-gap engineering in atomic-layer-deposited In-Ga-Zn-O stacks. J. Alloys Compd. 2022, 903, 163876. [Google Scholar] [CrossRef]

- Yao, J.; Xu, N.; Deng, S.; Chen, J.; She, J.; Shieh, H.D.; Liu, P.T.; Huang, Y.P. Electrical and photosensitive characteristics of a-IGZO TFTs related to oxygen vacancy. IEEE Trans. Electron Devices 2011, 58, 1121–1126. [Google Scholar] [CrossRef]

- Bukke, R.N.; Avis, C.; Jang, J. Solution-processed amorphous In–Zn–Sn oxide thin-film transistor performance improvement by solution-processed Y2O3 passivation. IEEE Electron Device Lett. 2016, 37, 433–436. [Google Scholar] [CrossRef]

- Mude, N.N.; Bukke, R.N.; Saha, J.K.; Avis, C.; Jang, J. Highly stable, solution-processed Ga-doped IZTO thin film transistor by Ar/O2 plasma treatment. Adv. Electron. Mater. 2019, 5, 1900768. [Google Scholar] [CrossRef]

- Li, L.; Xu, Y.; Wang, Q.; Nakamura, R.; Jiang, Y.; Ao, J.P. Metal-oxide-semiconductor AlGaN/GaN heterostructure field-effect transistors using TiN/AlO stack gate layer deposited by reactive sputtering. Semicond. Sci. Technol. 2015, 30, 015019. [Google Scholar] [CrossRef]

- Han, C.H.; Kim, S.S.; Kim, K.R.; Baek, D.H.; Kim, S.S.; Choi, B.D. Effects of electron trapping and interface state generation on bias stress induced in indium–gallium–zinc oxide thin-film transistors. Jpn. J. Appl. Phys. 2014, 53, 08NG04. [Google Scholar] [CrossRef]

- Zafar, S.; Callegari, A.; Gusev, E.; Fischetti, M.V. Charge trapping related threshold voltage instabilities in high permittivity gate dielectric stacks. J. Appl. Phys. 2003, 93, 9298–9303. [Google Scholar] [CrossRef]

- Suresh, A.; Muth, J.F. Bias stress stability of indium gallium zinc oxide channel based transparent thin film transistors. Appl. Phys. Lett. 2008, 92, 033502. [Google Scholar] [CrossRef]

- Qiang, L.; Liang, X.; Pei, Y.; Yao, R.; Wang, G. Extraction method of trap densities for indium zinc oxide thin-film transistors processed by solution method. Thin Solid Films 2018, 649, 51–56. [Google Scholar] [CrossRef]

- Nomura, K.; Kamiya, T.; Hirano, M.; Hosono, H. Origins of threshold voltage shifts in room-temperature deposited and annealed a-In–Ga–Zn–O thin-film transistors. Appl. Phys. Lett. 2009, 95, 013502. [Google Scholar] [CrossRef]

- Han, J.; Abliz, A.; Wan, D. Impact of hydrogen plasma treatment on the electrical performances of ZnO thin-film transistors. Chin. J. Phys. 2022, 77, 327–334. [Google Scholar] [CrossRef]

- Zhang, L.; Li, J.; Zhang, X.W.; Yu, D.B.; Lin, H.P.; Jiang, X.Y.; Zhang, Z.L. The influence of the SiO2 deposition condition on the ZnO thin-film transistor performance. Superlattices Microstruct. 2010, 48, 198–205. [Google Scholar] [CrossRef]

- Abliz, A.; Huang, C.W.; Wang, J.; Xu, L.; Liao, L.; Xiao, X.; Wu, W.W.; Fan, Z.; Jiang, C.; Li, J.; et al. Rational design of ZnO: H/ZnO bilayer structure for high-performance thin-film transistors. ACS Appl. Mater. Interfaces 2016, 8, 7862–7868. [Google Scholar] [CrossRef] [PubMed]

- Liu, P.T.; Chang, C.H.; Chang, C.J. Reliability enhancement of high-mobility amorphous indium-tungsten oxide thin film transistor. ECS Trans. 2015, 67, 9. [Google Scholar] [CrossRef]

- Qu, M.; Chang, C.H.; Meng, T.; Zhang, Q.; Liu, P.T.; Shieh, H.P.D. Stability study of indium tungsten oxide thin-film transistors annealed under various ambient conditions. Phys. Status Solidi (a) 2017, 214, 1600465. [Google Scholar] [CrossRef]

- Aikawa, S.; Darmawan, P.; Yanagisawa, K.; Nabatame, T.; Abe, Y.; Tsukagoshi, K. Thin-film transistors fabricated by low-temperature process based on Ga-and Zn-free amorphous oxide semiconductor. Appl. Phys. Lett. 2013, 102, 102101. [Google Scholar] [CrossRef]

| Channel Type (Ambient) | Vth [V] | μFE [cm2/V·s] | S.S [V/dec] | ION/OFF [A/A] |

|---|---|---|---|---|

| ZnO (O2) | −2.65 | 7.14 | 0.72 | 1.61 × 107 |

| [A] ZnO (Air) | 0.48 | 3.80 | 0.27 | 2.04 × 108 |

| 10/40 (O2) | −8.37 | 26.54 | 0.54 | 4.06 × 108 |

| [B] 10/40 (Air) | 0.25 | 28.89 | 0.27 | 5.03 × 108 |

| [C] 5/45 (Air) | 0.19 | 18.24 | 0.20 | 5.61 × 109 |

| [D] 5/45 (O2) | −0.44 | 26.28 | 0.17 | 7.50 × 109 |

| Temperature [°C] | PBTS | NBTS | ||||||

|---|---|---|---|---|---|---|---|---|

| A | D | A | D | |||||

| τ | β | τ | β | τ | β | τ | β | |

| 25 | 1.5 × 106 | 0.38 | 3.2 × 107 | 0.54 | 3.5 × 106 | 0.44 | 1.2 × 107 | 0.46 |

| 55 | 3.2 × 105 | 0.36 | 1.0 × 107 | 0.56 | 5.4 × 105 | 0.43 | 3.0 × 106 | 0.47 |

| 85 | 6.7 × 104 | 0.39 | 3.1 × 106 | 0.58 | 8.2 × 104 | 0.41 | 8.4 × 105 | 0.45 |

| Channel Layer | Gate Insulator /Thickness [nm] | Vth [V] | μFE [cm2/V·s] | S.S [V/dec] | ΔVth under PGBS [V] | ΔVth under NGBS [V] | Ref. |

|---|---|---|---|---|---|---|---|

| ZnO | SiO2/100 | 4.3 ± 0.5 | 11.5 ± 1.3 | 0.65 ± 0.08 | 8.7 ± 0.8 | −9.6 ± 0.9 | [64] |

| ZnO | SiO2/150 | 15 | 8.1 | 1.35 | 3 | N/A | [65] |

| ZnO | SiO2/100 | 4.1 ± 0.6 | 10.5 ± 0.5 | 0.45 ± 0.07 | 2.7 | −3.2 | [66] |

| IWO | SiO2/100 | −3.4 | 36.7 | 0.39 | ≈2.5 | N/A | [67] |

| IWO | SiO2/100 | 0.5 | 27.55 | 0.5 | 4.5 | −0.92 | [68] |

| IWO | SiO2/100 | −0.5 | 21.7 | 0.47 | N/A | N/A | [69] |

| [D] IWO/ZnO | SiO2/100 | −0.44 | 26.28 | 0.17 | 0.34 | −0.97 | This work |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lim, S.-H.; Mah, D.-G.; Cho, W.-J. Enhancing the Stability and Mobility of TFTs via Indium–Tungsten Oxide and Zinc Oxide Engineered Heterojunction Channels Annealed in Oxygen Ambient. Nanomaterials 2024, 14, 1252. https://doi.org/10.3390/nano14151252

Lim S-H, Mah D-G, Cho W-J. Enhancing the Stability and Mobility of TFTs via Indium–Tungsten Oxide and Zinc Oxide Engineered Heterojunction Channels Annealed in Oxygen Ambient. Nanomaterials. 2024; 14(15):1252. https://doi.org/10.3390/nano14151252

Chicago/Turabian StyleLim, Seong-Hwan, Dong-Gyun Mah, and Won-Ju Cho. 2024. "Enhancing the Stability and Mobility of TFTs via Indium–Tungsten Oxide and Zinc Oxide Engineered Heterojunction Channels Annealed in Oxygen Ambient" Nanomaterials 14, no. 15: 1252. https://doi.org/10.3390/nano14151252