Inverter Circuits Using ZnO Nanoparticle Based Thin-Film Transistors for Flexible Electronic Applications

Abstract

:1. Introduction

2. Results and Discussion

2.1. ZnO Stabilization Treatment

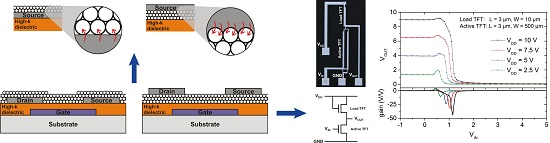

2.2. Transistor Electrical Characteristics

2.3. Inverter Characteristics

3. Materials and Methods

4. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

Abbreviations

| C8-BTBT | 2,7-dioctyl[1]benzothieno[3,2-b]benzothiophene |

| DNTT | Dinaphtho[2,3-b:2′,3′-f]thieno[3,2-b]thiophene |

| NMH | Noise margin for high levels |

| NML | Noise margin for low levels |

| MOSFET | Metal-oxide-semiconductor field-effect transistor |

| RH | Relative humidity |

| TFT | Thin-film transistor |

| UV | Ultra-violet |

| VIH | Inverter circuit input high voltage |

| VIL | Inverter circuit input low voltage |

| VOH | Inverter circuit output high voltage |

| VOL | Inverter circuit output low voltage |

| VON | Turn-on voltage |

| VTC | Voltage transfer characteristic |

References

- Sirringhaus, H. 25th anniversary article: Organic field-effect transistors: The path beyond amorphous silicon. Adv. Mater. 2014, 26, 1319–1335. [Google Scholar] [CrossRef] [PubMed]

- Fortunato, E.; Barquinha, P.; Martins, R. Oxide semiconductor thin-film transistors: A review of recent advances. Adv. Mater. 2012, 24, 2945–2986. [Google Scholar] [CrossRef] [PubMed]

- Vidor, F.; Meyers, T.; Hilleringmann, U. Flexible Electronics: Integration Processes for Organic and Inorganic Semiconductor-Based Thin-Film Transistors. Electronics 2015, 4, 480–506. [Google Scholar] [CrossRef]

- Burroughes, J.H.; Jones, C.A.; Friend, R.H. New semiconductor device physics in polymer diodes and transistors. Nature 1988, 335, 137–141. [Google Scholar] [CrossRef]

- Pannemann, C.; Diekmann, T.; Hilleringmann, U. Degradation of organic field-effect transistors made of pentacene. J. Mater. Res. 2004, 19, 1999–2002. [Google Scholar] [CrossRef]

- Zschieschang, U.; Ante, F.; Kälblein, D.; Yamamoto, T.; Takimiya, K.; Kuwabara, H.; Ikeda, M.; Sekitani, T.; Someya, T.; Nimoth, J.B.; et al. Dinaphtho[2,3-b:2′,3′-f]thieno[3,2-b]thiophene (DNTT) thin-film transistors with improved performance and stability. Org. Electron. 2011, 12, 1370–1375. [Google Scholar] [CrossRef]

- Liu, C.; Minari, T.; Lu, X.; Kumatani, A.; Takimiya, K.; Tsukagoshi, K. Solution-processable organic single crystals with bandlike transport in field-effect transistors. Adv. Mater. 2011, 23, 523–526. [Google Scholar] [CrossRef] [PubMed]

- Jagadish, C.; Pearton, S.J. Zinc Oxide Bulk, Thin Films and Nanostructures. Processing, Properties and Applications; Elsevier: Amsterdam, The Netherlands, 2006. [Google Scholar]

- Fan, Z.; Lu, J.G. Zinc Oxide Nanostructures: Synthesis and Properties. J. Nanosci. Nanotech. 2005, 5, 1561–1573. [Google Scholar] [CrossRef]

- Wang, Z.L. Zinc oxide nanostructures: Growth, properties and applications. J. Phys. Condens. Matter 2004, 16, R829–R858. [Google Scholar] [CrossRef]

- Xu, X.; Feng, L.; He, S.; Jin, Y.; Guo, X. Solution-Processed Zinc Oxide Thin-Film Transistors with a Low-Temperature Polymer Passivation Layer. IEEE Electron Device Lett. 2012, 33, 1420–1422. [Google Scholar] [CrossRef]

- Conley, J.F. Instabilities in Amorphous Oxide Semiconductor Thin-Film Transistors. IEEE Trans. Device Mater. Relib. 2010, 10, 460–475. [Google Scholar] [CrossRef]

- Vidor, F.F.; Wirth, G.; Assion, F.; Wolff, K.; Hilleringmann, U. Characterization and Analysis of the Hysteresis in a ZnO Nanoparticle Thin-Film Transistor. IEEE Trans. Nanotechnol. 2013, 12, 296–303. [Google Scholar] [CrossRef]

- Hong, D.; Yerubandi, G.; Chiang, H.Q.; Spiegelberg, M.C.; Wager, J.F. Electrical Modeling of Thin-Film Transistors. Crit. Rev. Solid State Mater. Sci. 2008, 33, 101–132. [Google Scholar] [CrossRef]

- Okamura, K.; Mechau, N.; Nikolova, D.; Hahn, H. Influence of interface roughness on the performance of nanoparticulate zinc oxide field-effect transistors. Appl. Phys. Lett. 2008, 93. [Google Scholar] [CrossRef]

- Faber, H.; Burkhardt, M.; Jedaa, A.; Kälblein, D.; Klauk, H.; Halik, M. Low-Temperature Solution-Processed Memory Transistors Based on Zinc Oxide Nanoparticles. Adv. Mater. 2009, 21, 3099–3104. [Google Scholar] [CrossRef]

- Vidor, F.F.; Meyers, T.; Wirth, G.I.; Hilleringmann, U. ZnO nanoparticle thin-film transistors on flexible substrate using spray-coating technique. Microelectron. Eng. 2016, 159, 155–158. [Google Scholar] [CrossRef]

- Xu, J.; Pan, Q.; Shun, Y.; Tian, Z. Grain size control and gas sensing properties of ZnO gas sensor. Sens. Actuators B 2000, 66, 277–279. [Google Scholar] [CrossRef]

- Jin, Y.; Wang, J.; Sun, B.; Blakesley, J.C.; Greenham, N.C. Solution-Processed Ultraviolet Photodetectors Based on Colloidal ZnO Nanoparticles. Nano Lett. 2008, 8, 1649–1653. [Google Scholar] [CrossRef] [PubMed]

- Li, Y.; Della Valle, F.; Simonnet, M.; Yamada, I.; Delaunay, J. Competitive surface effects of oxygen and water on UV photoresponse of ZnO nanowires. Appl. Phys. Lett. 2009, 94. [Google Scholar] [CrossRef]

- Hirschwald, W.H. Zinc oxide: An outstanding example of a binary compound semiconductor. Acc. Chem. Res. 1985, 18, 228–234. [Google Scholar] [CrossRef]

- Morrison, S. Semiconductor gas sensors. Sens. Actuators 1981, 2, 329–341. [Google Scholar] [CrossRef]

- Vidor, F.F.; Meyers, T.; Hilleringmann, U.; Wirth, G.I. Influence of UV irradiation and humidity on a low-cost ZnO nanoparticle TFT for flexible electronics. In Proceedings of the 2015 IEEE 15th International Conference on Nanotechnology (IEEE-NANO), Rome, Italy, 27–30 July 2015; pp. 1179–1181.

- Vidor, F.F.; Wirth, G.I.; Hilleringmann, U. Low temperature fabrication of a ZnO nanoparticle thin-film transistor suitable for flexible electronics. Microelectron. Reliab. 2014, 54, 2760–2765. [Google Scholar] [CrossRef]

- Vidor, F.F.; Meyers, T.; Hilleringmann, U. Low-Cost Treatment for Flexible Electronics. In Proceedings of the Smart Systems Integration Conference, Munich, Germany, 9–10 March 2016; pp. 477–480.

- Gonçalves, G.; Pimentel, A.; Fortunato, E.; Martins, R.; Queiroz, E.L.; Bianchi, R.F.; Faria, R.M. UV and ozone influence on the conductivity of ZnO thin films. J. Non-Cryst. Solids 2006, 352, 1444–1447. [Google Scholar] [CrossRef]

- Wu, J.-L.; Lin, H.-Y.; Kuo, P.-H.; Su, B.-Y.; Chu, S.-Y.; Chen, Y.-C.; Liu, S.-Y.; Chang, C.-C.; Wu, C.-J. Effect of UV-Ozone Treatment on the Performance of ZnO TFTs Fabricated by RF Sputtering Deposition Technique. IEEE Trans. Electron Devices 2014, 61, 1403–1409. [Google Scholar]

- Lee, S.; Jeong, Y.; Jeong, S.; Lee, J.; Jeon, M.; Moon, J. Solution-processed ZnO nanoparticle-based semiconductor oxide thin-film transistors. Superlattices Microstruct. 2008, 44, 761–769. [Google Scholar] [CrossRef]

- Pan, H.; Misra, N.; Ko, S.H.; Grigoropoulos, C.P.; Miller, N.; Haller, E.E.; Dubon, O. Melt-mediated coalescence of solution-deposited ZnO nanoparticles by excimer laser annealing for thin-film transistor fabrication. Appl. Phys. A 2009, 94, 111–115. [Google Scholar] [CrossRef]

- Lee, D.; Pan, H.; Ko, S.H.; Park, H.K.; Kim, E.; Grigoropoulos, C.P. Non-vacuum, single-step conductive transparent ZnO patterning by ultra-short pulsed laser annealing of solution-deposited nanoparticles. Appl. Phys. A 2012, 107, 161–171. [Google Scholar] [CrossRef]

- Hoffman, R.L. ZnO-channel thin-film transistors: Channel mobility. J. Appl. Phys. 2004, 95. [Google Scholar] [CrossRef]

- Pesavento, P.V.; Chesterfield, R.J.; Newman, C.R.; Frisbie, C.D. Gated four-probe measurements on pentacene thin-film transistors: Contact resistance as a function of gate voltage and temperature. J. Appl. Phys. 2004, 96. [Google Scholar] [CrossRef]

- Verbakel, F.; Meskers, S.C.J.; Janssen, R.A.J. Electronic memory effects in diodes of zinc oxide nanoparticles in a matrix of polystyrene or poly(3-hexylthiophene). J. Appl. Phys. 2007, 102. [Google Scholar] [CrossRef]

- Meulenkamp, E.A. Electron Transport in Nanoparticulate ZnO Films. J. Phys. Chem. B 1999, 103, 7831–7838. [Google Scholar] [CrossRef]

- Martins, R.; Barquinha, P.; Ferreira, I.; Pereira, L.; Gonçalves, G.; Fortunato, E. Role of order and disorder on the electronic performances of oxide semiconductor thin film transistors. J. Appl. Phys. 2007, 101. [Google Scholar] [CrossRef]

- Ko, S.H.; Park, I.; Pan, H.; Misra, N.; Rogers, M.S.; Grigoropoulos, C.P.; Pisano, A.P. ZnO nanowire network transistor fabrication on a polymer substrate by low-temperature, all-inorganic nanoparticle solution process. Appl. Phys. Lett. 2008, 92. [Google Scholar] [CrossRef]

- Kwon, J.; Hong, S.; Lee, H.; Yeo, J.; Lee, S.S.; Ko, S.H. Direct selective growth of ZnO nanowire arrays from inkjet-printed zinc acetate precursor on a heated substrate. Nanoscale Res. Lett. 2013, 8. [Google Scholar] [CrossRef] [PubMed]

- Faber, H.; Hirschmann, J.; Klaumunzer, M.; Braunschweig, B.; Peukert, W.; Halik, M. Impact of oxygen plasma treatment on the device performance of zinc oxide nanoparticle-based thin-film transistors. ACS Appl. Mater. Interfaces 2012, 4, 1693–1696. [Google Scholar] [CrossRef] [PubMed]

- Cho, S.Y.; Kang, Y.H.; Jung, J.-Y.; Nam, S.Y.; Lim, J.; Yoon, S.C.; Choi, D.H.; Lee, C. Novel Zinc Oxide Inks with Zinc Oxide Nanoparticles for Low-Temperature, Solution-Processed Thin-Film Transistors. Chem. Mater. 2012, 24, 3517–3524. [Google Scholar] [CrossRef]

- Park, S.Y.; Kim, B.J.; Kim, K.; Kang, M.S.; Lim, K.-H.; Lee, T.I.; Myoung, J.M.; Baik, H.K.; Cho, J.H.; Kim, Y.S. Low-Temperature, solution-processed and alkali metal doped ZnO for high-performance thin-film transistors. Adv. Mater. 2012, 24, 834–838. [Google Scholar] [CrossRef] [PubMed]

- Meyers, S.T.; Anderson, J.T.; Hung, C.M.; Thompson, J.; Wager, J.F.; Keszler, D.A. Aqueous inorganic inks for low-temperature fabrication of ZnO TFTs. J. Am. Chem. Soc. 2008, 130, 17603–17609. [Google Scholar] [CrossRef] [PubMed]

- Theissmann, R.; Bubel, S.; Sanlialp, M.; Busch, C.; Schierning, G.; Schmechel, R. High performance low temperature solution-processed zinc oxide thin film transistor. Thin Solid Films 2011, 519, 5623–5628. [Google Scholar] [CrossRef]

- Barquinha, P.; Pereira, L.; Gonçalves, G.; Martins, R.; Fortunato, E. Toward High-Performance Amorphous GIZO TFTs. J. Electrochem. Soc. 2009, 156. [Google Scholar] [CrossRef]

- Fortunato, E.; Pimentel, A.; Pereira, L.; Gonçalves, A.; Lavareda, G.; Águas, H.; Ferreira, I.; Carvalho, C.N.; Martins, R. High field-effect mobility zinc oxide thin film transistors produced at room temperature. J. Non-Cryst. Solids 2004, 338–340, 806–809. [Google Scholar] [CrossRef]

- Lim, S.J.; Kwon, S.-J.; Kim, H.; Park, J.-S. High performance thin film transistor with low temperature atomic layer deposition nitrogen-doped ZnO. Appl. Phys. Lett. 2007, 91. [Google Scholar] [CrossRef]

- Huang, T.-C.; Fukuda, K.; Lo, C.-M.; Yeh, Y.-H.; Sekitani, T.; Someya, T.; Cheng, K.-T. Pseudo-CMOS: A Design Style for Low-Cost and Robust Flexible Electronics. IEEE Trans. Electron Devices 2011, 58, 141–150. [Google Scholar] [CrossRef]

- Ofuji, M.; Abe, K.; Shimizu, H.; Kaji, N.; Hayashi, R.; Sano, M.; Kumomi, H.; Nomura, K.; Kamiya, T.; Hosono, H. Fast Thin-Film Transistor Circuits Based on Amorphous Oxide Semiconductor. IEEE Electron Device Lett. 2007, 28, 273–275. [Google Scholar] [CrossRef]

- Myny, K.; Smout, S.; Rockele, M.; Bhoolokam, A.; Ke, T.H.; Steudel, S.; Cobb, B.; Gulati, A.; Gonzalez Rodriguez, F.; Obata, K.; et al. A thin-film microprocessor with inkjet print-programmable memory. Sci. Rep. 2014, 4. [Google Scholar] [CrossRef]

- Diekmann, T.; Pannemann, C.; Hilleringmann, U. Dielectric layers for organic field effect transistors as gate dielectric and surface passivation. Phys. Stat. Sol. (A) 2008, 205, 564–577. [Google Scholar] [CrossRef]

- Inomat GmbH. Datasheet: InoFlex T3; Inomat GmbH: Neunkirchen, Germany, 2015. [Google Scholar]

- Nanophase Technologies Corporation. Datasheet: ZN-3014; Nanophase Technologies Corporation: Romeoville, IL, USA, 2016. [Google Scholar]

© 2016 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC-BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Vidor, F.F.; Meyers, T.; Hilleringmann, U. Inverter Circuits Using ZnO Nanoparticle Based Thin-Film Transistors for Flexible Electronic Applications. Nanomaterials 2016, 6, 154. https://doi.org/10.3390/nano6090154

Vidor FF, Meyers T, Hilleringmann U. Inverter Circuits Using ZnO Nanoparticle Based Thin-Film Transistors for Flexible Electronic Applications. Nanomaterials. 2016; 6(9):154. https://doi.org/10.3390/nano6090154

Chicago/Turabian StyleVidor, Fábio F., Thorsten Meyers, and Ulrich Hilleringmann. 2016. "Inverter Circuits Using ZnO Nanoparticle Based Thin-Film Transistors for Flexible Electronic Applications" Nanomaterials 6, no. 9: 154. https://doi.org/10.3390/nano6090154

APA StyleVidor, F. F., Meyers, T., & Hilleringmann, U. (2016). Inverter Circuits Using ZnO Nanoparticle Based Thin-Film Transistors for Flexible Electronic Applications. Nanomaterials, 6(9), 154. https://doi.org/10.3390/nano6090154