Low-Temperature Bonding for Silicon-Based Micro-Optical Systems

Abstract

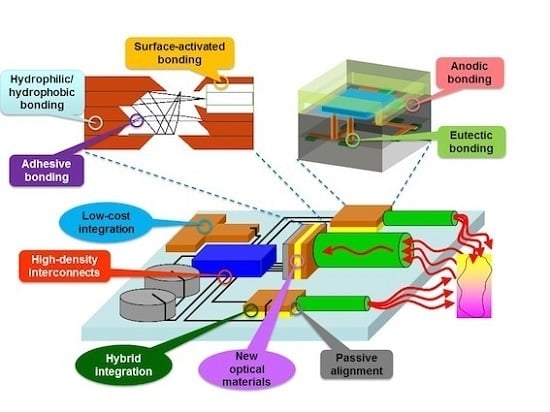

:1. Introduction

2. Electrical and Optical Interfaces in Micro-Optical Systems

2.1. Electrical and Optical Interfaces

2.1.1. Electrical Interconnects

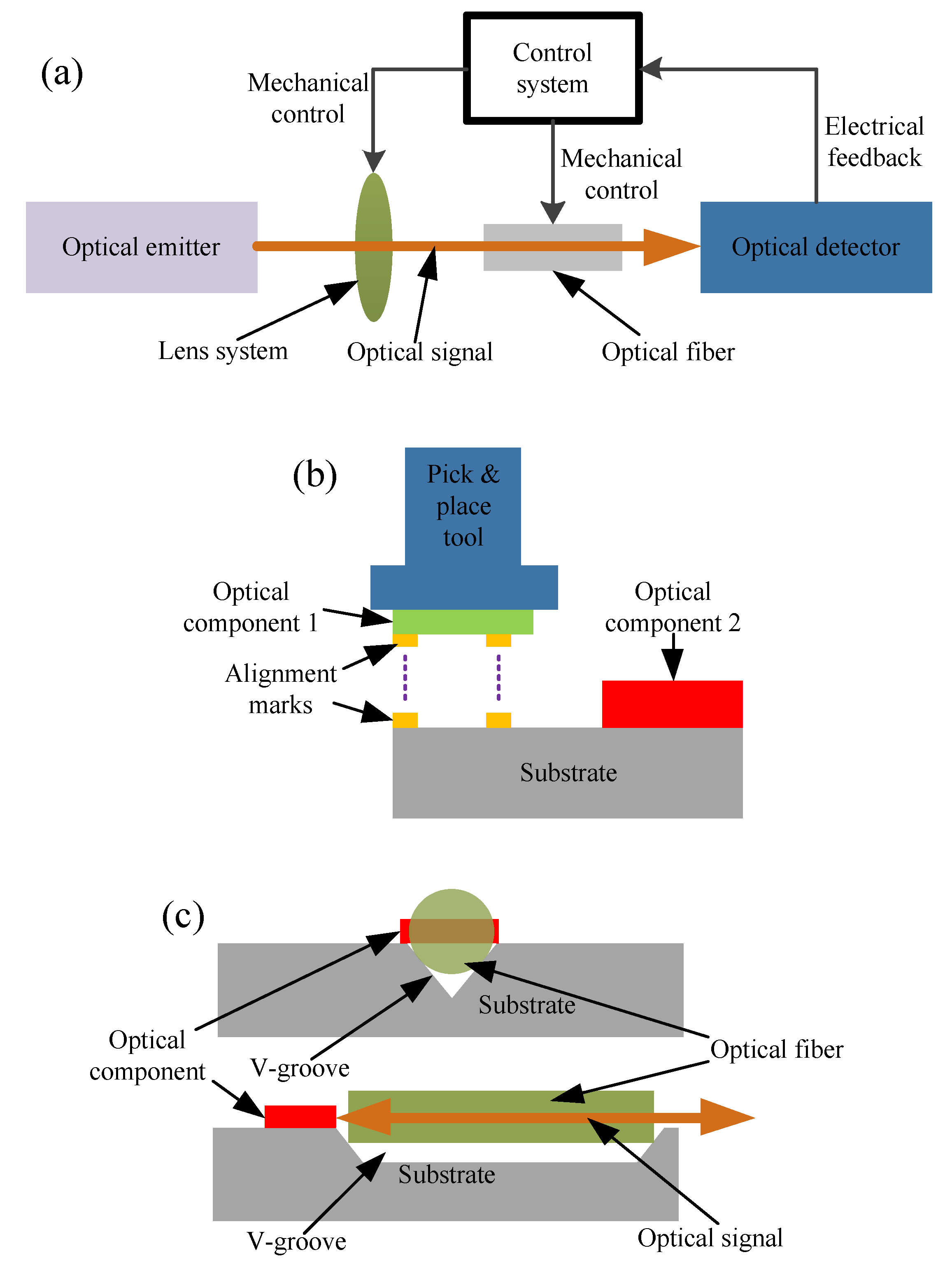

2.1.2. Optical Coupling

2.2. Wafer Bonding for Electrical and Optical Interfaces

3. Low-Temperature Wafer Bonding Technologies

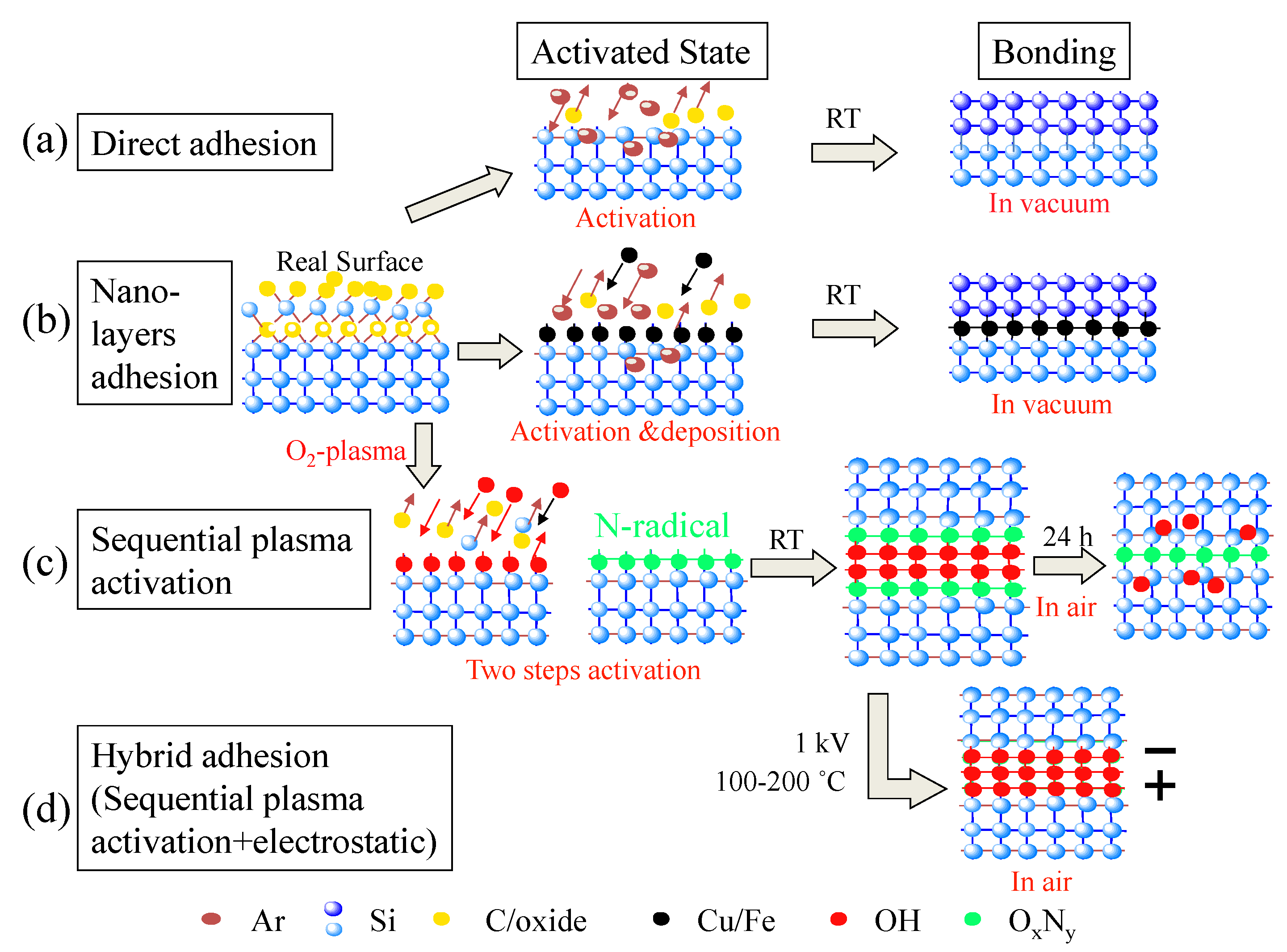

3.1. Direct Bonding without Intermediate Layers

3.1.1. Anodic Bonding

3.1.2. Hydrophilic and Hydrophobic Bonding

3.1.3. Surface Activated Bonding

3.1.4. Other Direct Bonding Technologies

3.2. Indirect Bonding with Intermediate Layers

3.2.1. Adhesive Bonding

3.2.2. Eutectic Bonding

3.2.3. Surface Activated Bonding with Nanoadhesion Layers

4. Future Assembly of Optical Systems

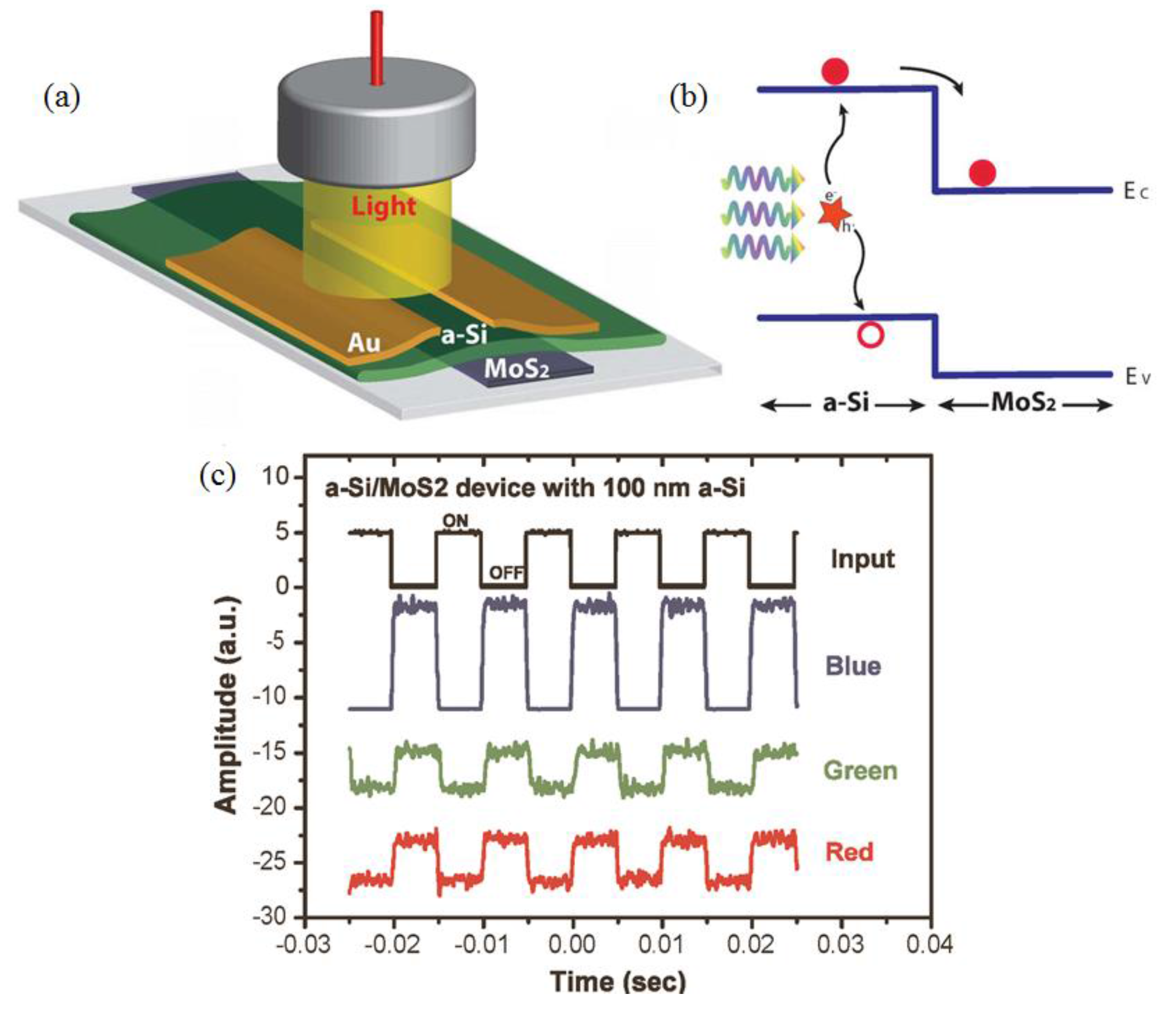

4.1. New Materials

4.2. Advanced Assembly Concepts

4.2.1. Monolithic Integration

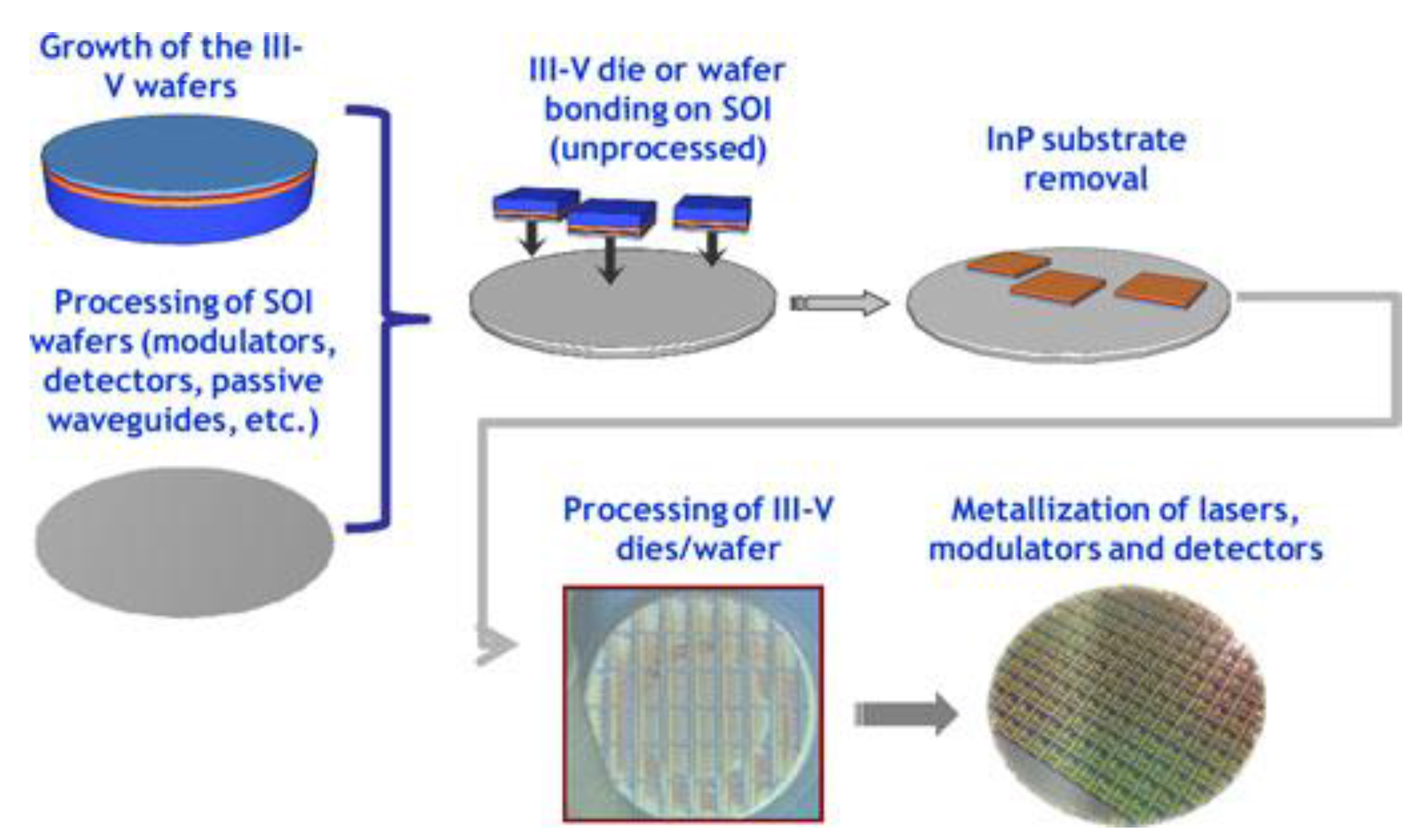

4.2.2. Hybrid Integration

4.3. Cost Reduction Approaches

4.4. Prospected Systems

5. Conclusions

Acknowledgments

Conflicts of Interest

References

- Haes, A.J.; Chang, L.; Klein, W.L.; van Duyne, R.P. Detection of a biomarker for Alzheimer’s disease from synthetic and clinical samples using a nanoscale optical biosensor. J. Am. Chem. Soc. 2005, 127, 2264–2271. [Google Scholar] [CrossRef] [PubMed]

- Zhao, W.; Yao, S.; Hsing, I. A microsystem compatible strategy for viable Escherichia coli detection. Bios. Bioelectron. 2006, 21, 1163–1170. [Google Scholar] [CrossRef] [PubMed]

- Miller, D.A.B. Device requirements for optical interconnects to silicon chips. IEEE Proc. 2009, 97, 1166–1185. [Google Scholar] [CrossRef]

- Burlacu, D.; Nguyen, L.; Kivilahti, J. Influence of Solder Microstructure and Oxide Layers on High Frequency Electrical Losses of WL-CSP Pb-Free Interconnections. In Proceedings of IEEE 56th Electronic Components and Technology Conference, San Diego, CA, USA, 30 May–2 June 2006; pp. 577–583.

- Nemoto, S.; Makimoto, T. Analysis of splice loss in single-mode fibres using a Gaussian field approximation. Opt. Quantum Electron. 1979, 11, 447–457. [Google Scholar] [CrossRef]

- Yoon, S.W.; Yang, D.W.; Koo, J.H.; Padmanathan, M.; Carson, F. 3D TSV Processes and its Assembly/Packaging Technology. In Proceedings of IEEE International Conference on 3D System Integration, San Francisco, CA, USA, 28–30 September 2009; pp. 1–5.

- Leib, R.; Topper, M. New Wafer-Level-Packaging Technology Using Silicon-Via-Contacts for Optical and Other Sensor Applications. In Proceedings of IEEE 54th Electronic Components and Technology Conference, Las Vegas, NV, USA, 4 June 2004; pp. 843–847.

- Liepvre, A.L.; Accard, A.; Poingt, F.; Jany, C.; Lamponi, M.; Make, D.; Lelarge, F.; Fedeli, J.-M.; Messaoudene, S.; Bordel, D. Wavelength selectable hybrid III-V/Si laser fabricated by wafer bonding. IEEE Photonics Technol. Lett. 2013, 25, 1582–1585. [Google Scholar] [CrossRef]

- Barth, P.W. Silicon fusion bonding for fabrication of sensors, actuators and microstructures. Sens. Actuators A Phys. 1990, 23, 919–926. [Google Scholar] [CrossRef]

- Tsau, C.H.; Spearing, S.M.; Schmidt, M.A. Characterization of wafer-level thermocompression bonds. J. Microelectromech. Syst. 2004, 13, 963–971. [Google Scholar] [CrossRef]

- Dagel, D.J.; Cowan, W.D.; Spahn, O.B.; Grossetete, G.D.; Griñe, A.J.; Shaw, M.J.; Resnick, P.J.; Jokiel, B., Jr. Large-stroke MEMS deformable mirrors for adaptive optics. J. Microelectromech. Syst. 2006, 15, 572–583. [Google Scholar] [CrossRef]

- Jung, I.W.; Kim, S.; Solgaard, O. High-reflectivity broadband photonic crystal mirror MEMS scanner with low dependence on incident angle and polarization. J. Microelectromech. Syst. 2009, 18, 924–932. [Google Scholar] [CrossRef]

- Howlader, M.M.R.; Okada, H.; Kim, T.H.; Itoh, T.; Suga, T. Wafer level surface activated bonding tool for MEMS packaging. J. Electrochem. Soc. 2004, 151, G461–G467. [Google Scholar] [CrossRef]

- Howlader, M.M.R.; Doyle, T.E. Low temperature nanointegration for emerging biomedical applications. Microelectron. Reliab. 2012, 52, 361–374. [Google Scholar] [CrossRef]

- Howlader, M.M.R.; Kibria, M.G.; Zhang, F.; Kim, M.J. Hybrid plasma bonding for void-free strong bonded interface of silicon/glass at 200 °C. Talanta 2010, 82, 508–515. [Google Scholar] [CrossRef] [PubMed]

- Howlader, M.M.R.; Selvaganapathy, P.R.; Deen, M.J.; Suga, T. Nanobonding technology toward electronic, fluidic, and photonic systems integration. IEEE J. Sel. Top. Quantum Electron. 2011, 17, 689–703. [Google Scholar] [CrossRef]

- Howlader, M.M.R.; Suga, T.; Itoh, H.; Lee, T.H.; Kim, M.J. Role of heating on plasma-activated silicon wafers bonding. J. Electrochem. Soc. 2009, 156, H846–H851. [Google Scholar] [CrossRef]

- Howlader, M.M.R.; Suga, T.; Kim, M.J. Wafer Level and Chip Size Direct Wafer Bonding at Room Temperature. In Proceedings of International Symposia of State-of-the-Art Program on Compound Semiconductors XLI and Nitride and Wide Bandgap Semiconductors for Sensors, Photonics and Electronics V, Honolulu, HI, USA, 4–9 October 2004; pp. 150–160.

- Howlader, M.M.R.; Suga, T.; Kim, M.J. A novel bonding method for ionic wafers. IEEE Trans. Adv. Packag. 2007, 30, 598–604. [Google Scholar] [CrossRef]

- Howlader, M.M.R.; Watanabe, T.; Suga, T. Characterization of the bonding strength and interface current of p-Si/n-InP wafers bonded by surface activated bonding method at room temperature. J. Appl. Phys. 2002, 91, 3062–3066. [Google Scholar] [CrossRef]

- Howlader, M.M.R.; Watanabe, T.; Suga, T. Investigation of the bonding strength and interface current of p-Si/n-GaAs wafers bonded by surface activated bonding at room temperature. J. Vac. Sci. Technol. B 2001, 19, 2114–2118. [Google Scholar] [CrossRef]

- Howlader, M.M.R.; Zhang, F. Void-free strong bonding of surface activated silicon wafers from room temperature to annealing at 600 °C. Thin Solid Films 2010, 519, 804–808. [Google Scholar] [CrossRef]

- Howlader, M.M.R.; Zhang, F.; Kibria, M.G. Void nucleation at a sequentially plasma-activated silicon/silicon bonded interface. J. Micromech. Microeng. 2010, 20. [Google Scholar] [CrossRef]

- Takagi, H.; Maeda, R.; Suga, T. Wafer-scale spontaneous bonding of silicon wafers by argon-beam surface activation at room temperature. Sens. Actuators A Phys. 2003, 105, 98–102. [Google Scholar] [CrossRef]

- Suga, T.; Kim, T.H.; Howlader, M.M.R. Combined Process for Wafer Direct Bonding by Means of the Surface Activation Method. In Proceedings of IEEE 54th Electronic Components and Technology Conference, Las Vegas, NV, USA, 4 June 2004; pp. 484–490.

- Takigawa, R.; Higurashi, E.; Suga, T. Passive alignment and mounting of LiNbO3 waveguide chips on Si substrates. IEEE J. Sel. Top. Quantum Electron. 2011, 17, 652–658. [Google Scholar] [CrossRef]

- Zhang, F.; Kibria, M.G.; Cormier, K.; Howlader, M. Surface and interface characterization of sequentially plasma activated silicon, silicon dioxide and germanium wafers for low temperature bonding applications. ECS Trans. 2010, 33, 329–338. [Google Scholar]

- Howlader, M.M.R.; Suga, T. Comparative annealing effect on bonded wafers in air and ultrahigh vacuum for microelectromechanical systems/microfluidics packaging. J. Micro Nanolith. MEMS MOEMS 2010, 9. [Google Scholar] [CrossRef]

- Lai, K.W.C.; Xi, N.; Zhang, J.; Li, G.; Chen, H. Packaging Carbon Nanotube Based Infrared Detector. In Proceedings of IEEE 7th Conference on Nanotechnology, Hong Kong, China, 2–5 August 2007; pp. 778–781.

- Gan, X.; Shiue, R.-J.; Gao, Y.; Meric, I.; Heinz, T.F.; Shepard, K.; Hone, J.; Assefa, S.; Englund, D. Chip-integrated ultrafast graphene photodetector with high responsivity. Nat. Photonics 2013, 7, 883–887. [Google Scholar] [CrossRef]

- Esmaeili-Rad, M.R.; Salahuddin, S. High performance molybdenum disulfide amorphous silicon heterojunction photodetector. Sci. Rep. 2013, 3. [Google Scholar] [CrossRef] [PubMed]

- Gutiérrez, H.R.; Perea-López, N.; Elías, A.L.; Berkdemir, A.; Wang, B.; Lv, R.; López-Urías, F.; Crespi, V.H.; Terrones, H.; Terrones, M. Extraordinary room-temperature photoluminescence in triangular WS2 monolayers. Nano Lett. 2012, 13, 3447–3454. [Google Scholar] [CrossRef] [PubMed]

- Wang, J.B.; Li, W.L.; Chu, B.; Chen, L.L.; Zhang, G.; Su, Z.S.; Chen, Y.R.; Yang, D.F.; Zhu, J.Z.; Wu, S.H.; et al. Visible-blind ultraviolet photo-detector using tris-(8-hydroxyquinoline) rare earth as acceptors and the effects of the bulk and interfacial exciplex emissions on the photo-responsivity. Org. Electron. 2010, 11, 1301–1306. [Google Scholar] [CrossRef]

- Bernabé, S. Advanced Packaging Concepts for Low-Cost Optoelectronic Devices. In Proceedings of Workshop on Optical Components for Broadband Communication, Stockholm, Sweden, 27 July 2006; p. 635008.

- Ciftcioglu, B.; Berman, R.; Wang, S.; Hu, J.; Savidis, I.; Jain, M.; Moore, D.; Huang, M.; Friedman, E.G.; Wicks, G. 3-D integrated heterogeneous intra-chip free-space optical interconnect. Opt. Express 2012, 20, 4331–4345. [Google Scholar] [CrossRef] [PubMed]

- Sainati, R.A.; Moravec, T.J. Estimating high speed circuit interconnect performance. IEEE Trans. Circuits Syst. 1989, 36, 533–541. [Google Scholar] [CrossRef]

- Tekin, T. Review of packaging of optoelectronic, photonic, and MEMS components. IEEE J. Sel. Top. Quantum Electron. 2011, 17, 704–719. [Google Scholar] [CrossRef]

- Matthews, M.R.; Macdonald, B.M.; Preston, K.P. Optical Components-The New Challenge in Packaging. In Proceedings of IEEE 40th Electronic Components and Technology Conference, Las Vegas, NV, USA, 20–23 May 1990; pp. 206–213.

- Sancaktar, E.; Bai, L. Electrically conductive epoxy adhesives. Polymers 2011, 3, 427–466. [Google Scholar] [CrossRef]

- O’Connor, I. Optical Solutions for System-Level Interconnect. In Proceedings of International Workshop on System Level Interconnect Prediction, Paris, France, 14–15 February 2004; pp. 79–88.

- Tan, Q.; Lee, Y.C. Soldering Technology for Optoelectronic Packaging. In Proceedings of IEEE 46th Electronic Components and Technology Conference, Orlando, FL, USA, 28–31 May 1996; pp. 26–36.

- RoHS-Restriction of the Use of Certain Hazardous Substances in Electrical and Electronic Equipment Regulations. Available online: http://www.rohs.eu (accessed on 15 August 2015).

- Tian, Y.; Hutt, D.A.; Liu, C.; Stevens, B. High Density Indium Bmping Through Pulse Plating Used for Pixel X-ray Detectors. In Proceedings of International Conference on Electronic Packaging Technology & High Density Packaging, Beijing, China, 10–13 August 2009; pp. 456–460.

- Fritzsch, T.; Jordan, R.; Glaw, V.; Topper, M.; Dietrich, L.; Wolf, J.; Ehrmann, O.; Oppermann, H.; Reichl, H.; Wermes, N. Packaging of Radiation and Particle Detectors. In Proceedings of IEEE 56th Electronic Components and Technology Conference, San Diego, CA, USA, 30 May–2 June 2006; pp. 310–314.

- Garrou, P.; Bower, C.; Ramm, P. Handbook of 3D Integration: Technology and Applications of 3D Integrated Circuits; John Wiley & Sons: Weinheim, Germany, 2008; Vol. 1. [Google Scholar]

- Ji, F.; Leppävuori, S.; Luusua, I.; Henttinen, K.; Eränen, S.; Hietanen, I.; Juntunen, M. Fabrication of silicon based through-wafer interconnects for advanced chip scale packaging. Sens. Actuators A Phys. 2008, 142, 405–412. [Google Scholar] [CrossRef]

- Lapisa, M.; Stemme, G.; Niklaus, F. Wafer-level heterogeneous integration for MOEMS, MEMS, and NEMS. IEEE J. Sel. Top. Quantum Electron. 2011, 17, 629–644. [Google Scholar] [CrossRef]

- Ho, F.; Hung, V.; Tong, E.; Choi, T.; Chow, A.; Wong, E.; Lui, B.; Yau, K.; Egnisaban, G.; Mangente, T. Ultralow-Cost Optical Transceiver Modules Based on Leadframe Plastic-Package Technology. In Proceedings of IEEE 55th Electronic Components and Technology Conference, Lake Buena Vista, FL, USA, 31 May–3 June 2005; pp. 1032–1038.

- Lee, S.H.; Lee, Y.C. Optoelectronic packaging for optical interconnects. Opt. Photonics News 2006, 17, 40–45. [Google Scholar] [CrossRef]

- Welch, D.F.; Kish, F.A.; Melle, S.; Nagarajan, R.; Kato, M.; Joyner, C.H.; Pleumeekers, J.L.; Schneider, R.; Back, J.; Dentai, A.G. Large-scale InP photonic integrated circuits: Enabling efficient scaling of optical transport networks. IEEE J. Sel. Top. Quantum Electron. 2007, 13, 22–31. [Google Scholar] [CrossRef]

- Cho, S.-Y.; Seo, S.-W.; Brooke, M.A.; Jokerst, N.M. Integrated detectors for embedded optical interconnections on electrical boards, modules, and integrated circuits. IEEE J. Sel. Top. Quantum Electron. 2002, 8, 1427–1434. [Google Scholar] [CrossRef]

- Cho, S.-Y.; Hall, J.; Chellappa, A.; Jokerst, N.M.; Brooke, M. High Speed Optical Interconnection Using Embedded PDs on Electrical Boards. In Proceedings of IEEE 56th Electronic Components and Technology Conference, San Diego, CA, USA, 30 May–2 June 2003; pp. 1046–1052.

- Bhandarkar, S.M. Planar and wafer level packaging of semiconductor lasers and photo detectors for transmitter optical sub-assemblies. U.S. Patent 6,970,491, 29 November 2005. [Google Scholar]

- Yamamoto, S.-I.; Higurashi, E.; Suga, T.; Sawada, R. Low-temperature hermetic packaging for microsystems using Au-Au surface-activated bonding at atmospheric pressure. J. Micromech. Microeng. 2012, 22. [Google Scholar] [CrossRef]

- Higurashi, E.; Chino, D.; Suga, T.; Sawada, R. Au-Au surface-activated bonding and its application to optical microsensors with 3-D structure. IEEE J. Sel. Top. Quantum Electron. 2009, 15, 1500–1505. [Google Scholar] [CrossRef]

- Higurashi, E. Low-temperature bonding technologies for photonics applications. ECS Trans. 2013, 50, 351–362. [Google Scholar] [CrossRef]

- Brusberg, L.; Schroder, H.; Topper, M.; Arndt-Staufenbiel, N.; Roder, J.; Lutz, M.; Reichl, H. Thin Glass Based Packaging Technologies for Optoelectronic Modules. In Proceedings of IEEE 59th Electronic Components and Technology Conference, San Diego, CA, USA, 26–29 May 2009; pp. 207–212.

- Qin, Y.; Turkenburg, D.H.; Barbu, I.; Smaal, W.T.T.; Myny, K.; Lin, W.-Y.; Gelinck, G.H.; Heremans, P.; Liu, J.; Meinders, E.R. Organic thin-film transistors with anodized gate dielectric patterned by self-aligned embossing on flexible substrates. Adv. Funct. Mater. 2012, 22, 1209–1214. [Google Scholar] [CrossRef]

- Park, J.-S.; Park, K.-B.; Shin, K.-S.; Park, H.-D.; Kim, M.-C.; Kim, J.-R.; Park, S.-J.; Song, Y.-H. Design, fabrication and characterization of an integrated micro ammonia analysis system (IMAAS) with microreactor and in-plane type optical detector based on the Berthelot reaction. Sens. Actuators B Chem. 2006, 117, 516–522. [Google Scholar] [CrossRef]

- Kopp, C.; Bernabe, S.; Bakir, B.B.; Fedeli, J.; Orobtchouk, R.; Schrank, F.; Porte, H.; Zimmermann, L.; Tekin, T. Silicon photonic circuits: On-CMOS integration, fiber optical coupling, and packaging. IEEE J. Sel. Top. Quantum Electron. 2011, 17, 498–509. [Google Scholar] [CrossRef]

- Dragoi, V.; Mittendorfer, G.; Thanner, C.; Lindner, P. Wafer-level plasma activated bonding: New technology for MEMS fabrication. Microsyst. Technol. 2008, 14, 509–515. [Google Scholar] [CrossRef]

- Howlader, M.M.R.; Zhang, F.; Deen, M.J.; Suga, T.; Yamauchi, A. Surface activated bonding of copper through silicon vias and gold stud bumps at room temperature. J. Vac. Sci. Technol. A 2011, 29. [Google Scholar] [CrossRef]

- Roelkens, G.; Liu, L.; Liang, D.; Jones, R.; Fang, A.; Koch, B.; Bowers, J. III-V/silicon photonics for on-chip and intra-chip optical interconnects. Laser Photonics Rev. 2010, 4, 751–779. [Google Scholar] [CrossRef]

- Roelkens, G.; Van Campenhout, J.; Brouckaert, J.; Van Thourhout, D.; Baets, R.; Romeo, P.R.; Regreny, P.; Kazmierczak, A.; Seassal, C.; Letartre, X. III-V/Si photonics by die-to-wafer bonding. Mater. Today 2007, 10, 36–43. [Google Scholar] [CrossRef]

- Candler, R.N.; Park, W.-T.; Li, H.; Yama, G.; Partridge, A.; Lutz, M.; Kenny, T.W. Single wafer encapsulation of MEMS devices. IEEE Trans. Adv. Packag. 2003, 26, 227–232. [Google Scholar] [CrossRef]

- Gooch, R.; Schimert, T. Low-cost wafer-level vacuum packaging for MEMS. MRS Bull. 2003, 28, 55–60. [Google Scholar] [CrossRef]

- Liang, D.; Roelkens, G.; Baets, R.; Bowers, J.E. Hybrid integrated platforms for silicon photonics. Materials 2010, 3, 1782–1802. [Google Scholar] [CrossRef] [Green Version]

- Deen, M.J.; Basu, P.K. Silicon Photonics: Fundamentals and Devices; John Wiley & Sons: Chichester, UK, 2012. [Google Scholar]

- Beling, A.; Cross, A.S.; Piels, M.; Peters, J.; Zhou, Q.; Bowers, J.E.; Campbell, J.C. InP-based waveguide photodiodes heterogeneously integrated on silicon-on-insulator for photonic microwave generation. Opt. Express 2013, 21, 25901–25906. [Google Scholar] [CrossRef] [PubMed]

- Park, H.; Sysak, M.N.; Chen, H.-W.; Fang, A.W.; Liang, D.; Liao, L.; Koch, B.R.; Bovington, J.; Tang, Y.; Wong, K. Device and integration technology for silicon photonic transmitters. IEEE J. Sel. Top. Quantum Electron. 2011, 17, 671–688. [Google Scholar] [CrossRef]

- Le Liepvre, A.; Jany, C.; Accard, A.; Lamponi, M.; Poingt, F.; Make, D.; Lelarge, F.; Fedeli, J.-M.; Messaoudene, S.; Bordel, D. Widely Wavelength Tunable Hybrid III–V/Silicon Laser with 45 nm Tuning Range Fabricated Using a Wafer Bonding Technique. In Proceedings of IEEE 9th International Conference on Group IV Photonics, San Diego, CA, USA, 29–31 August 2012; pp. 54–56.

- Fang, A.W.; Park, H.; Cohen, O.; Jones, R.; Paniccia, M.J.; Bowers, J.E. Electrically pumped hybrid AlGaInAs-silicon evanescent laser. Opt. Express 2006, 14, 9203–9210. [Google Scholar] [CrossRef] [PubMed]

- Chen, L.; Dong, P.; Lipson, M. High performance germanium photodetectors integrated on submicron silicon waveguides by low temperature wafer bonding. Opt. Express 2008, 16, 11513–11518. [Google Scholar] [CrossRef] [PubMed]

- Qin, Y.; Howlader, M.M.R.; Deen, M.J.; Haddara, Y.M.; Selvaganapathy, P.R. Polymer integration for packaging of implantable sensors. Sens. Actuators B Chem. 2014, 202, 758–778. [Google Scholar] [CrossRef]

- Mehta, A.; Gromova, M.; Rusu, C.; Olivier, R.; Baert, K.; Van Hoof, C.; Witvrouw, A. Novel High Growth Rate Processes for Depositing Poly-SiGe Structural Layers at CMOS Compatible Temperatures. In Proceedings of 17th IEEE International Conference on Micro Electro Mechanical Systems, Maastricht, the Netherlands, 25–29 January 2004; pp. 721–724.

- Chen, M.; Yuan, L.; Liu, S. Research on low-temperature anodic bonding using induction heating. Sens. Actuators A Phys. 2007, 133, 266–269. [Google Scholar] [CrossRef]

- Wallis, G.; Pomerantz, D.I. Field assisted glass-metal sealing. J. Appl. Phys. 1969, 40, 3946–3949. [Google Scholar] [CrossRef]

- Rogers, T. Considerations of anodic bonding for capacitive type silicon/glass sensor fabrication. J. Micromech. Microeng. 1992, 2. [Google Scholar] [CrossRef]

- Leib, J.; Gyenge, O.; Hansen, U.; Maus, S.; Hauck, K.; Zoschke, K.; Toepper, M. Wafer-Level Glass-Caps for Advanced Optical Applications. In Proceedings of IEEE 61st Electronic Components and Technology Conference, Lake Buena Vista, FL, USA, 31 May–3 June 2011; pp. 1642–1648.

- Stenchly, V.; Quenzer, H.-J.; Hofmann, U.; Janes, J.; Jensen, B.; Benecke, W. New Fabrication Method of Glass Packages with Inclined Optical Windows for Micromirrors on Wafer Level. Proc. SPIE 2013, 8613. [Google Scholar] [CrossRef]

- Daschner, R.; Kübler, H.; Löw, R.; Baur, H.; Frühauf, N.; Pfau, T. Triple stack glass-to-glass anodic bonding for optogalvanic spectroscopy cells with electrical feedthroughs. Appl. Phys. Lett. 2014, 105. [Google Scholar] [CrossRef]

- Lee, H.J.; Kim, Y.; Yoon, E.-S.; Cho, I.-J. Versatile size and shape microlens arrays with high numerical apertures. J. Microelectromech. Syst. 2014, 23, 771–773. [Google Scholar] [CrossRef]

- Bargiel, S.; Gorecki, C.; Barański, M.; Passilly, N.; Wiemer, M.; Jia, C.; Froemel, J. 3D Micro-Optical Lens Scanner Made by Multi-Wafer Bonding Technology. Proc. SPIE 2013, 8616. [Google Scholar] [CrossRef]

- Yoo, S.; Jin, J.-Y.; Ha, J.-G.; Ji, C.-H.; Kim, Y.-K. Two-dimensional optical scanner with monolithically integrated glass microlens. J. Micromech. Microeng. 2014, 24. [Google Scholar] [CrossRef]

- Surdo, S.; Merlo, S.; Carpignano, F.; Strambini, L.M.; Trono, C.; Giannetti, A.; Baldini, F.; Barillaro, G. Optofluidic microsystems with integrated vertical one-dimensional photonic crystals for chemical analysis. Lab Chip 2012, 12, 4403–4415. [Google Scholar] [CrossRef] [PubMed]

- Mhaskar, R.; Knappe, S.; Kitching, J. A low-power, high-sensitivity micromachined optical magnetometer. Appl. Phys. Lett. 2012, 101. [Google Scholar] [CrossRef]

- Kogita, Y.; Hirai, Y.; Tabata, O.; Tsuchiya, T. Double-side-drive electrostatic optical chopper for time-resolved Raman spectroscopy. In Proceedings of International Conference on Optical MEMS and Nanophotonics, Glasgow, Scotland, 17–21 August 2014; pp. 65–66.

- Tong, Q.-Y.; Schmidt, E.; Gösele, U.; Reiche, M. Hydrophobic silicon wafer bonding. Appl. Phys. Lett. 1994, 64, 625–627. [Google Scholar] [CrossRef]

- Suni, T.; Henttinen, K.; Suni, I.; Mäkinen, J. Effects of plasma activation on hydrophilic bonding of Si and SiO2. J. Electrochem. Soc. 2002, 149, G348–G351. [Google Scholar] [CrossRef]

- Tong, Q.-Y.; Schmidt, E.; Gosele, U.; Reiche, M. Hydrophobic silicon wafer bonding. Appl. Phys. Lett. 1994, 64, 625–627. [Google Scholar] [CrossRef]

- Tong, Q.-Y.; Gan, Q.; Hudson, G.; Fountain, G.; Enquist, P.; Scholz, R.; Gösele, U. Low-temperature hydrophobic silicon wafer bonding. Appl. Phys. Lett. 2003, 83, 4767–4769. [Google Scholar] [CrossRef]

- Kopp, C.; Augendre, E.; Orobtchouk, R.; Lemonnier, O.; Fedeli, J.-M. Enhanced fiber grating coupler integrated by wafer-to-wafer bonding. J. Lightwave Technol. 2011, 29, 1847–1851. [Google Scholar] [CrossRef]

- Emboras, A.; Briggs, R.M.; Najar, A.; Nambiar, S.; Delacour, C.; Grosse, P.; Augendre, E.; Fedeli, J.M.; de Salvo, B.; Atwater, H.A. Efficient coupler between silicon photonic and metal-insulator-silicon-metal plasmonic waveguides. Appl. Phys. Lett. 2012, 101. [Google Scholar] [CrossRef]

- Maruyama, T.; Okumura, T.; Arai, S. Direct wafer bonding of GaInAsP/InP membrane structure on silicon-on-insulator substrate. Jpn. J. Appl. Phys. 2006, 45, 8717–8718. [Google Scholar] [CrossRef]

- Kalkowski, G.; Zeitner, U.; Benkenstein, T.; Fuchs, J.; Rothhardt, C.; Eberhardt, R. Direct wafer bonding for encapsulation of fused silica optical gratings. Microelectron. Eng. 2012, 97, 177–180. [Google Scholar] [CrossRef]

- Kanbe, H.; Miyaji, M.; Ito, T. Ge/Si heterojunction photodiodes fabricated by low temperature wafer bonding. Appl. Phys. Express 2008, 1. [Google Scholar] [CrossRef]

- Higurashi, E.; Imamura, T.; Suga, T.; Sawada, R. Low-temperature bonding of laser diode chips on silicon substrates using plasma activation of Au films. IEEE Photonics Technol. Lett. 2007, 19, 1994–1996. [Google Scholar] [CrossRef]

- Shigetou, A.; Itoh, T.; Matsuo, M.; Hayasaka, N.; Okumura, K.; Suga, T. Bumpless interconnect through ultrafine Cu electrodes by means of surface-activated bonding (SAB) method. IEEE Trans. Adv. Packag. 2006, 29, 218–226. [Google Scholar] [CrossRef]

- Howlader, M.M.R.; Yamauchi, A.; Suga, T. Surface activation based nano-bonding and interconnection at room temperature. J. Micromech. Microeng. 2011, 21. [Google Scholar] [CrossRef]

- Howlader, M.M.R.; Suga, T.; Zhang, F.; Lee, T.H.; Kim, M.J. Interfacial behavior of surface activated p-GaP/n-GaAs bonded wafers at room temperature. Electrochem. Solid State Lett. 2010, 13, H61–H65. [Google Scholar] [CrossRef]

- Mizumoto, T.; Saito, H.; Sakurai, K.; Shoji, Y. Wafer bonding of magneto-optic garnet and its application to waveguide optical devices. ECS Trans. 2006, 3, 11–22. [Google Scholar]

- Howlader, M.M.R.; Suga, T.; Kim, M.J. Room temperature bonding of silicon and lithium niobate. Appl. Phys. Lett. 2006, 89. [Google Scholar] [CrossRef]

- Shoji, Y.; Mizumoto, T.; Yokoi, H.; Hsieh, I.-W.; Osgood, R.M. Magneto-optical isolator with silicon waveguides fabricated by direct bonding. Appl. Phys. Lett. 2008, 92. [Google Scholar] [CrossRef]

- Howlader, M.M.R.; Iwashita, M.; Nanbu, K.; Saijo, K.; Suga, T. Enhanced Cu/LCP adhesion by pre-sputter cleaning prior to Cu deposition. IEEE Trans. Adv. Packag. 2005, 28, 495–502. [Google Scholar] [CrossRef]

- Howlader, M.M.R.; Kibria, M.G.; Zhang, F. Hybrid plasma bonding of germanium and glass wafers at low temperature. Mater. Lett. 2010, 64, 1532–1535. [Google Scholar] [CrossRef]

- Howlader, M.M.R.; Suehara, S.; Takagi, H.; Kim, T.H.; Maeda, R.; Suga, T. Room-temperature microfluidics packaging using sequential plasma activation process. IEEE Trans. Adv. Packag. 2006, 29, 448–456. [Google Scholar] [CrossRef]

- Howlader, M.M.R.; Suga, T.; Takahashi, A.; Saijo, K.; Ozawa, S.; Nanbu, K. Surface activated bonding of LCP/Cu for electronic packaging. J. Mater. Sci. 2005, 40, 3177–3184. [Google Scholar] [CrossRef]

- Howlader, M.M.R.; Zhang, F.; Deen, M.J. Formation of gallium arsenide nanostructures in Pyrex glass. Nanotechnology 2013, 24. [Google Scholar] [CrossRef] [PubMed]

- Gueguen, P.; Di Cioccio, L.; Rivoire, M.; Scevola, D.; Zussy, M.; Charvet, A.M.; Bally, L.; Lafond, D.; Clavelier, L. Copper Direct Bonding for 3D Integration. In Proceedings of IEEE International Interconnect Technology Conference, Burlingame, CA, USA, 1–4 June 2008; pp. 61–63.

- Gueguen, P.; di Cioccio, L.; Gergaud, P.; Rivoire, M.; Scevola, D.; Zussy, M.; Charvet, A.M.; Bally, L.; Lafond, D.; Clavelier, L. Copper direct-bonding characterization and its interests for 3D integration. J. Electrochem. Soc. 2009, 156, H772–H776. [Google Scholar] [CrossRef]

- Taibi, R.; Di Cioccio, L.; Chappaz, C.; Chapelon, L.-L.; Gueguen, P.; Decham, J.; Fortunier, R.; Clavelier, L. Full Characterization of Cu/Cu Direct Bonding for 3D Integration. In Proceedings of IEEE 60th Electronic Components and Technology Conference, Las Vegas, NV, USA, 1–4 June 2010; pp. 219–225.

- Moriceau, H.; Bataillou, B.; Morales, C.; Cartier, A.M.; Rieutord, F. Interest of a Short Plasma Treatment to Achieve Si-SiO2-Si Bonded Structures. In Proceedings of the 7th International Symposium on Semiconductor Wafer Bonding Science, Technology, and Applications, Paris, France, 27 April–2 May 2003; pp. 110–117.

- Moriceau, H.; Rieutord, F.; Morales, C.; Sartori, S.; Charvet, A.M. Surface plasma activation before direct wafer bonding: A short review and recent results. In Proceedings of 207th Meeting of the Electrochemical Society, Quebec, QC, Canada, 16–18 May 2005; pp. 34–49.

- Niklaus, F.; Stemme, G.; Lu, J.-Q.; Gutmann, R.J. Adhesive wafer bonding. J. Appl. Phys. 2006, 99. [Google Scholar] [CrossRef]

- Keyvaninia, S.; Muneeb, M.; Stanković, S.; van Veldhoven, P.J.; van Thourhout, D.; Roelkens, G. Ultra-thin DVS-BCB adhesive bonding of III-V wafers, dies and multiple dies to a patterned silicon-on-insulator substrate. Opt. Mater. Express 2013, 3, 35–46. [Google Scholar] [CrossRef]

- Zoberbier, M.; Hansen, S.; Hennemeyer, M.; Tönnies, D.; Zoberbier, R.; Brehm, M.; Kraft, A.; Eisner, M.; Völkel, R. Wafer Level Cameras-Novel Fabrication and Packaging Technologies. In Proceedings of International Image Sensor Workshop, Bergen, Norway, 26–28 June 2009.

- Wang, Z. 3-D integration and through-silicon vias in MEMS and microsensors. J. Microelectromech. Syst. 2015, 24, 1211–1244. [Google Scholar] [CrossRef]

- Snyder, B.W.; O’Brien, P.A. Developments in Packaging and Integration for Silicon Photonics. Proc. SPIE 2013, 8614. [Google Scholar] [CrossRef]

- Stanković, S.; Jones, R.; Sysak, M.N.; Heck, J.M.; Roelkens, G.; Van Thourhout, D. Hybrid III-V/Si distributed-feedback laser based on adhesive bonding. IEEE Photonics Technol. Lett. 2012, 24, 2155–2158. [Google Scholar] [CrossRef]

- Lee, J.; Maeda, Y.; Atsumi, Y.; Takino, Y.; Nishiyama, N.; Arai, S. Low-loss GaInAsP wire waveguide on Si substrate with benzocyclobutene adhesive wafer bonding for membrane photonic circuits. Jpn. J. Appl. Phys. 2012, 51. [Google Scholar] [CrossRef]

- Ryckeboer, E.; Gassenq, A.; Hattasan, N.; Kuyken, B.; Cerutti, L.; Rodriguez, J.-B.; Tournie, E.; Roelkens, G.; Bogaerts, W.; Baets, R. Integrated Spectrometer and Integrated Detectors on Silicon-on-Insulator for Short-Wave Infrared Applications. In Proceedings of Conference on Lasers and Electro-Optics, San Jose, CA, USA, 6–11 May 2012.

- Roelkens, G.; Green, W.M.J.; Kuyken, B.; Liu, X.; Hattasan, N.; Gassenq, A.; Cerutti, L.; Rodriguez, J.B.; Osgood, R.M.; Tournié, E. III–V/silicon photonics for short-wave infrared spectroscopy. IEEE J. Quantum Electron. 2012, 48, 292–298. [Google Scholar] [CrossRef]

- Ghosh, S.; Keyvaninia, S.; Van Roy, W.; Mizumoto, T.; Roelkens, G.; Baets, R. Adhesively bonded Ce:YIG/SOI integrated optical circulator. Opt. Lett. 2013, 38, 965–967. [Google Scholar] [CrossRef] [PubMed]

- Wolffenbuttel, R.F. Low-temperature intermediate Au-Si wafer bonding; eutectic or silicide bond. Sens. Actuators A Phys. 1997, 62, 680–686. [Google Scholar] [CrossRef]

- Sood, S.; Farrens, S.; Pinker, R.; Xie, J.; Cataby, W. Al-Ge eutectic wafer bonding and bond characterization for CMOS compatible wafer packaging. ECS Trans. 2010, 33, 93–101. [Google Scholar]

- Liu, H.; Salomonsen, G.; Wang, K.; Aasmundtveit, K.E.; Hoivik, N. Wafer-level Cu/Sn to Cu/Sn SLID-bonded interconnects with increased strength. IEEE Trans. Compon. Packag. Manuf. Technol. 2011, 1, 1350–1358. [Google Scholar] [CrossRef]

- Itzler, M.A.; Entwistle, M.; Krishnamachari, U.; Owens, M.; Jiang, X.; Slomkowski, K.; Rangwala, S. SWIR Geiger-Mode APD Detectors and Cameras for 3D Imaging. Proc. SPIE 2014, 9114. [Google Scholar] [CrossRef]

- Wen, S.-Y.; Hu, H.-L.; Tsai, Y.-J.; Hsu, C.-P.; Lin, R.-C.; Horng, R.H. A novel integrated structure of thin film GaN LED with ultra-low thermal resistance. Opt. Express 2014, 22, A601–A606. [Google Scholar] [CrossRef] [PubMed]

- Choi, E.; Kim, A.; Cui, Y.; Chae, S.J.; Nam, M.; Kwon, S.H.; Cha, Y.W.; Pyo, S.G. Eutectic bonding utilizing radio frequency induction heating for fabricating vertical light-emitting diodes. J. Nanosci. Nanotechnol. 2015, 15, 8533–8536. [Google Scholar] [CrossRef]

- Hao, G.-D.; Wang, X.-L. Enhancement of light-extraction efficiency in AlGaInP light-emitting diodes using evanescent wave coupling effect. Appl. Phys. Lett. 2013, 103. [Google Scholar] [CrossRef]

- McDougall, S.; McKee, A.; Eddie, I.; Tweedie, A.; Meredith, W. Development of High Power Laser Technology: 915 nm Mini-Bars for Fibre Laser Pumping and Red Lser Bars for Cinema/Projector Applications. In Proceedings of High Power Diode Lasers and Systems Conference, Coventry, UK, 16–17 October 2013; pp. 22–23.

- Han, M.-S.; Han, S.M.; Kim, H.J.; Shin, J.C.; Ahn, M.S.; Kim, H.W.; Han, Y.H. Low-Cost Compact Thermal Imaging Sensors for Body Temperature Measurement. Proc. SPIE 2013, 8704. [Google Scholar] [CrossRef]

- Lani, S.; Bayat, D.; Pétremand, Y. 2D Electrostatic Micromirror Array with High Field Factor for High-Power Application. Proc. SPIE 2013, 8616. [Google Scholar] [CrossRef]

- Griffel, G.; Ruschin, S.; Croitoru, N. Linear Electrooptic Effect in Sputtered Polycrystalline LiNbO3 Films. In Proceedings of International Congress on Optical Science and Engineering, Hamburg, Germany, 19–23 September 1988; pp. 228–232.

- Kotov, V.N.; Uchoa, B.; Pereira, V.M.; Guinea, F.; Neto, A.H.C. Electron-electron interactions in graphene: Current status and perspectives. Rev. Mod. Phys. 2012, 84. [Google Scholar] [CrossRef]

- Gan, X.; Mak, K.F.; Gao, Y.; You, Y.; Hatami, F.; Hone, J.; Heinz, T.F.; Englund, D. Strong enhancement of light-matter interaction in graphene coupled to a photonic crystal nanocavity. Nano Lett. 2012, 12, 5626–5631. [Google Scholar] [CrossRef] [PubMed]

- Furchi, M.; Urich, A.; Pospischil, A.; Lilley, G.; Unterrainer, K.; Detz, H.; Klang, P.; Andrews, A.M.; Schrenk, W.; Strasser, G. Microcavity-integrated graphene photodetector. Nano Lett. 2012, 12, 2773–2777. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Liu, Y.; Cheng, R.; Liao, L.; Zhou, H.; Bai, J.; Liu, G.; Liu, L.; Huang, Y.; Duan, X. Plasmon resonance enhanced multicolour photodetection by graphene. Nat. Commun. 2011, 2. [Google Scholar] [CrossRef] [PubMed]

- Cheng, S.-H.; Weng, T.-M.; Lu, M.-L.; Tan, W.-C.; Chen, J.-Y.; Chen, Y.-F. All carbon-based photodetectors: An eminent integration of graphite quantum dots and two dimensional graphene. Sci. Rep. 2013, 3. [Google Scholar] [CrossRef] [PubMed]

- Fu, Y.; Qin, Y.; Wang, T.; Chen, S.; Liu, J. Ultrafast transfer of metal-enhanced carbon nanotubes at low temperature for large-scale electronics assembly. Adv. Mater. 2010, 22, 5039–5042. [Google Scholar] [CrossRef] [PubMed]

- Wang, T.; Jiang, D.; Chen, S.; Jeppson, K.; Ye, L.; Liu, J. Formation of three-dimensional carbon nanotube structures by controllable vapor densification. Mater. Lett. 2012, 78, 184–187. [Google Scholar] [CrossRef]

- Wang, T.; Chen, S.; Jiang, D.; Fu, Y.; Jeppson, K.; Ye, L.; Liu, J. Through-silicon vias filled with densified and transferred carbon nanotube forests. IEEE Electron Device Lett. 2012, 33, 420–422. [Google Scholar] [CrossRef]

- Reichl, H.; Aschenbrenner, R.; Potter, H. Hetero system integration-Enabling technology for future products. German Technology-Electronics Production Equipment; VDMA Verlag: Frankfurt/Main, Germany, 2008; pp. 45–49. [Google Scholar]

- Heck, M.; Bauters, J.; Davenport, M.; Doylend, J.; Jain, S.; Kurczveil, G.; Srinivasan, S.; Tang, Y.; Bowers, J. Hybrid silicon photonic integrated circuit technology. IEEE J. Sel. Top. Quantum Electron. 2013, 4, 1–18. [Google Scholar] [CrossRef]

- Ahn, D.; Hong, C.-Y.; Liu, J.; Giziewicz, W.; Beals, M.; Kimerling, L.C.; Michel, J.; Chen, J.; Kńrtner, F.X. High performance, waveguide integrated Ge photodetectors. Opt. Express 2007, 15, 3916–3921. [Google Scholar] [CrossRef] [PubMed]

- Michel, J.; Liu, J.; Kimerling, L.C. High-performance Ge-on-Si photodetectors. Nat. Photonics 2010, 4, 527–534. [Google Scholar] [CrossRef]

- Rogalski, A. Progress in focal plane array technologies. Prog. Quantum Electron. 2012, 36, 342–473. [Google Scholar] [CrossRef]

- Rogalski, A. History of infrared detectors. Opto Electron. Rev. 2012, 20, 279–308. [Google Scholar] [CrossRef]

- El-Desouki, M.; Jamal Deen, M.; Fang, Q.; Liu, L.; Tse, F.; Armstrong, D. CMOS image sensors for high speed applications. Sensors 2009, 9, 430–444. [Google Scholar] [CrossRef] [PubMed]

- Liang, D.; Bowers, J.E. Photonic integration: Si or InP substrates? Electron. Lett. 2009, 45, 578–581. [Google Scholar] [CrossRef]

- Duan, G.-H.; Jany, C.; le Liepvre, A.; Accard, A.; Lamponi, M.; Make, D.; Kaspar, P.; Levaufre, G.; Girard, N.; Lelarge, F. Hybrid III-V on silicon lasers for photonic integrated circuits on silicon. IEEE J. Sel. Top. Quantum Electron. 2014, 20, 158–170. [Google Scholar] [CrossRef]

- Song, F.; Xiao, J.; Udawala, F.; Seo, S.-W. Heterogenous integration of a thin-film GaAs photodetector and a microfluidic device on a silicon substrate. J. Micromech. Microeng. 2011, 21. [Google Scholar] [CrossRef]

- Bock, K.; Wolf, J.; Reichl, H. Trends in RF & Wireless Packaging. In Proceedings of the International Conference on Compound Semiconductor Manufacturing Technology (Sharing Ideas Throughout the Industry), Miami, FL, USA, 3–6 May 2004; p. 10A.

- Ma, C.L.F.; Deen, M.J.; Tarof, L.E.; Yu, J.C.H. Temperature dependence of breakdown voltages in separate absorption, grading, charge, and multiplication InP/InGaAs avalanche photodiodes. IEEE Trans. Electron Devices 1995, 42, 810–818. [Google Scholar] [CrossRef]

- Cho, I.-K.; Yun, J.-H.; Jeong, M.-Y.; Park, H.-H. Optical chip-to-chip link system by using optical wiring method for reducing EMI. IEEE Trans. Adv. Packag. 2010, 33, 722–728. [Google Scholar]

- Liu, F.; Guidotti, D.; Sundaram, V.; Mahajan, S.; Huang, Z.; Chang, Y.-J.; Chang, G.K.; Tummala, R.R. Material and Process Challenges in Embedding Polymeric Waveguides and Detectors in System on Package (SOP). In Proceedings of IEEE 9th International Symposium on Advanced Packaging Materials: Processes, Properties and Interfaces, Atlanta, GA, USA, 24–26 March 2004; pp. 89–94.

- Zhang, Z.; Felipe, D.; Katopodis, V.; Groumas, P.; Kouloumentas, C.; Avramopoulos, H.; Dupuy, J.-Y.; Konczykowska, A.; Dede, A.; Beretta, A. Hybrid photonic integration on a polymer platform. Photonics 2015, 2, 1005–1026. [Google Scholar] [CrossRef]

- Qin, Y.; Kwon, H.-J.; Howlader, M.M.R.; Deen, M.J. Microfabricated electrochemical pH and free chlorine sensors for water quality monitoring: Recent advances and research challenges. RSC Adv. 2015, 5, 69086–69109. [Google Scholar] [CrossRef]

- Deen, M.J.; Pascal, F. Electrical characterization of semiconductor materials and devices-Review. J. Mater. Sci. Mater. Electron. 2006, 17, 549–575. [Google Scholar] [CrossRef]

- Boudreau, R.; Zhou, P.; Bowen, T. Wafer scale photonic-die attachment. IEEE Trans. Compon. Packagi. Manuf. Technol. 1998, 21, 136–139. [Google Scholar] [CrossRef]

- Qin, Y.; Alam, A.U.; Pan, S.; Howlader, M.M.R.; Ghosh, R.; Selvaganapathy, P.R.; Wu, Y.; Deen, M.J. Low-temperature solution processing of palladium/palladium oxide films and their pH sensing performance. Talanta 2015, 146, 517–524. [Google Scholar] [CrossRef]

- Kfouri, M.; Marinov, O.; Quevedo, P.; Faramarzpour, N.; Shirani, S.; Liu, L.W.-C.; Fang, Q.; Deen, M.J. Toward a miniaturized wireless fluorescence-based diagnostic imaging system. IEEE J. Sel. Top. Quantum Electron. 2008, 14, 226–234. [Google Scholar] [CrossRef]

- Cheng, Z.; Deen, M.J.; Peng, H. A low-power gateable vernier ring oscillator time-to-digital converter for biomedical imaging applications. IEEE Trans. Biomed. Circuits Syst. 2015, PP, 1–10. [Google Scholar] [CrossRef] [PubMed]

- Cheng, Z.; Zheng, X.; Deen, M.J.; Peng, H. Development of a high performance digital silicon photomultiplier (dSiPM) for ToF PET imaging. J. Nucl. Med. 2015, 56, 603. [Google Scholar]

- Zheng, X.; Cheng, Z.; Deen, M.J.; Peng, H. Improving the spatial resolution in CZT detectors using charge sharing effect and transient signal analysis: Simulation study. Nucl. Instrum. Meth. A 2015, 808, 60–70. [Google Scholar] [CrossRef]

- Zheng, X.; Cheng, Z.; Deen, M.J.; Peng, H. Investigation of the sub-pixel spatial resolution and charge-sharing effect in CZT detectors for PET imaging. J. Nucl. Med. 2015, 56, 1873. [Google Scholar]

© 2015 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Qin, Y.; Howlader, M.M.R.; Deen, M.J. Low-Temperature Bonding for Silicon-Based Micro-Optical Systems. Photonics 2015, 2, 1164-1201. https://doi.org/10.3390/photonics2041164

Qin Y, Howlader MMR, Deen MJ. Low-Temperature Bonding for Silicon-Based Micro-Optical Systems. Photonics. 2015; 2(4):1164-1201. https://doi.org/10.3390/photonics2041164

Chicago/Turabian StyleQin, Yiheng, Matiar M.R. Howlader, and M. Jamal Deen. 2015. "Low-Temperature Bonding for Silicon-Based Micro-Optical Systems" Photonics 2, no. 4: 1164-1201. https://doi.org/10.3390/photonics2041164

APA StyleQin, Y., Howlader, M. M. R., & Deen, M. J. (2015). Low-Temperature Bonding for Silicon-Based Micro-Optical Systems. Photonics, 2(4), 1164-1201. https://doi.org/10.3390/photonics2041164