Ta2O5/SiO2 Multicomponent Dielectrics for Amorphous Oxide TFTs

Abstract

:1. Introduction

2. Materials and Methods

2.1. Device Fabrication

2.2. Films and Devices Characterization

3. Results and Discussion

3.1. Multicomponent Dielectric Properties

3.2. Device Characterization

3.2.1. TFT Performance

3.2.2. Insulation Reliability

3.2.3. Stability

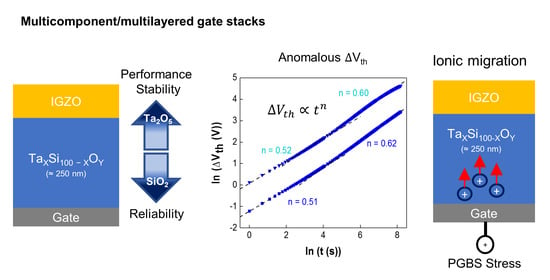

3.3. Mechanism of the Anomalous Vth Shift

4. Conclusions

Supplementary Materials

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Kwon, J.-Y.; Lee, D.-J.; Kim, K.-B. Review paper: Transparent amorphous oxide semiconductor thin film transistor. Electron. Mater. Lett. 2011, 7, 1–11. [Google Scholar] [CrossRef]

- Park, J.S.; Maeng, W.-J.; Kim, H.-S.; Park, J.-S. Review of recent developments in amorphous oxide semiconductor thin-film transistor devices. Thin Solid Films 2012, 520, 1679–1693. [Google Scholar] [CrossRef]

- Zhang, Y.H.; Mei, Z.X.; Liang, H.L.; Du, X.L.; Physics, M. Review of flexible and transparent thin-film transistors based on zinc. Chin. Phys. B Rev. 2017, 26. [Google Scholar] [CrossRef] [Green Version]

- Barquinha, P.; Martins, R.; Pereira, L.; Fortunato, E. Transparent Oxide Electronics: From Materials to Devices; John Wiley & Sons, Ltd.: Chichester, UK, 2012; ISBN 9780470683736. [Google Scholar]

- Facchetti, A.; Marks, T. Transparent Electronics; Facchetti, A., Marks, T.J., Eds.; John Wiley & Sons, Ltd.: Chichester, UK, 2010; ISBN 9780470710609. [Google Scholar]

- Tobjörk, D.; Österbacka, R. Paper electronics. Adv. Mater. 2011, 23, 1935–1961. [Google Scholar] [CrossRef]

- Martins, R.; Ferreira, I.; Fortunato, E. Electronics with and on paper. Phys. Status Solidi Rapid Res. Lett. 2011, 5, 332–335. [Google Scholar] [CrossRef]

- Gaspar, D.; Martins, J.; Bahubalindruni, P.; Pereira, L.; Fortunato, E.; Martins, R. Planar Dual-Gate Paper/Oxide Field Effect Transistors as Universal Logic Gates. Adv. Electron. Mater. 2018, 4, 1–8. [Google Scholar] [CrossRef]

- Martins, R.; Gaspar, D.; Mendes, M.J.; Pereira, L.; Martins, J.; Bahubalindruni, P.; Barquinha, P.; Fortunato, E. Papertronics: Multigate paper transistor for multifunction applications. Appl. Mater. Today 2018, 12, 402–414. [Google Scholar] [CrossRef]

- Bahubalindruni, P.G.; Martins, J.; Santa, A.; Tavares, V.; Martins, R.; Fortunato, E.; Barquinha, P. High-Gain transimpedance amplifier for flexible radiation dosimetry using ingazno tfts. IEEE J. Electron Devices Soc. 2018, 6, 760–765. [Google Scholar] [CrossRef]

- Tiwari, B.; Bahubalindruni, P.G.; Santa, A.; Martins, J.; Mittal, P.; Goes, J.; Martins, R.; Fortunato, E.; Barquinha, P. Oxide TFT Rectifiers on Flexible Substrates Operating at NFC Frequency Range. IEEE J. Electron Devices Soc. 2019, 7, 329–334. [Google Scholar] [CrossRef]

- Barquinha, P. Transparent Oxide Thin-Film Transistors: Production, Characterization and Integration. Ph.D. Thesis, NOVA School of Science and Technology, NOVA University Lisbon, Lisbon, Portugal, 2010. [Google Scholar]

- Olziersky, A.; Barquinha, P.; Vilà, A.; Magana, C.; Fortunato, E.; Morante, J.R.; Martins, R. Role of Ga2O3-In2O3-ZnO channel composition on the electrical performance of thin-film transistors. Mater. Chem. Phys. 2011, 131, 512–518. [Google Scholar] [CrossRef]

- Barquinha, P.; Pereira, L.; Gonçalves, G.; Martins, R.; Kuščer, D.; Kosec, M.; Fortunato, E. Performance and Stability of Low Temperature Transparent Thin-Film Transistors Using Amorphous Multicomponent Dielectrics. J. Electrochem. Soc. 2009, 156, H824. [Google Scholar] [CrossRef]

- Park, C.-R.R.; Hwang, J.-H.H. Effect of double-layered Al2O3/SiO2 dielectric materials on In–Ga–Zn–O(IGZO)-based amorphous transparent thin film transistors. Ceram. Int. 2014, 40, 12917–12922. [Google Scholar] [CrossRef]

- Honda, K.; Sakai, A.; Sakashita, M.; Ikeda, H.; Zaima, S.; Yasuda, Y. Pulsed Laser Deposition and Analysis for Structural and Electrical Properties of HfO2 –TiO2 Composite Films. Jpn. J. Appl. Phys. 2004, 43, 1571–1576. [Google Scholar] [CrossRef]

- Lebedinskii, Y.Y.; Zenkevich, A.; Gusev, E.P.; Gribelyuk, M. In situ investigation of growth and thermal stability of ultrathin Si layers on the HfO2∕Si (100) high-κ dielectric system. Appl. Phys. Lett. 2005, 86, 191904. [Google Scholar] [CrossRef]

- Xing, S.; Zhang, N.; Song, Z.; Shen, Q.; Lin, C. Preparation of hafnium oxide thin film by electron beam evaporation of hafnium incorporating a post thermal process. Microelectron. Eng. 2003, 66, 451–456. [Google Scholar] [CrossRef]

- Chowdhury, N.A.; Garg, R.; Misra, D. Charge trapping and interface characteristics of thermally evaporated HfO2. Appl. Phys. Lett. 2004, 85, 3289–3291. [Google Scholar] [CrossRef]

- Pereira, L.; Barquinha, P.; Gonçalves, G.; Vilà, A.; Olziersky, A.; Morante, J.; Fortunato, E.; Martins, R. Sputtered multicomponent amorphous dielectrics for transparent electronics. Phys. Status Solidi 2009, 206, 2149–2154. [Google Scholar] [CrossRef]

- Pereira, L.; Barquinha, P.; Gonçalves, G.; Fortunato, E.; Martins, R. Multicomponent dielectrics for oxide TFT. In Proceedings of the Oxide-Based Materials and Devices III; SPIE OPTO: San Francisco, CA, USA, 2012; Volume 8263, p. 826316. [Google Scholar]

- Song, J.I.; Park, J.S.; Kim, H.; Heo, Y.W.; Lee, J.H.; Kim, J.J.; Kim, G.M.; Choi, B.D. Transparent amorphous indium zinc oxide thin-film transistors fabricated at room temperature. Appl. Phys. Lett. 2007, 90. [Google Scholar] [CrossRef]

- Carlos, E.; Branquinho, R.; Kiazadeh, A.; Barquinha, P.; Martins, R.; Fortunato, E. UV-Mediated Photochemical Treatment for Low-Temperature Oxide-Based Thin-Film Transistors. ACS Appl. Mater. Interfaces 2016, 8, 31100–31108. [Google Scholar] [CrossRef]

- Carlos, E.; Leppäniemi, J.; Sneck, A.; Alastalo, A.; Deuermeier, J.; Branquinho, R.; Martins, R.; Fortunato, E. Printed, Highly Stable Metal Oxide Thin-Film Transistors with Ultra-Thin High-κ Oxide Dielectric. Adv. Electron. Mater. 2020, 6, 1901071. [Google Scholar] [CrossRef]

- Lim, W.; Kim, S.; Wang, Y.-L.; Lee, J.W.; Norton, D.P.; Pearton, S.J.; Ren, F.; Kravchenko, I.I. High-Performance Indium Gallium Zinc Oxide Transparent Thin-Film Transistors Fabricated by Radio-Frequency Sputtering. J. Electrochem. Soc. 2008, 155, H383. [Google Scholar] [CrossRef]

- Yao, Q.J.; Li, D.J. Fabrication and property study of thin film transistor using rf sputtered ZnO as channel layer. J. Non-Cryst. Solids 2005, 351, 3191–3194. [Google Scholar] [CrossRef]

- Barquinha, P.; Pereira, L.; Gonçalves, G.; Kuscer, D.; Kosec, M.; Vilà, A.; Olziersky, A.; Morante, J.R.; Martins, R.; Fortunato, E. Low-temperature sputtered mixtures of high-κ and high bandgap dielectrics for GIZO TFTs. J. Soc. Inf. Disp. 2010, 18, 762. [Google Scholar] [CrossRef]

- Yabuta, H.; Sano, M.; Abe, K.; Aiba, T.; Den, T.; Kumomi, H.; Nomura, K.; Kamiya, T.; Hosono, H. High-mobility thin-film transistor with amorphous InGaZnO4 channel fabricated by room temperature rf-magnetron sputtering. Appl. Phys. Lett. 2006, 89, 112123. [Google Scholar] [CrossRef]

- Kumomi, H.; Nomura, K.; Kamiya, T.; Hosono, H. Amorphous oxide channel TFTs. Thin Solid Film. 2008, 516, 1516–1522. [Google Scholar] [CrossRef]

- Hosono, H. Ionic amorphous oxide semiconductors: Material design, carrier transport, and device application. J. Non-Cryst. Solids 2006, 352, 851–858. [Google Scholar] [CrossRef]

- Lee, J.S.; Chang, S.; Koo, S.M.; Lee, S.Y. High-performance a-IGZO TFT with ZrO2 gate dielectric fabricated at room temperature. IEEE Electron. Device Lett. 2010, 31, 225–227. [Google Scholar]

- Mohsenifar, S.; Shahrokhabadi, M.H. Gate Stack High- κ Materials for Si-Based MOSFETs Past, Present, and Futures. Microelectron. Solid State Electron. 2015, 4, 12–24. [Google Scholar]

- Wilk, G.D.; Wallace, R.M.; Anthony, J.M. High-κ gate dielectrics: Current status and materials properties considerations. J. Appl. Phys. 2001, 89, 5243–5275. [Google Scholar] [CrossRef]

- Wager, J.F.; Keszler, D.A.; Presley, R.E. Transparent Circuits. In Transparent Electronics; Springer: Boston, MA, USA, 2008; pp. 153–182. ISBN 9780387723419. [Google Scholar]

- Hays, D.C.; Gila, B.P.; Pearton, S.J.; Ren, F. Energy band offsets of dielectrics on InGaZnO4. Appl. Phys. Rev. 2017, 4. [Google Scholar] [CrossRef] [Green Version]

- Fortunato, E.; Barquinha, P.; Martins, R. Oxide Semiconductor Thin-Film Transistors: A Review of Recent Advances. Adv. Mater. 2012, 24, 2945–2986. [Google Scholar] [CrossRef] [PubMed]

- Kim, I.-D.; Lim, M.-H.; Kang, K.; Kim, H.-G.; Choi, S.-Y. Room temperature fabricated ZnO thin film transistor using high-K Bi1.5Zn1.0Nb1.5O7 gate insulator prepared by sputtering. Appl. Phys. Lett. 2006, 89, 022905. [Google Scholar] [CrossRef]

- Kim, J.B.; Fuentes-Hernandez, C.; Kippelen, B. High-performance InGaZnO thin-film transistors with high- k amorphous Ba0.5Sr0.5TiO3 gate insulator. Appl. Phys. Lett. 2008, 93, 3–6. [Google Scholar] [CrossRef] [Green Version]

- Kim, D.H.; Cho, N.G.; Kim, H.-G.; Kim, H.-S.; Hong, J.-M.; Kim, I.-D. Low voltage operating InGaZnO4 thin film transistors using high-k MgO–Ba0.6Sr0.4TiO3 composite gate dielectric on plastic substrate. Appl. Phys. Lett. 2008, 93, 032901. [Google Scholar] [CrossRef]

- Pei, Z.L.; Pereira, L.; Gonçalves, G.; Barquinha, P.; Franco, N.; Alves, E.; Rego, A.M.B.; Martins, R.; Fortunato, E. Room-Temperature Cosputtered HfO2–Al2O3 Multicomponent Gate Dielectrics. Electrochem. Solid-State Lett. 2009, 12, G65. [Google Scholar] [CrossRef]

- Yuan, L.; Zou, X.; Fang, G.; Wan, J.; Zhou, H.; Zhao, X. High-performance amorphous indium gallium zinc oxide thin-film transistors with HfOxNy/HfO2/HfOxNy tristack gate dielectrics. IEEE Electron Device Lett. 2011, 32, 42–44. [Google Scholar] [CrossRef]

- Su, L.-Y.; Lin, H.-K.; Hung, C.-C.; Huang, J. Role of HfO2/SiO2 Gate Dielectric on the Reduction of Low-Frequent Noise and the Enhancement of a-IGZO TFT Electrical Performance. J. Disp. Technol. 2012, 8, 695–698. [Google Scholar]

- Hsu, H.H.; Chang, C.Y.; Cheng, C.H. A flexible IGZO thin-film transistor with stacked TiO2-based dielectrics fabricated at room temperature. IEEE Electron Device Lett. 2013, 34, 768–770. [Google Scholar] [CrossRef]

- Heo, J.; Park, S.Y.; Kim, J.W.; Song, S.; Yoon, Y.J.; Jeong, J.; Jang, H.; Lee, K.T.; Seo, J.H.; Walker, B.; et al. Implementation of Low-Power Electronic Devices Using Solution-Processed Tantalum Pentoxide Dielectric. Adv. Funct. Mater. 2018, 28, 1704215. [Google Scholar] [CrossRef]

- Park, S.Y.; Heo, J.; Yoon, Y.J.; Kim, J.W.; Jang, H.; Walker, B.; Kim, J.Y. Synergistic combination of amorphous indium oxide with tantalum pentoxide for efficient electron transport in low-power electronics. J. Mater. Chem. C 2019, 7, 4559–4566. [Google Scholar] [CrossRef]

- Carlos, E.; Branquinho, R.; Kiazadeh, A.; Martins, J.; Barquinha, P.; Martins, R.; Fortunato, E. Boosting Electrical Performance of High-κ Nanomultilayer Dielectrics and Electronic Devices by Combining Solution Combustion Synthesis and UV Irradiation. ACS Appl. Mater. Interfaces 2017, 9, 40428–40437. [Google Scholar] [CrossRef] [PubMed]

- Hwang, B.U.; Kim, D.I.; Cho, S.W.; Yun, M.G.; Kim, H.J.; Kim, Y.J.; Cho, H.K.; Lee, N.E. Role of ultrathin Al2O3 layer in organic/inorganic hybrid gate dielectrics for flexibility improvement of InGaZnO thin film transistors. Org. Electron. Phys. Mater. Appl. 2014, 15, 1458–1464. [Google Scholar] [CrossRef]

- Nomura, K.; Aoki, T.; Nakamura, K.; Kamiya, T.; Nakanishi, T.; Hasegawa, T.; Kimura, M.; Kawase, T.; Hirano, M.; Hosono, H. Three-dimensionally stacked flexible integrated circuit: Amorphous oxide/polymer hybrid complementary inverter using n-type a-In–Ga–Zn–O and p-type poly-(9,9-dioctylfluorene-co-bithiophene) thin-film transistors. Appl. Phys. Lett. 2010, 96, 263509. [Google Scholar] [CrossRef]

- Correia, A.P.P. A Second-Order ΣΔ ADC Using Sputtered IGZO TFTs with Multilayer Dielectric. Master’s Thesis, NOVA School of Science and Technology, NOVA University Lisbon, Lisbon, Portugal, 2014. [Google Scholar]

- Barradas, N.P.; Jeynes, C.; Webb, R.P. Simulated annealing analysis of Rutherford backscattering data. Appl. Phys. Lett. 1997, 71, 291–293. [Google Scholar] [CrossRef] [Green Version]

- Jellison, G.E.; Modine, F.A. Parameterization of the optical functions of amorphous materials in the interband region. Appl. Phys. Lett. 1996, 69, 371–373. [Google Scholar] [CrossRef]

- Riekkinen, T. Reactively sputtered tantalum pentoxide thin films for integrated capacitors. Microelectron. Eng. 2003, 70, 392–397. [Google Scholar] [CrossRef]

- Gonçalves, T.D.T. Implementation of X-Ray Reflectivity on the Characterization of Ultra-Thin Films for Memory Devices. Master’s Thesis, NOVA School of Science and Technology, NOVA University Lisbon, Lisbon, Portugal, 2018. [Google Scholar]

- Petersen, K.E. Dynamic micromechanics on silicon: Techniques and devices. IEEE Trans. Electron Devices 1978, 25, 1241–1250. [Google Scholar] [CrossRef]

- Cusick, A.B.; Lang, M.; Zhang, F.; Sun, K.; Li, W.; Kluth, P.; Trautmann, C.; Ewing, R.C. Amorphization of Ta2O5 under swift heavy ion irradiation. Nucl. Instrum. Methods Phys. Res. Sect. B Beam Interact. Mater. At. 2017, 407, 25–33. [Google Scholar] [CrossRef]

- Correia, A.P.P.; Cândido Barquinha, P.M.; Goes, J.C.d.P. A Second-Order ΣΔ ADC Using Sputtered IGZO TFTs; Springer Briefs in Electrical and Computer Engineering; Springer International Publishing: Cham, Switzerland, 2016; ISBN 978-3-319-27190-3. [Google Scholar]

- Chiu, F. A Review on Conduction Mechanisms in Dielectric Films. Adv. Mater. Sci. Eng. 2014, 2014. [Google Scholar] [CrossRef] [Green Version]

- Demiryont, H.; Sites, J.R.; Geib, K. Effects of oxygen content on the optical properties of tantalum oxide films deposited by ion-beam sputtering. Appl. Opt. 1985, 24, 490. [Google Scholar] [CrossRef]

- Corbella, C.; Vives, M.; Pinyol, A.; Porqueras, I.; Person, C.; Bertran, E. Influence of the porosity of RF sputtered Ta2O5 thin films on their optical properties for electrochromic applications. Solid State Ion. 2003, 165, 15–22. [Google Scholar] [CrossRef]

- Martins, J.; Bahubalindruni, P.; Rovisco, A.; Kiazadeh, A.; Martins, R.; Fortunato, E.; Barquinha, P. Bias Stress and Temperature Impact on InGaZnO TFTs and Circuits. Materials 2017, 10, 680. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Bahubalindruni, P.G.; Tiwari, B.; Pereira, M.; Santa, A.; Martins, J.; Rovisco, A.I.B.; Tavares, V.M.G.; Martins, R.; Fortunato, E.; Barquinha, P. Rail-to-Rail Timing Signals Generation Using InGaZnO TFTs For Flexible X-Ray Detector. IEEE J. Electron. Devices Soc. 2020, 8, 157–162. [Google Scholar] [CrossRef]

- Xu, W.; Dai, M.; Liang, L.; Liu, Z.; Sun, X.; Wan, Q.; Cao, H. Anomalous bias-stress-induced unstable phenomena of InZnO thin-film transistors using Ta2O5 gate dielectric. J. Phys. D Appl. Phys. 2012, 45, 205103. [Google Scholar] [CrossRef]

- Liu, J.; Buchholz, D.B.; Hennek, J.W.; Chang, R.P.H.; Facchetti, A.; Marks, T.J. All-amorphous-oxide transparent, flexible thin-film transistors. Efficacy of bilayer gate dielectrics. J. Am. Chem. Soc. 2010, 132, 11934–11942. [Google Scholar] [CrossRef] [PubMed]

- Jin, J.W.; Nathan, A.; Barquinha, P.; Pereira, L.; Fortunato, E.; Martins, R.; Cobb, B. Interpreting anomalies observed in oxide semiconductor TFTs under negative and positive bias stress. AIP Adv. 2016, 6. [Google Scholar] [CrossRef]

- Sato, M.; Kamiyama, S.; Matsuki, T.; Ishikawa, D.; Ono, T.; Morooka, T.; Yugami, J.; Ikeda, K.; Ohji, Y. Study of a negative threshold voltage shift in positive bias temperature instability and a positive threshold voltage shift the negative bias temperature instability of yttrium-doped HfO2 gate dielectrics. Jpn. J. Appl. Phys. 2010, 49. [Google Scholar] [CrossRef]

- Görrn, P.; Hölzer, P.; Riedl, T.; Kowalsky, W.; Wang, J.; Weimann, T.; Hinze, P.; Kipp, S. Stability of transparent zinc tin oxide transistors under bias stress. Appl. Phys. Lett. 2007, 90. [Google Scholar] [CrossRef]

- Alam, M.A.; Kufluoglu, H.; Varghese, D.; Mahapatra, S. A comprehensive model for PMOS NBTI degradation: Recent progress. Microelectron. Reliab. 2007, 47, 853–862. [Google Scholar] [CrossRef]

- Aleksandrov, O.V. Model of the Negative-Bias Temperature Instability of p-MOS Transistors. Semiconductors 2020, 54, 233–239. [Google Scholar] [CrossRef]

- Duggan, M.; Saito, T.; Niwa, T. Ionic conductivity of tantalum oxide by rf sputtering. Solid State Ion. 1993, 62, 15–20. [Google Scholar] [CrossRef]

- Chen, J.-Y.; Huang, C.-W.; Chiu, C.-H.; Huang, Y.-T.; Wu, W.-W. Switching Kinetic of VCM-Based Memristor: Evolution and Positioning of Nanofilament. Adv. Mater. 2015, 27, 5028–5033. [Google Scholar] [CrossRef] [PubMed]

- Ji, K.H.; Kim, J.-I.; Jung, H.Y.; Park, S.Y.; Choi, R.; Mo, Y.G.; Jeong, J.K. Comprehensive studies of the degradation mechanism in amorphous InGaZnO transistors by the negative bias illumination stress. Microelectron. Eng. 2011, 88, 1412–1416. [Google Scholar] [CrossRef]

- Kita, K.; Toriumi, A. Origin of electric dipoles formed at high-k/SiO2 interface. Appl. Phys. Lett. 2009, 94, 132902. [Google Scholar] [CrossRef]

- Toriumi, A.K.; Nabatame, T. Anomalous VFB Shift in High-k Gate Stacks—Is its origin at the top or bottom interface? ECS Trans. 2009, 25, 3–16. [Google Scholar] [CrossRef]

- Kamimuta, Y.; Iwamoto, K.; Nunoshige, Y.; Hirano, A.; Mizubayashi, W.; Watanabe, Y.; Migita, S.; Ogawa, A.; Ota, H.; Nabatame, T.; et al. Comprehensive Study of VFB Shift in High-k CMOS—Dipole Formation, Fermi-level Pinning and Oxygen Vacancy Effect. In Proceedings of the 2007 IEEE International Electron Devices Meeting, Washington, DC, USA, 10–12 December 2007; Volume 2, pp. 341–344. [Google Scholar]

- Shiraishi, K.; Yamada, K.; Torii, K.; Akasaka, Y.; Nakajima, K.; Konno, M.; Chikyow, T.; Kitajima, H.; Arikado, T.; Nara, Y. Oxygen-vacancy-induced threshold voltage shifts in Hf-related high-k gate stacks. Thin Solid Film. 2006, 508, 305–310. [Google Scholar] [CrossRef]

- Guo, Y.; Robertson, J. Materials selection for oxide-based resistive random access memories. Appl. Phys. Lett. 2014, 105, 223516. [Google Scholar] [CrossRef]

- Tajima, K.; Yamada, Y.; Bao, S.; Okada, M.; Yoshimura, K. Proton conductive tantalum oxide thin film deposited by reactive DC magnetron sputtering for all-solid-state switchable mirror. J. Phys. Conf. Ser. 2008, 100, 082017. [Google Scholar] [CrossRef]

- Banger, K.; Warwick, C.; Lang, J.; Broch, K.; Halpert, J.E.; Socratous, J.; Brown, A.; Leedham, T.; Sirringhaus, H. Identification of dipole disorder in low temperature solution processed oxides: Its utility and suppression for transparent high performance solution-processed hybrid electronics. Chem. Sci. 2016, 7, 6337–6346. [Google Scholar] [CrossRef] [Green Version]

- Zhuang, X.; Patel, S.; Zhang, C.; Wang, B.; Chen, Y.; Liu, H.; Dravid, V.P.; Yu, J.; Hu, Y.-Y.; Huang, W.; et al. Frequency-Agile Low-Temperature Solution-Processed Alumina Dielectrics for Inorganic and Organic Electronics Enhanced by Fluoride Doping. J. Am. Chem. Soc. 2020, 142, 12440–12452. [Google Scholar] [CrossRef]

| Name | Power in Ta2O5 Target (W) | Ta2O5 Content (mol.%) | SiO2 Content (mol.%) | εr |

|---|---|---|---|---|

| T39S61 | 50 | 38.8 | 61.2 | 10.0 |

| T60S40 | 75 | 59.9 | 40.1 | 13.2 |

| T69S31 | 100 | 68.6 | 31.4 | 15.7 |

| T74S26 | 125 | 73.9 | 26.1 | 16.4 |

| T75S25 | 150 | 75.0 | 25.0 | 17.8 |

| Ta2O5 | 100 | 100.0 | 0.0 | 22.7 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Martins, J.; Kiazadeh, A.; Pinto, J.V.; Rovisco, A.; Gonçalves, T.; Deuermeier, J.; Alves, E.; Martins, R.; Fortunato, E.; Barquinha, P. Ta2O5/SiO2 Multicomponent Dielectrics for Amorphous Oxide TFTs. Electron. Mater. 2021, 2, 1-16. https://doi.org/10.3390/electronicmat2010001

Martins J, Kiazadeh A, Pinto JV, Rovisco A, Gonçalves T, Deuermeier J, Alves E, Martins R, Fortunato E, Barquinha P. Ta2O5/SiO2 Multicomponent Dielectrics for Amorphous Oxide TFTs. Electronic Materials. 2021; 2(1):1-16. https://doi.org/10.3390/electronicmat2010001

Chicago/Turabian StyleMartins, Jorge, Asal Kiazadeh, Joana V. Pinto, Ana Rovisco, Tiago Gonçalves, Jonas Deuermeier, Eduardo Alves, Rodrigo Martins, Elvira Fortunato, and Pedro Barquinha. 2021. "Ta2O5/SiO2 Multicomponent Dielectrics for Amorphous Oxide TFTs" Electronic Materials 2, no. 1: 1-16. https://doi.org/10.3390/electronicmat2010001

APA StyleMartins, J., Kiazadeh, A., Pinto, J. V., Rovisco, A., Gonçalves, T., Deuermeier, J., Alves, E., Martins, R., Fortunato, E., & Barquinha, P. (2021). Ta2O5/SiO2 Multicomponent Dielectrics for Amorphous Oxide TFTs. Electronic Materials, 2(1), 1-16. https://doi.org/10.3390/electronicmat2010001