A Multipurpose CMOS Platform for Nanosensing

Abstract

:1. Introduction

2. The Micro-for-Nano Approach

3. Results and Discussions

3.1. The Low-Cost CMOS Post-Processing

3.2. The Configurable Micro-for-Nano Sensing-Array

3.3. Real-Time Portable Electronic Interface

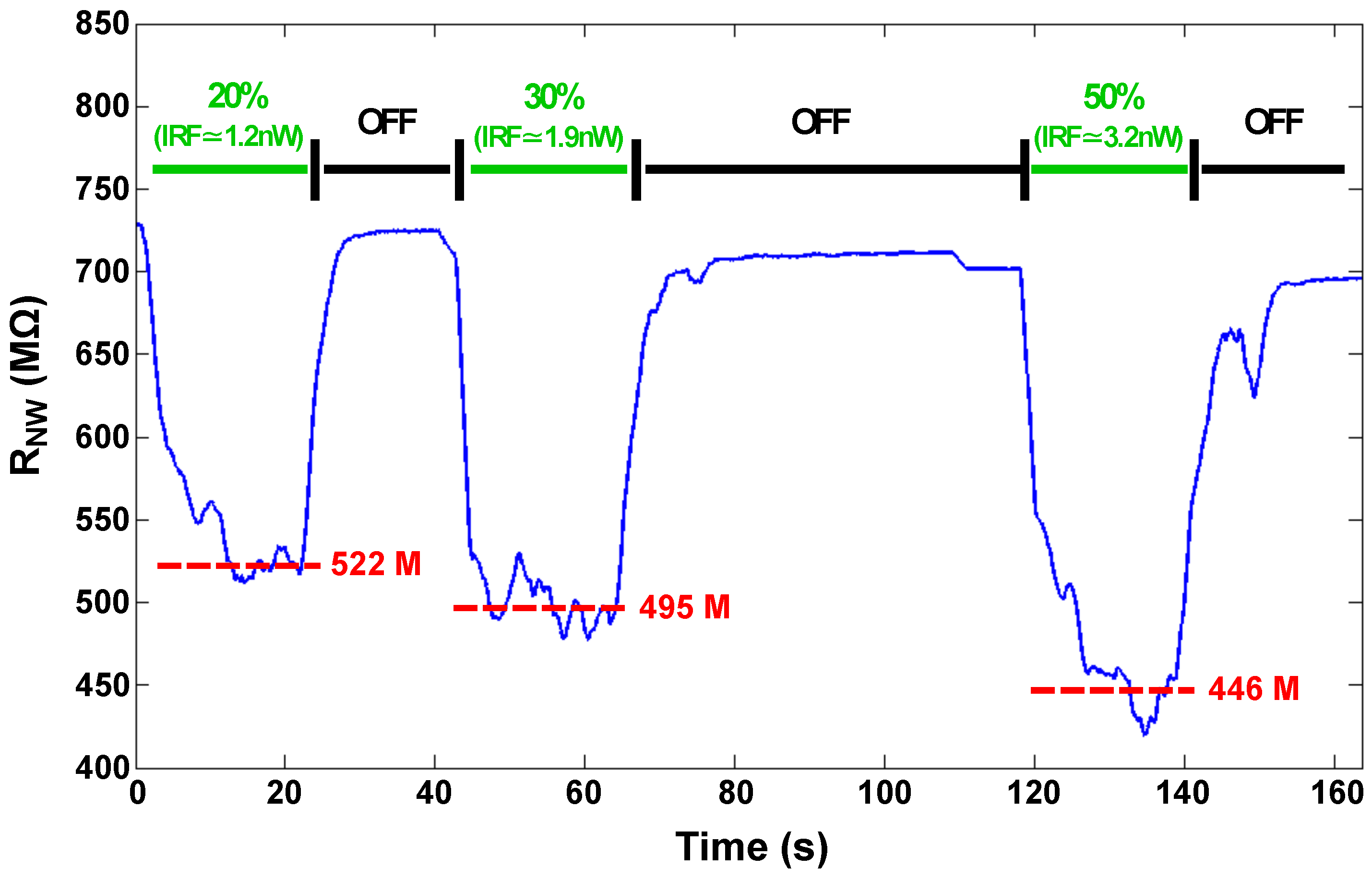

3.4. Experiments Using Single ZnO-NWs

4. Conclusions

Supplementary Materials

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Ragman, S.; Yusof, N.A.; Hashim, U.; Nor, N. Design and fabrication of silicon nanowire based sensor. Int. J. Electrochem. Sci. 2013, 8, 10946–10960. [Google Scholar]

- Das, S.N.; Moon, K.J.; Kar, J.P.; Choi, J.H.; Xiong, J.; Lee, T.I.; Myoung, J.M. ZnO single nanowire-based UV detectors. Appl. Phys. Lett. 2010, 97. [Google Scholar] [CrossRef]

- Du, J.; Liang, D.; Tang, H.; Gao, X.P. InAs Nanowire Transistors as Gas Sensor and the Response Mechanism. Nano Lett. 2009, 9, 4348–4351. [Google Scholar] [CrossRef] [PubMed]

- Lee, H.; Lee, H.; Woo, J.K.; Kim, S.; Park, Y.J.; Kim, S. A CMOS readout integrated circuit with wide dynamic range for a CNT bio-sensor array system. In Proceedings of the International Symposium on Low Power Electronics and Design (ISLPED), Fukuoka, Japan, 1–3 August 2011; pp. 357–360.

- Nazarov, A.; Balestra, F.; Kilchytska, V.; Flandre, D. Functional Nanomaterials and Devices for Electronics, Sensors and Energy Harvesting; Springer: Zurich, Switzerland, 2014. [Google Scholar]

- Michimata, K.; Kotani, H.; Watanabe, T.; Funayama, H.; Murakami, S.; Shimomura, K.; Waho, T. Heterogeneous integration of an InAs nanowire with energy-efficient CMOS delta-sigma modulator. In Proceedings of the IEEE Sensors, Baltimore, MD, USA, 3–6 November 2013; pp. 1–4.

- Narayanan, A.; Dan, Y.; Deshpande, V.; Di Lello, N.; Evoy, S.; Raman, S. Dielectrophoretic integration of nanodevices with CMOS VLSI circuitry. IEEE Trans. Nanotechnol. 2006, 5, 101–109. [Google Scholar] [CrossRef]

- Puppo, F.; Doucey, M.A.; Moh, T.; Pandraud, G.; Sarro, P.; De Micheli, G.; Carrara, S. Femto-molar sensitive field effect transistor biosensors based on silicon nanowires and antibodies. In Proceedings of the IEEE Sensors, Baltimore, MD, USA, 3–6 November 2013; pp. 1–4.

- Huang, C.W.; Huang, Y.J.; Yen, P.W.; Tsai, H.H.; Liao, H.H.; Juang, Y.Z.; Lu, S.S.; Lin, C.T. A CMOS wireless biomolecular sensing system-on-chip based on polysilicon nanowire technology. Lab Chip 2013, 13, 4451–4459. [Google Scholar] [CrossRef] [PubMed]

- Barth, S.; Jimenez-Diaz, R.; Sama, J.; Daniel Prades, J.; Gracia, I.; Santander, J.; Cane, C.; Romano-Rodriguez, A. Localized growth and in situ integration of nanowires for device applications. Chem. Commun. 2012, 48, 4734–4736. [Google Scholar] [CrossRef] [PubMed]

- Zhang, Y.; Lee, C.T. Negative Differential Resistance in ZnO Nanowires Bridging Two Metallic Electrodes. Nanoscale Res. Lett. 2010, 5, 1492–1495. [Google Scholar] [CrossRef] [PubMed]

- Gamerith, S.; Klug, A.; Scheiber, H.; Scherf, U.; Moderegger, E.; List, E.J. Direct Ink-Jet Printing of Ag–Cu Nanoparticle and Ag-Precursor Based Electrodes for OFET Applications. Adv. Funct. Mater. 2007, 17, 3111–3118. [Google Scholar] [CrossRef]

- Ru, C.; Luo, J.; Xie, S.; Sun, Y. A review of non-contact micro-and nano-printing technologies. J. Micromech. Microeng. 2014, 24, 053001. [Google Scholar] [CrossRef]

- Choi, J.Y.; Das, S.; Theodore, N.D.; Kim, I.; Honsberg, C.; Choi, H.W.; Alford, T. Advances in 2D/3D printing of functional nanomaterials and their applications. ECS J. Solid State Sci. Technol. 2015, 4, P3001–P3009. [Google Scholar] [CrossRef]

- Burg, B.R.; Bianco, V.; Schneider, J.; Poulikakos, D. Electrokinetic framework of dielectrophoretic deposition devices. J. Appl. Phys. 2010, 107, 1–11. [Google Scholar] [CrossRef]

- Liu, Y.; Chung, J.H.; Liu, W.K.; Ruoff, R.S. Dielectrophoretic Assembly of Nanowires. J. Phys. Chem. B 2006, 110, 14098–14106. [Google Scholar] [CrossRef] [PubMed]

- Wang, D.; Zhu, R.; Zhou, Z.; Ye, X. Controlled assembly of zinc oxide nanowires using dielectrophoresis. Appl. Phys. Lett. 2007, 90, 1–4. [Google Scholar] [CrossRef]

- Bonanno, A.; Morello, M.; Crepaldi, M.; Sanginario, A.; Benetto, S.; Cauda, V.; Civera, P.; Demarchi, D. A Low-Power 0.13 μm CMOS IC for ZnO-Nanowire Assembly and Nanowire-Based UV Sensor Interface. IEEE Sens. J. 2015, 15, 4203–4212. [Google Scholar] [CrossRef]

- Green, T.A. Gold electrodeposition for microelectronic, optoelectronic and microsystem applications. Gold Bull. 2007, 40, 105–114. [Google Scholar] [CrossRef]

- Ko, J.W.; Koo, H.C.; Kim, D.W.; Seo, S.M.; Kang, T.J.; Kwon, Y.; Yoon, J.L.; Cheon, J.H.; Kim, Y.H.; Kim, J.J.; Park, Y.J. Electroless Gold Plating on Aluminum Patterned Chips for CMOS-Based Sensor Applications. J. Electrochem. Soc. 2010, 157, D46–D49. [Google Scholar] [CrossRef]

- Hwang, S.; LaFratta, C.; Agarwal, V.; Yu, X.; Walt, D.; Sonkusale, S. CMOS Microelectrode Array for Electrochemical Lab-on-a-Chip Applications. IEEE Sens. J. 2009, 9, 609–615. [Google Scholar] [CrossRef]

- Abdullah, S.; Ahmad, I.; Jalar, A. The Effect of Number of Zincation in Electroless Nickel Immersion Gold (ENIG) Under Bump Metallurgy (UBM) on Reliability in Microelectronics Packaging. In Proceedings of the 25th International Conference on Microelectronics, Nis, Serbia, 14–17 May 2006; pp. 567–570.

- Arshad, M.K.M.; Jalar, A.; Ahmad, I.; Omar, G. The characterization of Al Bond pad surface treatment in Electroless Nickel Immersion Gold (ENIG) deposition. Am. J. Appl. Sci. 2007, 4, 133–141. [Google Scholar] [CrossRef]

- Chen, C.L.; Agarwal, V.; Sonkusale, S.; Dokmeci, M.R. Integration of Single-Walled Carbon Nanotubes on to CMOS Circuitry with Parylene-C Encapsulation. In Proceedings of the 8th IEEE Conference on Nanotechnology (NANO), Arlington, TX, USA, 18–21 August 2008; pp. 480–483.

- Yurish, S. Extension of IEEE 1451 Standard to Quasi-Digital Sensors. In Proceedings of the IEEE Sensors Applications Symposium, San Diego, CA, USA, 6–8 February 2007; pp. 1–6.

- Chang, S.J.; Hsueh, T.J.; Hsu, C.L.; Lin, Y.R.; Chen, I.C.; Huang, B.R. A ZnO nanowire vacuum pressure sensor. Nanotechnology 2008, 19. [Google Scholar] [CrossRef] [PubMed]

- Seo, Y.K.; Kumar, S.; Kim, G.H. Photoconductivity characteristics of ZnO nanoparticles assembled in nanogap electrodes for portable photodetector applications. Physica E 2010, 42, 1163–1166. [Google Scholar] [CrossRef]

- Luo, L.; Lin, L. Self-Assembled ZNO Nanowires Via Local Vapor Transport Synthesis as UV Sensor. In Proceedings of the 14th International Conference on Solid-State Sensors, Actuators and Microsystems (TRANSDUCERS ’07), Lyon, France, 10–14 June 2007; pp. 403–406.

- Cauda, V.; Motto, P.; Perrone, D.; Piccinini, G.; Demarchi, D. pH-triggered conduction of amine-functionalized single ZnO wire integrated on a customized nanogap electronic platform. Nanoscale Res. Lett. 2014, 9. [Google Scholar] [CrossRef] [PubMed]

- Motto, P.; Cauda, V.; Stassi, S.; Canavese, G.; Demarchi, D. Functionalized single ZnO-metal junction as a pH sensor. In Proceedings of the IEEE Sensors, Baltimore, MD, USA, 3–6 November 2013; pp. 1–4.

- Kiasari, N.; Servati, P. Dielectrophoresis-Assembled ZnO Nanowire Oxygen Sensors. IEEE Electron Device Lett. 2011, 32, 982–984. [Google Scholar] [CrossRef]

- Pau, J.; Nunez, C.; Marin, A.; Ruiz, E.; Piqueras, J. Metal oxide nanowires as building blocks for light detectors, gas sensors and biosensors. In Proceedings of the Spanish Conference on Electron Devices (CDE), Valladolid, Spain, 12–14 February 2013; pp. 171–174.

- Niepelt, R.; Schröder, U.; Sommerfeld, J.; Slowik, I.; Rudolph, B.; Möller, R.; Seise, B.; Csaki, A.; Fritzsche, W.; Ronning, C. Biofunctionalization of zinc oxide nanowires for DNA sensory applications. Nanoscale Res. Lett. 2011, 6, 1–7. [Google Scholar] [CrossRef] [PubMed]

- Alenezi, M.R.; Henley, S.J.; Silva, S. On-chip fabrication of high performance nanostructured ZnO UV detectors. Sci. Rep. 2015, 5. [Google Scholar] [CrossRef] [PubMed]

- Kind, H.; Yan, H.; Messer, B.; Law, M.; Yang, P. Nanowire ultraviolet photodetectors and optical switches. Adv. Mater. 2002, 14, 158–160. [Google Scholar] [CrossRef]

- Sanginario, A.; Cauda, V.; Bonanno, A.; Bejtka, K.; Sapienza, S.; Demarchi, D. An electronic platform for real-time detection of bovine serum albumin by means of amine-functionalized zinc oxide microwires. RSC Adv. 2016, 6, 891–897. [Google Scholar] [CrossRef]

© 2016 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC-BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bonanno, A.; Sanginario, A.; Marasso, S.L.; Miccoli, B.; Bejtka, K.; Benetto, S.; Demarchi, D. A Multipurpose CMOS Platform for Nanosensing. Sensors 2016, 16, 2034. https://doi.org/10.3390/s16122034

Bonanno A, Sanginario A, Marasso SL, Miccoli B, Bejtka K, Benetto S, Demarchi D. A Multipurpose CMOS Platform for Nanosensing. Sensors. 2016; 16(12):2034. https://doi.org/10.3390/s16122034

Chicago/Turabian StyleBonanno, Alberto, Alessandro Sanginario, Simone L. Marasso, Beatrice Miccoli, Katarzyna Bejtka, Simone Benetto, and Danilo Demarchi. 2016. "A Multipurpose CMOS Platform for Nanosensing" Sensors 16, no. 12: 2034. https://doi.org/10.3390/s16122034