Mutually Coupled Time-to-Digital Converters (TDCs) for Direct Time-of-Flight (dTOF) Image Sensors ‡

Abstract

:1. Introduction

2. TDC Sharing

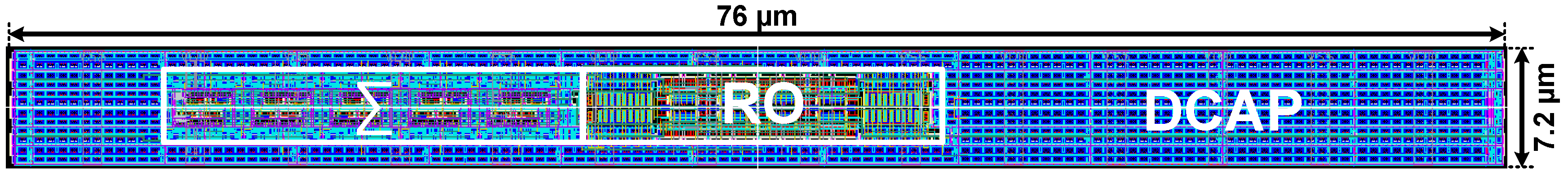

2.1. Power Consumption

2.2. Effects on Sensitivity

3. Synchronization

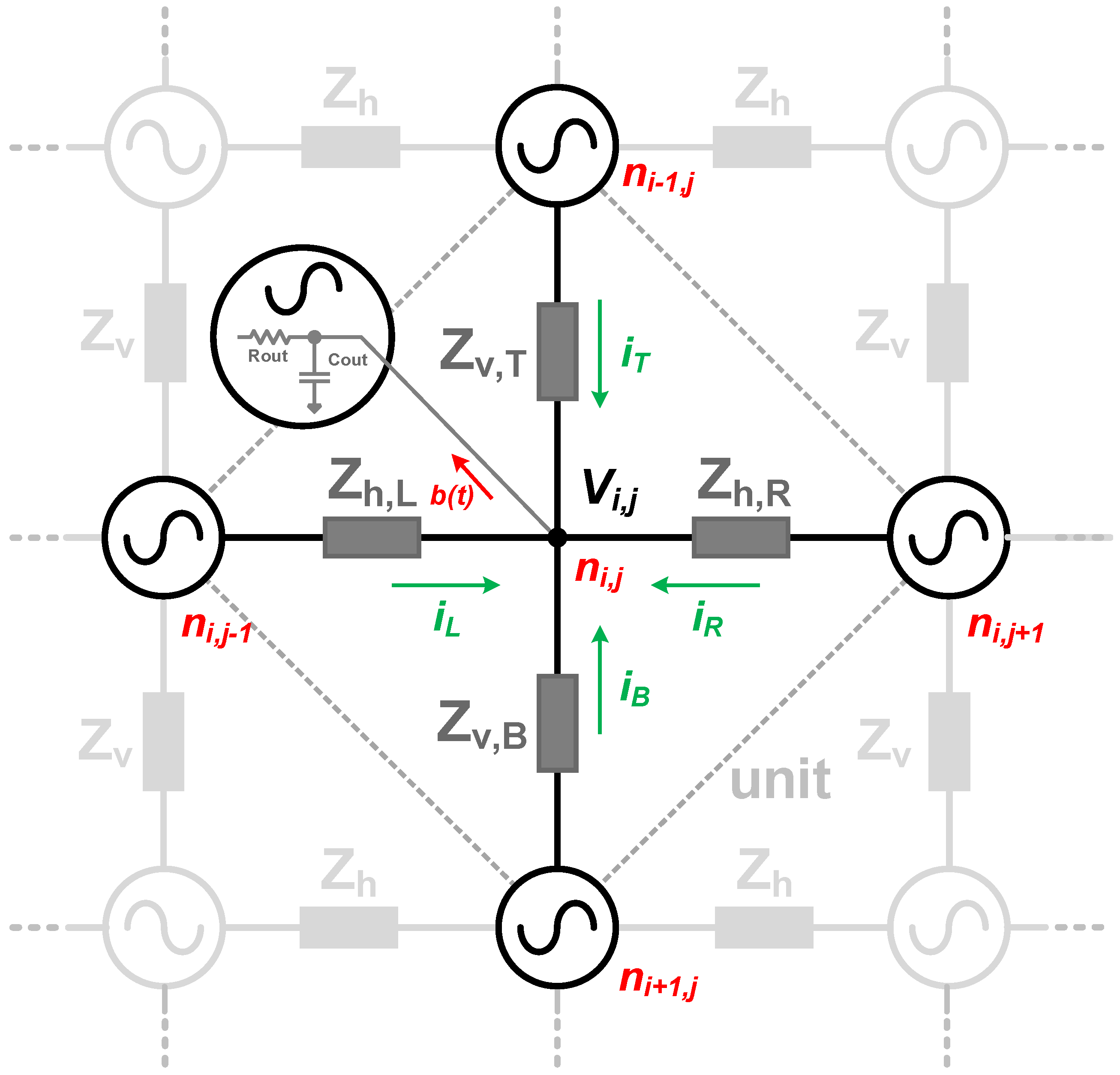

3.1. Non-Linear Modeling

3.2. SPICE-Compatible Model

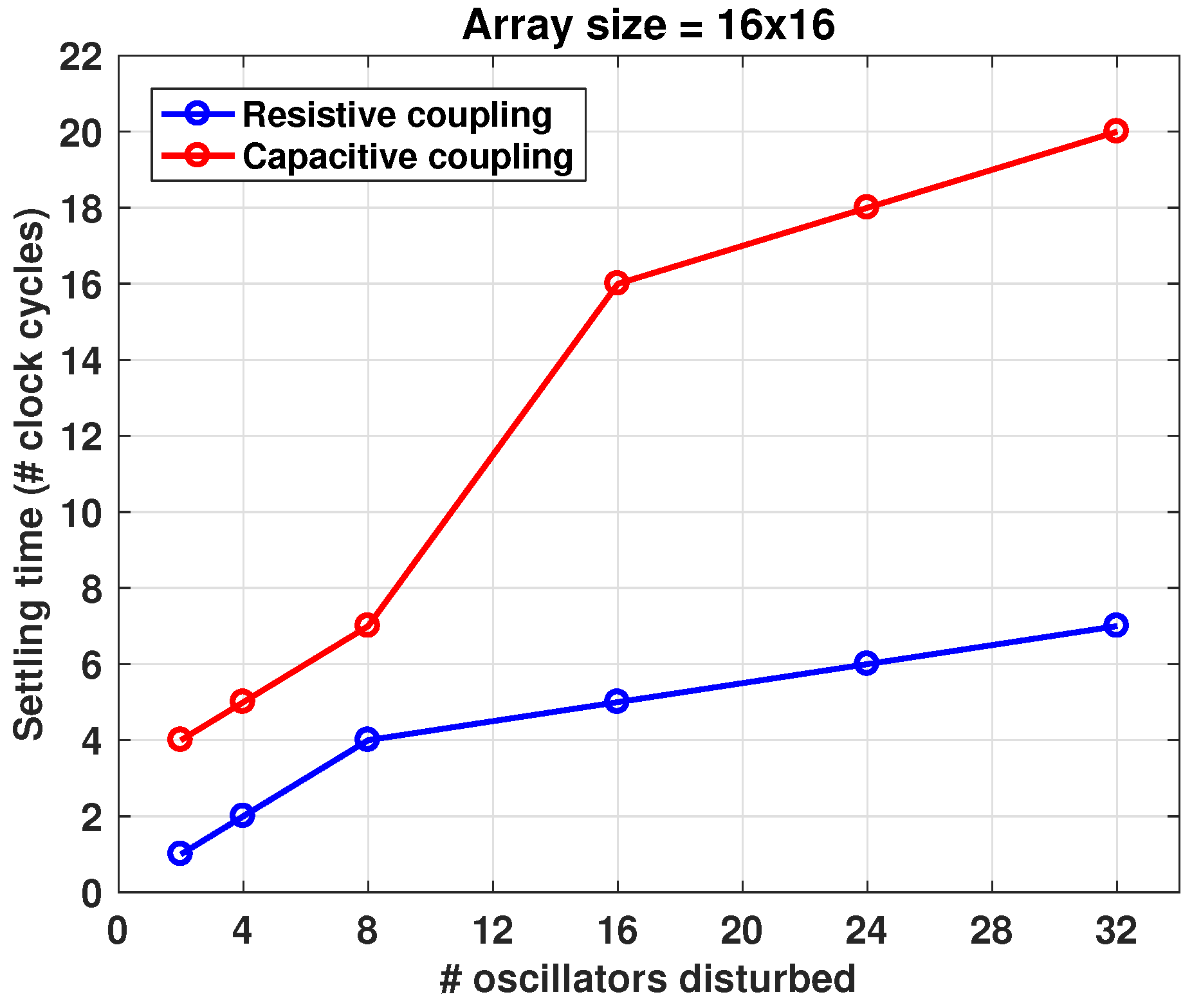

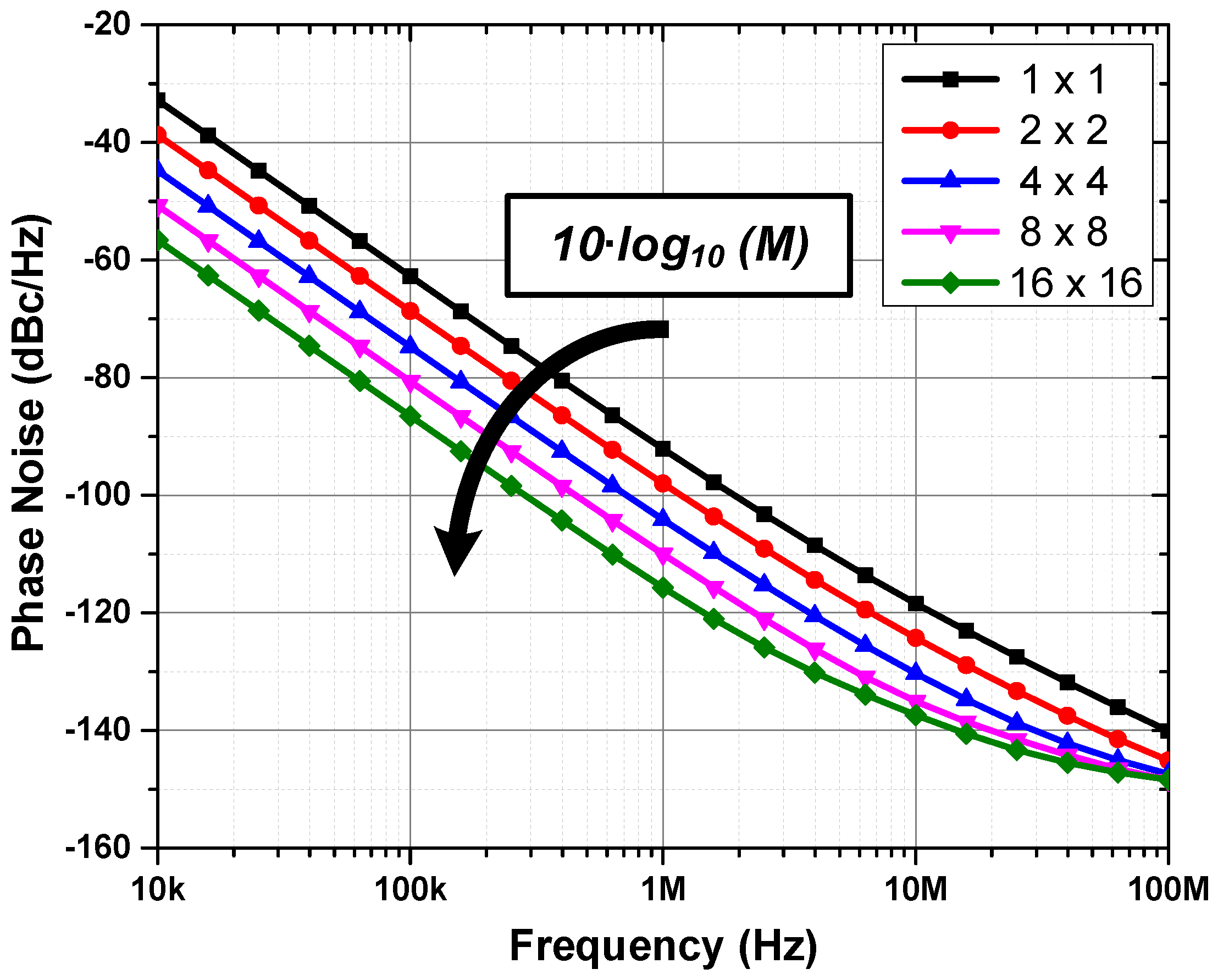

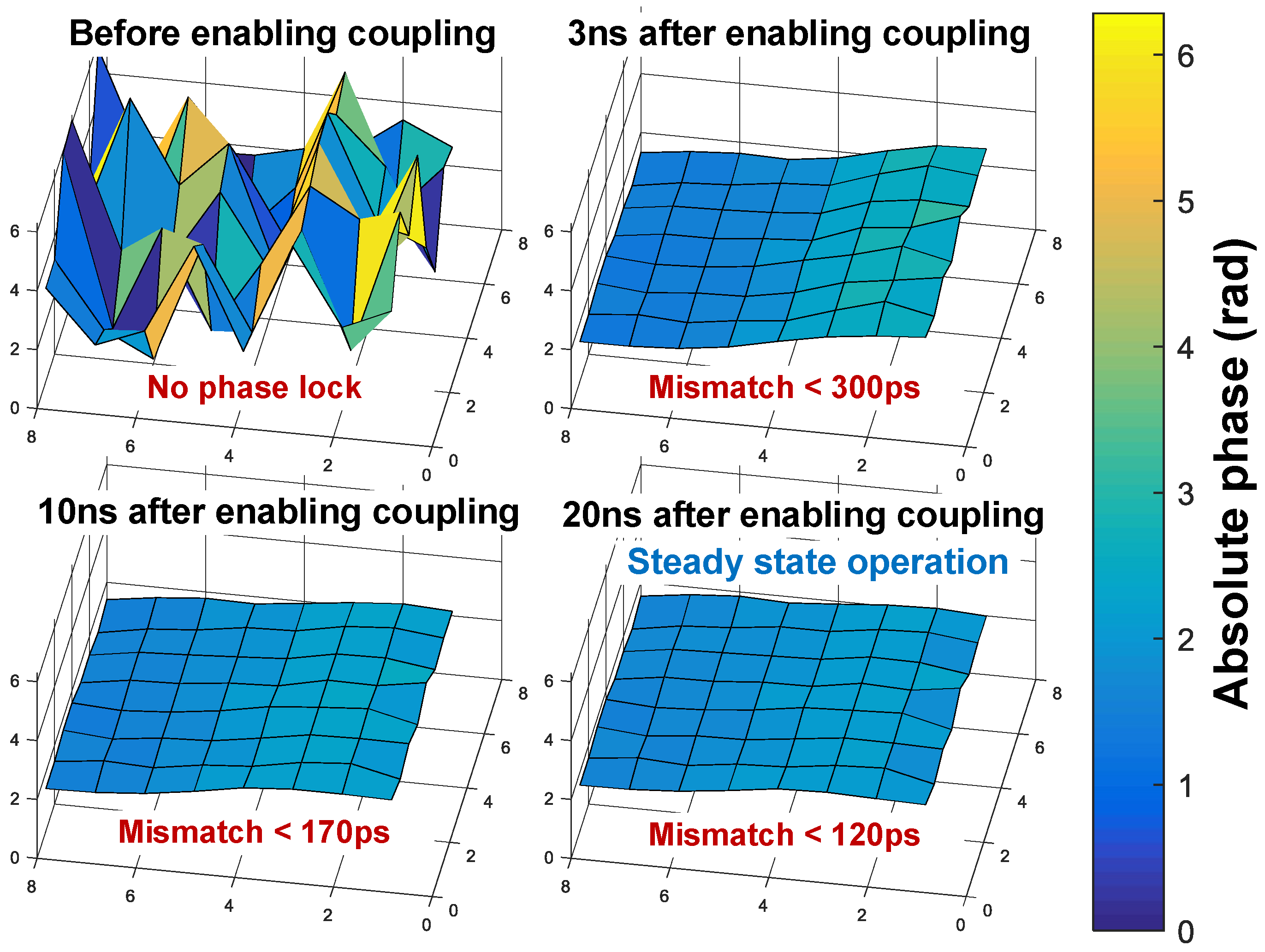

4. Results

5. Conclusions

6. Patents

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Abbreviations

| dTOF | Direct time-of-flight |

| PLL | Phase-locked loop |

| DLL | Delay-locked loop |

| TDC | Time-to-digital converter |

| RO | Ring oscillator |

| LSB | Least mean square |

| DNL | differential nonlinearity |

| INL | integral nonlinearity |

| SiPM | Silicon photomultiplier |

| TCSPC | Time-correlated single-photon counting |

| TTTR | Time-tagged time-resolved |

| SNR | Signal-to-noise ratio |

| FOV | Field of view |

| AR | Augmented reality |

| VR | Virtual reality |

| PET | Positron emission tomography |

| FLIM | Fluorescence lifetime imaging |

| LiDAR | Light detection and ranging |

| ADAS | Advanced driver-assistance system |

| AV | Autonomous vehicles |

| FIFO | First-in-first-out |

| RMS | Root mean square |

| SPAD | Single-photon avalanche diode |

| PVT | Process-voltage-temperature |

| ROIC | Readout integrated circuit |

Appendix A

References

- Charbon, E. Single-photon imaging in complementary metal oxide semiconductor processes. Philos. Trans. R. Soc. A 2014, 372, 20130100. [Google Scholar] [CrossRef] [PubMed]

- Ren, X.; Connolly, P.W.; Halimi, A.; Altmann, Y.; McLaughlin, S.; Gyongy, I.; Henderson, R.K.; Buller, G.S. High-resolution depth profiling using a range-gated CMOS SPAD quanta image sensor. Opt. Express 2018, 26, 5541–5557. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Gnecchi, S.; Jackson, C. A 1× 16 SiPM Array for Automotive 3D Imaging LiDAR Systems. In Proceedings of the 2017 International Image Sensor Workshop (IISW), Hiroshima, Japan, 30 May–2 June 2017; pp. 133–136. [Google Scholar]

- Veerappan, C.; Richardson, J.; Walker, R.; Li, D.U.; Fishburn, M.W.; Maruyama, Y.; Stoppa, D.; Borghetti, F.; Gersbach, M.; Henderson, R.K.; et al. A 160 × 128 single-photon image sensor with on-pixel 55ps 10b time-to-digital converter. In IEEE International Solid-State Circuits Conference Digest of Technical Papers; IEEE: Piscataway, NJ, USA, 2011; pp. 312–314. 55p. [Google Scholar]

- Wahl, M.; Rahn, H.J.; Gregor, I.; Erdmann, R.; Enderlein, J. Dead-time optimized time-correlated photon counting instrument with synchronized, independent timing channels. Rev. Sci. Instrum. 2007, 78, 033106. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Niclass, C.; Soga, M.; Charbon, E. 3D Imaging based on single photon detectors. Available online: https://infoscience.epfl.ch/record/125188 (accessed on 9 October 2018).

- Braga, L.H.; Pancheri, L.; Gasparini, L.; Perenzoni, M.; Walker, R.; Henderson, R.K.; Stoppa, D. A CMOS mini-SiPM detector with in-pixel data compression for PET applications. In Proceedings of the 2011 IEEE Nuclear Science Symposium Conference Record, Valencia, Spain, 23–29 October 2011; pp. 548–552. [Google Scholar]

- Suhling, K.; French, P.M.; Phillips, D. Time-resolved fluorescence microscopy. Photochem. Photobiol. Sci. 2005, 4, 13–22. [Google Scholar] [CrossRef] [PubMed]

- Stoppa, D.; Mosconi, D.; Pancheri, L.; Gonzo, L. Single-photon avalanche diode CMOS sensor for time-resolved fluorescence measurements. IEEE Sens. J. 2009, 9, 1084–1090. [Google Scholar] [CrossRef]

- Becker, W. Advanced Time-Correlated Single Photon Counting Applications; Springer: Berlin, Germany, 2015; Volume 111. [Google Scholar]

- Levinson, J.; Askeland, J.; Becker, J.; Dolson, J.; Held, D.; Kammel, S.; Kolter, J.Z.; Langer, D.; Pink, O.; Pratt, V.; et al. Towards fully autonomous driving: Systems and algorithms. In Proceedings of the 2011 IEEE Intelligent Vehicles Symposium (IV), Baden-Baden, Germany, 5–9 June 2011; pp. 163–168. [Google Scholar]

- Van de Beek, R.C.; Klumperink, E.A.; Vaucher, C.S.; Nauta, B. Low-jitter clock multiplication: A comparison between PLLs and DLLs. IEEE Trans. Circuits Syst. II 2002, 49, 555–566. [Google Scholar] [CrossRef]

- Razavi, B. A study of phase noise in CMOS oscillators. IEEE J. Solid-State Circuits 1996, 31, 331–343. [Google Scholar] [CrossRef]

- Niclass, C.; Favi, C.; Kluter, T.; Gersbach, M.; Charbon, E. A 128 × 128 Single-Photon Image Sensor with Column-Level 10-Bit Time-to-Digital Converter Array. IEEE J. Solid-State Circuits 2008, 43, 2977–2989. [Google Scholar] [CrossRef]

- Carimatto, A.; Mandai, S.; Venialgo, E.; Gong, T.; Borghi, G.; Schaart, D.R.; Charbon, E. A 67,392-SPAD PVTB-compensated multi-channel digital SiPM with 432 column-parallel 48ps 17b TDCs for endoscopic time-of-flight PET. In Proceedings of the 2015 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 22–26 February 2015; pp. 1–3. [Google Scholar]

- Niclass, C.; Ito, K.; Soga, M.; Matsubara, H.; Aoyagi, I.; Kato, S.; Kagami, M. Design and characterization of a 256 × 64-pixel single-photon imager in CMOS for a MEMS-based laser scanning time-of-flight sensor. Opt. Express 2012, 20, 11863–11881. [Google Scholar] [CrossRef] [PubMed]

- Al Abbas, T.; Dutton, N.A.; Almer, O.; Finlayson, N.; Della Rocca, F.M.; Henderson, R. A CMOS SPAD Sensor With a Multi-Event Folded Flash Time-to-Digital Converter for Ultra-Fast Optical Transient Capture. IEEE Sens. J. 2018, 18, 3163–3173. [Google Scholar] [CrossRef] [Green Version]

- Knoll, G.F. Radiation Detection and Measurement; John Wiley & Sons: Hoboken, NJ, USA, 2010. [Google Scholar]

- Lee, S.H.; Gardner, R.P. A new G–M counter dead time model. Appl. Radiat. Isot. 2000, 53, 731–737. [Google Scholar] [CrossRef]

- Braga, L.H.C.; Gasparini, L.; Grant, L.; Henderson, R.K.; Massari, N.; Perenzoni, M.; Stoppa, D.; Walker, R.J. A Fully Digital 8 × 16 SiPM Array for PET Applications with Per-Pixel TDCs and Real-Time Energy Output. IEEE J. Solid-State Circuits 2014, 49, 301–314. [Google Scholar] [CrossRef]

- Villa, F.; Lussana, R.; Bronzi, D.; Tisa, S.; Tosi, A.; Zappa, F.; Dalla Mora, A.; Contini, D.; Durini, D.; Weyers, S.; et al. CMOS imager with 1024 SPADs and TDCs for single-photon timing and 3-D time-of-flight. IEEE J. Sel. Top. Quantum Electron. 2014, 20, 364–373. [Google Scholar] [CrossRef]

- Ximenes, A.R.; Padmanabhan, P.; Lee, M.J.; Yamashita, Y.; Yaung, D.; Charbon, E. A 256 × 256 45/65 nm 3D-stacked SPAD-based direct TOF image sensor for LiDAR applications with optical polar modulation for up to 18.6 dB interference suppression. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 11–15 February 2018; pp. 96–98. [Google Scholar]

- Chien, J.C.; Lu, L.H. Analysis and design of wideband injection-locked ring oscillators with multiple-input injection. IEEE J. Solid-State Circuits 2007, 42, 1906–1915. [Google Scholar] [CrossRef]

- Verhoeven, C. A high-frequency electronically tunable quadrature oscillator. IEEE J. Solid-State Circuits 1992, 27, 1097–1100. [Google Scholar] [CrossRef] [Green Version]

- Mizuno, H.; Ishibashi, K. A noise-immune GHz-clock distribution scheme using synchronous distributed oscillators. In Proceedings of the 1998 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 5–7 February 1998; pp. 404–405. [Google Scholar]

- Adler, R. A study of locking phenomena in oscillators. Proc. IRE 1946, 34, 351–357. [Google Scholar] [CrossRef]

- Razavi, B. A study of injection locking and pulling in oscillators. IEEE J. Solid-State Circuits 2004, 39, 1415–1424. [Google Scholar] [CrossRef]

- Demir, A.; Mehrotra, A.; Roychowdhury, J. Phase noise in oscillators: A unifying theory and numerical methods for characterization. IEEE Trans. Circuits Syst. I 2000, 47, 655–674. [Google Scholar] [CrossRef]

- Demir, A. Floquet theory and non-linear perturbation analysis for oscillators with differential-algebraic equations. Int. J. Circuit Theory Appl. 2000, 28, 163–185. [Google Scholar] [CrossRef]

- Gray, P.R.; Hurst, P.; Meyer, R.G.; Lewis, S. Analysis and Design of Analog Integrated Circuits; Wiley: Hoboken, NJ, USA, 2001. [Google Scholar]

- Kinget, P. Integrated GHz Voltage Controlled Oscillators; Springer: Berlin, Germany, 1999; pp. 353–381. [Google Scholar]

- Hajimiri, A.; Limotyrakis, S.; Lee, T.H. Jitter and phase noise in ring oscillators. IEEE J. Solid-State Circuits 1999, 34, 790–804. [Google Scholar] [CrossRef] [Green Version]

- Chang, H.C.; Cao, X.; Mishra, U.K.; York, R.A. Phase noise in coupled oscillators: Theory and experiment. IEEE Trans. Microw. Theory Tech. 1997, 45, 604–615. [Google Scholar] [CrossRef]

- Ximenes, A.R.; Padmanabhan, P.; Charbon, E. Mutually Coupled Ring Oscillators for Large Array Time-of-Flight Imagers. In Proceedings of the 2017 International Image Sensor Workshop (IISW), Hiroshima, Japan, 30 May–2 June 2017; p. R25. [Google Scholar]

- Lee, M.J.; Ximenes, A.R.; Padmanabhan, P.; Wang, T.J.; Huang, K.C.; Yamashita, Y.; Yaung, D.N.; Charbon, E. High-Performance Back-Illuminated Three-Dimensional Stacked Single-Photon Avalanche Diode Implemented in 45-nm CMOS Technology. IEEE J. Sel. Top. Quantum Electron. 2018, 24, 1–9. [Google Scholar] [CrossRef]

- Villa, F.; Lussana, R.; Tamborini, D.; Bronzi, D.; Markovic, B.; Tosi, A.; Zappa, F.; Tisa, S. CMOS single photon sensor with in-pixel TDC for Time-of-Flight applications. In Proceedings of the 2013 IEEE Nordic-Mediterranean Workshop on Time-to-Digital Converters (NoMe TDC), Perugia, Italy, 3 October 2013; pp. 1–6. [Google Scholar]

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ronchini Ximenes, A.; Padmanabhan, P.; Charbon, E. Mutually Coupled Time-to-Digital Converters (TDCs) for Direct Time-of-Flight (dTOF) Image Sensors ‡. Sensors 2018, 18, 3413. https://doi.org/10.3390/s18103413

Ronchini Ximenes A, Padmanabhan P, Charbon E. Mutually Coupled Time-to-Digital Converters (TDCs) for Direct Time-of-Flight (dTOF) Image Sensors ‡. Sensors. 2018; 18(10):3413. https://doi.org/10.3390/s18103413

Chicago/Turabian StyleRonchini Ximenes, Augusto, Preethi Padmanabhan, and Edoardo Charbon. 2018. "Mutually Coupled Time-to-Digital Converters (TDCs) for Direct Time-of-Flight (dTOF) Image Sensors ‡" Sensors 18, no. 10: 3413. https://doi.org/10.3390/s18103413