Dynamically Reconfigurable Encryption and Decryption System Design for the Internet of Things Information Security

Abstract

:1. Introduction

2. Related Work

3. AES and Data Encryption Standard (3DES) Implementation

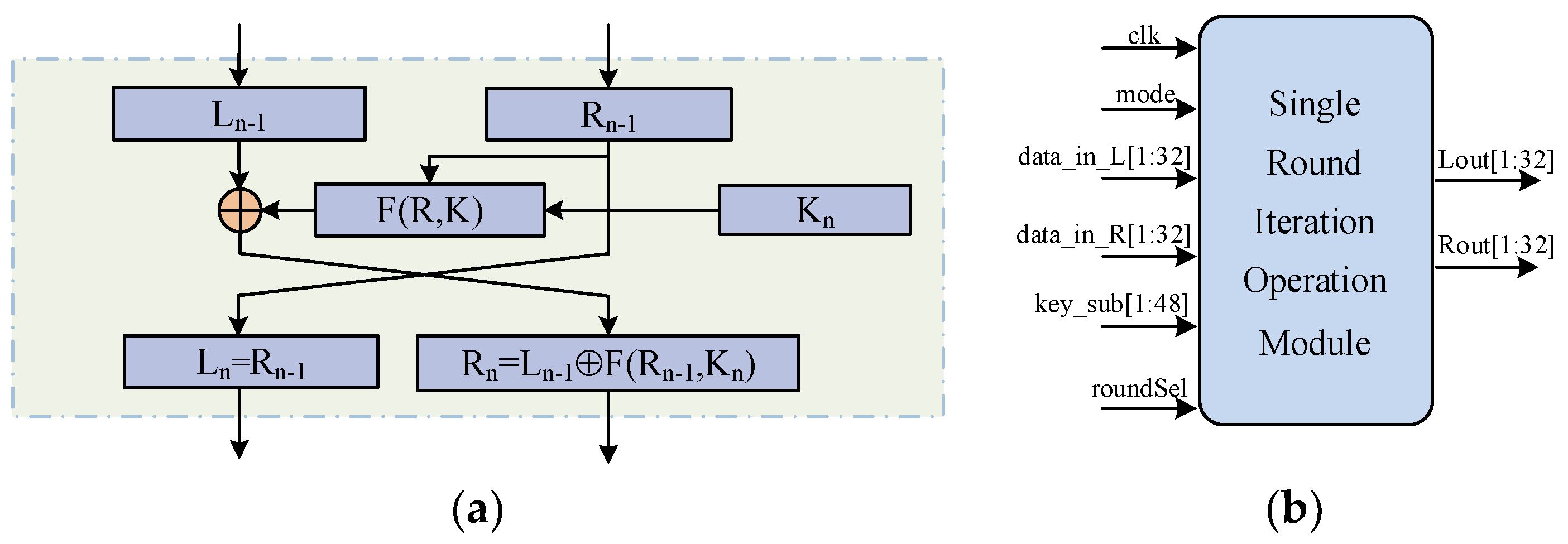

3.1. 3DES Optimizaiton

3.1.1. Subkey Generation

3.1.2. F(R,K) Function

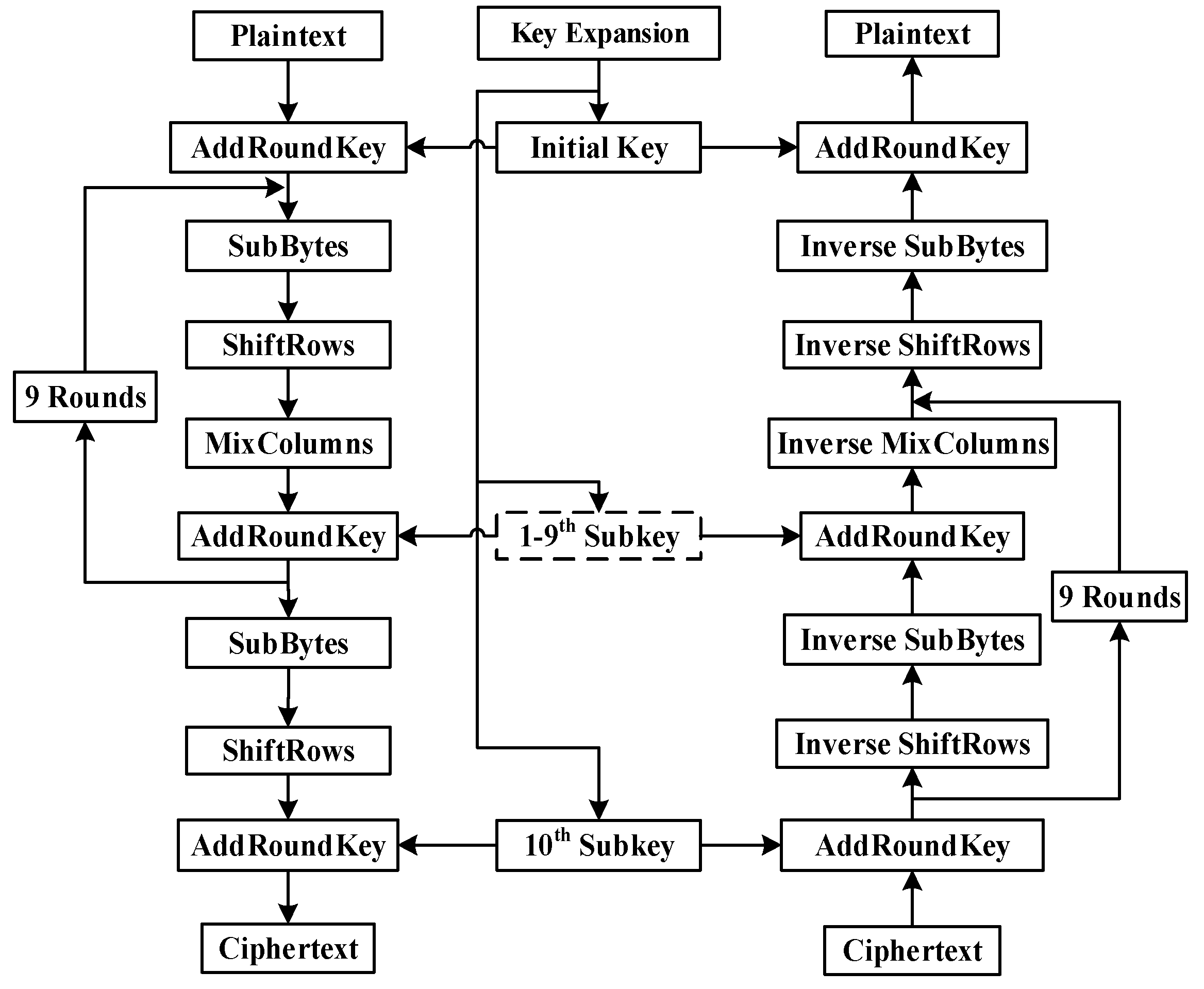

3.2. AES Optimization

3.2.1. SubBytes/Inverse SubBytes

3.2.2. MixColumns/Inverse MixColumns

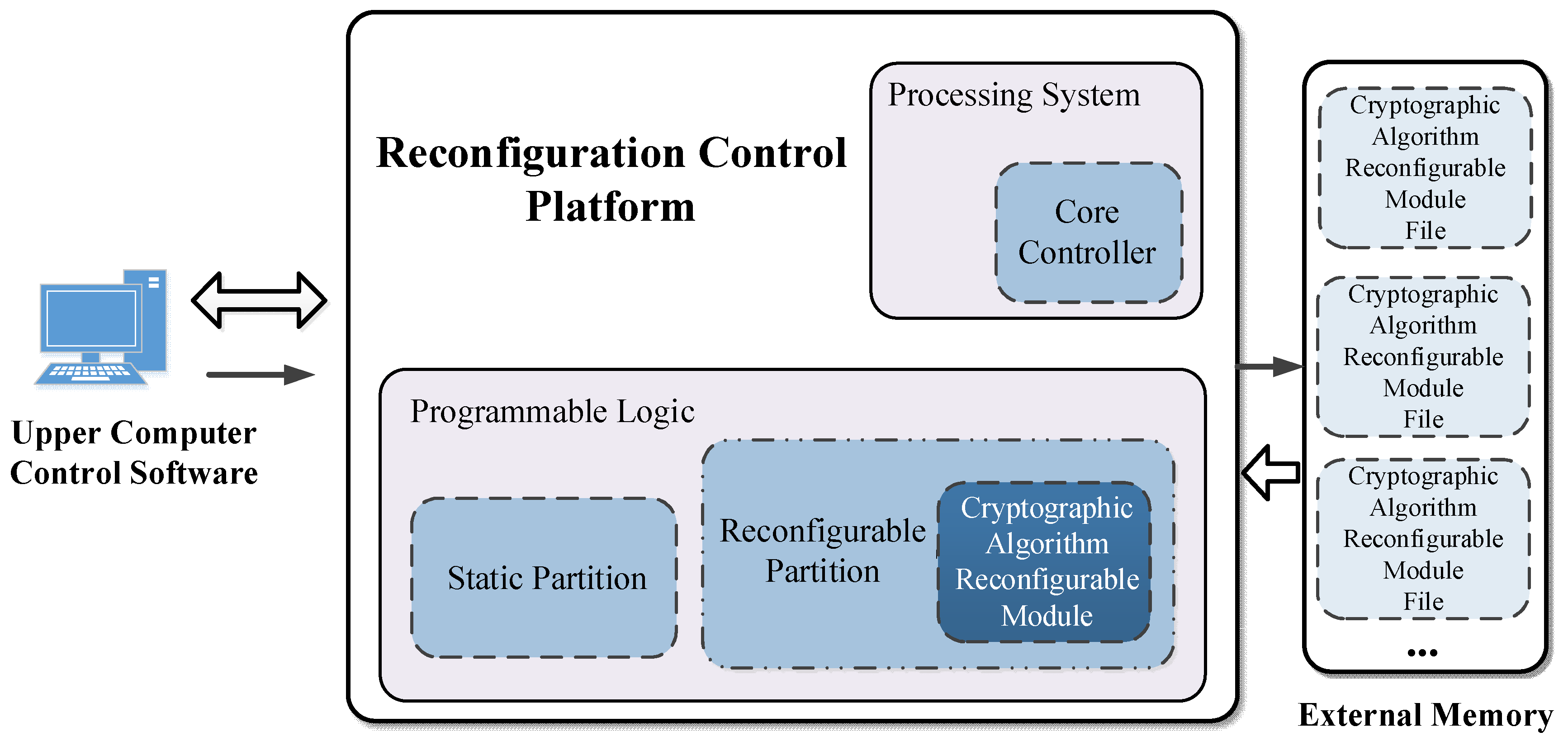

4. Dynamically Reconfigurable Encryption and Decryption System

4.1. Overall Structure

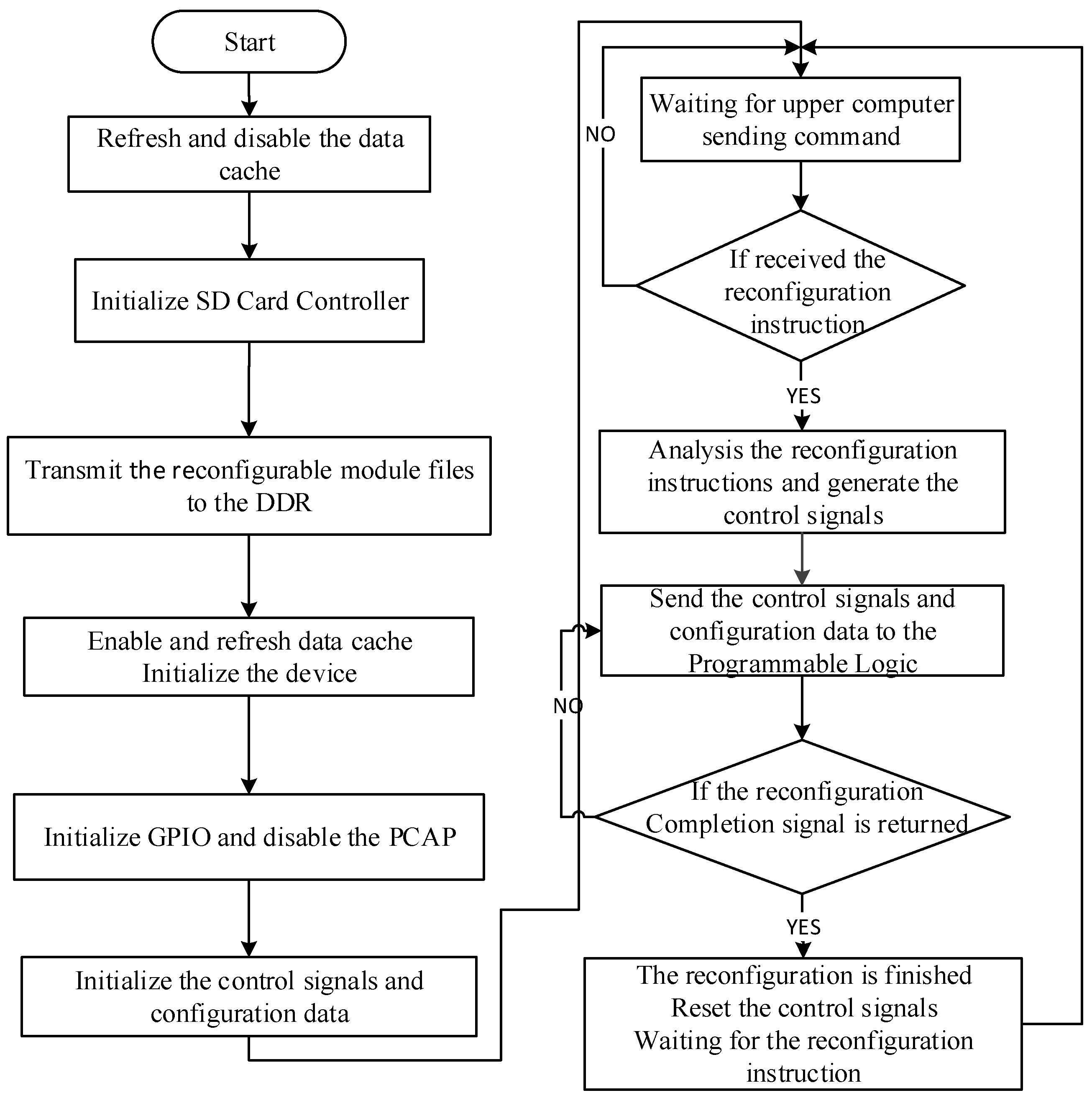

4.2. Reconfiguration Control Platform

- The peripheral controllers is used for initializing peripherals and controlling working status.

- The control instructions sent by the upper computer is received and the system status is returned to the upper computer through Universal Asynchronous Receiver/Transmitter (UART).

- The control signal is generated to transmit to other modules according to the instructions.

- The External Memory is controlled to transfer the selected cryptographic algorithm reconfigurable module file to DDR.

- The reconfiguration control signal is generated, and transmitted the reconfiguration data to the RP.

- Reconfiguration Initialization State: The initialization setting of the internal configuration access port is completed and the read-write enable control signal is reset as the original value.

- Reconfiguration Transmission Beginning State: The internal configuration access port is activated to alter to writing mode, ready for receiving the reconfiguration data from DDR to write in the Reconfigurable Partition.

- Reconfiguration Transmission State: The transmission signal stored in DDR takes effect to control the bitstream sequence of cryptographic algorithm reconfigurable module transmitted from the memory. The logic is decoupled to stabilize the signal between SP and RP, ensuring the bitstream sequence is written correctly into RP.

- Waiting State: The internal configuration access port is keeping in the writing state, the bitstream sequence is downloaded steadily into the Reconfigurable Partition to configure the logic circuit. In the meantime, the condition of the internal configuration access port output is under check. After the command completion flag of the bitstream sequence downloaded is received, the Waiting State is exited.

- Reconfiguration Reset State: The synchronization reset is enabled to reset the new logic elements in the Reconfiguration Partition, keeping in the known status.

- Reconfiguration Completion State: The decoupled logic is released and the internal configuration access port and DDR is disabled. After the reconfiguration process is completed, the cryptographic algorithm reconfigurable module starts to work.

4.3. Core Controller

5. Results and Discussion

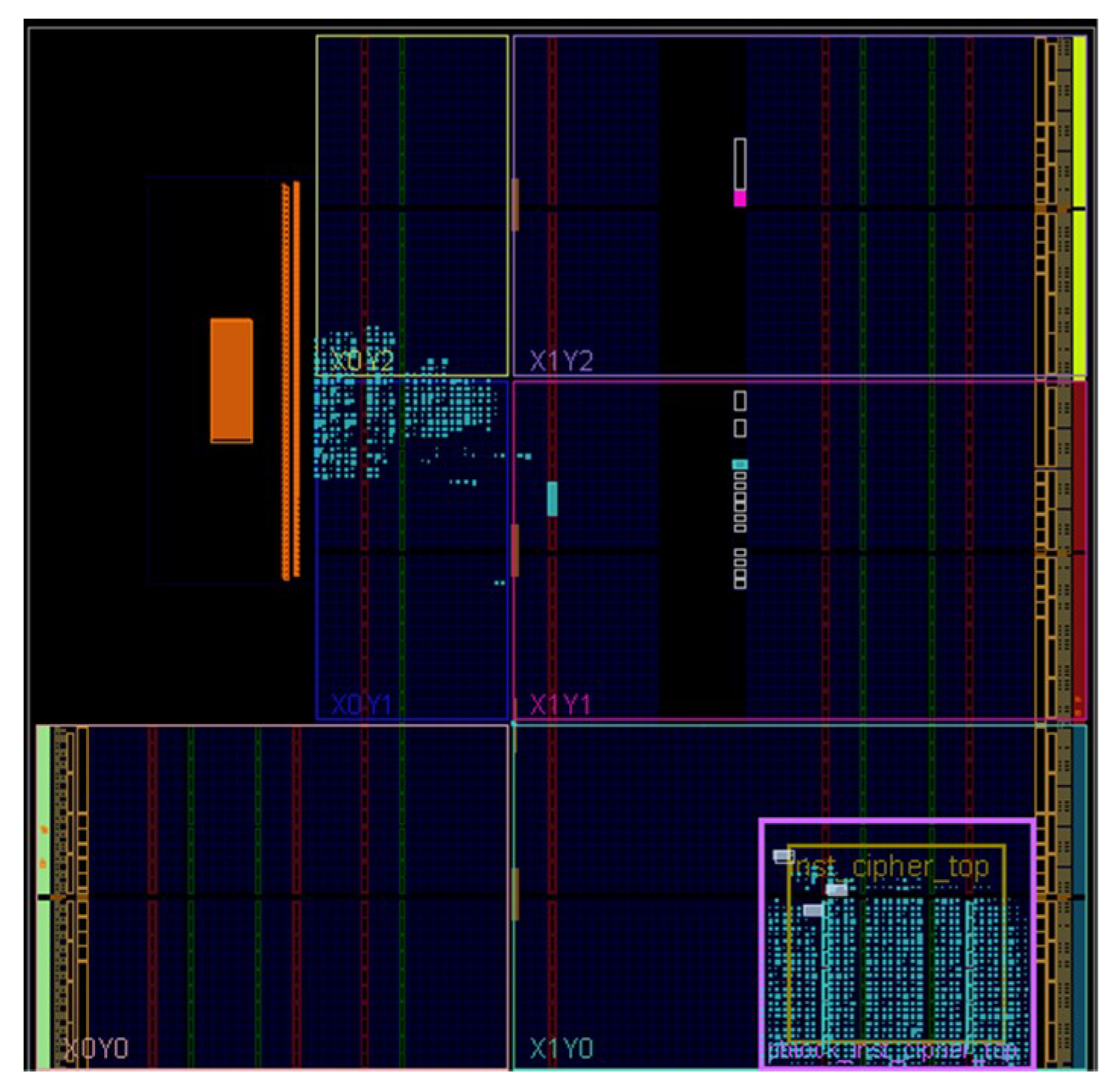

5.1. Test Platform

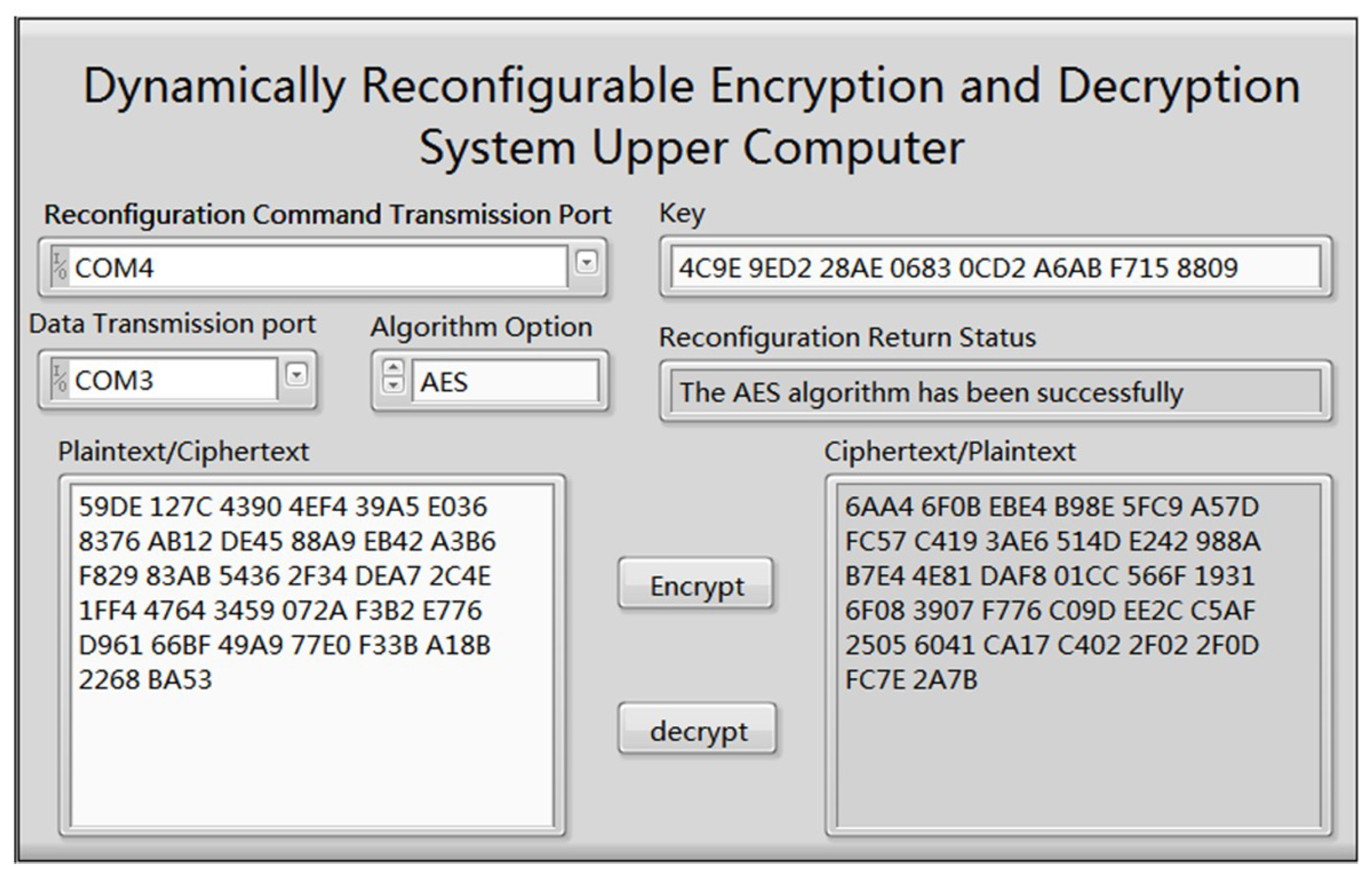

5.2. Data Validation

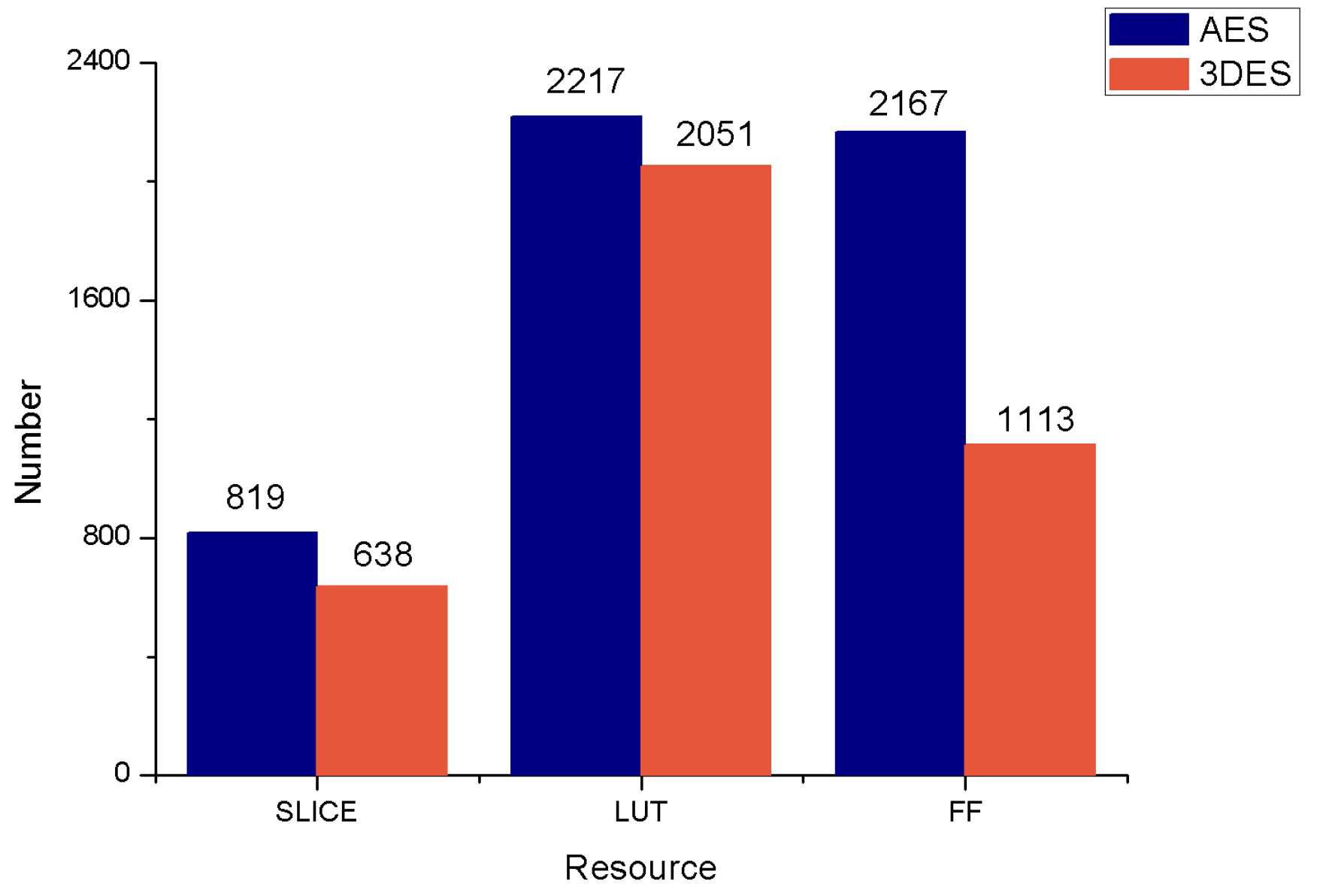

5.3. Resources Consumption

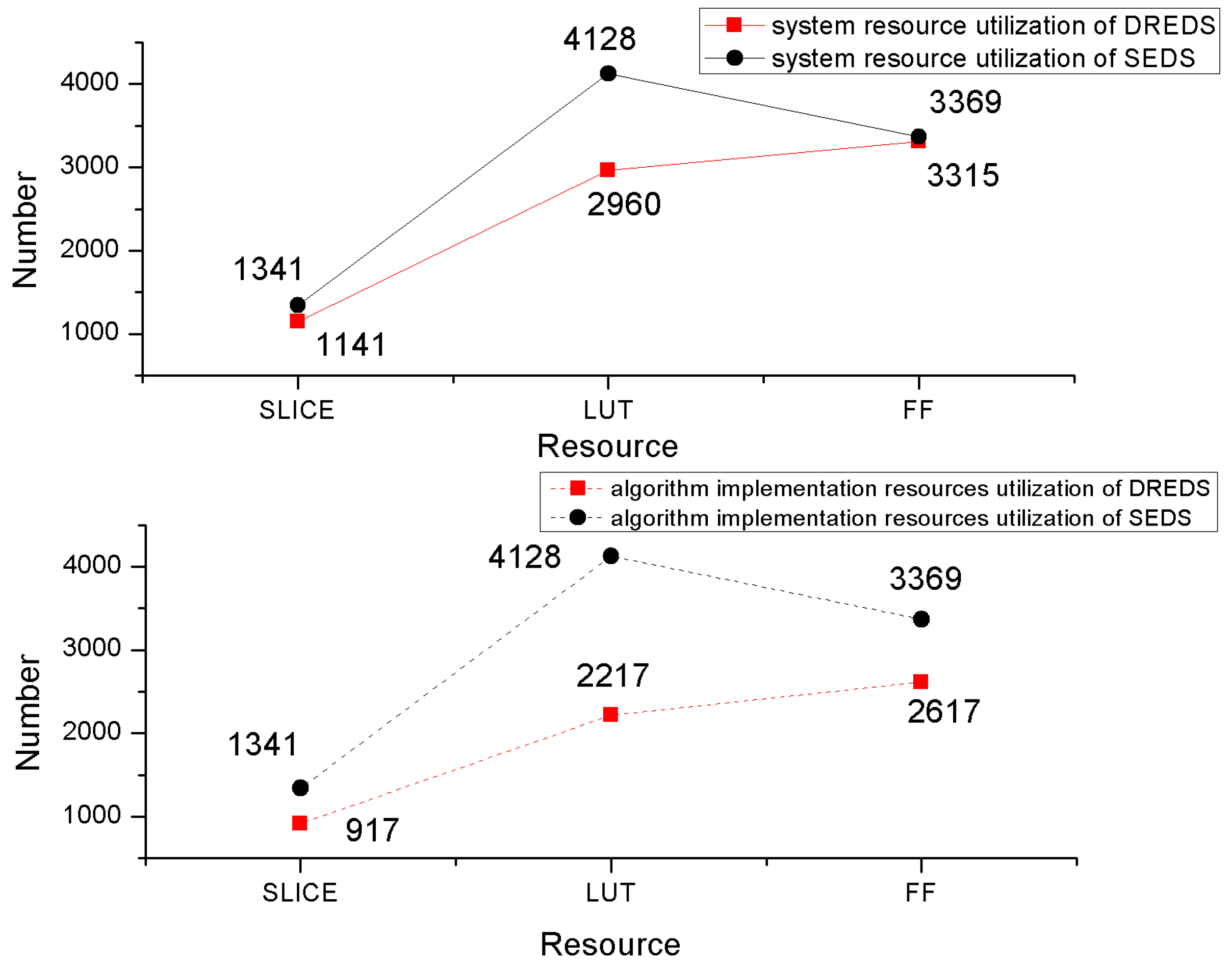

5.4. Contrast with the SEDS

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Qiu, T.; Qiao, R.; Wu, D.O. EABS: An Event-Aware Backpressure Scheduling Scheme for Emergency Internet of Things. IEEE. Trans. Mob. Comput. 2018, 17, 72–84. [Google Scholar] [CrossRef]

- Fortino, G.; Russo, W.; Savaglio, C.; Shen, W.; Zhou, M. Agent-oriented cooperative smart objects: From IoT system design to implementation. IEEE Trans. Syst. Man Cybern. Syst. 2018, 48, 1936–1956. [Google Scholar] [CrossRef]

- Shi, F.; Li, Q.; Zhu, T.; Ning, H. A Survey of Data Semantization in Internet of Things. Sensors 2018, 18, 313. [Google Scholar] [CrossRef] [PubMed]

- Qiu, T.; Chen, N.; Li, K.; Atiquzzaman, M.; Zhao, W. How can heterogeneous Internet of Things build our future: A Survey. IEEE Commun. Surv. Tutor. 2018, 20, 2011–2027. [Google Scholar] [CrossRef]

- Mohammed, J. 5 Predictions for the Internet of Things in 2016; World Economic Forum: Cologny, Switzerland, 15 December 2015. [Google Scholar]

- Casadei, R.; Fortino, G.; Pianini, D.; Russo, W.; Savaglio, C.; Viroli, M. Modelling and simulation of Opportunistic IoT Services with Aggregate Computing. Future Gener. Comput. Syst. 2019, 91, 252–262. [Google Scholar]

- Alaba, F.A.; Othman, M.; Hashem, I.A.T.; Alotaibi, F. Internet of things security. J. Netw. Comput. Appl. 2017, 88, 10–28. [Google Scholar] [CrossRef]

- Cheema, P.; Julka, N. Dynamic Cipher for Enhanced Cryptography and Communication for Internet of Things. In Proceedings of the 1st International Conference on Intelligent, Secure, and Dependable Systems in Distributed and Cloud Environments, Vancouver, BC, Canada, 26–28 October 2017; IEEE Computer Society: Washington, DC, USA, 2012; pp. 84–94. [Google Scholar]

- Pandey, J.G.; Goel, T.; Karmakar, A. A High-Performance and Area-Efficient VLSI Architecture for the PRESENT Lightweight Cipher. In Proceedings of the 17th International Conference on Embedded Systems, Maharashtra, India, 6–10 January 2018; pp. 392–397. [Google Scholar]

- Vinyaga, S.B.; Ramnath, M.; Prasanth, M.; Varsha, S.J. Encryption and hash based security in Internet of Things. In Proceedings of the 3rd International Conference on Signal Processing, Communication and Networking, Chennai, India, 26–28 March 2015; Institute of Electrical and Electronics Engineers Inc.: Piscataway, NJ, USA, 2015; pp. 1–6. [Google Scholar]

- Yan, Y.; Zhu, W.; Tong, X.; Luo, Q. A dynamic reconfigurable design of multiple cryptographic algorithms based on FPGA. In Proceedings of the 2018 IEEE International Conference on Smart Internet of Things, Xi’an, China, 17–19 August 2018; pp. 105–110. [Google Scholar]

- Banerjee, N.; Patil, R.; Chandrakant, S.; Shankar, A. Tunable Encryption System. U.S. Patent US8756429, 17 June 2014. [Google Scholar]

- Jasim, M.S.; Imad, J.M. ARSMS: A Hybrid Secured SMS Protocol for Smart Home using AES and RC4. CSNS Int. J. Comput. Sci. Netw. Secur. 2018, 18, 74–80. [Google Scholar]

- Hossain, M.J.; Hossain, M.B.; Morshed, K.M. Reconfigurable encryption system: Encrypt digital data. In Proceedings of the 15th International Conference on Computer and Information Technology, Chittagong, Bangladesh, 22–24 December 2012; IEEE Computer Society: Washington, DC, USA, 2012; pp. 429–435. [Google Scholar]

- Zhang, X.; Ng, K. A review of high-level synthesis for dynamically reconfigurable FPGAs. Microprocess. Microsyst. 2000, 24, 199–211. [Google Scholar] [CrossRef] [Green Version]

- Gilberto, O.; Lina, M.A.; Romain, B.; Lamotte, F.; Diguet, J. Towards Dynamically Reconfigurable SoCs (DRSoCs) in industrial automation: State of the art, challenges and opportunities. Microprocess. Microsyst. 2018, 62, 20–40. [Google Scholar]

- Idilia, B.; Georgi, P.; Hristo, K.; Grigor, S. Dynamic reconfigurability of control systems using IEC 61499 standard. IFAC Proc. Vol. 2013, 46, 256–261. [Google Scholar]

- Vennila, C.; Patel, A.K.; Lakshminarayanan, G.; Ko, S. Dynamic partial reconfigurable Viterbi decoder for wireless standards. Comput. Electr. Eng. 2013, 39, 164–174. [Google Scholar] [CrossRef]

- Trabelsi, C.; Meftali, S.; Dekeyser, J. Decentralized control for dynamically reconfigurable FPGA systems. Microprocess. Microsyst. 2013, 37, 871–884. [Google Scholar] [CrossRef]

- Gu, L.; Bai, G.; Guo, Y.; Chen, X.; Mei, H. Security model oriented attestation on dynamically reconfigurable component-based systems. J. Netw. Comput. Appl. 2012, 35, 974–981. [Google Scholar] [CrossRef]

- Huang, C.-H.; Hsiung, P.-A.; Shen, J.-S. UML-based hardware/software co-design platform for dynamically partially reconfigurable network security systems. J. Syst. Archit. 2010, 56, 88–102. [Google Scholar] [CrossRef]

- Niar, S.; Yurdakul, A.; Unsal, O.; Tugcu, T.; Yuceturk, A. A dynamically reconfigurable architecture for emergency and disaster management in ITS. In Proceedings of the 2014 International Conference on Connected Vehicles and Expo (ICCVE), Vienna, Austria, 3–7 November 2014; pp. 479–484. [Google Scholar]

- Ben, A.N.; Lahbib, K.; Frikha, T. Design of a dynamically reconfigurable architecture for the 3D image synthesis. In Proceedings of the 2017 International Conference on Advanced Technologies for Signal and Image Processing (ATSIP), Fez, Morocco, 22–24 May 2017; pp. 1–5. [Google Scholar]

- Silva, N.V.; Oliveira, A.S.R.; Gustavsson, U.; Carvalho, N.B. A dynamically reconfigurable architecture enabling all-digital transmission for cognitive radios. In Proceedings of the 2012 IEEE Radio and Wireless Symposium, Santa Clara, CA, USA, 15–18 January 2012; pp. 1–4. [Google Scholar]

- Nachef, V.; Patarin, J.; Volte, E. Des and Variants: 3DES, DES–X. In Feistel Ciphers; Springer: Cham, Switzerland, 2017; pp. 157–176. ISBN 978-3-319-49528-6. [Google Scholar]

- Dichou, K.; Tourtchine, V.; Rahmoune, F. Finding the best FPGA implementation of the DES algorithm to secure smart cards. In Proceedings of the International Conference on Electrical Engineering, Boumerdes, Algeria, 13–15 December 2016. [Google Scholar]

- Zhu, Y.; Zhang, H.; Bao, Y. Study of the AES Realization Method on the Reconfigurable Hardware. In Proceedings of the International Conference on Computer Sciences and Applications, Wuhan, China, 14–15 December 2013; pp. 72–76. [Google Scholar]

- Wankhade, S.; Mahajan, R. Dynamic Partial Reconfiguration Implementation of AES Algorithm. Int. J. Comput. Appl. 2014, 97, 15–18. [Google Scholar] [CrossRef]

- Crockett, L.H.; Elliot, R.A.; Enderwitz, M.A.; Stewart, R.W. The Zynq Book: Embedded Processing with the Arm Cortex-A9 on the Xilinx Zynq-7000 All Programmable Soc; Strathclyde Academic Media: Glasgow, UK, 2014; pp. 20–25. ISBN 978-0-992-97870-9. [Google Scholar]

- Kizheppatt, V.; Fahmy, S.A. ZyCAP: Efficient Partial Reconfiguration Management on the Xilinx Zynq. IEEE Embed. Syst. Lett. 2014, 6, 41–44. [Google Scholar] [CrossRef] [Green Version]

| Works | High Flexibility | Multiple Cryptographic Algorithms Supporting | Cryptographic Algorithm Optimization | Low Resource Consumption |

|---|---|---|---|---|

| [6] | √ 1 | × | √ | × |

| [7] | × 2 | × | √ | √ |

| [10] | √ | √ | × | × |

| [12] | × | √ | × | √ |

| DREDS | √ | √ | √ | √ |

| Algorithms | Slice | Data Processing Rate | |||

|---|---|---|---|---|---|

| Clock Period Constraint | Clock Period Remain | Throughout | TPS | ||

| AES | 689 | 5.000 ns | 0.324 ns | 2.74 Gbps | 3.97 Mbps/Slice |

| 3DES | 412 | 5.000 ns | 0.246 ns | 280.47 Mbps | 680.75 kbps/Slice |

| Resources | Total Number | SP | PL | ||

|---|---|---|---|---|---|

| Number | Percentage | Number | Percentage | ||

| SLICE | 13,300 | 322 | 2.42% | 819 | 6.16% |

| LUT | 53,200 | 743 | 1.40% | 2217 | 4.17% |

| FF | 106,400 | 1148 | 1.08% | 2167 | 2.04% |

| BRAM | 140 | 1 | 0.71% | 9 | 6.43% |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, Z.; Yao, Y.; Tong, X.; Luo, Q.; Chen, X. Dynamically Reconfigurable Encryption and Decryption System Design for the Internet of Things Information Security. Sensors 2019, 19, 143. https://doi.org/10.3390/s19010143

Wang Z, Yao Y, Tong X, Luo Q, Chen X. Dynamically Reconfigurable Encryption and Decryption System Design for the Internet of Things Information Security. Sensors. 2019; 19(1):143. https://doi.org/10.3390/s19010143

Chicago/Turabian StyleWang, Zhu, Yan Yao, Xiaojun Tong, Qinghua Luo, and Xiangyu Chen. 2019. "Dynamically Reconfigurable Encryption and Decryption System Design for the Internet of Things Information Security" Sensors 19, no. 1: 143. https://doi.org/10.3390/s19010143