Design and Analysis of a Continuously Tunable Low Noise Amplifier for Software Defined Radio

Abstract

:1. Introduction

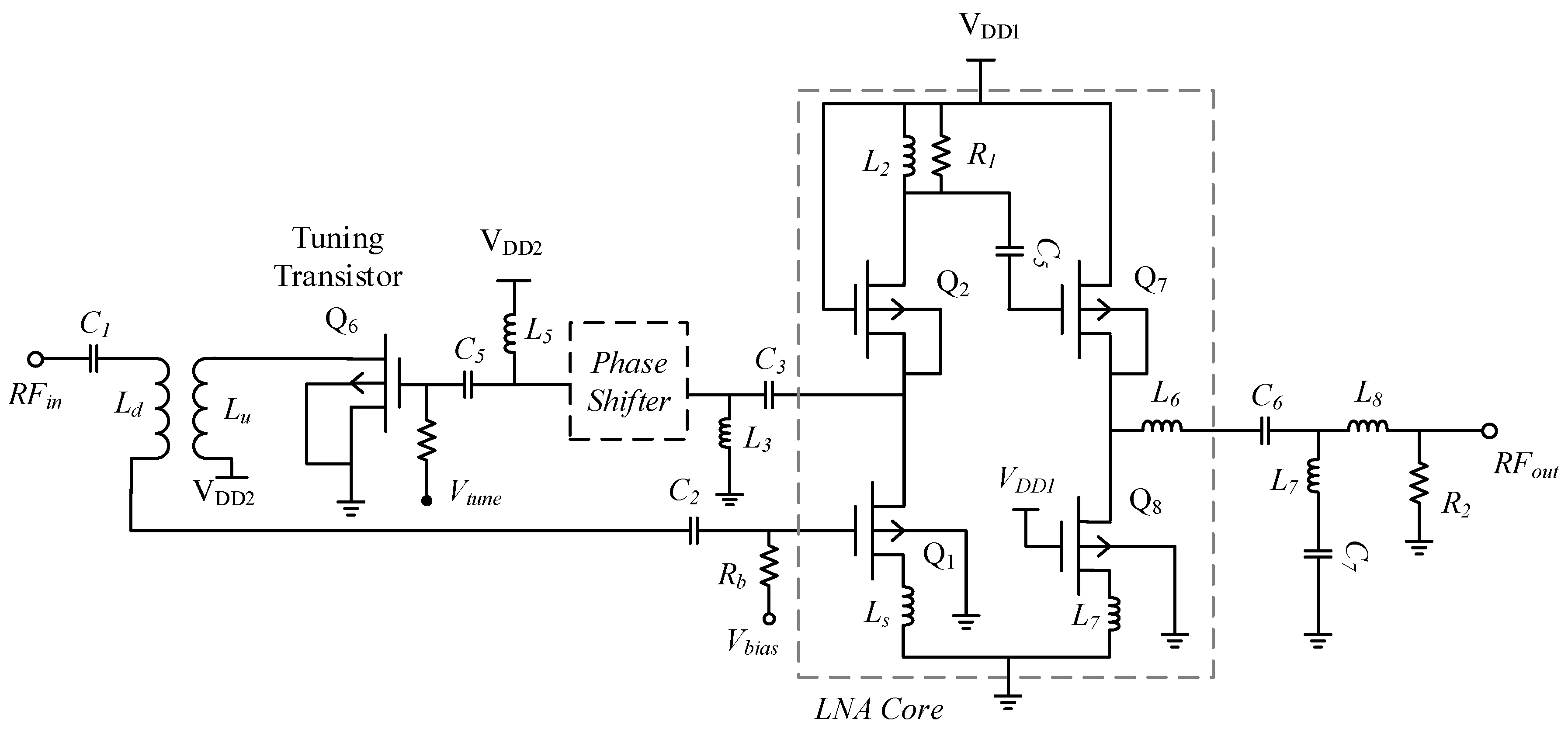

2. Motivation

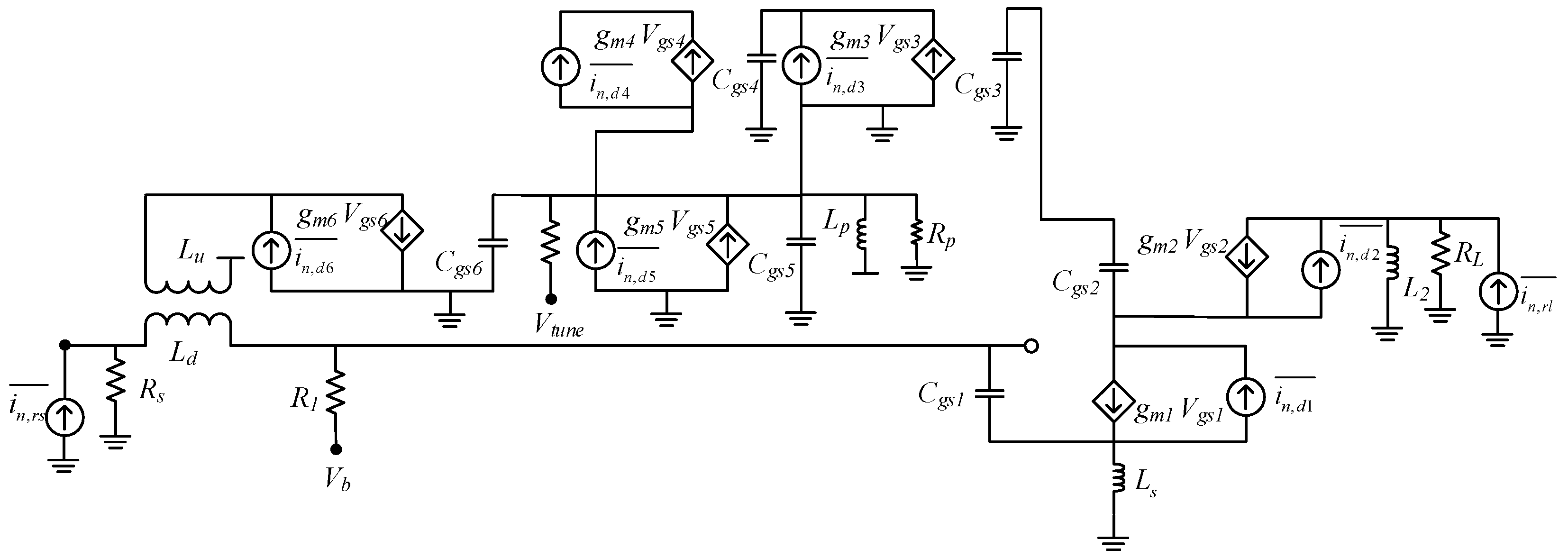

3. Proposed Circuit Topology

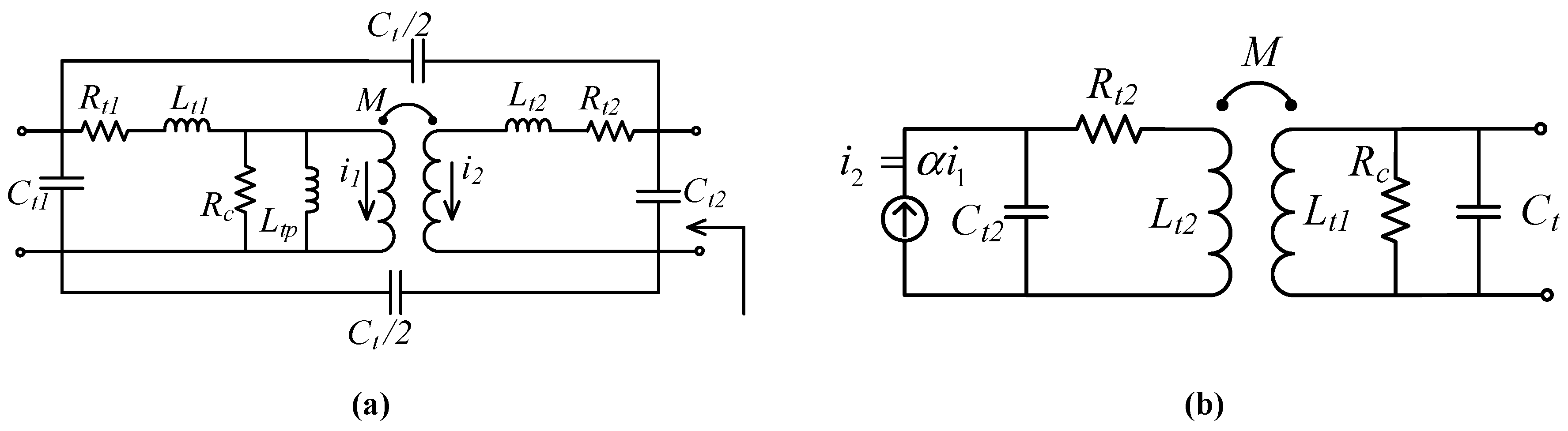

3.1. Transformer Network

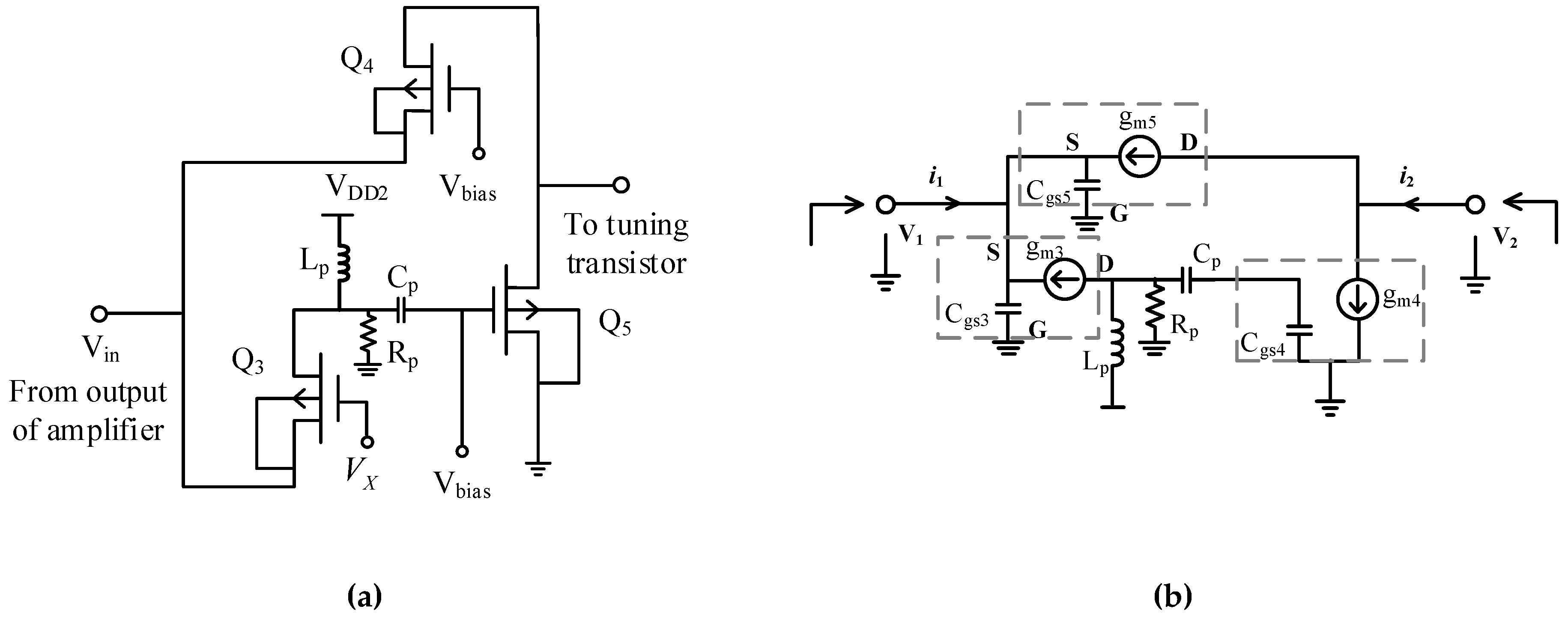

3.2. Phase Shifter

3.3. Tuning Stage

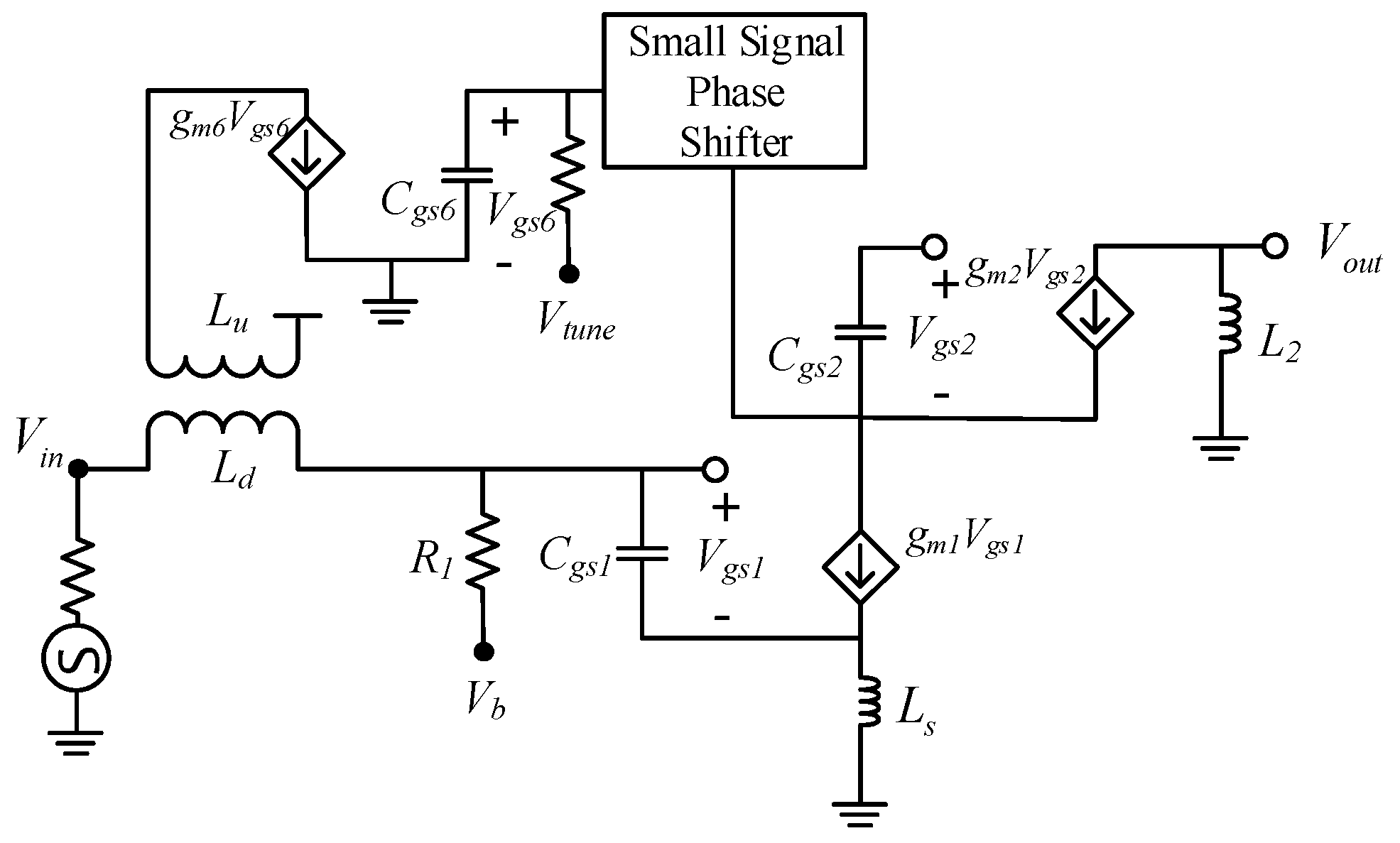

4. Circuit Analysis

4.1. Input Impedance

4.2. Gain

4.3. Noise Figure

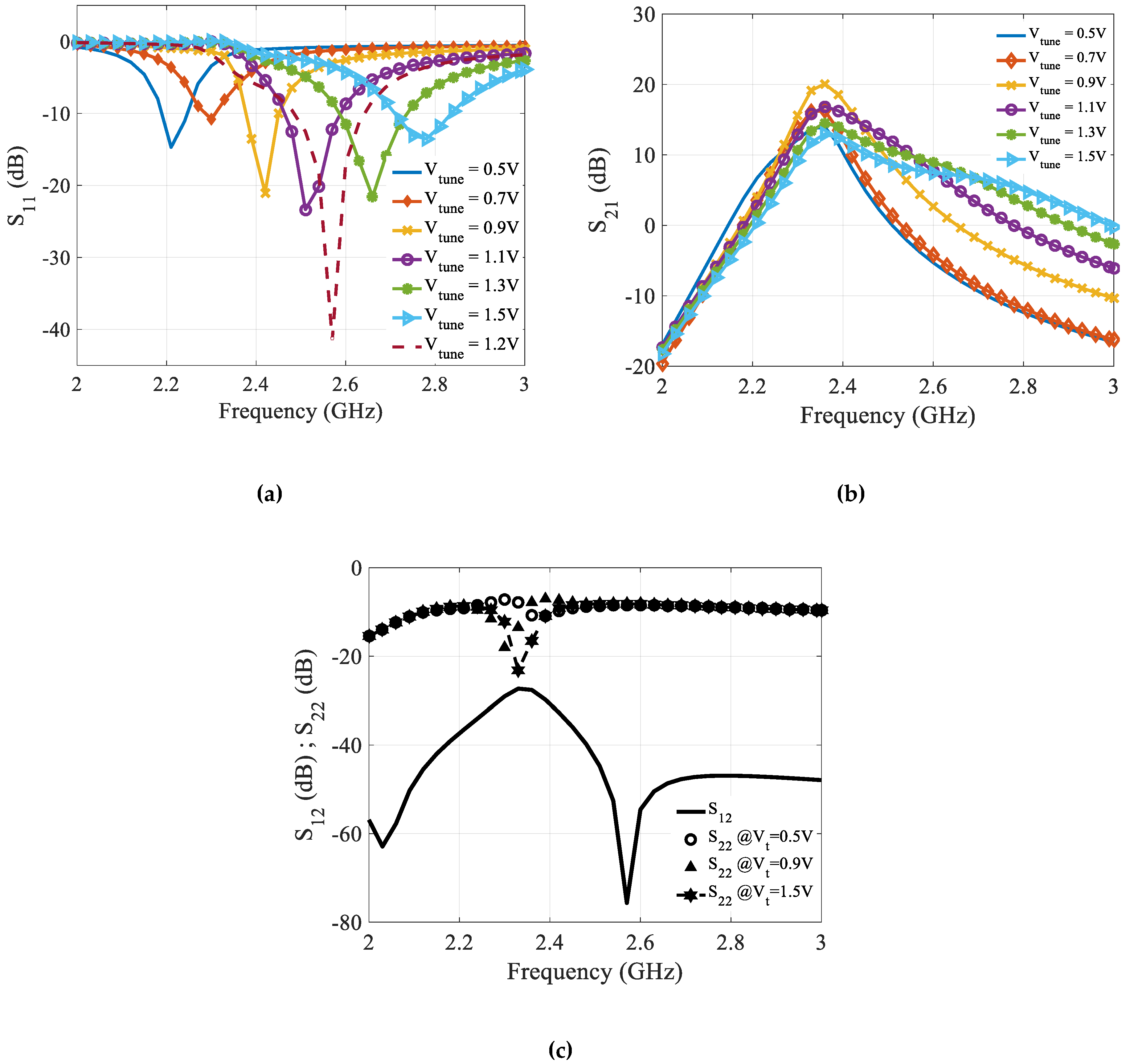

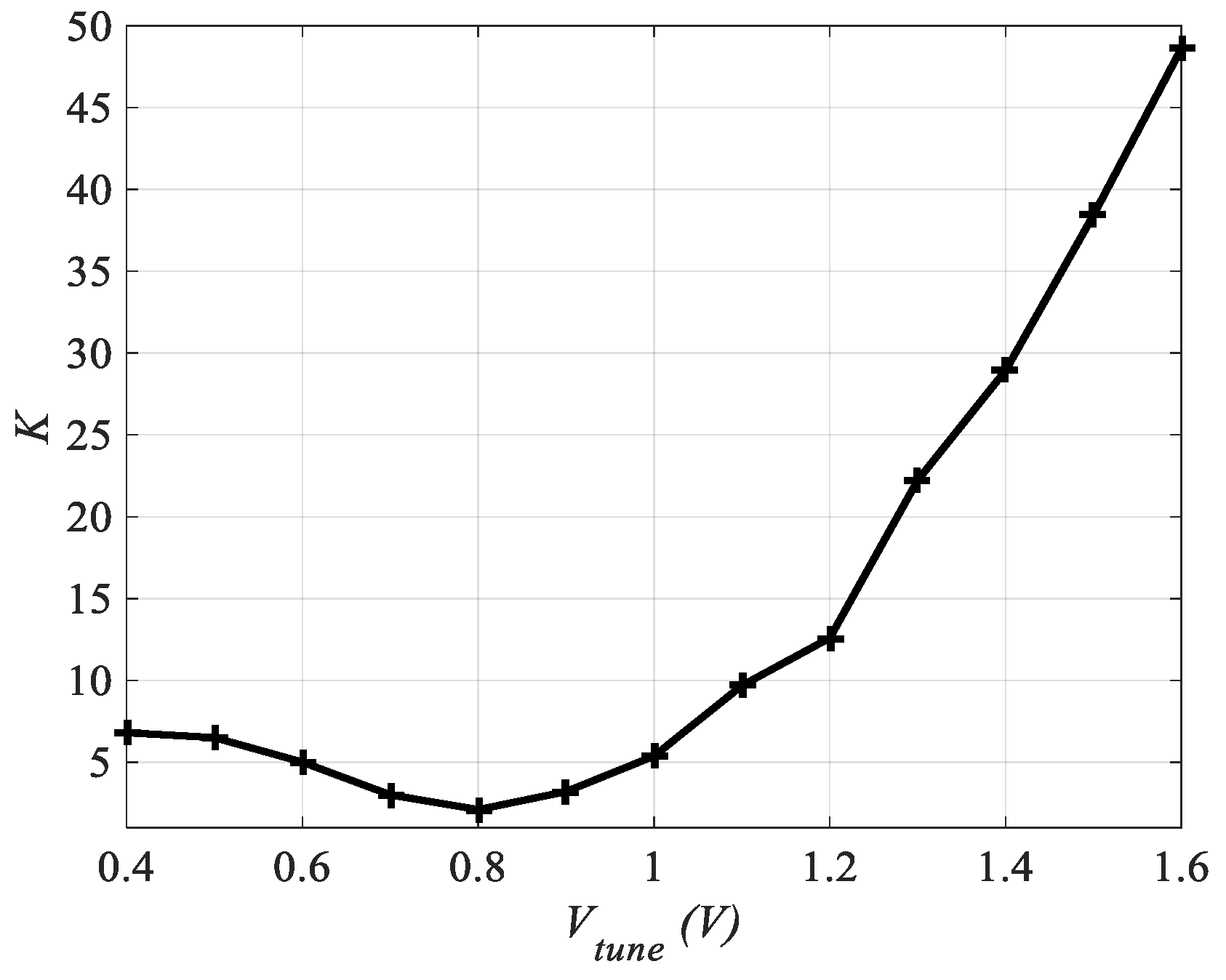

5. Results and Discussion

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Bazrafshan, A.; Taherzadeh-Sani, M.; Nabki, F. A 0.8–4-GHz Software-Defined Radio Receiver With Improved Harmonic Rejection Through Non-Overlapped Clocking. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 3186–3195. [Google Scholar] [CrossRef]

- Adom-Bamfi, G.; Entesari, K. A multiband low noise amplifier with a switchable Gm active shunt feedback for SDRs. In Proceedings of the IEEE Radio and Wireless Symposium (RWS), Austin, TX, USA, 24–27 January 2016; pp. 179–182. [Google Scholar]

- Aneja, A.; Li, X.J.; Li, B.E. Design of Continuously Tunable Low Noise Amplifier for Multiband Radio. In Proceedings of the 2017 Mediterranean Microwave Symposium (MMS), Marseille, France, 28–30 November 2017; pp. 1–4. [Google Scholar]

- Yu, X.; Neihart, N.M. A 2–11 GHz reconfigurable multi-mode LNA in 0.13 µm CMOS. In Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Montreal, QC, Canada, 17–19 June 2012; pp. 475–478. [Google Scholar]

- El-Nozahi, M.; Sanchez-Sinencio, E.; Entesari, K. A CMOS low-noise amplifier with reconfigurable input matching network. IEEE Trans. Microw. Theory Tech. 2009, 57, 1054–1062. [Google Scholar] [CrossRef]

- Wu, C.-R.; Hsieh, H.-H.; Lai, L.-S.; Lu, L.-H. A 3–5 GHz frequency-tunable receiver frontend for multiband applications. IEEE Microw. Wirel. Compon. Lett. 2008, 18, 638–640. [Google Scholar] [CrossRef]

- Kwon, K.; Kim, S.; Son, K.Y. A Hybrid Transformer-Based CMOS Duplexer With a Single-Ended Notch-Filtered LNA for Highly Integrated Tunable RF Front-Ends. IEEE Microw. Wirel. Compon. Lett. 2018, 28, 1032–1034. [Google Scholar] [CrossRef]

- Wang, J.-J.; Chen, D.-Y.; Wang, S.-F.; Wei, R.-S. A multi-band low noise amplifier with wide-band interference rejection improvement. AEU-Int. J. Electron. Commun. 2016, 70, 320–325. [Google Scholar] [CrossRef]

- Zokaei, A.; Amirabadi, A. A dual-band common-gate LNA using active post distortion for mobile WiMAX. Microelectron. J. 2014, 45, 921–929. [Google Scholar] [CrossRef]

- Neihart, N.M.; Brown, J.; Yu, X. A dual-band 2.45/6 GHz CMOS LNA utilizing a dual-resonant transformer-based matching network. IEEE Trans. Circuits Syst. I Regul. Pap. 2012, 59, 1743–1751. [Google Scholar] [CrossRef]

- Yu, X.; Neihart, N.M. Analysis and design of a reconfigurable multimode low-noise amplifier utilizing a multitap transformer. IEEE Trans. Microw. Theory Tech. 2013, 61, 1236–1246. [Google Scholar] [CrossRef]

- Fu, C.-T.; Ko, C.-L.; Kuo, C.-N.; Juang, Y.-Z. A 2.4–5.4-GHz wide tuning-range CMOS reconfigurable low-noise amplifier. IEEE Trans. Microw. Theory Tech. 2008, 56, 2754–2763. [Google Scholar]

- Kia, H.B.; A’ain, A.K.; Grout, I.; Kamisian, I. A reconfigurable low-noise amplifier using a tunable active inductor for multistandard receivers. CircuitsSyst. Signal Process. 2013, 32, 979–992. [Google Scholar] [CrossRef]

- Wu, C.-R.; Lu, L.-H. A 2.9-3.5-GHz tunable low-noise amplifier. In Proceedings of the IEEE Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems, San Diego, CA, USA, 18–20 January 2006. [Google Scholar]

- Beare, R.; Plett, C.; Rogers, J. Highly reconfigurable single-ended low noise amplifier for software defined radio applications. In Proceedings of the IEEE 10th International New Circuits and Systems Conference (NEWCAS), Montreal, QC, Canada, 17–20 June 2012; pp. 549–552. [Google Scholar]

- Chen, Z.; Zhang, X.; Song, Z.; Jia, W.; Chi, B. A 1.0–5.0 GHz tunable LNA with automatic frequency calibration in 65 nm CMOS. In Proceedings of the 2016 IEEE International Symposium on Radio-Frequency Integration Technology (RFIT), Taipei, Taiwan, 24–26 August 2016; pp. 1–3. [Google Scholar]

- Emami, N.; Arshed, O.; Bakri-Kassem, M.; Albasha, L. Reconfigurable low noise amplifier using MEMS varactor. In Proceedings of the 2013 8th International Conference on Design & Technology of Integrated Systems in Nanoscale Era (DTIS), Abu Dhabi, UAE, 26–28 March 2013; pp. 145–150. [Google Scholar]

- Akbar, F.; Atarodi, M.; Saeedi, S. Design method for a reconfigurable CMOS LNA with input tuning and active balun. AEU-Int. J. Electron. Commun. 2015, 69, 424–431. [Google Scholar] [CrossRef]

- Macias-Bobadilla, G.; Rodríguez-Reséndiz, J.; Mota-Valtierra, G.; Soto-Zarazúa, G.; Méndez-Loyola, M.; Garduño-Aparicio, M. Dual-Phase Lock-In Amplifier Based on FPGA for Low-Frequencies Experiments. Sensors 2016, 16, 379. [Google Scholar] [CrossRef]

- Brown, J. Design of a Magnetically Tunable Low Noise Amplifier in 0.13 um CMOS Technology; Iowa State University: Ames, IA, USA, 2012. [Google Scholar]

- Gómez-Espinosa, A.; Hernández-Guzmán, V.M.; Bandala-Sánchez, M.; Jiménez-Hernández, H.; Rivas-Araiza, E.A.; Rodríguez-Reséndiz, J.; Herrera-Ruíz, G. A New Adaptive Self-Tuning Fourier Coefficients Algorithm for Periodic Torque Ripple Minimization in Permanent Magnet Synchronous Motors (PMSM). Sensors 2013, 13, 3831–3847. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Brown, J.L.; Neihart, N.M. An analytical study of a magnetically tuned matching network. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Seoul, Korea, 20–23 May 2012; pp. 1979–1982. [Google Scholar]

- Hayashi, H.; Mauraguchi, M. An MMIC active phase shifter using a variable resonant circuit [and MESFETs]. IEEE Trans. Microw. Theory Tech. 1999, 47, 2021–2026. [Google Scholar] [CrossRef]

- Tan, E.L. A quasi-invariant single-parameter criterion for linear two-port unconditional stability. IEEE Microw. Wirel. Compon. Lett. 2004, 14, 487–489. [Google Scholar] [CrossRef]

| Parameter | Value |

|---|---|

| Turns Ratio ‘N’ | 0.69 |

| Magnetising Inductance ‘Ltp’ | 2.23 nH |

| Cross loss resistance ‘Rc’ | 1000 |

| Coefficient of Coupling ‘k’ | 0.11 |

| Primary loss resistance ‘Rt1’ | 0.91 |

| Secondary loss resistance ‘Rt2’ | 4.47 |

| Primary capacitance ‘Ct1’ | 924 fF |

| Secondary capacitance ‘Ct2’ | 150 fF |

| Interwinding capacitance ‘Ct’ | 340 fF |

| Ref. | Freq. (GHz) | S21 (dB) | S11 (dB) | NF (dB) | IP3 (dBm) | VDD | Tech. | PDC (mW) |

|---|---|---|---|---|---|---|---|---|

| This work | 2.2–2.8 | 7–18 | −40–−11 | 1.4–4.8 | −31–15 | 1.8 | MIC | 16.2 |

| [16] | 1–5 | 19–27 | −18–−5 | 2.4–3.8 | - | 1.2 | 65 nm CMOS | 12.1 |

| [5] | 1.9–2.4 | 10–14 | −25–12 | 3.2–3.7 | −6.7 | 1.2 | 0.13 µm CMOS | 17 |

| [12] | 2.4–5.4 | 9.9–22 | −14–−30 | 2.4–4.9 | −20.4–−9.7 | 1 | 0.13 µm CMOS | 3.1–4.6 |

| [13] | 0.8–2.5 | 17–20 | −27–−11 | 3.1–3.6 | - | 1.8 | 0.18 µm CMOS |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Aneja, A.; Li, X.J. Design and Analysis of a Continuously Tunable Low Noise Amplifier for Software Defined Radio. Sensors 2019, 19, 1273. https://doi.org/10.3390/s19061273

Aneja A, Li XJ. Design and Analysis of a Continuously Tunable Low Noise Amplifier for Software Defined Radio. Sensors. 2019; 19(6):1273. https://doi.org/10.3390/s19061273

Chicago/Turabian StyleAneja, Aayush, and Xue Jun Li. 2019. "Design and Analysis of a Continuously Tunable Low Noise Amplifier for Software Defined Radio" Sensors 19, no. 6: 1273. https://doi.org/10.3390/s19061273