Passive Equalization Networks—Efficient Synthesis Approach for High-Speed Signal Integrity Characterization

Abstract

:1. Introduction

2. Materials and Methods

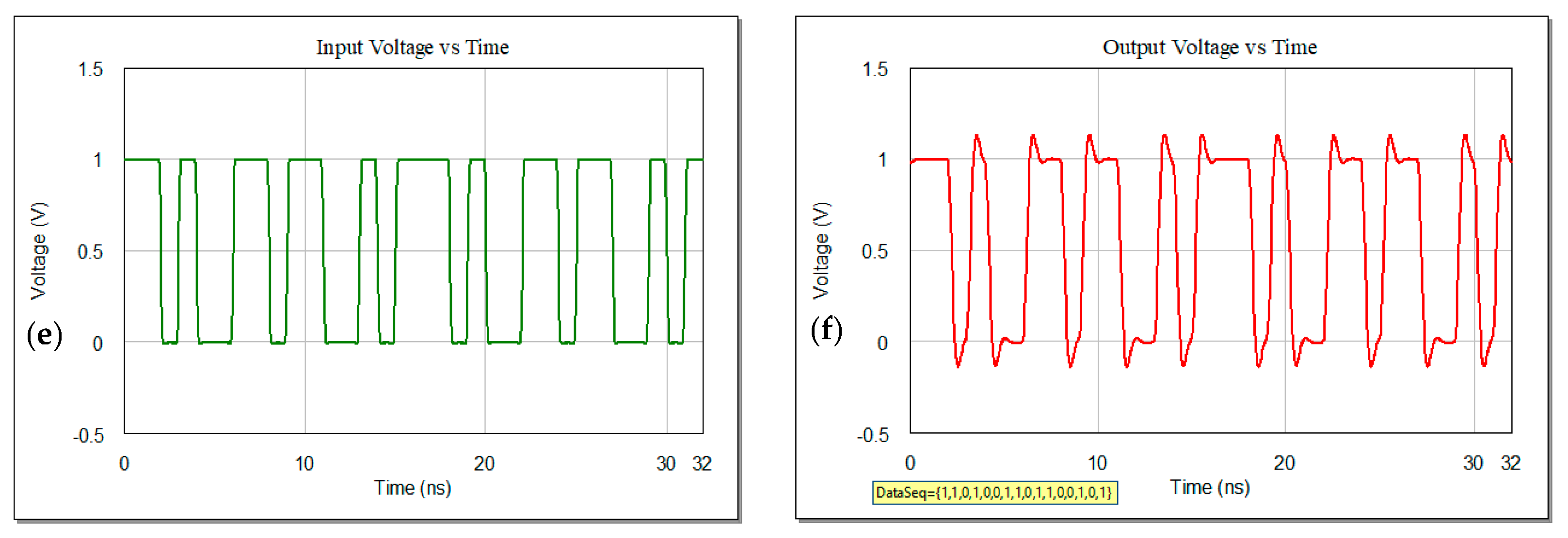

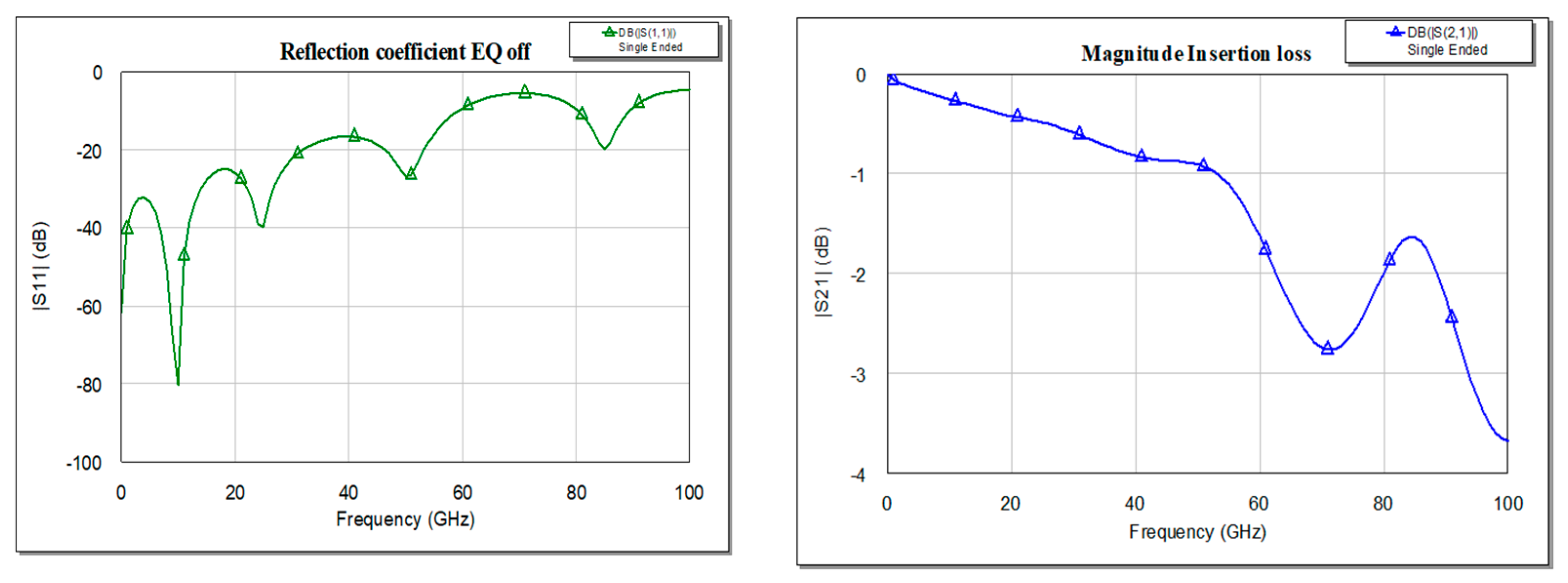

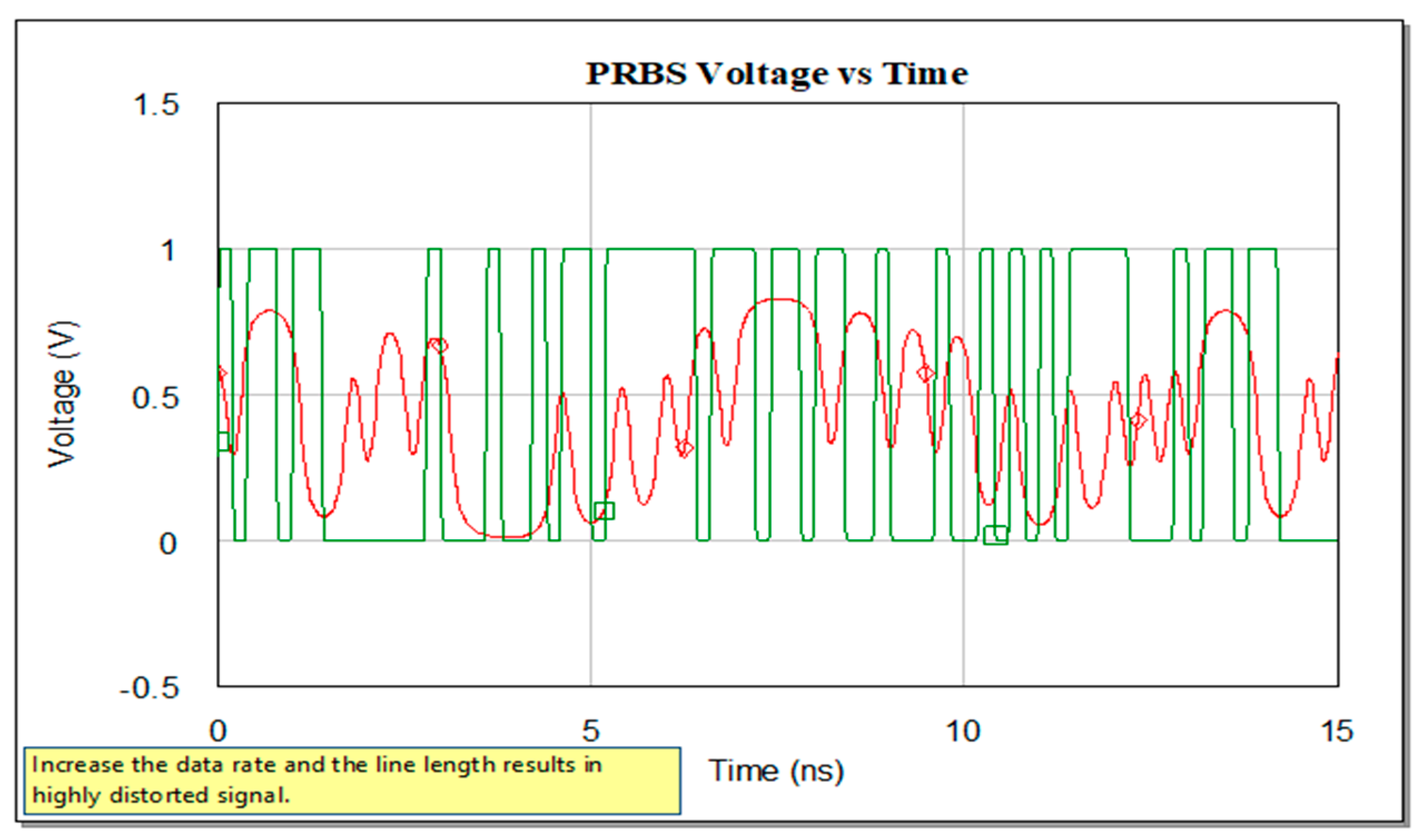

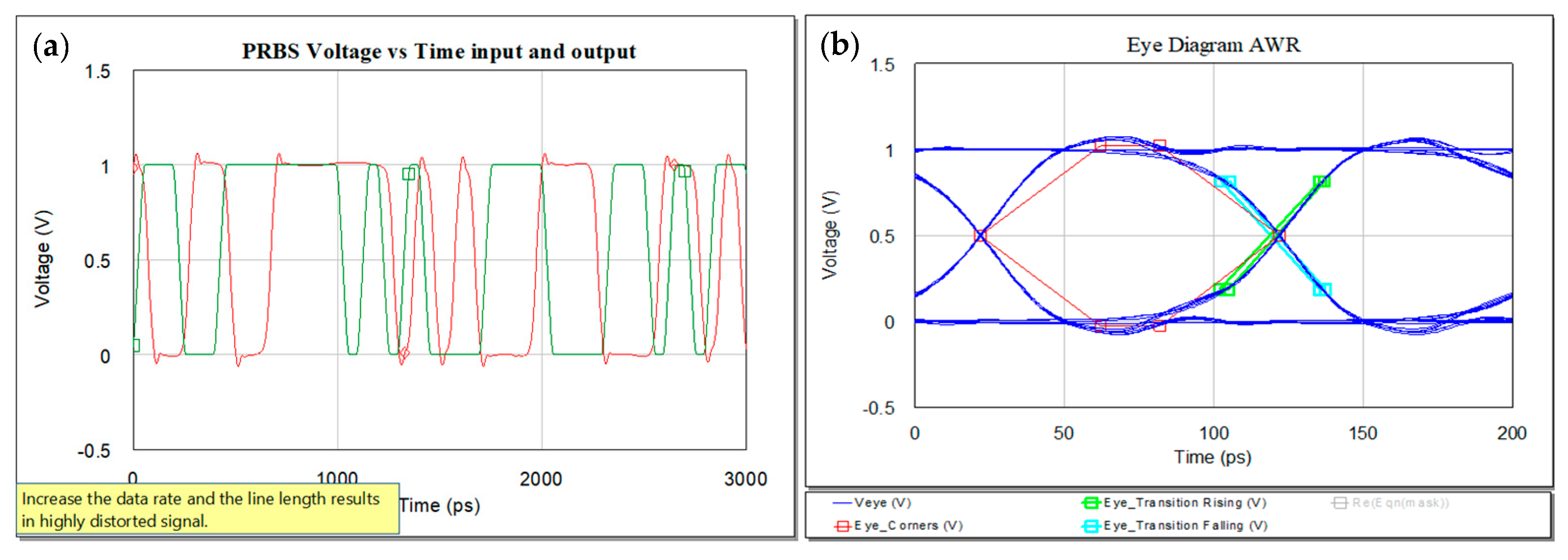

2.1. Typical Characteristics of Signals on Interconnections

2.2. General Aspects on EQ

- Active

- Passive

- Adaptive

2.3. Passive Equalization

- Pre-emphasis

- Post-emphasis

- Pre- and post-emphasis

2.4. Active Equalization

2.5. Adaptive Equalization

3. Results

3.1. Passive EQ-Lumped Elements, Synthesis

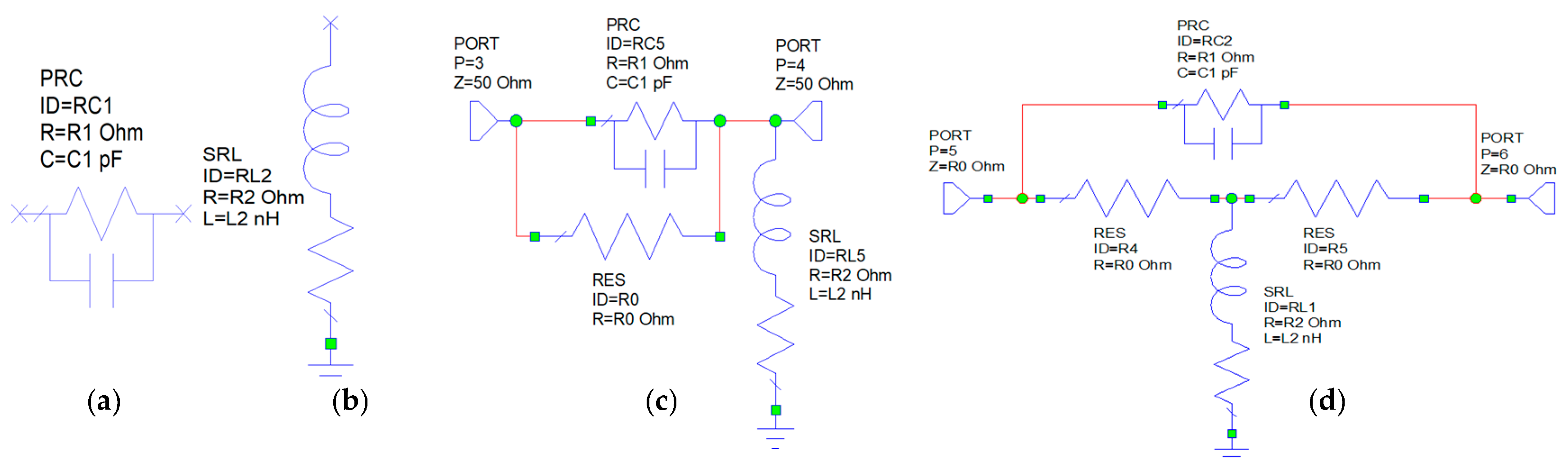

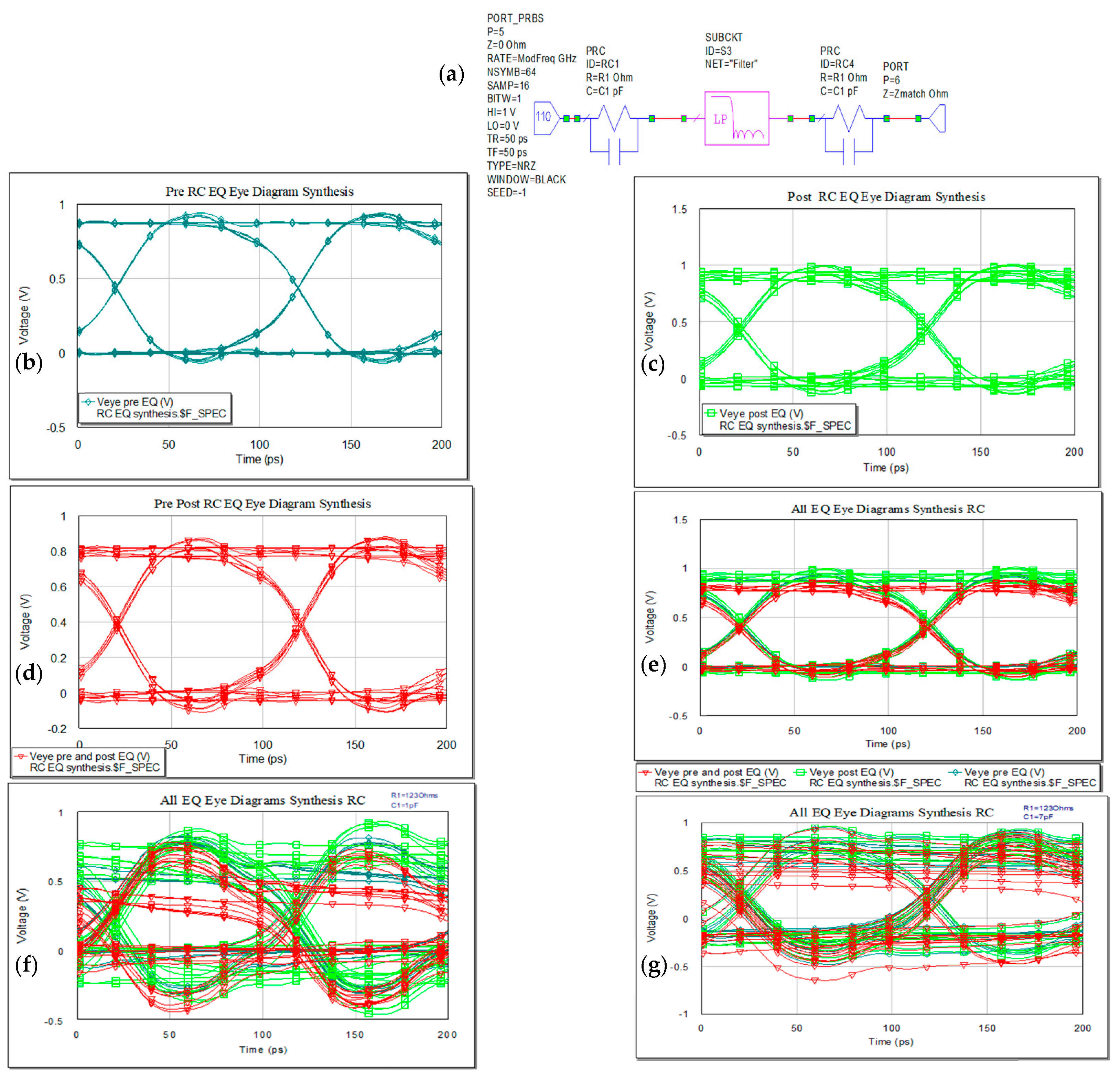

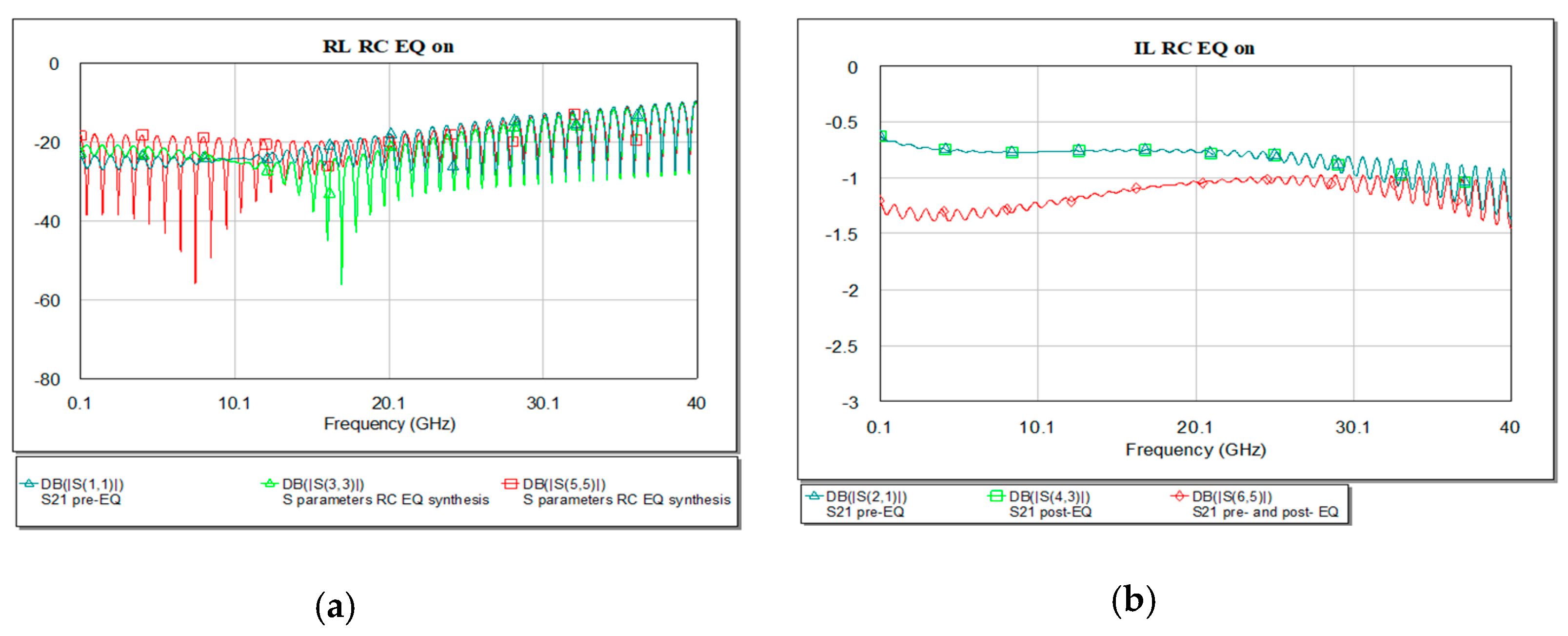

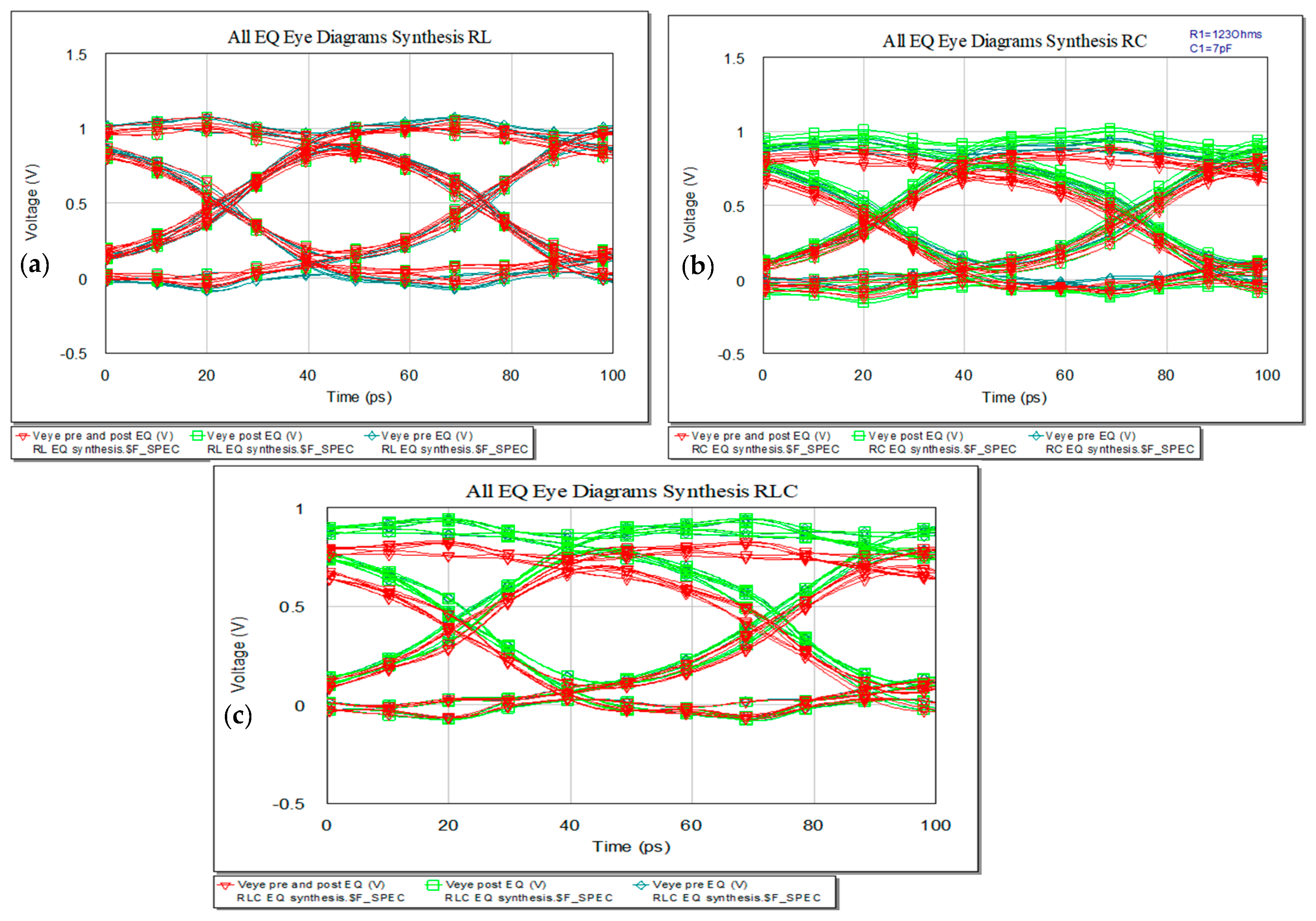

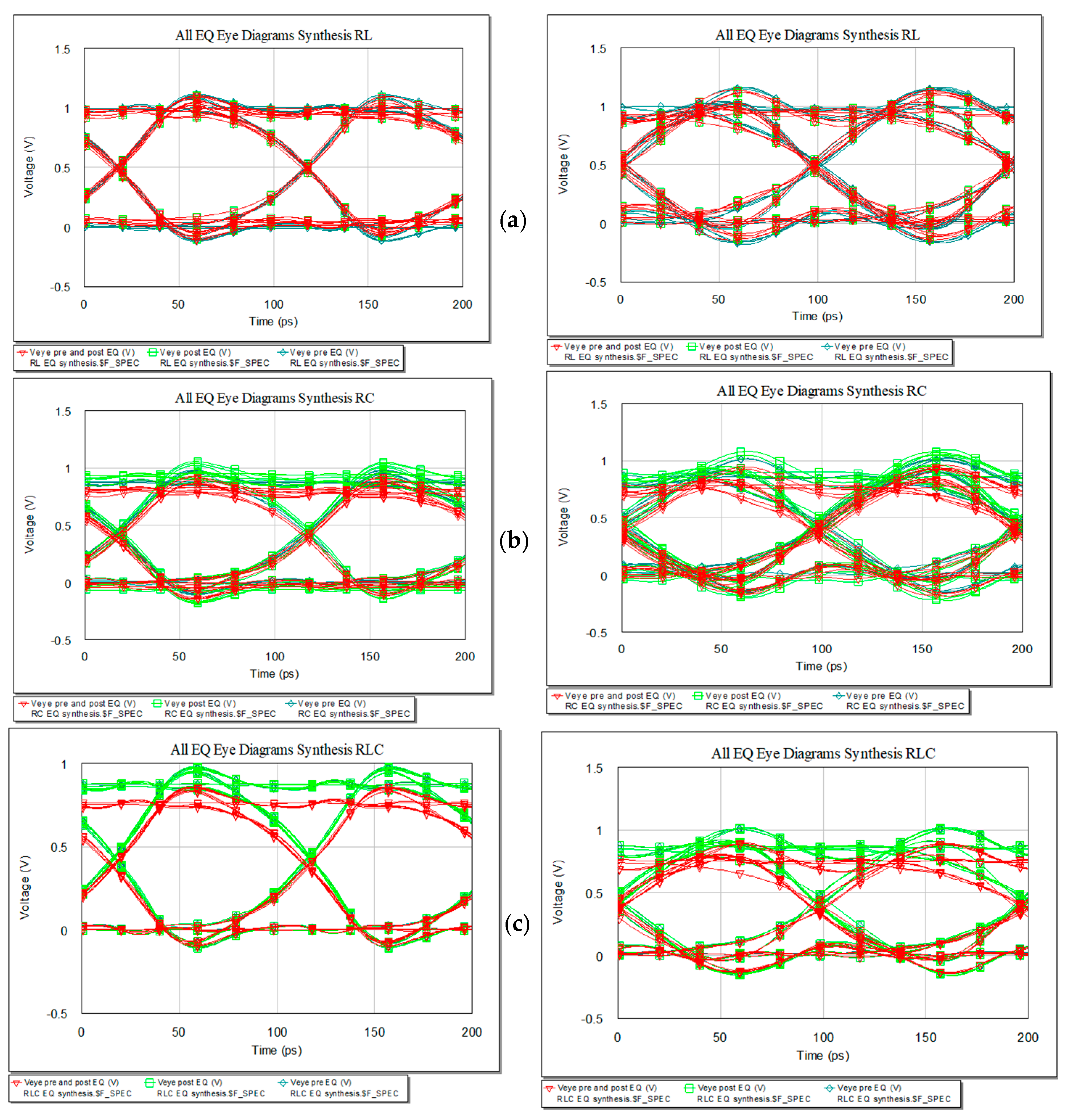

3.1.1. RC EQ

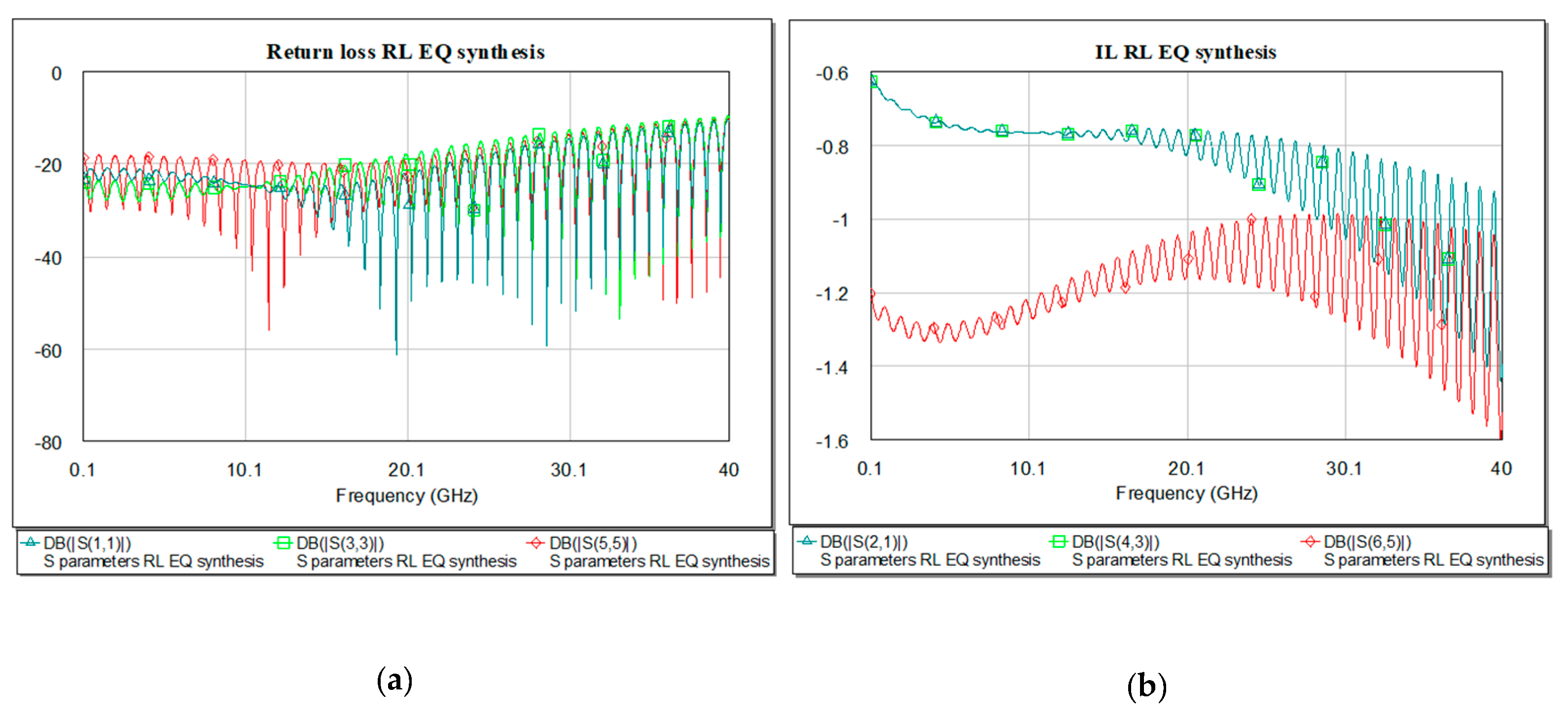

3.1.2. RL EQ

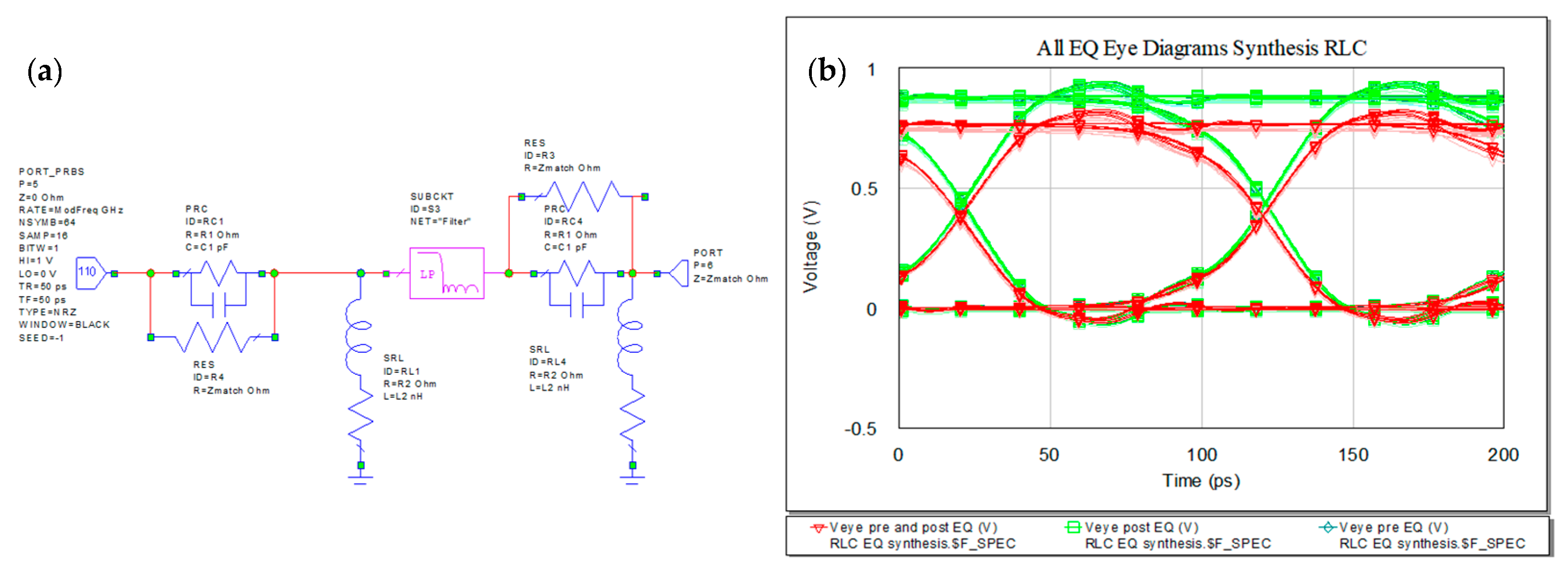

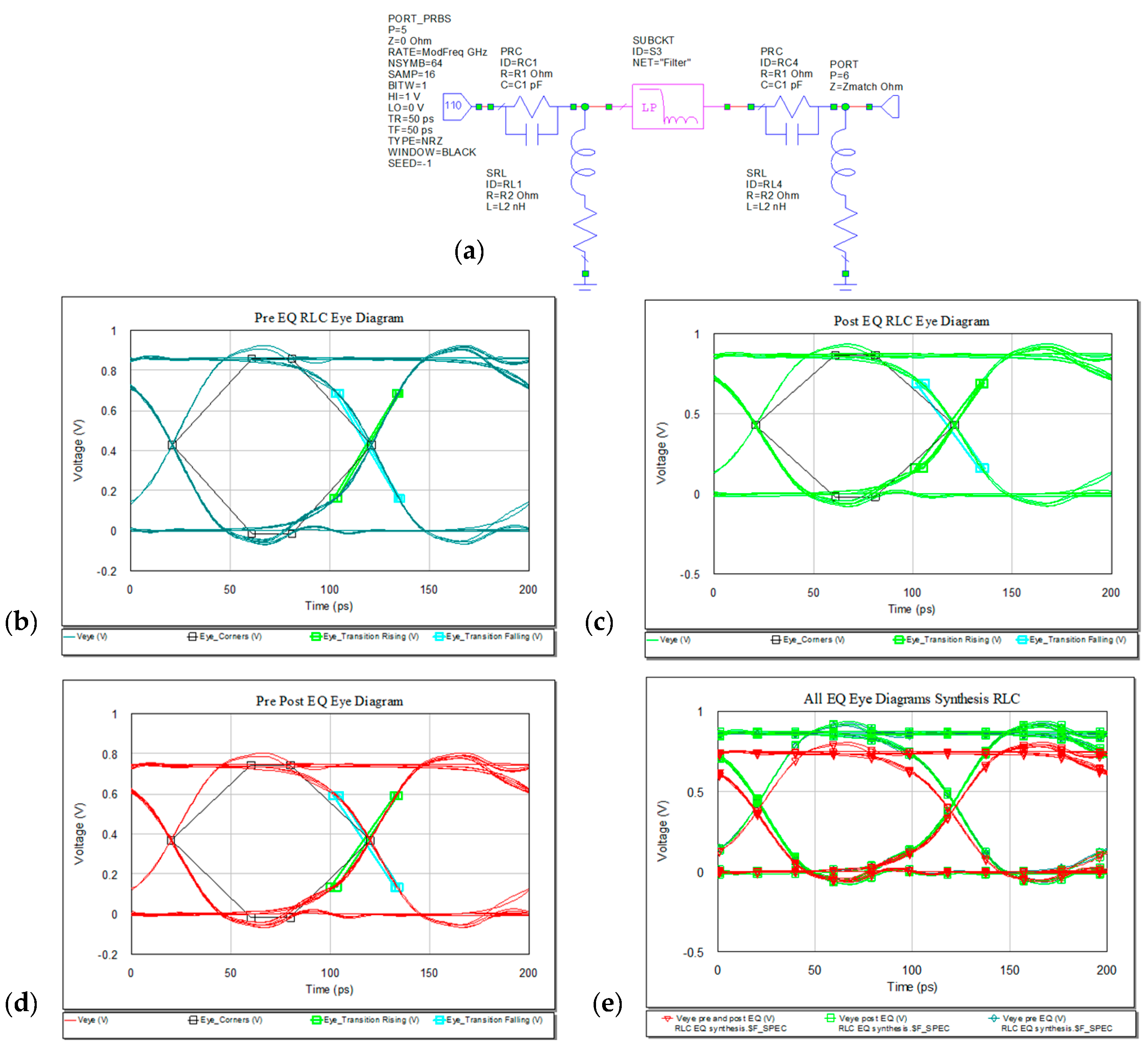

3.1.3. RLC EQ

3.1.4. Bridge T EQ

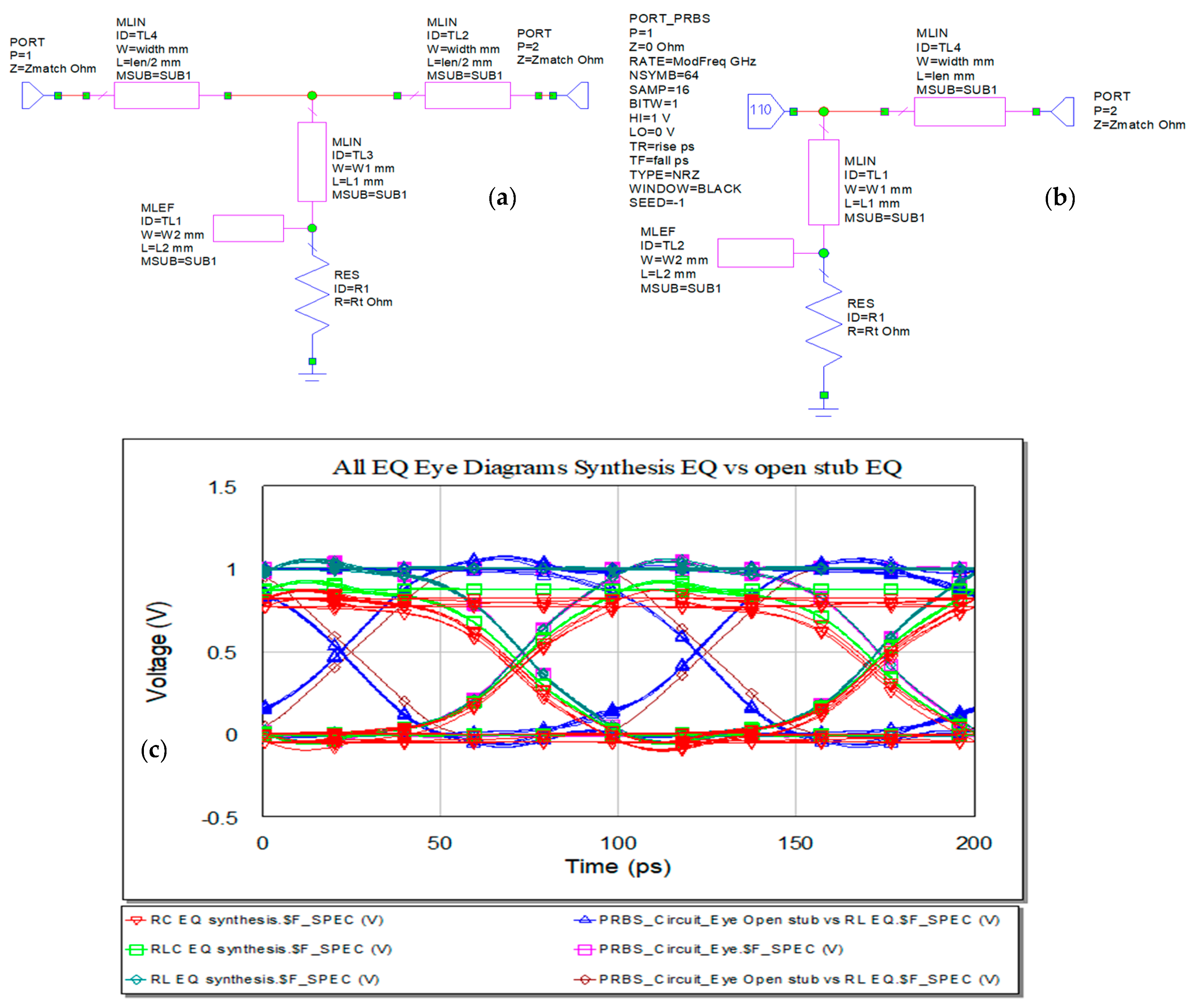

3.2. Passive EQ—Distributed Parameters

4. Discussion and Conclusions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| ARBS | Arbitrary Bit Sequence |

| AWR | Applied Wave Research |

| BER | Bit Error Rate |

| BITW | Bit Width |

| CRLH | Composite Right/Left-Handed |

| CTLE | Continuous Time Linear Equalizer |

| DFE | Decision Feedback Equalizer |

| DSP | Digital Signal Processing |

| EQ | Equalizer |

| FEC | Forward Error Correction |

| FFE | Feed-Forward Equalizer |

| I/O | Input/Output |

| IL | Insertion loss |

| ISI | Intersymbol interference |

| LMS | Least Mean Square |

| MWO | Microwave Office |

| NRZ | Non Return to Zero |

| PAM | Pulse Amplitude Modulation |

| PCB | Printed Circuit Board |

| PRBS | Pseudo Random Bit Sequence |

| PRC | Parallel RC |

| RC | Resistor Capacitor |

| RLC | Resistor inductor capacitor |

| S | Scattering |

| SI | Signal Integrity |

| SLR | Series LR |

References

- Bode, W.H. Attenuation Equalizer. U.S. Patent 2,096,027,027, 30 January 1936. [Google Scholar]

- Thierauf, S. High-Speed Circuit Board Signal Integrity; Artech House Inc.: Norwood, MA, USA, 2004; pp. 138–150. [Google Scholar]

- Beyene, W.T.; Hahm, Y.C.; Secker, D.; Mullen, D.; Mayandi, N. Measurement and Characterization of Backplanes for Serial Links Operating at 56 Gbps. In Proceedings of the 2015 IEEE 65th Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 26–29 May 2015. [Google Scholar]

- Moreira, J.; Roth, B.; Werkmann, H.; Klapproth, L.; Howeison, M.; Broman, M.; Ouedraogo, W.; Lin, M. An Active Test Fixture Approach for 40 Gbps and Above At-Speed Testing Using a Standard ATE System, Engineering, Computer Science. In Proceedings of the 22nd Asian Test Symposium, Jiaosi Township, Japan, 18–21 November 2013. [Google Scholar]

- Hall, S.H. Advanced Signal Integrity for High-Speed Digital Designs; John Wiley & Sons Inc.: Hoboken, NJ, USA, 2009. [Google Scholar]

- AWR DE, 15.0 1r Rev8, Microwave Office. Available online: http://www.awr.com (accessed on 8 February 2021).

- Proakis, J.G. Digital Communications; McGraw Hill: New York, NY, USA, 2000. [Google Scholar]

- Horowitz, M.; Yang, C.-K.K.; Sidiropoulos, S. High-speed electrical signaling: Overview and limitations. IEEE Micro 1998, 18, 12–24. [Google Scholar] [CrossRef]

- RO3000® Series Circuit Materials RO3003™, RO3006™, RO3010™ and RO3035™ High Frequency Laminates. Available online: www.rogerscorp.com (accessed on 1 July 2020).

- Reuschel, T.; Preibisch, J.; Scharff, K.; Rimolo-Donadio, R.; Duan, X.; Kwark, Y.H.; Schuster, C. Efficient Prediction of Equalization Effort and Channel Performance for PCB-Based Data Links. IEEE Trans. Compon. Packag. Manuf. Technol. 2017, 7, 1842–1851. [Google Scholar] [CrossRef]

- Liu, J.; Lin, X. Feature−Equalization in high-speed communication systems. IEEE Circuits Syst. Mag. 2004, 4, 4–17. [Google Scholar] [CrossRef]

- Menin, D.; De Pra, A.; Bandiziol, A.; Grollitsch, W.; Nonis, R.; Palestri, P. A Simple Simulation Approach for the Estimation of Convergence and Performance of Fully-Adaptive Equalization in High-Speed Serial Interfaces. IEEE Trans. Compon. Packag. Manuf. Technol. 2019, 9, 2079–2086. [Google Scholar] [CrossRef]

- Wu, H.; Shimanouchi, M.; PengLi, M. Effective Link Equalizations for Serial Links at 112 Gbps and Beyond. In Proceedings of the 2018 IEEE 27th Conference on Electrical Performance of Electronic Packaging and Systems (EPEPS), San Jose, CA, USA, 14–17 October 2018. [Google Scholar]

- Terman, F.E. Radio Engineers’ Handbook; McGraw-Hill: New York, NY, USA, 1943; pp. 244–249. [Google Scholar]

- Huang, S.H.; Kuo, C.W.; Wang, C.C.; Kitazawa, T. Enhanced Passive Equalizer Using the Open Stub Compensation Technique. In Proceedings of the 2014 International Symposium on Electromagnetic Compatibility, Tokyo, Japan, 12–16 May 2014. [Google Scholar]

- Xu, X.; Li, W. A Novel Design and Realization of Microstrip Lumped-like Amplitude Equalizer. In Proceedings of the 2016 IEEE International Conference on Microwave and Millimeter Wave Technology (ICMMT), Beijing, China, 5–8 June 2016. [Google Scholar]

- Beyene, T.W.; Madden, C.; Vaidya, N.; Lan, H. Return Loss Characterization and Analysis of High-Speed Serial Interface. In Proceedings of the 2015 IEEE 24th Electrical Performance of Electronic Packaging and Systems (EPEPS), San Jose, CA, USA, 25–28 October 2015. [Google Scholar]

- Wu, S.M.; Huang, S.H.; Wang, H.Y.; Chiu, C.T.; Hung, C.P.; Kuo, C.W.; Wang, C.C. Enhanced passive equaliser using open-stub, structure. Electron. Lett. 2013, 49, 1528–1529. [Google Scholar] [CrossRef]

- Lv, J.; Bao, Y.; Huang, J. Wideband Low Noise Amplifier Using a Novel Equalization. In Proceedings of the the 2016 Progress in Electromagnetic Research Symposium (PIERS), Shanghai, China, 8–11 August 2016. [Google Scholar]

- Zhou, T.; Huang, J. A novel wideband microwave gain equalizer using SIR branch lines. In Proceedings of the 2014 3rd Asia-Pacific Conference on Antennas and Propagation, Harbin, China, 26–29 July 2014. [Google Scholar]

- He, H.-H.; Xia, L. Microwave L TCC Equalizer Based on Composite Right/Left-Handed Structure. In Proceedings of the 2015 IEEE International Conference on Communication Problem-Solving (ICCP), Guilin, China, 16–18 October 2015. [Google Scholar]

- Park, J.; Ha, M.; Li, Q. DDR Memory Channel Design from Passive Stub Equalizer Perspective. In Proceedings of the DesignCon 2013, Santa Clara, CA, USA, 28–31 January 2013. [Google Scholar]

| Relative Dielectric Constant (/) | Loss Tangent of Dielectric (/) | Dielectric Thickness (mm) | Conductor Thickness (μm) |

|---|---|---|---|

| 3 | 0.001 | 1.524 | 17.5 |

| Transmission Line Parameters | TL1 | TL2 |

|---|---|---|

| Length (mm) | 5 | 4.43 |

| Width (mm) | 0.43 | 1.26 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Brinaru, D. Passive Equalization Networks—Efficient Synthesis Approach for High-Speed Signal Integrity Characterization. Sensors 2021, 21, 1222. https://doi.org/10.3390/s21041222

Brinaru D. Passive Equalization Networks—Efficient Synthesis Approach for High-Speed Signal Integrity Characterization. Sensors. 2021; 21(4):1222. https://doi.org/10.3390/s21041222

Chicago/Turabian StyleBrinaru, Diana. 2021. "Passive Equalization Networks—Efficient Synthesis Approach for High-Speed Signal Integrity Characterization" Sensors 21, no. 4: 1222. https://doi.org/10.3390/s21041222