Evaluation and Reliability Assessment of GaN-on-Si MIS-HEMT for Power Switching Applications

Abstract

:1. Introduction

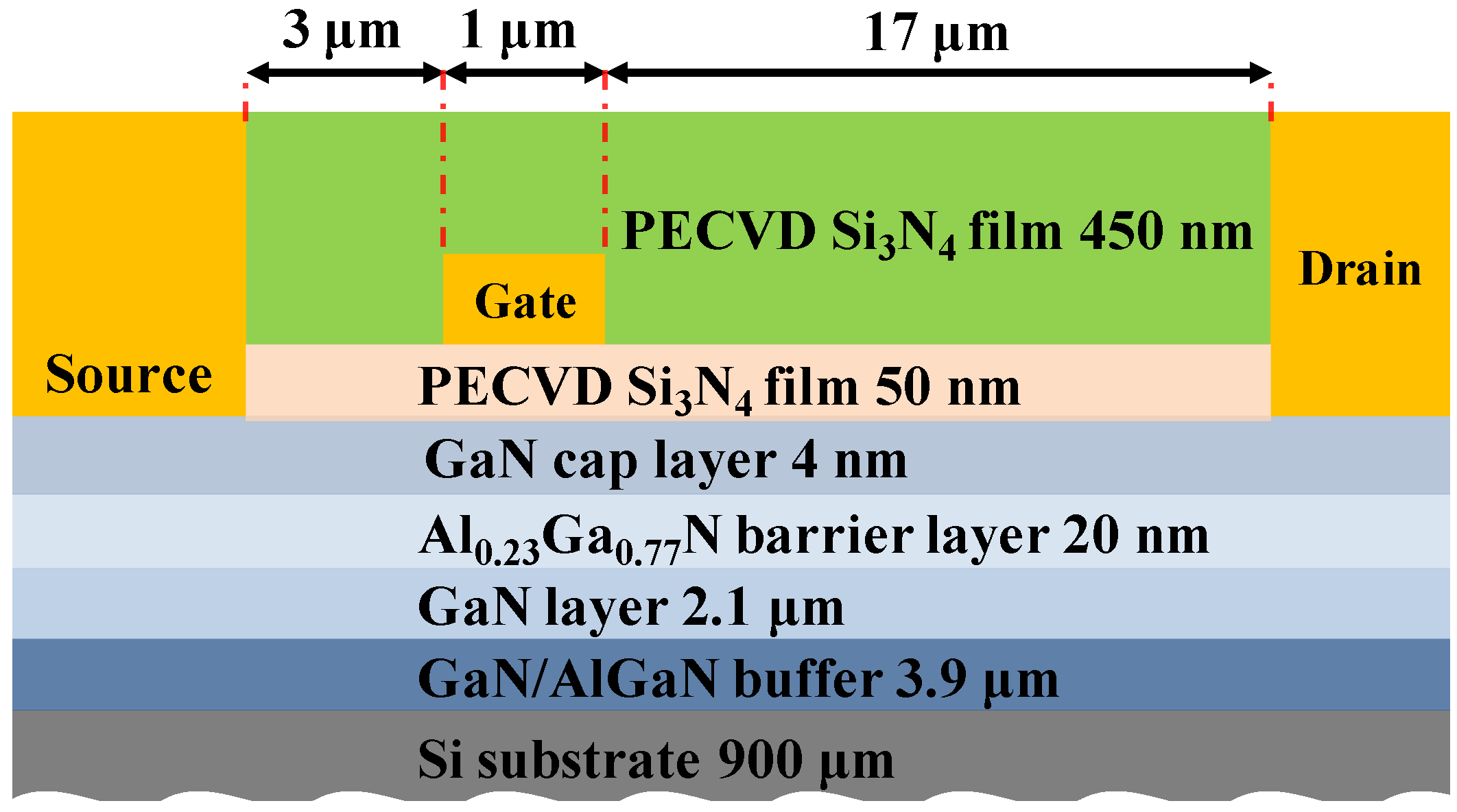

2. Device Structure and Experimental Setup

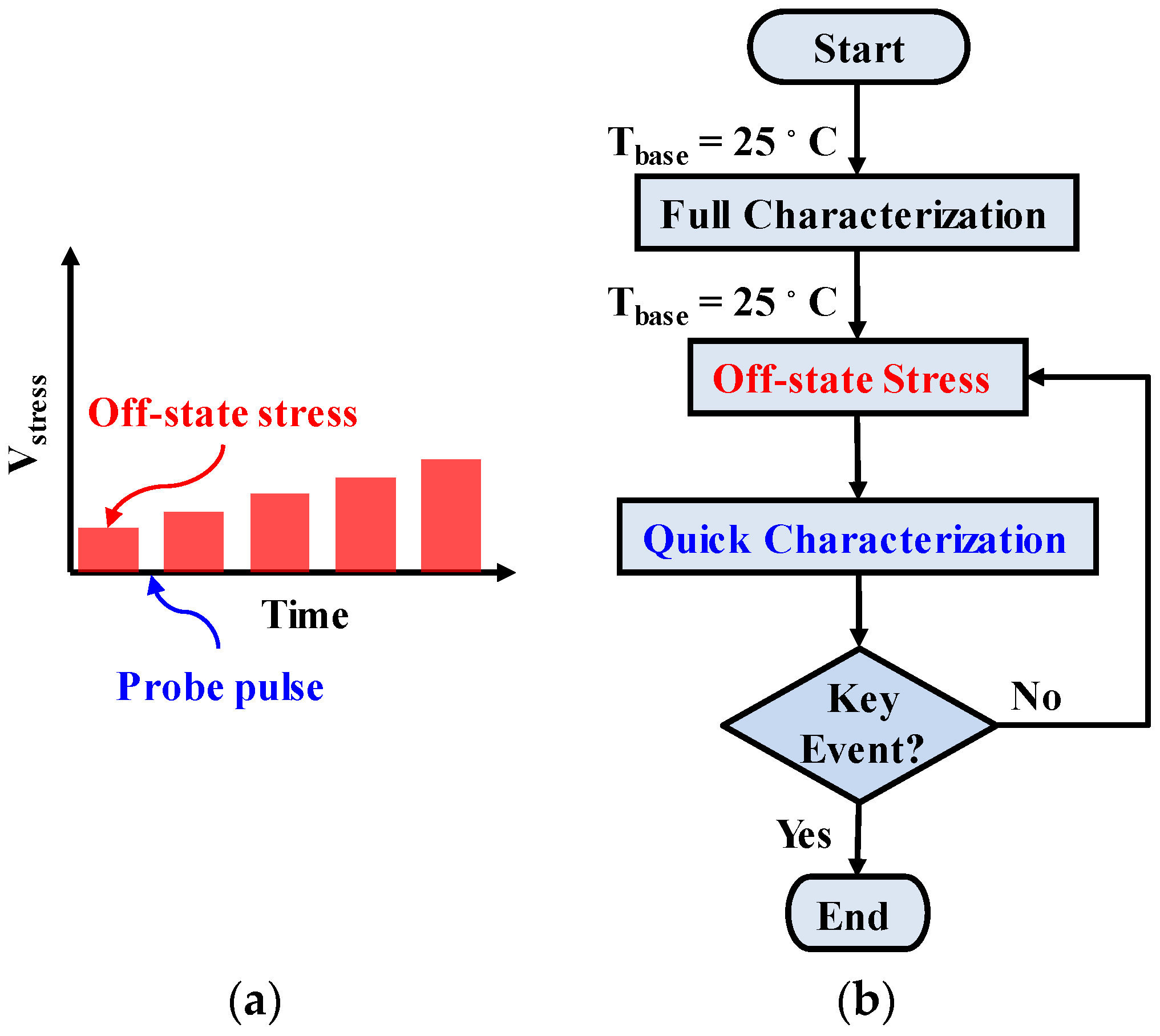

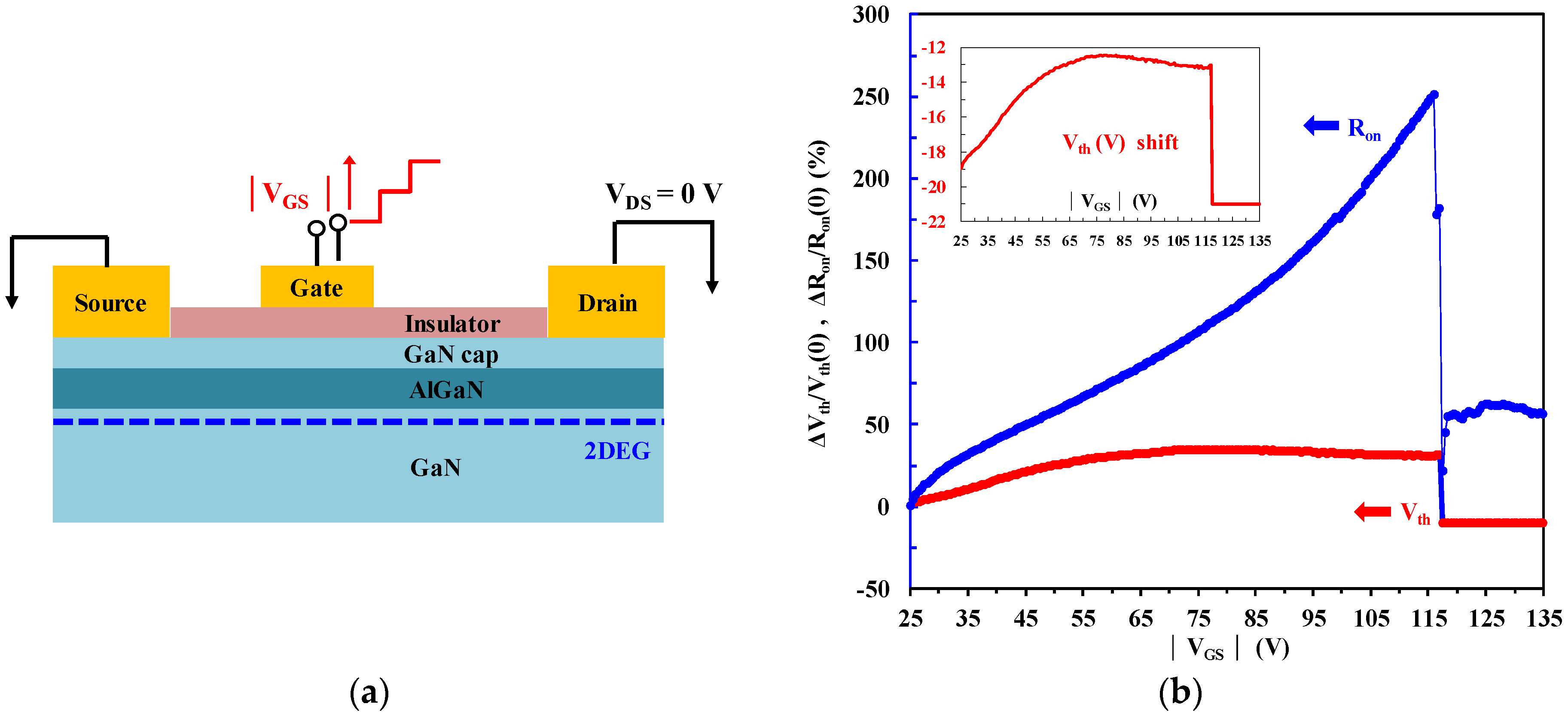

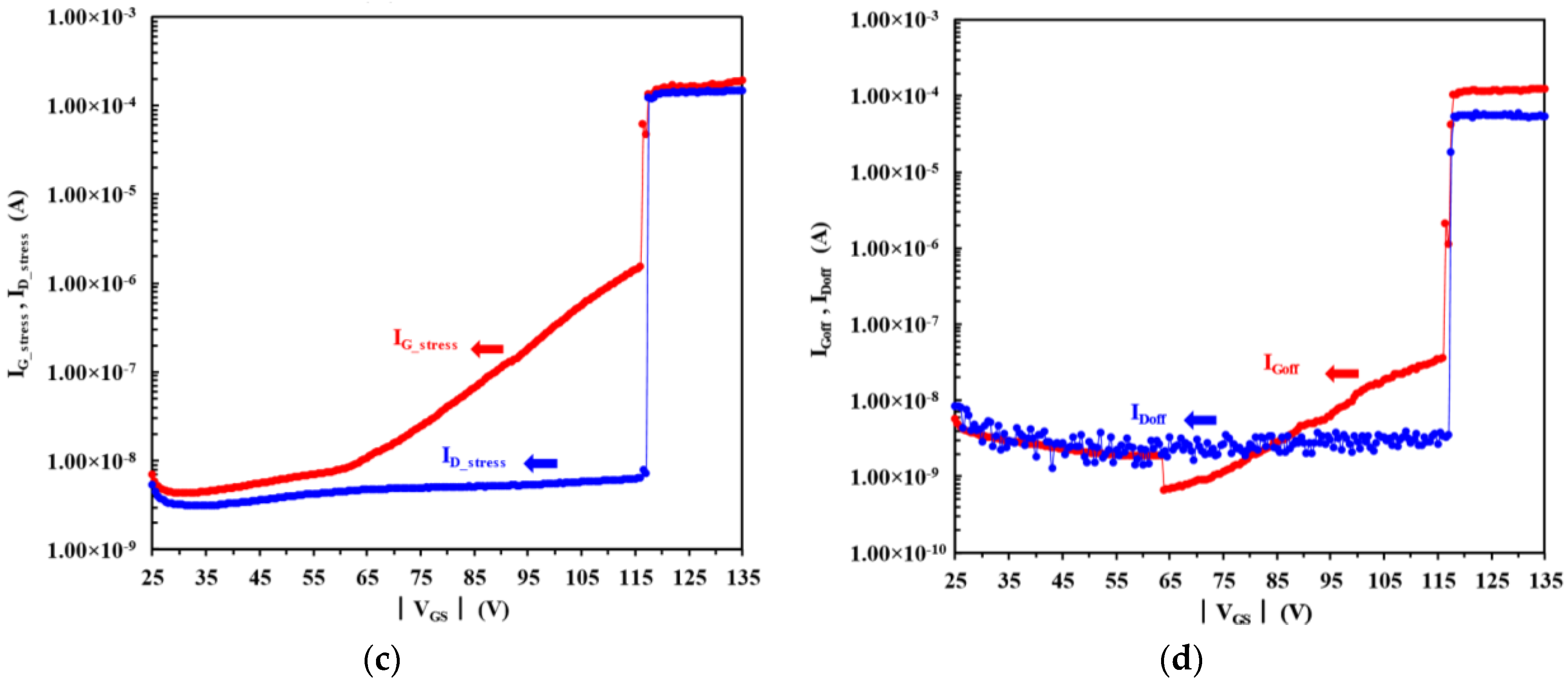

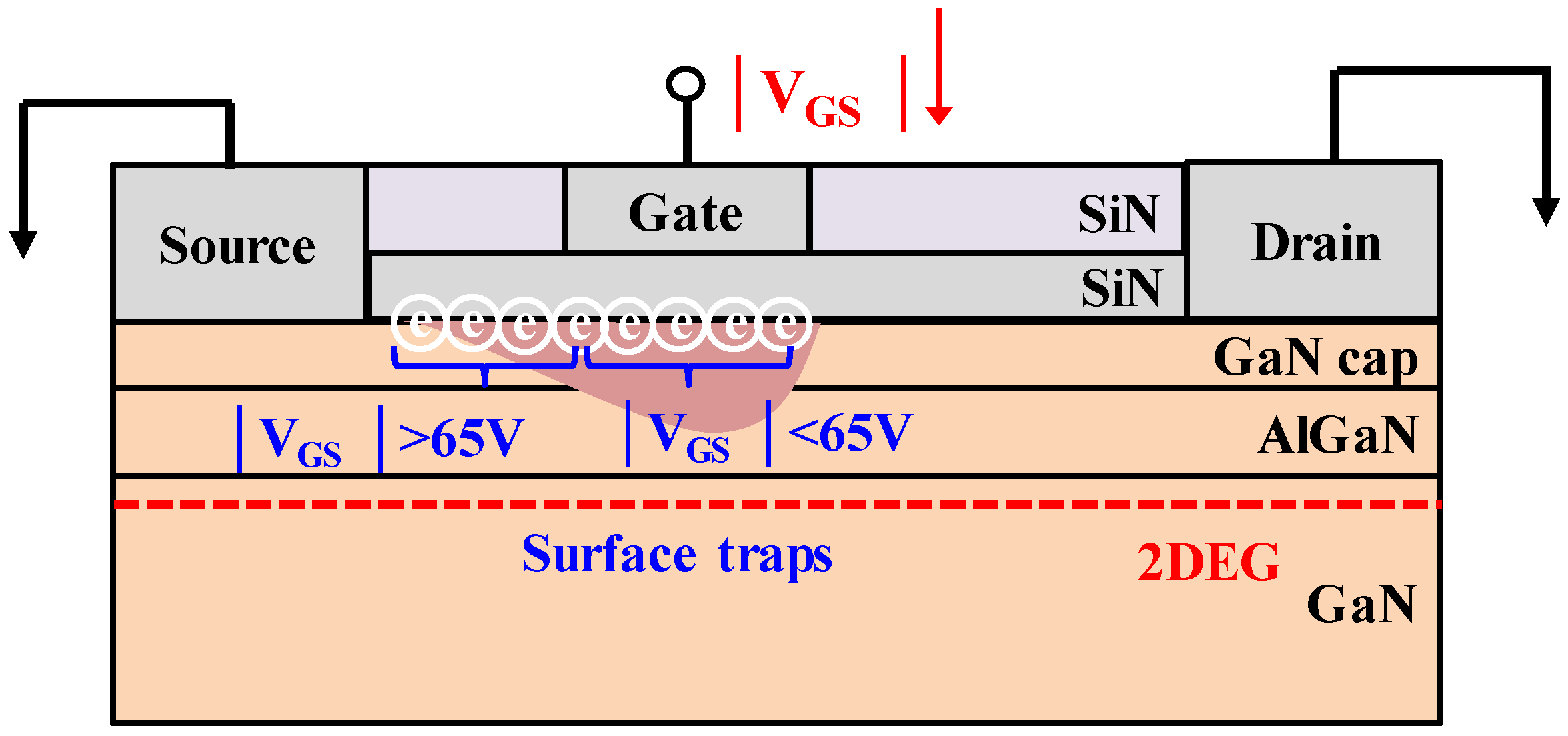

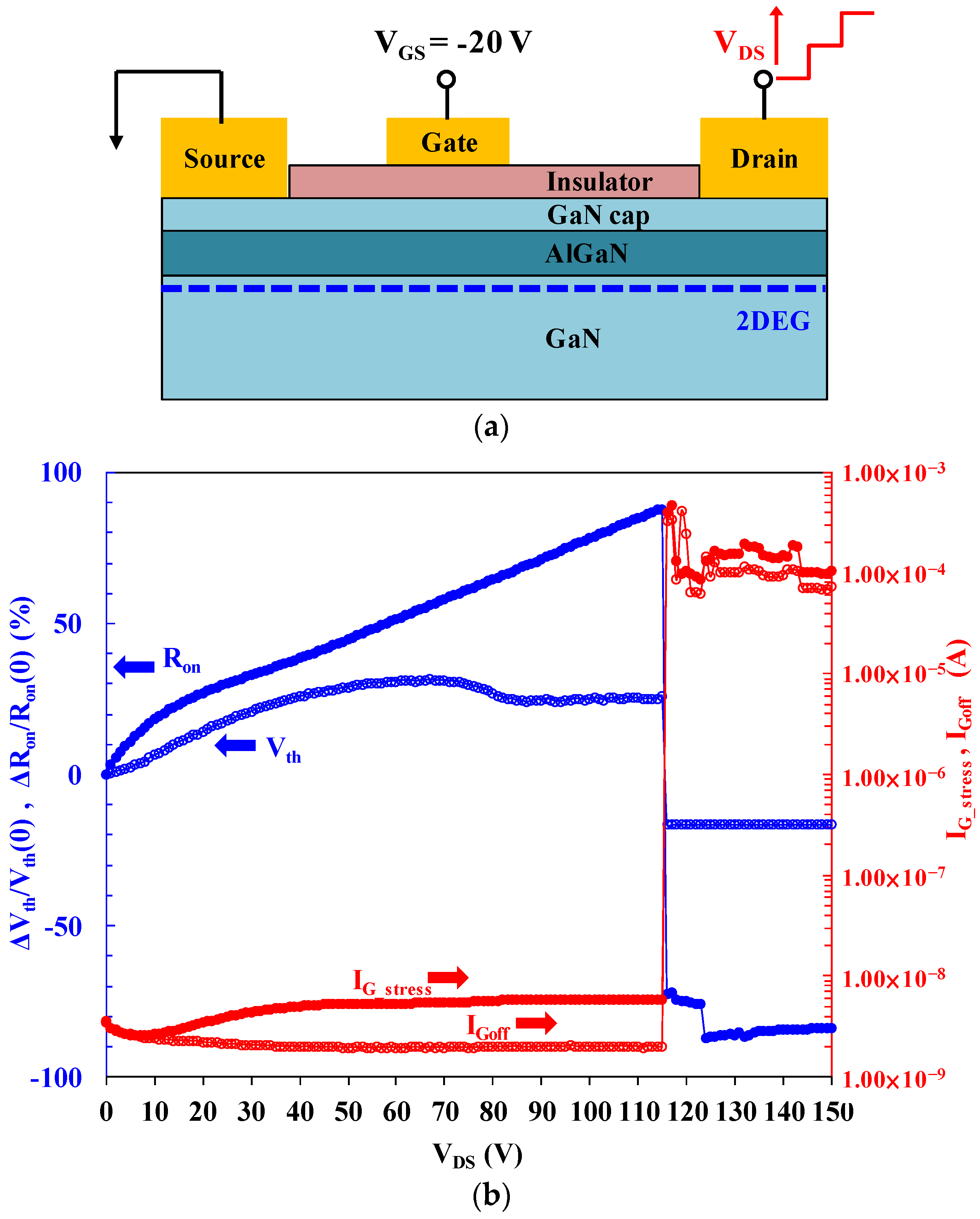

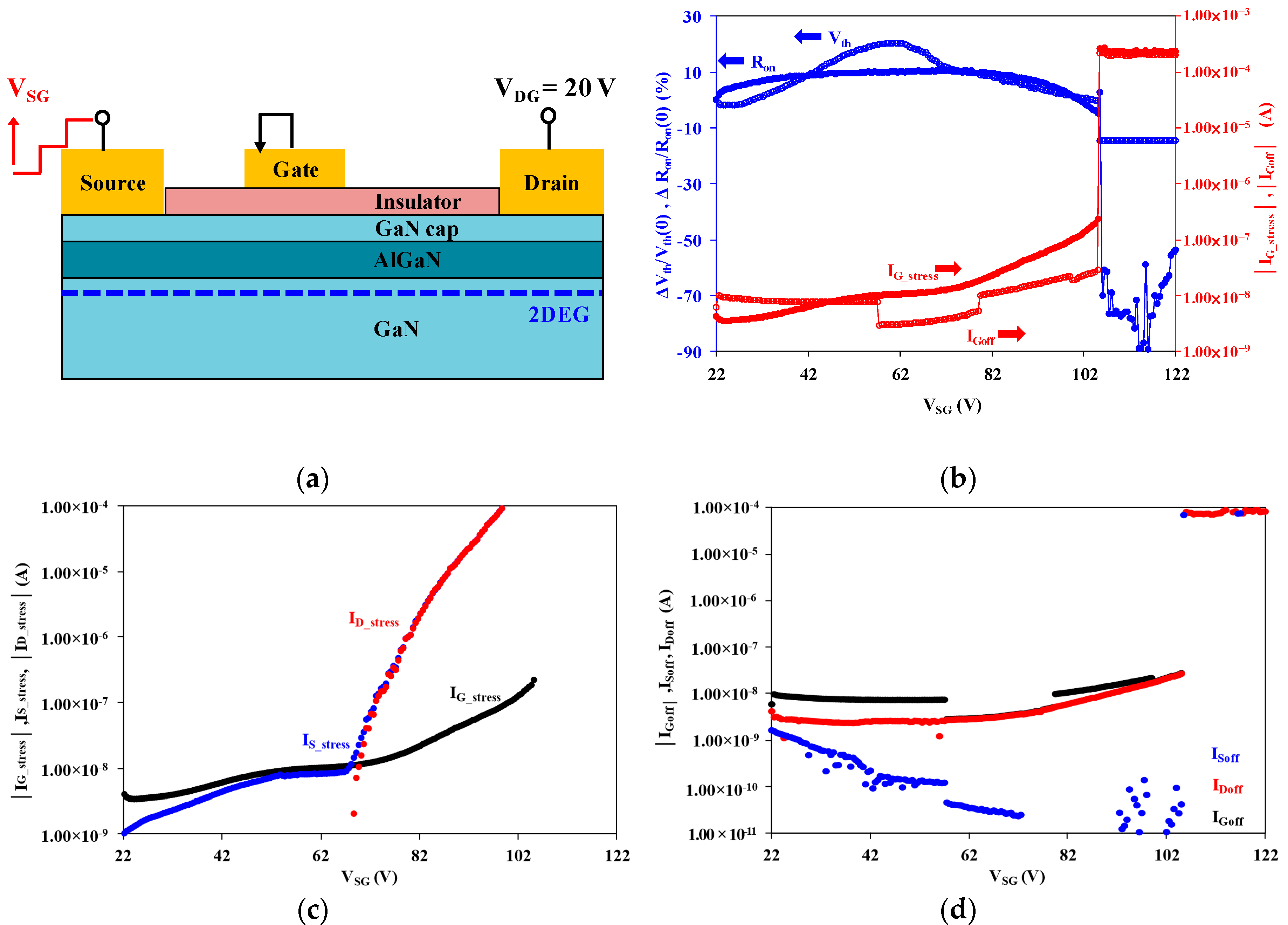

3. Short-Term Step-Stress Experiment

4. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Baliga, B.J. Gallium nitride devices for power electronic applications. Semicond. Sci. Technol. 2013, 28, 074011. [Google Scholar] [CrossRef]

- Mitova, R.; Ghosh, R.; Mhaskar, U.; Klikic, D.; Miao-Xin, W.; Dentella, A. Investigations of 600-V GaN HEMT and GaN diode for power converter applications. IEEE Trans. Power Electron. 2014, 29, 2441–2452. [Google Scholar] [CrossRef]

- Mishra, U.K.; Shen, L.; Kazior, T.E.; Wu, Y. GaN-Based RF Power Devices and Amplifiers. Proc. IEEE 2008, 96, 287–305. [Google Scholar] [CrossRef]

- Endoh, A.; Yamashita, Y.; Ikeda, K.; Higashiwaki, M.; Hikosaka, K.; Matsui, T.; Hiyamizu, S.; Mimura, T. Non-Recessed-Gate enhancement-mode AlGaN/GaN high electron mobility transistors with high RF performance. Jpn. J. Appl. Phys. 2004, 43, 2255–2258. [Google Scholar] [CrossRef]

- Lu, W.; Wang, L.; Gu, S.; Aplin, D.P.R.; Estrada, D.M.; Yu, P.K.L.; Asbeck, P.M. Analysis of reverse leakage current and breakdown voltage in GaN and InGaN/GaN Schottky barriers. IEEE Trans. Electron Devices 2011, 58, 1986–1994. [Google Scholar] [CrossRef]

- Saito, W.; Kuraguchi, M.; Takada, Y.; Tsuda, K.; Omura, I.; Omura, T. Influence of surface defect charge at AlGaN/GaN-HEMT upon Schottky gate leakage current and breakdown voltage. IEEE Trans. Electron Devices 2005, 52, 159–164. [Google Scholar] [CrossRef]

- Wuertl, J.; Bahat-Treidel, E.; Brunner, F.; Cho, E.; Hilt, O.; Ivo, P.; Knauer, A.; Kurpas, P.; Lossy, R.; Schulz, M.; et al. Reliability issues of GaN based high voltage power devices. J. Microelectron. Reliab. 2011, 51, 1710–1716. [Google Scholar]

- Meneghesso, G.; Verzellesi, G.; Danesin, F.; Rampazzo, F.; Zanon, F.; Tazzoli, A.; Meneghini, M.; Zanoni, E. Reliability of GaN high-electron-mobility transistors: State of the art and perspectives. IEEE Trans. Device Mater. Reliab. 2008, 8, 332–343. [Google Scholar] [CrossRef]

- Joh, J.; del Alamo, J.A. Impact of electrical degradation on trapping characteristics of GaN high electron mobility transistors. In Proceedings of the IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2008; pp. 461–464.

- Meneghesso, G.; Meneghini, M.; Rossetto, I.; Bisi, D.; Stoffels, S.; Van Hove, M.; Decoutere, S.; Zanoni, E. Reliability and parasitic issues in GaN-based power HEMTs: A review. Semicond. Sci. Technol. 2016, 31, 093004. [Google Scholar] [CrossRef]

- Zanoni, E.; Meneghini, M.; Meneghesso, G.; Bisi, D.; Rossetto, I.; Stocco, A. Reliability and failure physics of GaN HEMT, MISHEMT and p-gate HEMTs for power switching applications: Parasitic effects and degradation due to deep level effects and timedependent breakdown phenomena. In Proceedings of the IEEE 3rd Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Blacksburg, VA, USA, 2–4 November 2015; p. 75.

- Zanoni, E.; Meneghini, M.; Chini, A.; Marcon, D.; Meneghesso, G. AlGaN/GaN-Based HEMTS failure physics and reliability: Mechanisms affecting gate edge and Schottky junction. IEEE Trans. Electron Devices 2013, 60, 3119–3131. [Google Scholar] [CrossRef]

- Lossy, R.; Gargouri, H.; Arens, M.; Würfl, J. Gallium nitride MIS-HEMT using atomic layer deposited Al2O3 as gate dielectricas gate dielectric. J. Vac. Sci. Technol. A 2013, 31. [Google Scholar] [CrossRef]

- Liu, S.-C.; Chen, B.-Y.; Lin, Y.-C.; Hsieh, T.-E.; Wang, H.-C.; Chang, E.Y. GaN MIS-HEMTs with nitrogen passivation for power device applications. IEEE Electron Device Lett. 2014, 35, 1001–1003. [Google Scholar]

- Hsieh, T.E.; Yi-Chang, E.; Song, Y.Z.; Lin, Y.C.; Wang, H.C.; Liu, S.C.; Salahuddin, S.; Hu, C.C. Gate Recessed Quasi-normally OFF Al2O3/AlGaN/GaN MIS-HEMT with Low Threshold Voltage Hysteresis using PEALD AlN Interfacial Passivation Layer. IEEE Electron Device Lett. 2014, 35, 732–734. [Google Scholar]

- Hsieh, T.-E.; Lin, Y.-C.; Liao, J.-T.; Lan, W.-C.; Chin, P.-T.; Yi-Chang, E. Effect of high voltage stress on the DC performance of the Al2O3/AlN GaN metal–insulator–semiconductor high-electron mobility transistor for power applications. Appl. Phys. Express 2015, 8, 104102. [Google Scholar] [CrossRef]

- Bahl, S.R.; van Hove, M.; Kang, X.; Marcon, D.; Zahid, M.; Decoutere, S. New source-side breakdown mechanism in AlGaN/GaN insulated-gate HEMTs. In Proceedings of the 25th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Kanazawa, Japan, 26–30 May 2013; pp. 419–422.

- Lu, Y.Y.; Li, B.K.; Tang, X.; Jiang, Q.M.; Yang, S.; Tang, Z.K.; Chen, K.J. Normally OFF Al2O3-AlGaN/GaN MIS-HEMT with Transparent Gate Electrode for Gate Degradation Investigation. IEEE Trans. Electron Devices 2015, 62, 821–827. [Google Scholar] [CrossRef]

- Chou, P.C.; Cheng, S. Performance characterization of gallium nitride HEMT cascode switch for power conditioning applications. Mater. Sci. Eng. B 2015, 198, 43–50. [Google Scholar] [CrossRef]

- Huang, X.; Liu, Z.; Li, Q.; Lee, F.C. Evaluation and application of 600 V GaN HEMT in cascode structure. In Proceedings of the 2013 Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 17–21 March 2013; pp. 1279–1286.

- Kikkawa, T.; Hosoda, T.; Imanishi, K.; Shono, K.; Itabashi, K.; Ogino, T.; Miyazaki, Y.; Mochizuki, A.; Kiuchi, K.; Kanamura, M.; et al. 600 V JEDEC-Qualified Highly Reliable GaN HEMTs on Si Substrates. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2014; pp. 40–43.

- Wong, K.-Y.; Lin, Y.S.; Hsiung, C.W.; Lansbergen, G.P.; Lin, M.C.; Yao, F.W.; Yu, C.J.; Chen, P.C.; Su, R.Y.; Yu, J.L.; et al. AlGaN/GaN MIS-HFET with Improvement in High Temperature Gate Bias Stress-induced Reliability. In Proceedings of the IEEE 26th International Symposium on Power Semiconductor Devices & IC’s (ISPSD), Waikoloa, HI, USA, 15–19 June 2014; pp. 370–373.

- Meneghini, M.; Bisi, D.; Marcon, D.; Stoffels, S.; van Hove, M.; Wu, T.; Decoutere, S.; Meneghesso, G.; Zanoni, E. Trapping and Reliability Assessment in D-Mode GaN-Based MIS-HEMTs for Power Applications. IEEE Trans. Power Electron. 2014, 29, 2199–2207. [Google Scholar] [CrossRef]

- Wu, T.; Marcon, D.; Zahid, M.; van Hove, M.; Decoutere, S.; Groeseneken, G. Comprehensive investigation of on-state stress on d-mode AlGaN/GaN MIS-HEMTs. In Proceedings of the IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 14–18 April 2013; pp. 3C.5.1–3C.5.7.

- Del Alamo, J.A.; Joh, J. GaN HEMT reliability. Microelectron. Reliab. 2009, 49, 1200–1206. [Google Scholar] [CrossRef]

- Joh, J.; del Alamo, J.A. Critical Voltage for Electrical Degradation of GaN High Electron Mobility Transistors. IEEE Electron Device Lett. 2008, 29, 287–289. [Google Scholar] [CrossRef]

- Joh, J.; del Alamo, J.A.; Langworthy, K.; Xie, S.; Zheleva, T. Role of stress voltage on structural degradation of GaN high-electron-mobility transistors. Microelectron. Reliab. 2011, 51, 201–206. [Google Scholar] [CrossRef]

- Gao, F.; Tan, S.; del Alamo, J.; Thomson, C.; Palacios, T. Impact of water-assisted electrochemical reactions on the OFF-state degradation of AlGaN/GaN HEMTs. IEEE Trans. Electron Device. 2014, 61, 437–444. [Google Scholar] [CrossRef]

- Marcon, D.; Meneghesso, G.; Wu, T.-L.; Stoffels, S.; Meneghini, M.; Zanoni, E.; Decoutere, S. Reliability analysis of permanent degradations on AlGaN/GaN HEMTs. IEEE Trans. Electron Devices 2013, 60, 3132–3141. [Google Scholar] [CrossRef]

- Chowdhury, U.; Jimenez, J.L.; Lee, C.; Beam, E.; Saunier, P.; Balistreri, T.; Park, S.-Y.; Lee, T.; Wang, J.; Kim, M.J.; et al. TEM Observation of Crack- and Pit-Shaped Defects in Electrically Degraded GaN HEMTs. IEEE Electron Device Lett. 2008, 29, 1098–1100. [Google Scholar] [CrossRef]

- Joh, J.; Gao, F.; Palacios, T.; del Alamo, J.A. A model for the critical voltage for electrical degradation of GaN high electron mobility transistors. Microelectron. Reliab. 2010, 50, 767–773. [Google Scholar] [CrossRef]

- Demirtas, S.; del Alamo, J.A. Critical voltage for electrical reliability of GaN High Electron Mobility Transistors on Si Substrate. Microelectron. Reliab. 2010, 50, 758–762. [Google Scholar] [CrossRef]

- Meneghini, M.; Bisi, D.; Marcon, D.; Stoffels, S.; van Hove, M.; Wu, T.-L.; Decoutere, S.; Meneghesso, G.; Zanoni, E. Trapping in GaN-based metal-insulator-semiconductor transistors: Role of high drain bias and hot electrons. Appl. Phys. Lett. 2014, 104, 143505. [Google Scholar] [CrossRef]

- Jin, D.; Joh, J.; Krishnan, S.; Tipirneni, N.; Pendharkar, S.; del Alamo, J.A. Total current collapse in High-Voltage GaN MIS-HEMTs induced by Zener trapping. In Proceedings of the IEEE International Electron Devices Meeting, Washington, DC, USA, 9–11 December 2013; pp. 148–151.

- Liu, Z. Characterization and Failure Mode Analysis of Cascode GaN HEMT. Master’s Thesis, Virginia Polytechnic Institute and State University, Blacksburg, VA, USA, 2014. [Google Scholar]

| Parameters | Definition |

|---|---|

| IGoff | Gate leakage current. Measured at VGS = −20 V and VDS = 0 V. |

| IDoff | Drain leakage current. Measured at VGS = −20 V and VDS = 0 V. |

| ISoff | Source leakage current. Measured at VGS = −20 V and VDS = 0 V. |

| IG_stress | Gate stress current. Measured at the 29th second (step-stress on gate and source) or 179th second (step-stress on drain). |

| ID_stress | Drain stress current. Measured at the 29th second (step-stress on gate and source) or 179th second (step-stress on drain). |

| IS_stress | Source stress current. Measured at the 29th second (step-stress on gate and source) or 179th second (step-stress on drain). |

| IDlin | Linear-regime drain current. Measured at VGS = 0 V and VDS = 1 V. |

| IDmax | Maximum drain current. Measured at VGS = 0 V and VDS = 10 V. |

| Vth | Threshold voltage. Defined as VGS at IDS = 1 mA/mm for VDS = 1 V. |

| Ron | Device’s on-resistance. Defined as the inverse of IDlin. |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license ( http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chou, P.-C.; Chen, S.-H.; Hsieh, T.-E.; Cheng, S.; Del Alamo, J.A.; Chang, E.Y. Evaluation and Reliability Assessment of GaN-on-Si MIS-HEMT for Power Switching Applications. Energies 2017, 10, 233. https://doi.org/10.3390/en10020233

Chou P-C, Chen S-H, Hsieh T-E, Cheng S, Del Alamo JA, Chang EY. Evaluation and Reliability Assessment of GaN-on-Si MIS-HEMT for Power Switching Applications. Energies. 2017; 10(2):233. https://doi.org/10.3390/en10020233

Chicago/Turabian StyleChou, Po-Chien, Szu-Hao Chen, Ting-En Hsieh, Stone Cheng, Jesús A. Del Alamo, and Edward Yi Chang. 2017. "Evaluation and Reliability Assessment of GaN-on-Si MIS-HEMT for Power Switching Applications" Energies 10, no. 2: 233. https://doi.org/10.3390/en10020233