Highly-Efficient and Compact 6 kW/4 × 125 kHz Interleaved DC-DC Boost Converter with SiC Devices and Low-Capacitive Inductors

Abstract

:1. Introduction

2. Description of the System

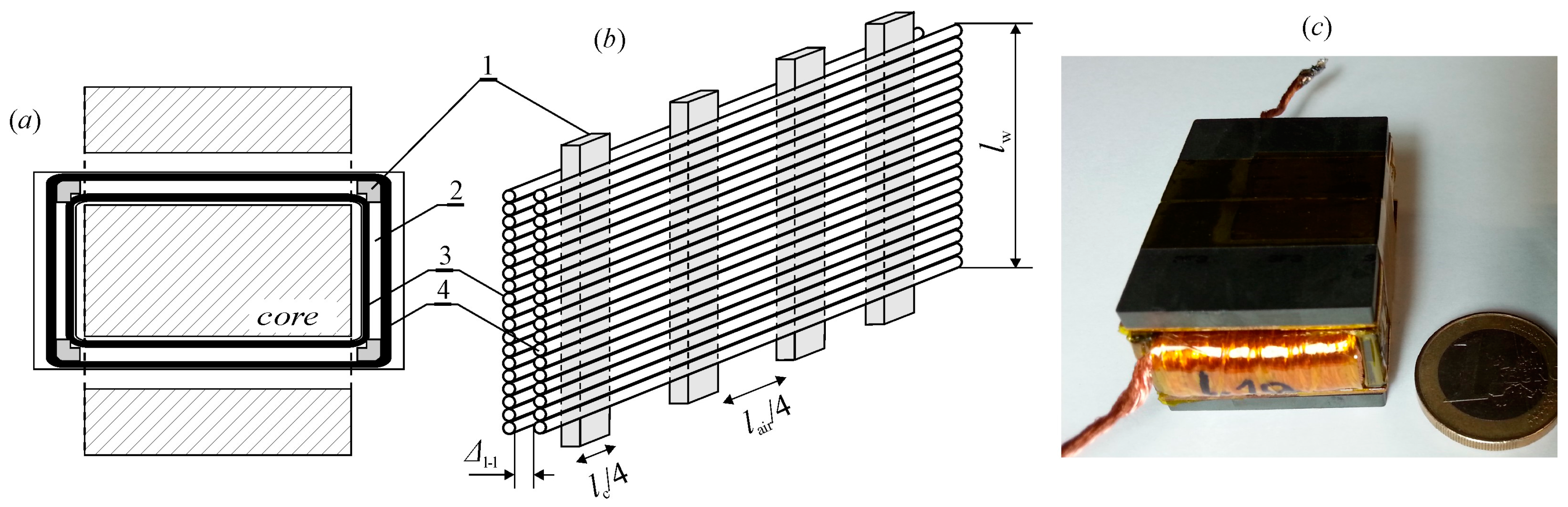

3. Low-Capacitive Inductors

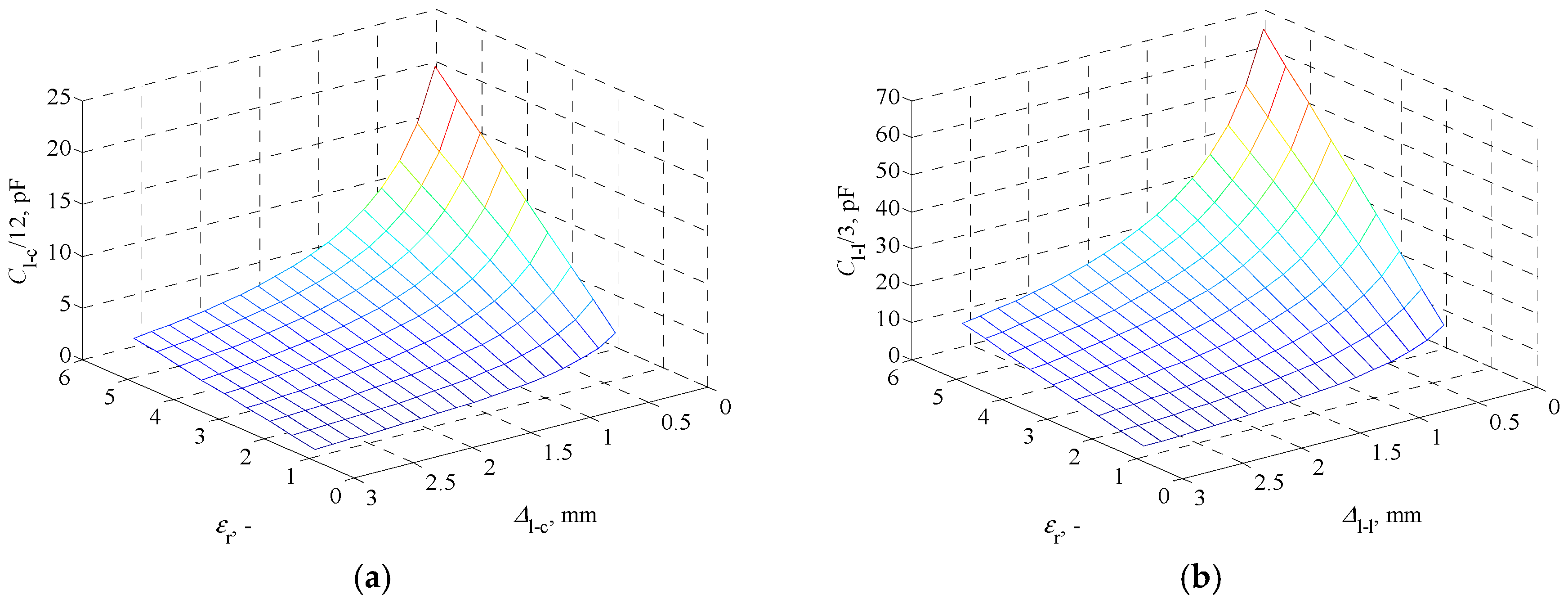

3.1. Parasitic Capacitance of Windings

3.2. Low-Capacitive Design

4. Laboratory Model of the Four-Leg, 6 kW Interleaved DC-DC Boost Converter

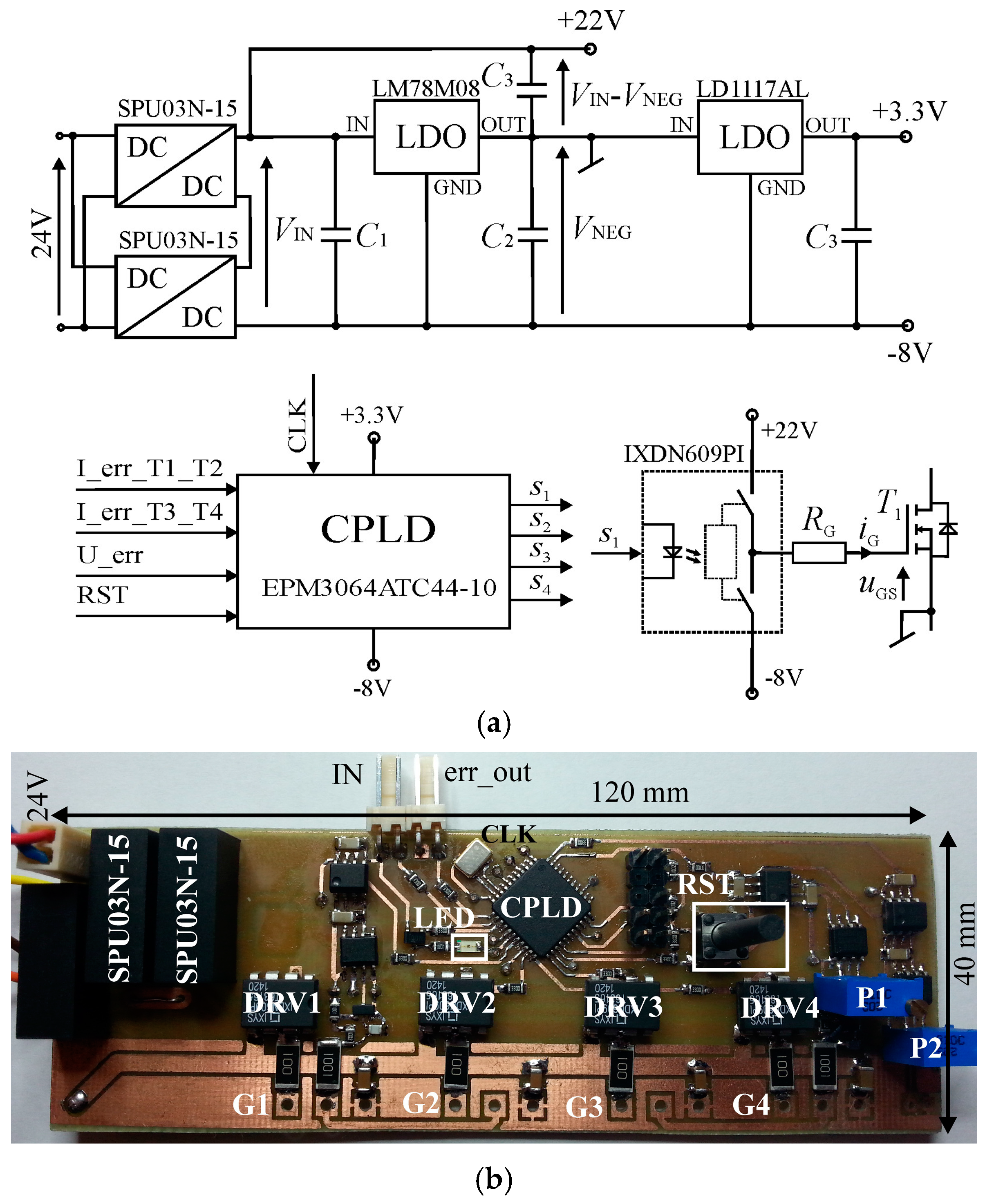

4.1. System Layout

4.2. Gate Driver and Protection

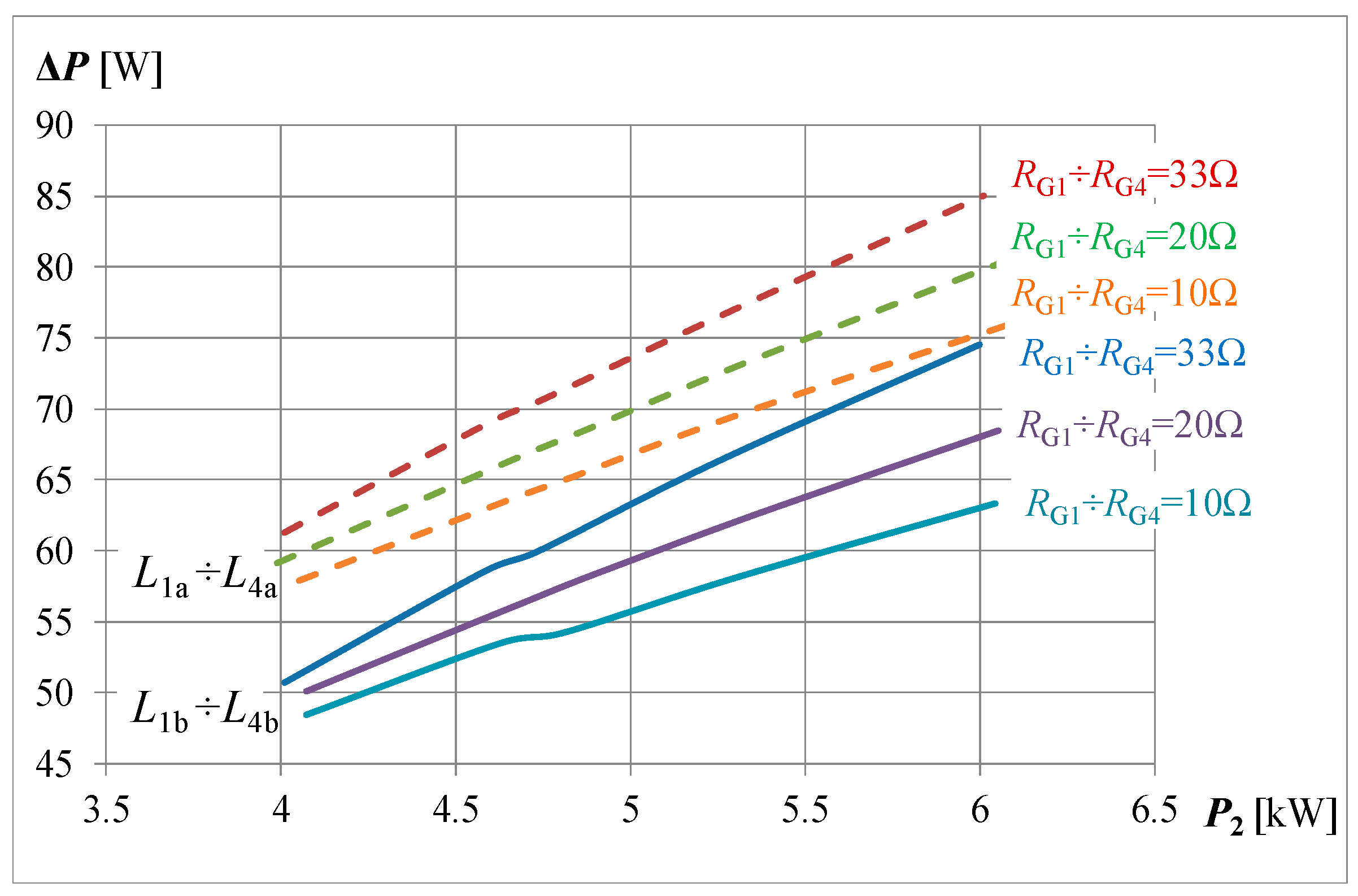

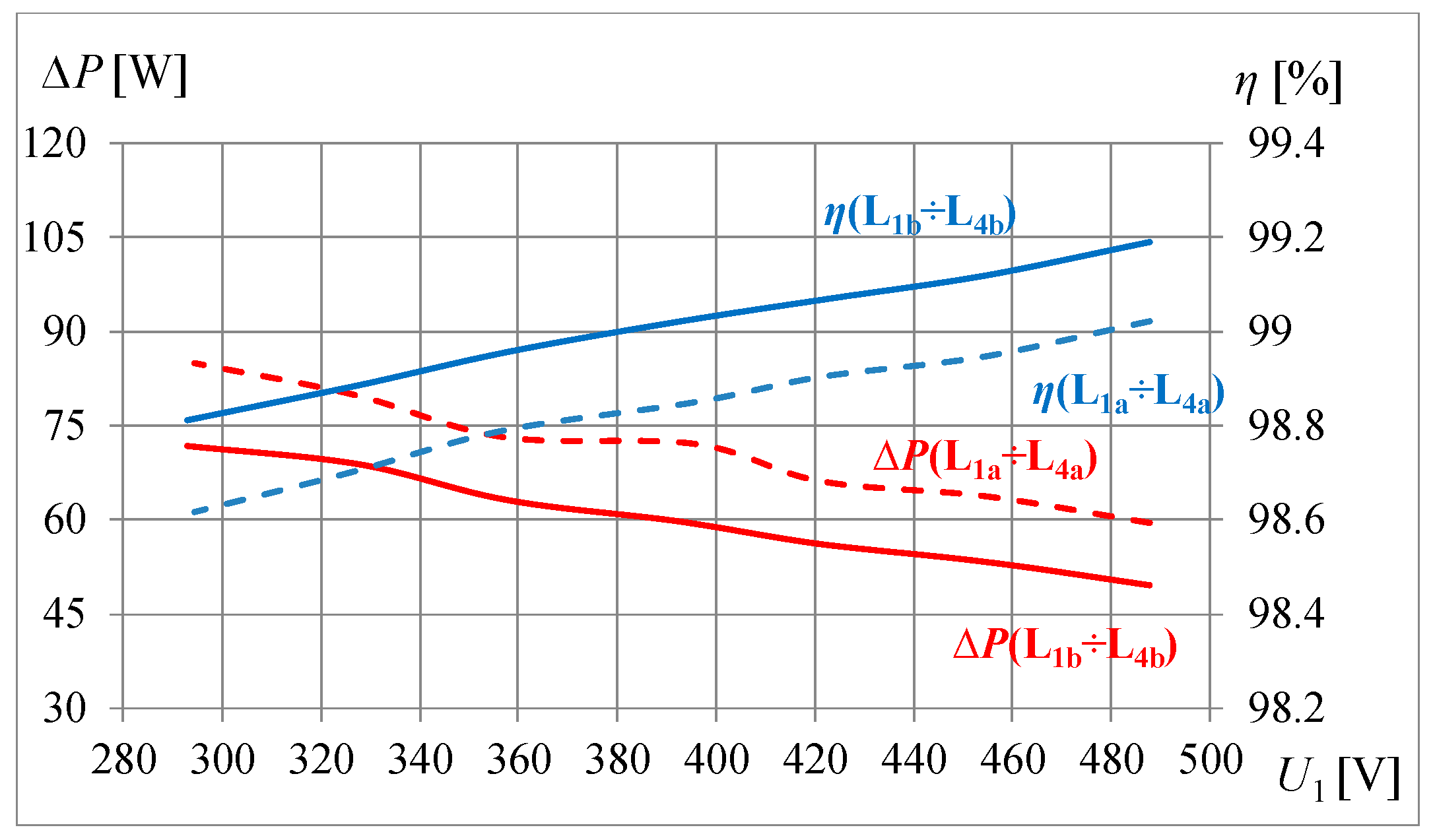

5. Experiments

6. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Milan, J.; Gondignon, P.; Perpina, X.; Perez-Tomas, A.; Rebollo, J. A survey of wide bandgap power semiconductor devices. IEEE Trans. Power Electron. 2014, 29, 2155–2163. [Google Scholar] [CrossRef]

- Rabkowski, J.; Peftitsis, D.; Nee, H.P. SiC power transistors—A new era in power electronics is initiated. IEEE Ind. Electron. Mag. 2012, 6, 17–26. [Google Scholar] [CrossRef]

- Biela, J.; Schweizer, M.; Waffler, S.; Kolar, J.W. SiC vs. Si—Evaluation of potentials for performance improvement of inverter and DC-DC converter systems by SiC power semiconductors. IEEE Trans. Ind. Electron. 2011, 58, 2872–2882. [Google Scholar] [CrossRef]

- Zhao, C.; Trento, B.; Jiang, L.; Jones, E.A.; Liu, B.; Zhang, Z.; Costinett, D.; Wang, F.F.; Tolbert, L.M.; Jansen, J.F.; et al. Design and implementation of a GaN-based, 100 kHz, 102-W/In3 single-phase inverter. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 824–840. [Google Scholar] [CrossRef]

- Zhong, X.; Wu, X.; Zhou, W.; Cheng, S.; Cheng, K. Design and experimental analysis of a 1 kW, 800 kHz, all-SiC boost DC-DC converter. In Proceedings of the Twenty-Ninth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Fort Worth, TX, USA, 16–20 March 2014; pp. 488–492.

- Whitaker, B.; Barkley, A.; Cole, Z.; Passmore, B.; Martin, D.; McNutt, T.R.; Lostetter, A.B.; Lee, J.S.; Shiozaki, K. A high-density, high-efficiency, isolated on-board vehicle battery charger utilizing silicon carbide power devices. IEEE Trans. Power Electron. 2013, 29, 2606–2617. [Google Scholar] [CrossRef]

- Rabkowski, J.; Peftitsis, D.; Nee, H.-P. Design steps toward a 40-kVA SiC JFET inverter with natural-convection and an efficiency exceeding 99.5%. IEEE Trans. Ind. Appl. 2013, 49, 1589–1598. [Google Scholar] [CrossRef]

- Abou-Alfotouh, A.M.; Radun, A.V.; Chang, H.-R.; Winterhalter, C. A 1-MHz hard-switched silicon carbide DC-DC converter. IEEE Trans. Power Electron. 2006, 21, 880–889. [Google Scholar] [CrossRef]

- Bosshard, R.; Kolar Johann, W. All-SiC 9.5 kW/dm3 on-board power electronics for 50 kW/85 kHz automotive IPT system. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 5, 419–431. [Google Scholar] [CrossRef]

- Hu, Y.; Cao, W.; Finney, S.J.; Xiao, W.; Zhang, F.; McLoone, S.F. New modular structure DC-DC converter without electrolytic capacitors for renewable energy applications. IEEE Trans. Sustain. Energy 2014, 5, 1184–1192. [Google Scholar] [CrossRef]

- Hu, Y.; Zeng, R.; Zhang, J.; Finney, S.J. Design of a modular, high step-up ratio DC-DC converter for HVDC applications integrating offshore wind power. IEEE Trans. Ind. Electron. 2016, 63, 2190–2202. [Google Scholar] [CrossRef]

- Agamy, M.S.; Chi, S.; Elasser, A.; Harfman-Todorovic, M.; Jiang, Y.; Mueller, F.; Tao, F. A high-power-density DC-DC converter for distributed PV architectures. IEEE J. Photovolt. 2013, 3, 791–798. [Google Scholar] [CrossRef]

- Huang, X.; Lee Fred, C.; Li, Q.; Du, W. High-frequency high-efficiency GaN-based interleaved CRM bidirectional buck/boost converter with inverse coupled inductor. IEEE Trans. Power Electron. 2016, 31, 4343–4352. [Google Scholar] [CrossRef]

- Choe, G.-Y.; Kim, J.-S.; Kang, H.-S.; Lee, B.-K. An optimal design methodology of an interleaved boost converter for fuel cell applications. J. Electr. Eng. Technol. 2010, 5, 319–328. [Google Scholar] [CrossRef]

- Hegazy, O.; Mierlo, J.V.; Lataire, P. Analysis, modeling, and implementation of a multidevice DC/DC converter for fuel cell hybrid electric vehicles. IEEE Trans. Power Electron. 2012, 27, 4445–4458. [Google Scholar] [CrossRef]

- Zhang, X.; Mattavelli, P.; Boroyevich, D. Impact of interleaving on input passive components of paralleled DC–DC converters for high power PV applications. In Proceedings of the 15th International Power Electronics and Motion Control Conference (EPE-PEMC), Novi Sad, Serbia, 4–6 September 2012; pp. LS7d.5-1–LS7d.5-6.

- Kosai, H.; Scofield, J.; McNeal, S.; Jordan, B.; Ray, B. Design and performance evaluation of a 200 °C interleaved boost converter. IEEE Trans. Power Electron. 2013, 28, 1691–1699. [Google Scholar] [CrossRef]

- Liu, J.; Wong, K.L.; Allen, S.; Mookken, J. Performance evaluations of hard-switching interleaved DC/DC boost converter with new generation silicon carbide MOSFETs. In Proceedings of the Annual Conference of the IEEE Industrial Electronics Society (IECON), Vienna, Austria, 10–13 November 2013; pp. 1157–1162.

- Gu, Y.; Zhang, D. Interleaved boost converter with ripple cancellation network. IEEE Trans. Power Electron. 2013, 28, 3860–3869. [Google Scholar] [CrossRef]

- Magne, P.; Liu, P.; Bilgin, B.; Emadi, A. Investigation of impact of number of phases in interleaved DC-DC boost converter. In Proceedings of the IEEE Transportation Electrification Conference and Expo (ITEC), Metro Detroit, MI, USA, 14–17 June 2015; pp. 1–6.

- Martinez, W.; Kimura, S.; Imaoka, J.; Yamamoto, M.; Cortes, C.A. Volume comparison of DC-DC converters for electric vehicles. In Proceedings of the IEEE Workshop on Power Electronics and Power Quality Applications (PEPQA), Bogota, Colombia, 2–4 June 2015; pp. 1–6.

- Mouli, G.R.C.; Schijffelen, J.; Bauer, P.; Zeman, M. Design and comparison of a 10kW interleaved boost converter for PV application using Si and SiC devices. IEEE J. Emerg. Sel. Top. Power Electron. 2016, PP. [Google Scholar] [CrossRef]

- Velandia, F.; Martinez, W.; Cortes, C.A.; Noah, M.; Yamamoto, M. Power loss analysis of multi-phase and modular interleaved boost DC-DC converters with coupled inductor for electric vehicles. In Proceedings of the 18th European Conference on Power Electronics and Applications (EPE’16 ECCE Europe), Karlsruhe, Germany, 5–9 September 2016; pp. 1–10.

- Jang, J.; Pidaparthy, S.K.; Lee, S.; Choi, B. Performance of an interleaved boundary conduction mode boost PFC converter with wide band-gap switching devices. In Proceedings of the IEEE 2nd International Future Energy Electronics Conference (IFEEC), Taipei, Taiwan, 1–4 November 2015.

- Zdanowski, M.; Rabkowski, J.; Barlik, R. Design issues of the high-frequency interleaved DC/DC boost converter with silicon carbide MOSFETs. In Proceedings of the 16th European Conference on Power Electronics and Applications (EPE’14-ECCE Europe), Lappeenranta, Finland, 26–28 August 2014; pp. 1–10.

- Zdanowski, M.; Kostov, K.; Rabkowski, J.; Nee, H.P. The role of the parasitic capacitance in boost converters with normally-on SiC JFETs. In Proceedings of the 7th International Power Electronics and Motion Control Conference (IPEMC), Harbin, China, 2–5 June 2012; pp. 1842–1847.

- Zdanowski, M.; Kostov, K.; Rabkowski, J.; Barlik, R.; Nee, H.P. Design and evaluation of reduced self-capacitance inductor in DC/DC converters with fast-switching SiC transistors. IEEE Trans. Power Electron. 2014, 29, 2492–2499. [Google Scholar] [CrossRef]

- C2M0080120D Datasheet from Cree Inc. Available online: www.cree.com (accessed on 10 February 2017).

- IDH10S120 Datasheet from Infineon Technologies AG. Available online: www.infineon.com (accessed on 10 February 2017).

- Snelling, E.C. Soft Ferrities—Properties and Applications; Chemical Rubber Company (CRC): Boca Raton, FL, USA, 1969. [Google Scholar]

- Weber, S.; Schinkel, M.; Guttowski, S.; John, W.; Reichl, H. Calculating parasitics capacitance of three-phase common-mode chokes. In Proceedings of the Power Conversion Intelligent Motion (PCIM), Nuremberg, Germany, 20–25 May 2005; pp. 1–6.

- Venkatachalani, K.; Sullivan, C.R.; Abdallah, T.; Tacca, H. Accurate prediction of ferrite core loss with nonsinusoidal waveforms using only Steinmetz parameters. In Proceedings of the IEEE Workshop on Computers in Power Electronics, Mayaguez, Puerto Rico, 3–4 June 2002; pp. 36–41.

- Hurley, W.G.; Wölfle, W.H. Transformers and Inductors for Power Electronics: Theory, Design and Applications; John Wiley & Sons: Hoboken, NJ, USA, 2013. [Google Scholar]

- Kondrath, N.; Kazimierczuk, M.K. Inductor winding loss owing to skin and proximity effects including harmonics in non-isolated pulse-width modulated DC-DC converters operating in continuous conduction mode. IET Power Electron. 2010, 3, 989–1000. [Google Scholar] [CrossRef]

| Symbol | Quantity | Value |

|---|---|---|

| V1 | input voltage range | 290–485 V |

| V2 | output voltage range | 650–700 V |

| Pn | nominal power | 6 kW |

| D | duty cycle range | 0.25–0.55 |

| fs | switching frequency | 4 × 125 kHz |

| L1–L4 | inductance of input inductors | 220 μH |

| IL_m | inductor maximum current | 9 A |

| C1 | input capacitor | 220 nF/1 kV |

| C2 | output capacitor | 6 μF/700 V + 4 × 47 nF/1 kV |

| T1–T4 | SiC transistors | 1.2 kV/80 mΩ (C2M0080120D) |

| D1–D4 | SiC diodes | 1.2 kV/10 A (IDH10S120) |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license ( http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zdanowski, M.; Rabkowski, J.; Barlik, R. Highly-Efficient and Compact 6 kW/4 × 125 kHz Interleaved DC-DC Boost Converter with SiC Devices and Low-Capacitive Inductors. Energies 2017, 10, 363. https://doi.org/10.3390/en10030363

Zdanowski M, Rabkowski J, Barlik R. Highly-Efficient and Compact 6 kW/4 × 125 kHz Interleaved DC-DC Boost Converter with SiC Devices and Low-Capacitive Inductors. Energies. 2017; 10(3):363. https://doi.org/10.3390/en10030363

Chicago/Turabian StyleZdanowski, Mariusz, Jacek Rabkowski, and Roman Barlik. 2017. "Highly-Efficient and Compact 6 kW/4 × 125 kHz Interleaved DC-DC Boost Converter with SiC Devices and Low-Capacitive Inductors" Energies 10, no. 3: 363. https://doi.org/10.3390/en10030363