A High-Power-Density Single-Phase Rectifier Based on Three-Level Neutral-Point Clamped Circuits

Abstract

:1. Introduction

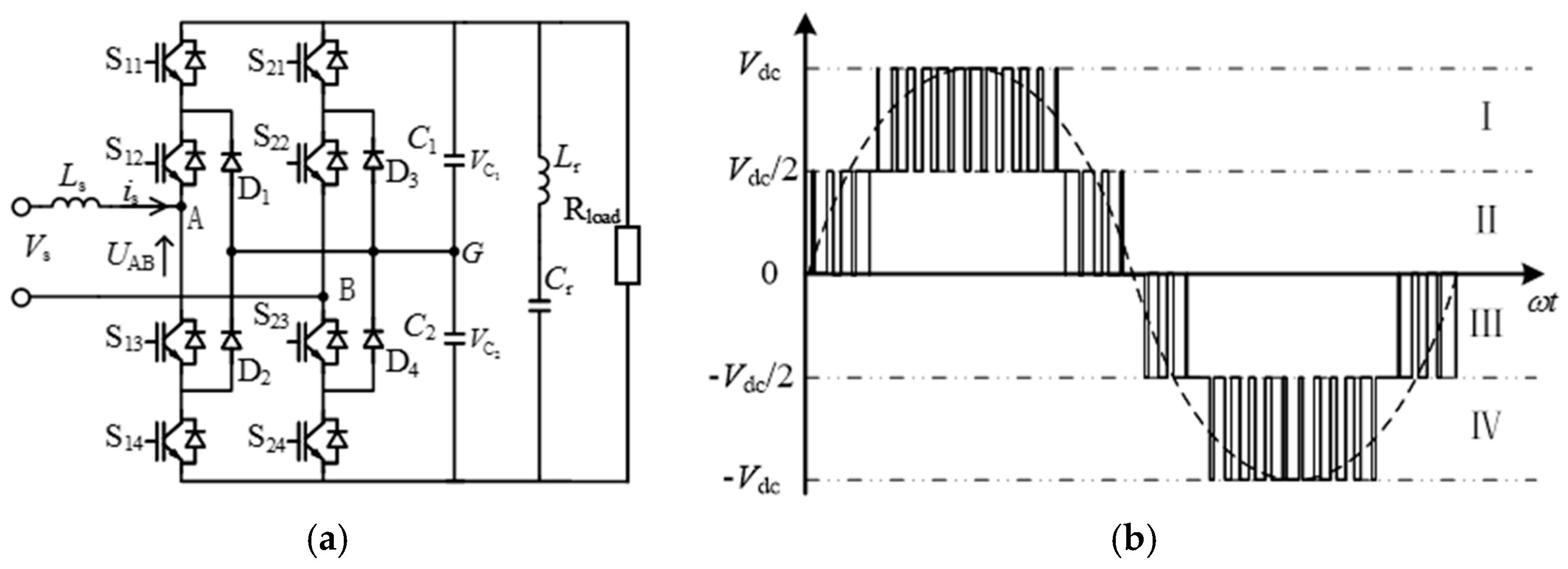

2. Configuration

- (a)

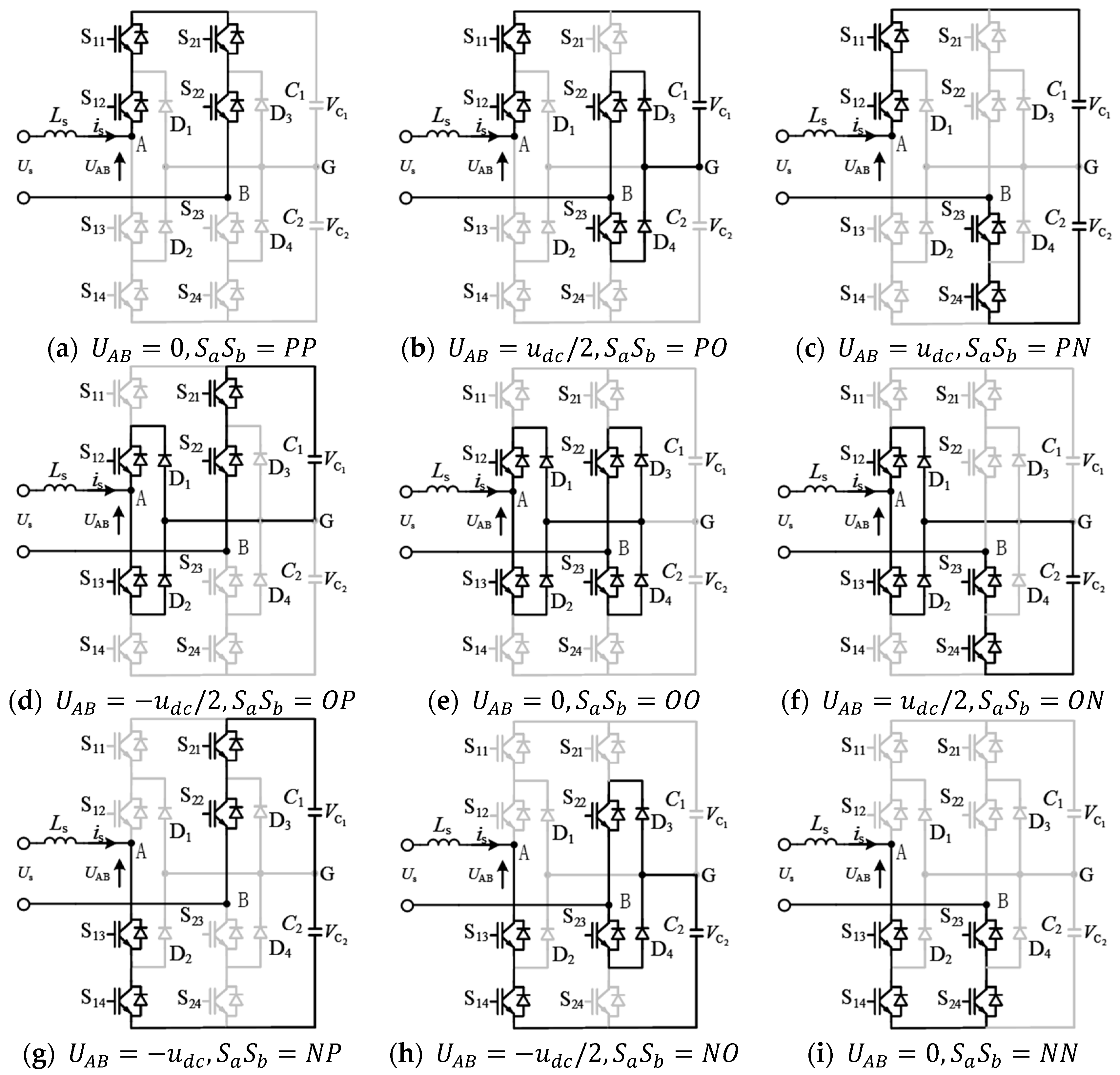

- State 1: Switches S11, S12, S21, and S22 are on, while the others are off. The input voltage UAB is zero, and input has no effect on C1 or C2. When is > 0, the current passes through the parallel diode of S11 and S12 first, and then passes through the S21 and S22. When is < 0, the current passes through the parallel diode of S21 and S22 first, and then passes through the S11 and S12.

- (b)

- State 2: Switches S11, S12, S22, and S23 are on, while the others are off. The input voltage UAB is VC1, and C1 is charged when is > 0 and discharged when is < 0, while input has no effect on C2.

- (c)

- State 3: Switches S11, S12, S23, and S24 are on, while the others are off. The input voltage UAB is VC1 + VC2, and C1 and C2 are charged when is > 0 and discharged when is < 0.

- (d)

- State 4: Switches S12, S13, S21, and S22 are on, while the others are off. The input voltage UAB is −VC1, and C1 is discharged when is > 0 and charged when is < 0, while input has no effect on C2.

- (e)

- State 5: Switches S12, S13, S22, and S23 are on, while the others are off. The input voltage UAB is zero, and input has no effect on C1 or C2.

- (f)

- State 6: Switches S12, S13, S23, and S24 are on, while the others are off. The input voltage UAB is VC2, and C2 is charged when is > 0 and discharged when is < 0, while input has no effect on C1.

- (g)

- State 7: Switches S13, S14, S21, and S22 are on, while the others are off. The input voltage UAB is −VC1-VC2, and C1 and C2 are discharged when is > 0 and charged when is < 0.

- (h)

- State 8: Switches S13, S14, S22, and S23 are on, while the others are off. The input voltage UAB is −VC2, and C2 is discharged when is > 0 and charged when is < 0, while input has no effect on C1.

- (i)

- State 9: Switches S13, S14, S23, and S24 are on, while the others are off. The input voltage UAB is zero, and input has no effect on C1 or C2.

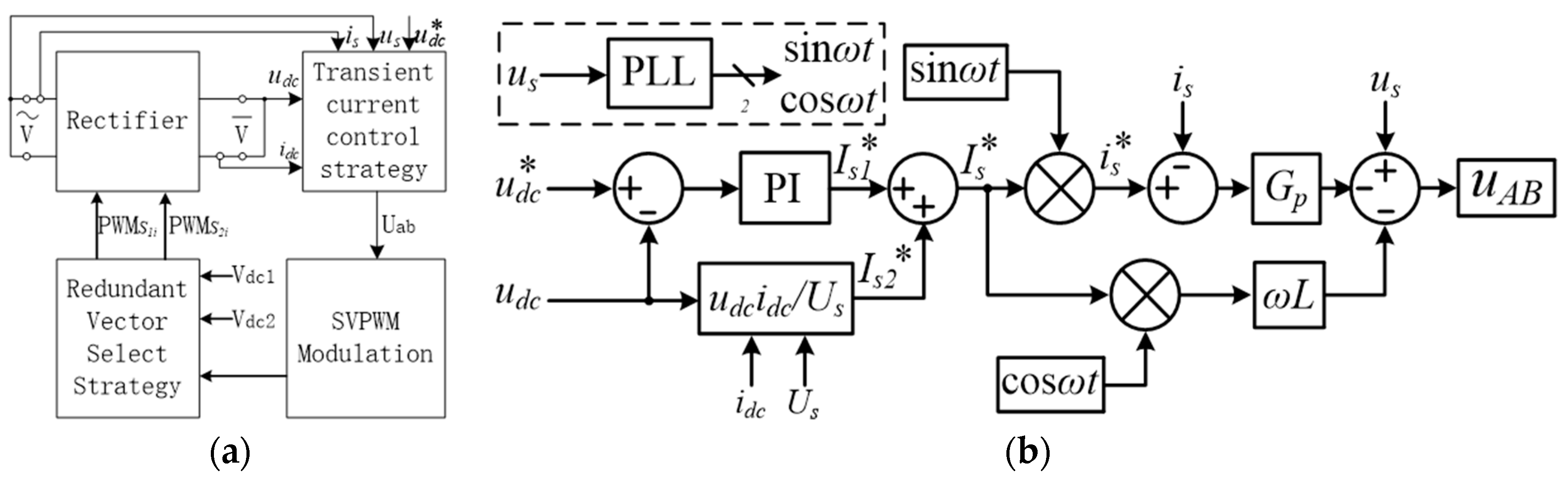

3. Control Algorithm and Modulation

3.1. Transient Current Control Strategy

3.2. Space Vector Pulse Width Modulation

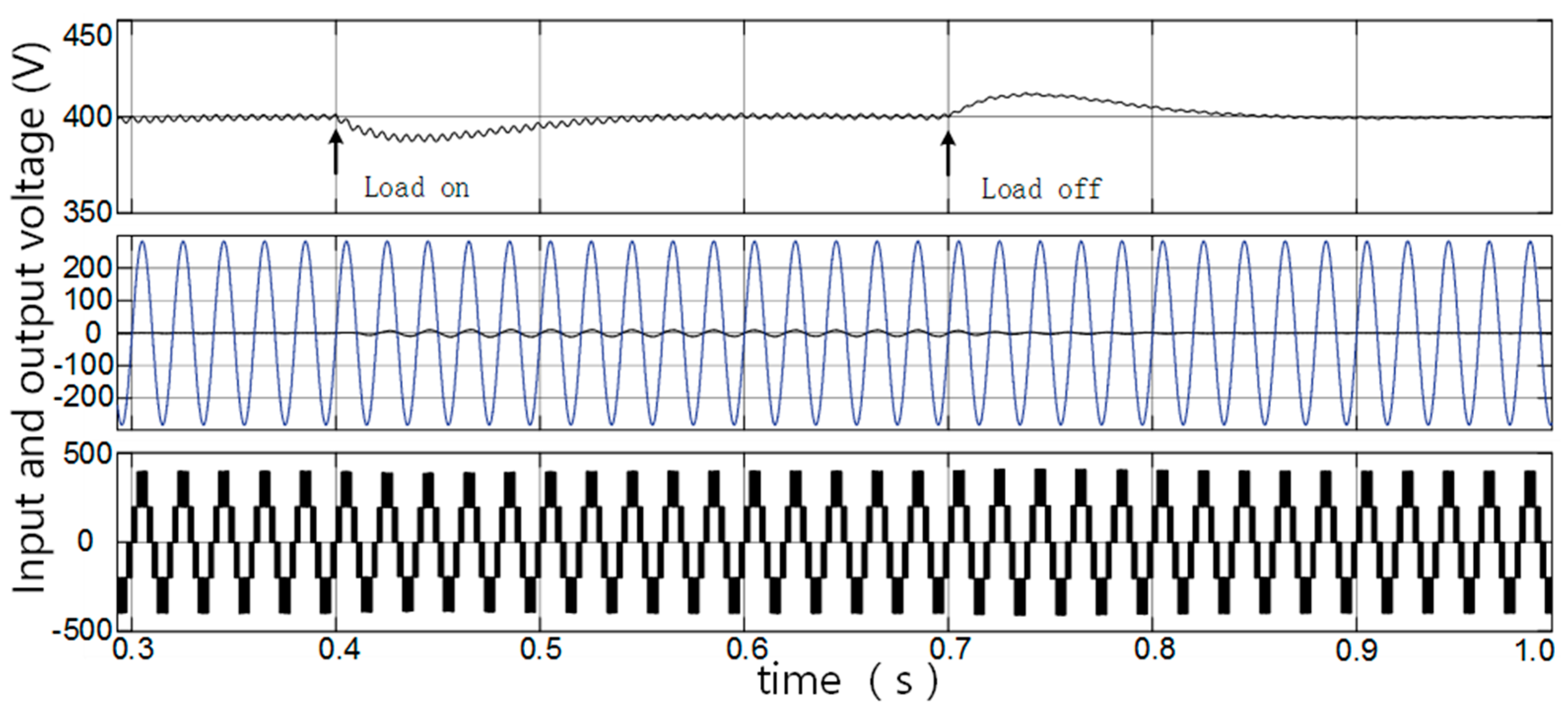

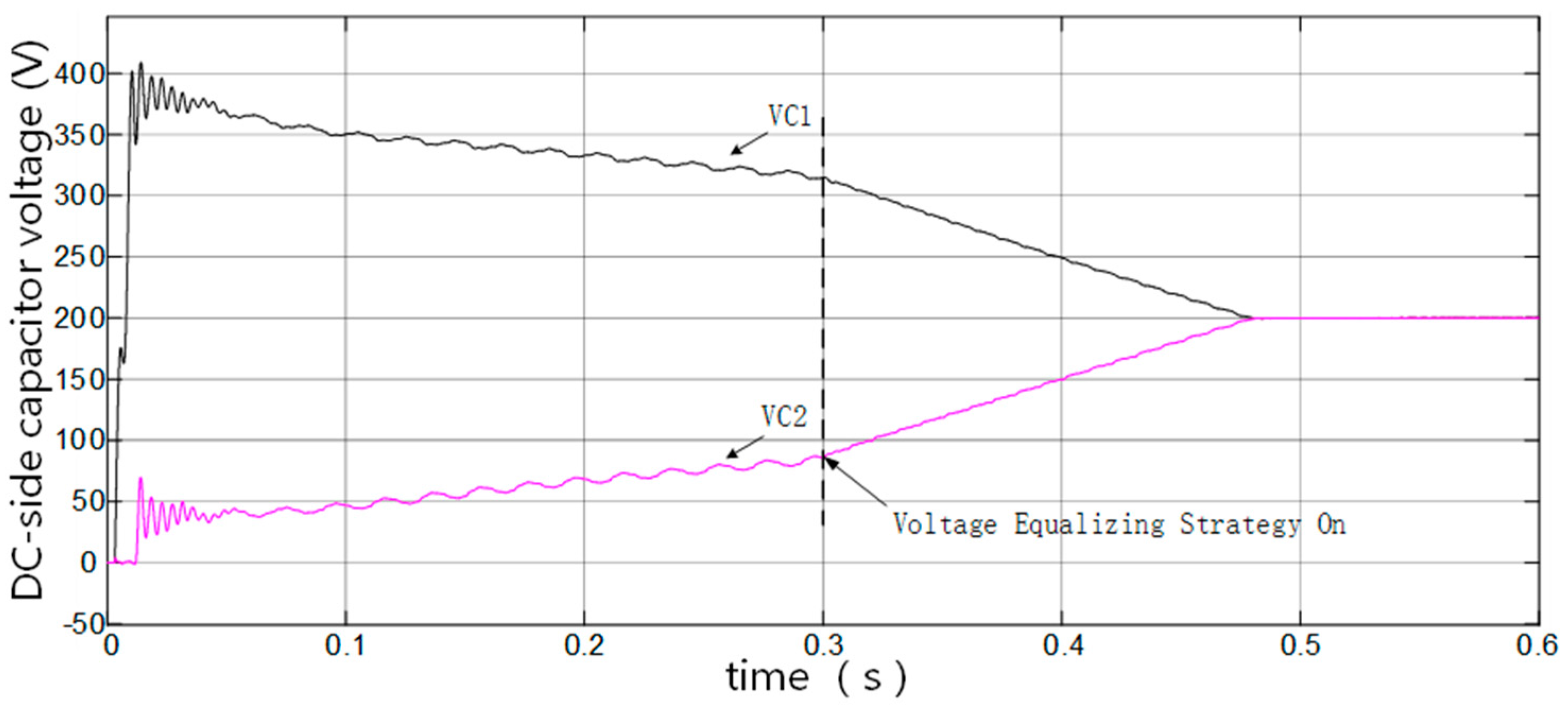

4. Simulation

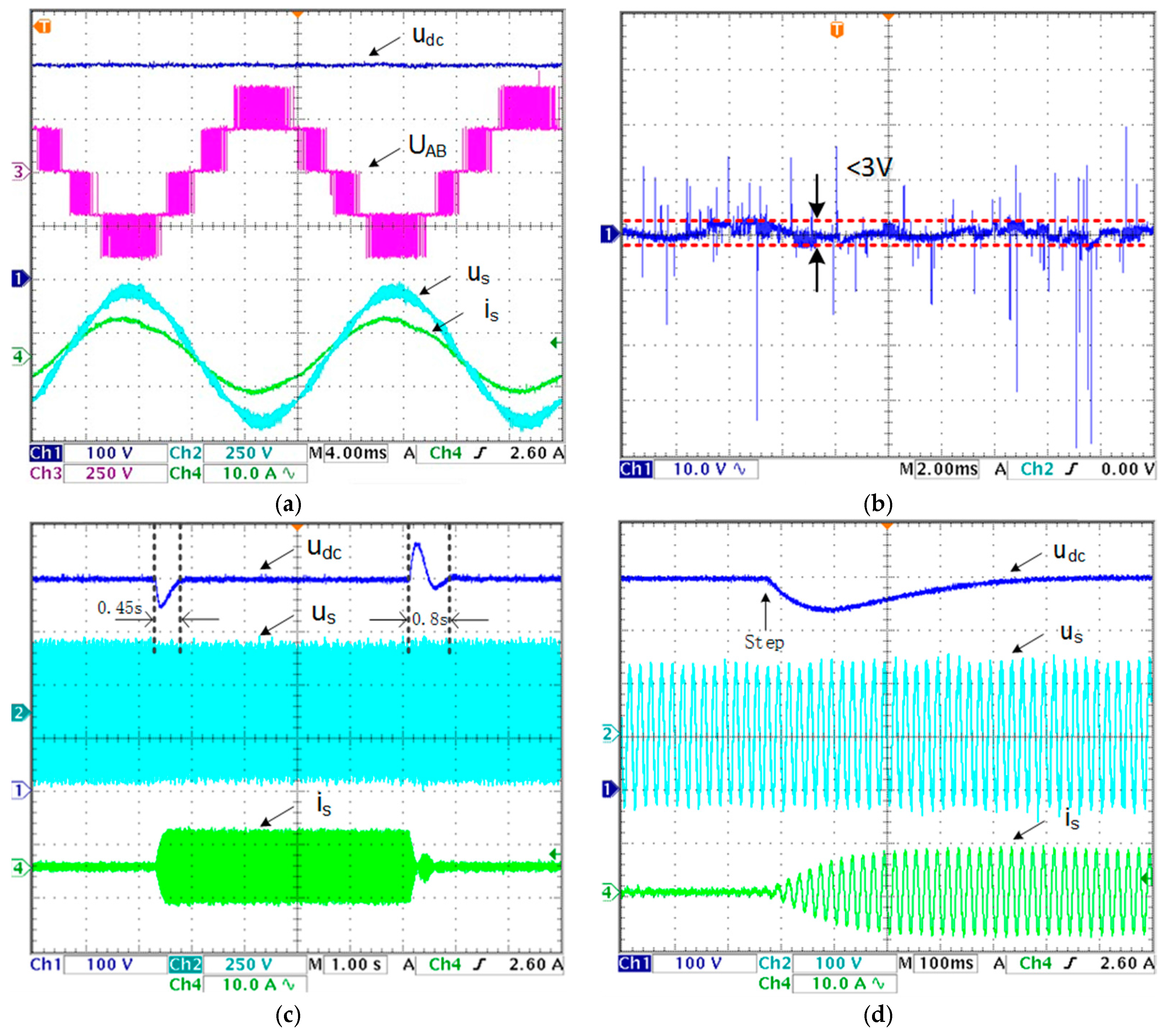

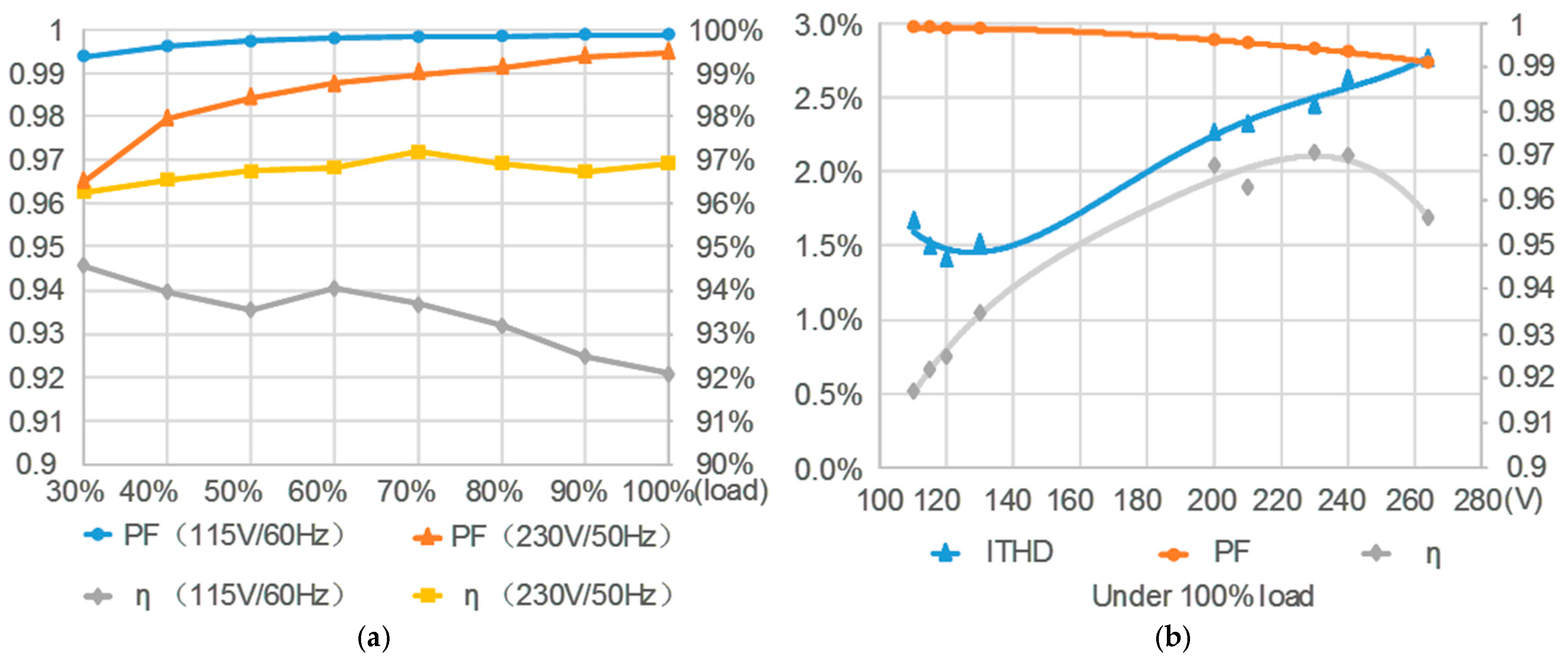

5. Experiment Results

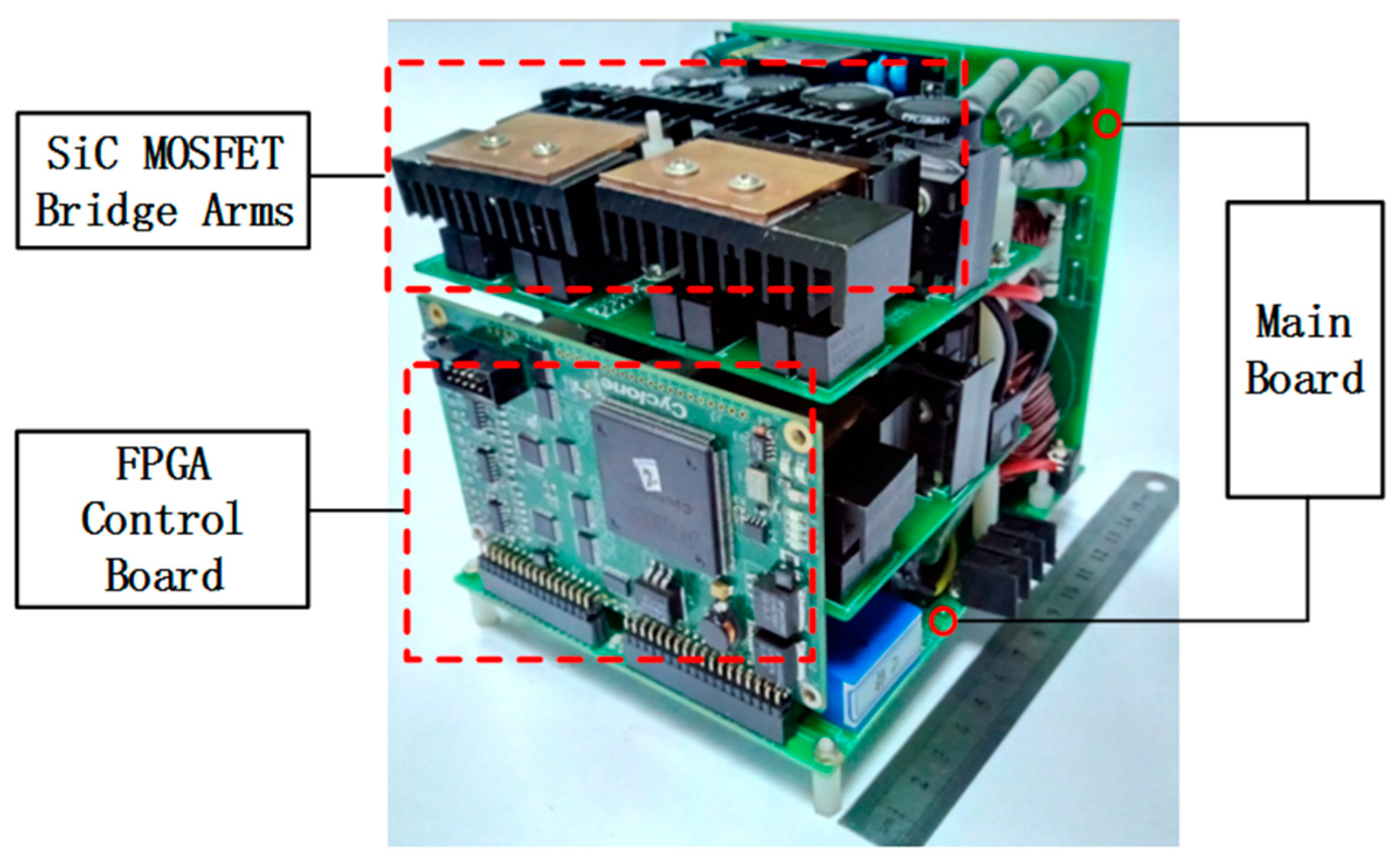

5.1. Prototype

5.2. Experiment Results

6. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Peng, H.; Hagiwara, M.; Akagi, H. Modeling and analysis of switching-ripple voltage on the DC Link between a diode rectifier and a modular multilevel cascade inverter (MMCI). IEEE Trans. Power Electron. 2013, 28, 75–84. [Google Scholar] [CrossRef]

- Gautam, S.P.; Kumar, L.; Gupta, S. Hybrid topology of symmetrical multilevel inverter using less number of devices. IET Power Electron. 2015, 8, 2125–2135. [Google Scholar] [CrossRef]

- Kouro, S.; Malinowski, M.; Gopakumar, K.; Pou, J.; Franquelo, L.G.; Wu, B.; Rodriguez, J.; Perez, M.A.; Leon, J.I. Recent advances and industrial applications of multilevel converters. IEEE Trans. Ind. Electron. 2010, 57, 2553–2580. [Google Scholar] [CrossRef]

- He, X.; Shu, Z.; Peng, X.; Zhou, Q.; Zhou, Y.; Zhou, Q.; Gao, S. Advanced cophase traction power supply system based on three-phase to single-phase converter. IEEE Trans. Power Electron. 2014, 29, 5323–5333. [Google Scholar] [CrossRef]

- Shu, Z.; Zhu, H.; He, X.; Ding, N.; Jing, Y. One-inductor-based auxiliary circuit for dc-link capacitor voltage equalization of diode-clamped multilevel converter. IET Power Electron. 2013, 6, 1339–1349. [Google Scholar] [CrossRef]

- Zhu, H.; Shu, Z.; Gao, F.; Qin, B.; Gao, S. Five-level diode-clamped active power filter using voltage space vector-based indirect current and predictive harmonic control. IET Power Electron. 2014, 7, 713–723. [Google Scholar] [CrossRef]

- He, X.Q.; Guo, A.P.; Peng, X.; Zhou, Y.Y.; Shi, Z.H.; Shu, Z.L. A traction three-phase to single-phase cascade converter substation in an advanced traction power supply system. Energies 2015, 8, 9915–9929. [Google Scholar] [CrossRef]

- Shu, Z.; Ding, N.; Chen, J.; Zhu, H.; He, X. Multilevel SVPWM with DC-Link capacitor voltage balancing control for diode-clamped multilevel converter based STATCOM. IEEE Trans. Ind. Electron. 2013, 60, 1884–1896. [Google Scholar] [CrossRef]

- Xu, P.; He, X.Q.; Han, P.C.; Guo, A.P.; Shu, Z.L.; Gao, S.B. Smooth Switching Technique for Voltage Balance Management Based on Three-Level Neutral Point Clamped Cascaded Rectifier. Energies 2016, 9, 803. [Google Scholar] [CrossRef]

- Anthon, A.; Zhang, Z.; Andersen, M.A.E.; Holmes, D.G.; McGrath, B.; Teixeira, C.A. The Benefits of SiC MOSFETS in a T-Type Inverter for Grid-Tie Applications. IEEE Trans. Power Electron. 2017, 32, 2808–2821. [Google Scholar] [CrossRef]

- Hazra, S.; Madhusoodhanan, S.; Moghaddam, G.K.; Hatua, K.; Bhattacharya, S. Design Considerations and Performance Evaluation of 1200-V 100-A SiC MOSFET-Based Two-Level Voltage Source Converter. IEEE Trans. Ind. Appl. 2016, 52, 4257–4268. [Google Scholar] [CrossRef]

- Chen, Z.; Yao, Y.; Boroyevich, D.; Ngo, K.D.T.; Mattavelli, P.; Rajashekara, K. A 1200-V, 60-A SiC MOSFET Multichip Phase-Leg Module for High-Temperature, High-Frequency Applications. IEEE Trans. Power Electron. 2014, 29, 2307–2320. [Google Scholar] [CrossRef]

- Mainali, K.; Tripathi, A.; Madhusoodhanan, S.; Kadavelugu, A.; Patel, D.; Hazra, S.; Hatua, K.; Bhattacharya, S. A Transformerless Intelligent Power Substation: A three-phase SST enabled by a 15-kV SiC IGBT. IEEE Power Electron. Mag. 2015, 2, 31–43. [Google Scholar] [CrossRef]

- Han, D.; Sarlioglu, B. Comprehensive Study of the Performance of SiC MOSFET-Based Automotive DC–DC Converter under the Influence of Parasitic Inductance. IEEE Trans. Ind. Appl. 2016, 52, 5100–5111. [Google Scholar] [CrossRef]

- Jahdi, S.; Alatise, O.; Gonzalez, J.A.O.; Bonyadi, R.; Li, R.; Mawby, P. Temperature and Switching Rate Dependence of Crosstalk in Si-IGBT and SiC Power Modules. IEEE Trans. Ind. Electron. 2016, 63, 849–863. [Google Scholar] [CrossRef]

| State | Vector Categories | |||||

|---|---|---|---|---|---|---|

| 1 | P | P | 0 | Z | ||

| 2 | P | O | SP | |||

| 3 | P | N | + | LP | ||

| 4 | O | P | SN | |||

| 5 | O | O | 0 | Z | ||

| 6 | O | N | SP | |||

| 7 | N | P | LN | |||

| 8 | N | O | SN | |||

| 9 | N | N | 0 | Z |

| Terminal Voltage | Relation | Current Direction | Vector Selected | Result |

|---|---|---|---|---|

| A→B | ||||

| B→A | ||||

| A→B | ||||

| B→A | ||||

| A→B | ||||

| B→A | ||||

| A→B | ||||

| B→A |

| Parameters | Values |

|---|---|

| Input AC Voltage | 115 V–264 V |

| Input Current | 15 A (Max) |

| Input AC Voltage Frequency | 47 Hz–63 Hz |

| Output DC Voltage | 400 V |

| Output Power | 1.3 kW (Max) |

| Power Density | 0.56 W/cm3 |

| The Inductance of Input Side | 0.4 mH |

| Filter Circuit | 3 mF/0.84 mH |

| Switching Frequency | 30 kHz |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhou, T.; Shu, Z.; Lin, H.; Luo, D.; Chen, Y.; Guo, X. A High-Power-Density Single-Phase Rectifier Based on Three-Level Neutral-Point Clamped Circuits. Energies 2017, 10, 697. https://doi.org/10.3390/en10050697

Zhou T, Shu Z, Lin H, Luo D, Chen Y, Guo X. A High-Power-Density Single-Phase Rectifier Based on Three-Level Neutral-Point Clamped Circuits. Energies. 2017; 10(5):697. https://doi.org/10.3390/en10050697

Chicago/Turabian StyleZhou, Tao, Zeliang Shu, Hongjian Lin, Deng Luo, Yajun Chen, and Xiaoxiao Guo. 2017. "A High-Power-Density Single-Phase Rectifier Based on Three-Level Neutral-Point Clamped Circuits" Energies 10, no. 5: 697. https://doi.org/10.3390/en10050697