Integrated Solution for Driving Series-Connected IGBTs and Its Natural Intrinsic Balancing

Abstract

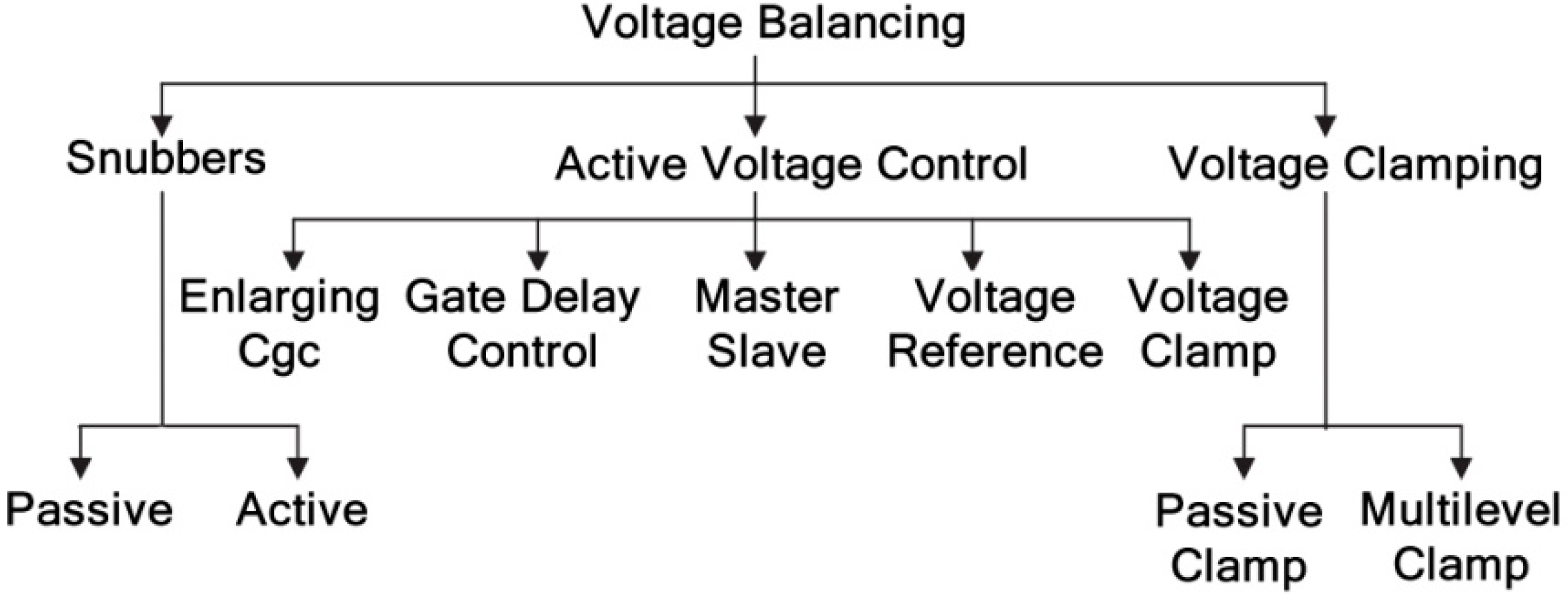

:1. Introduction

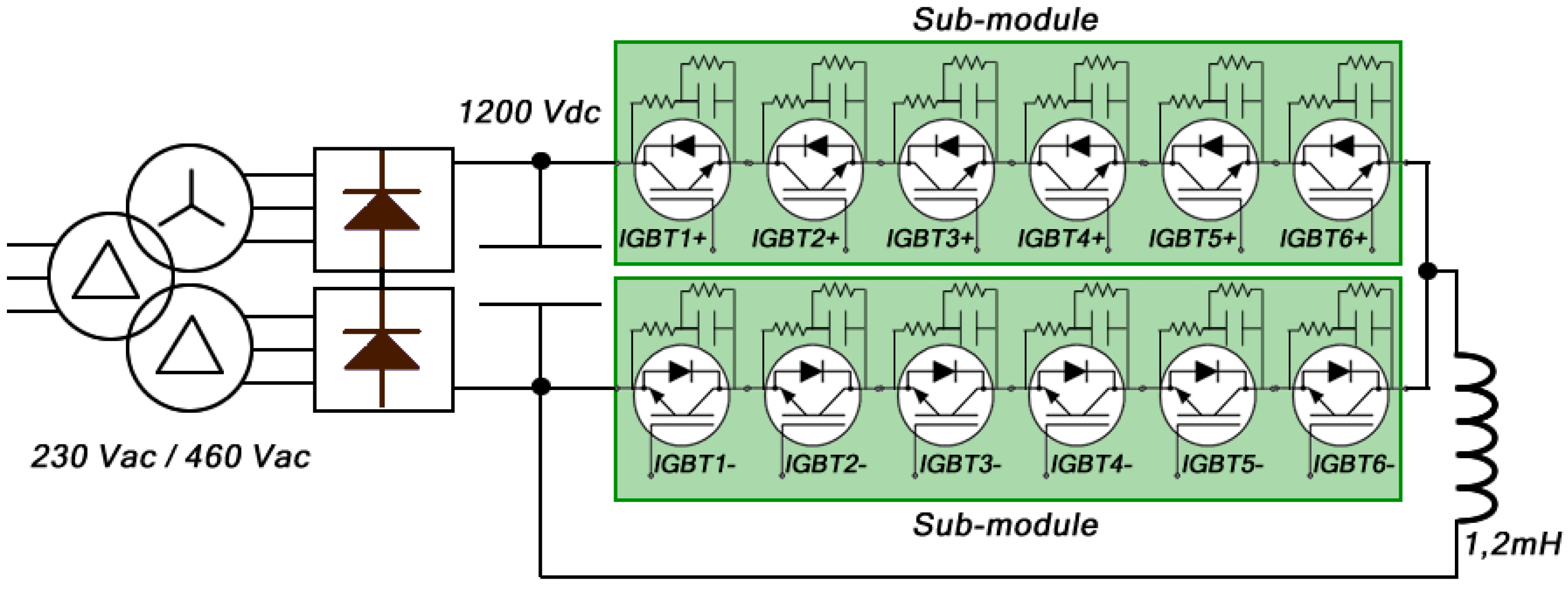

2. Main Requirements

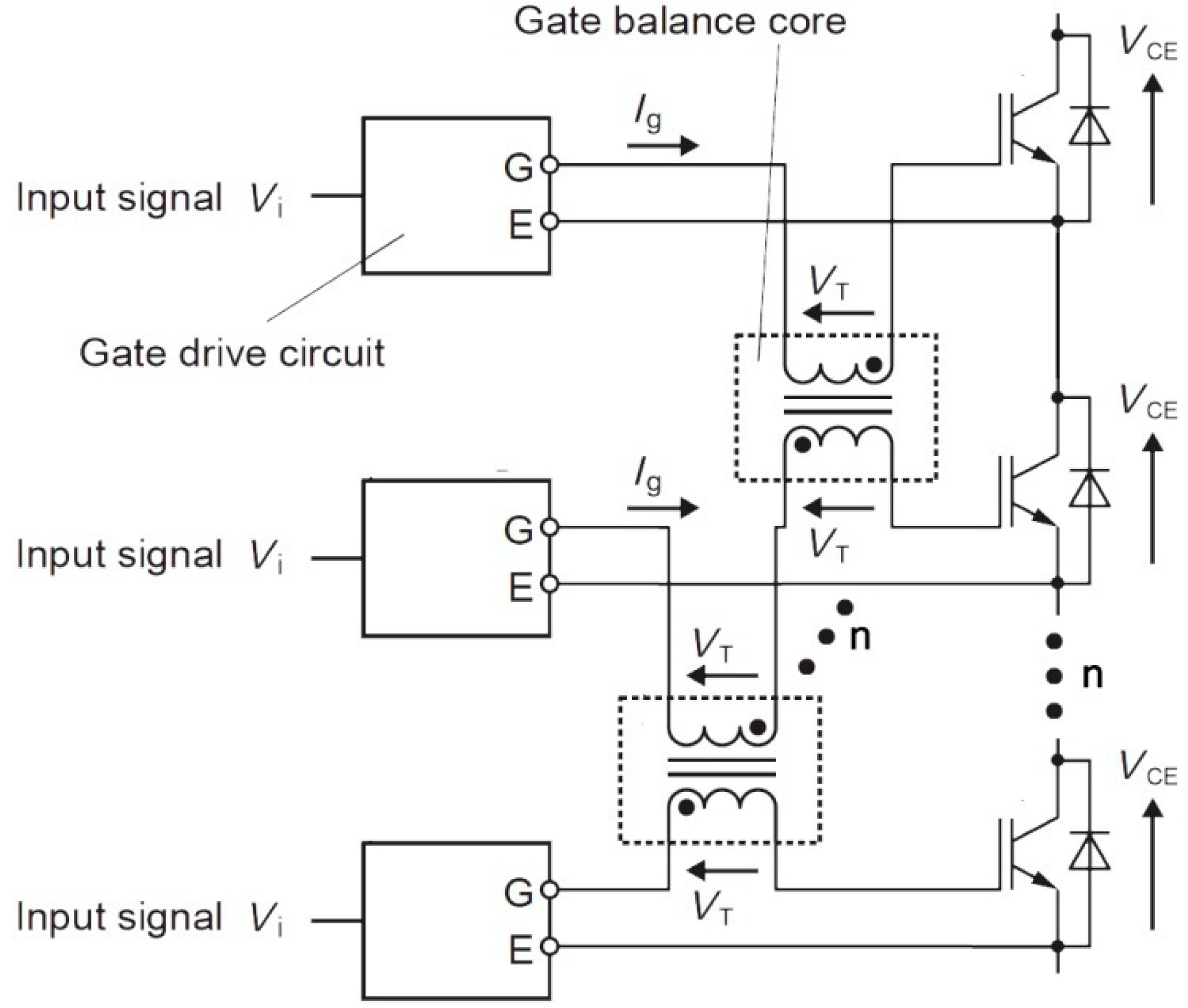

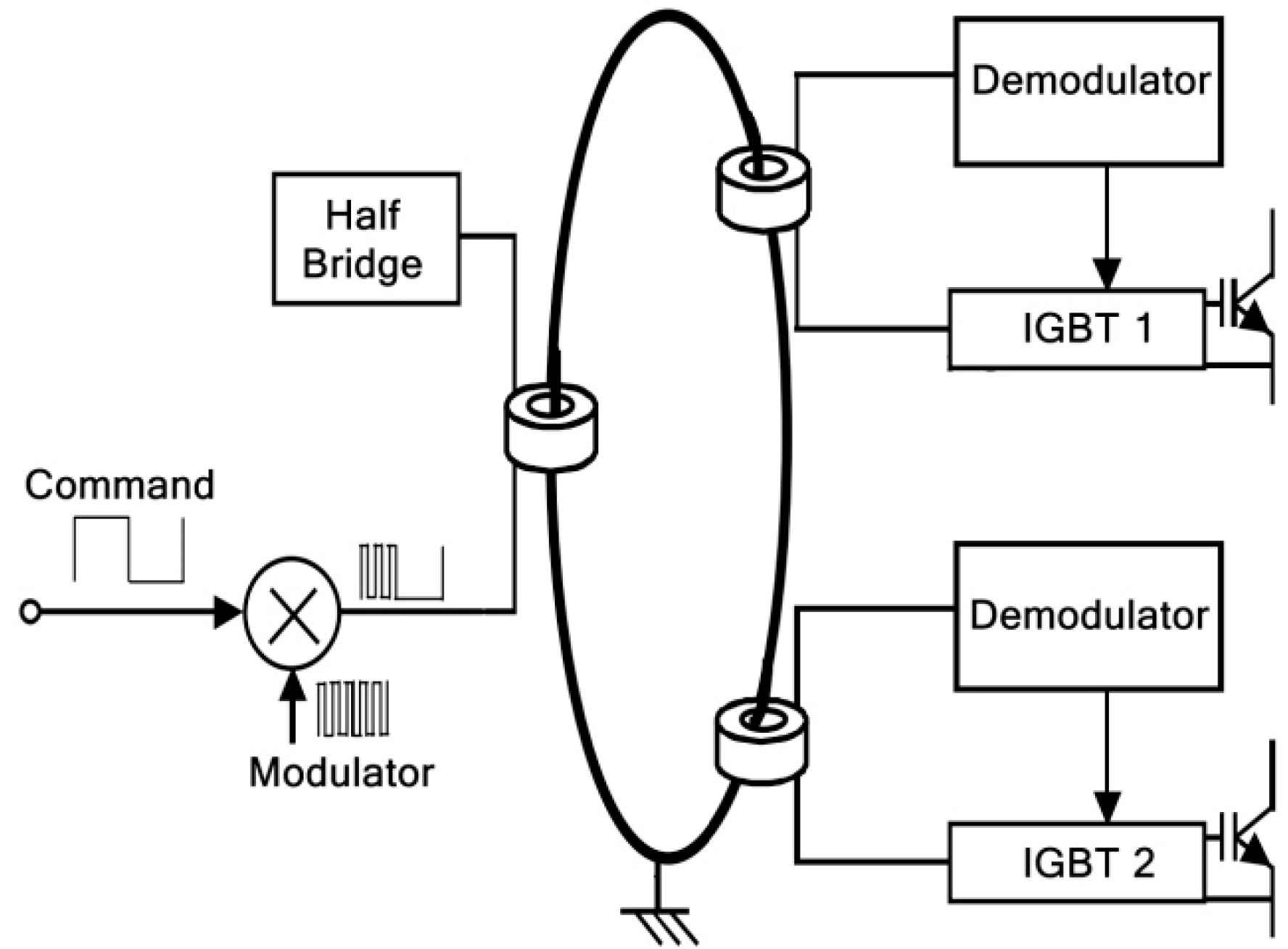

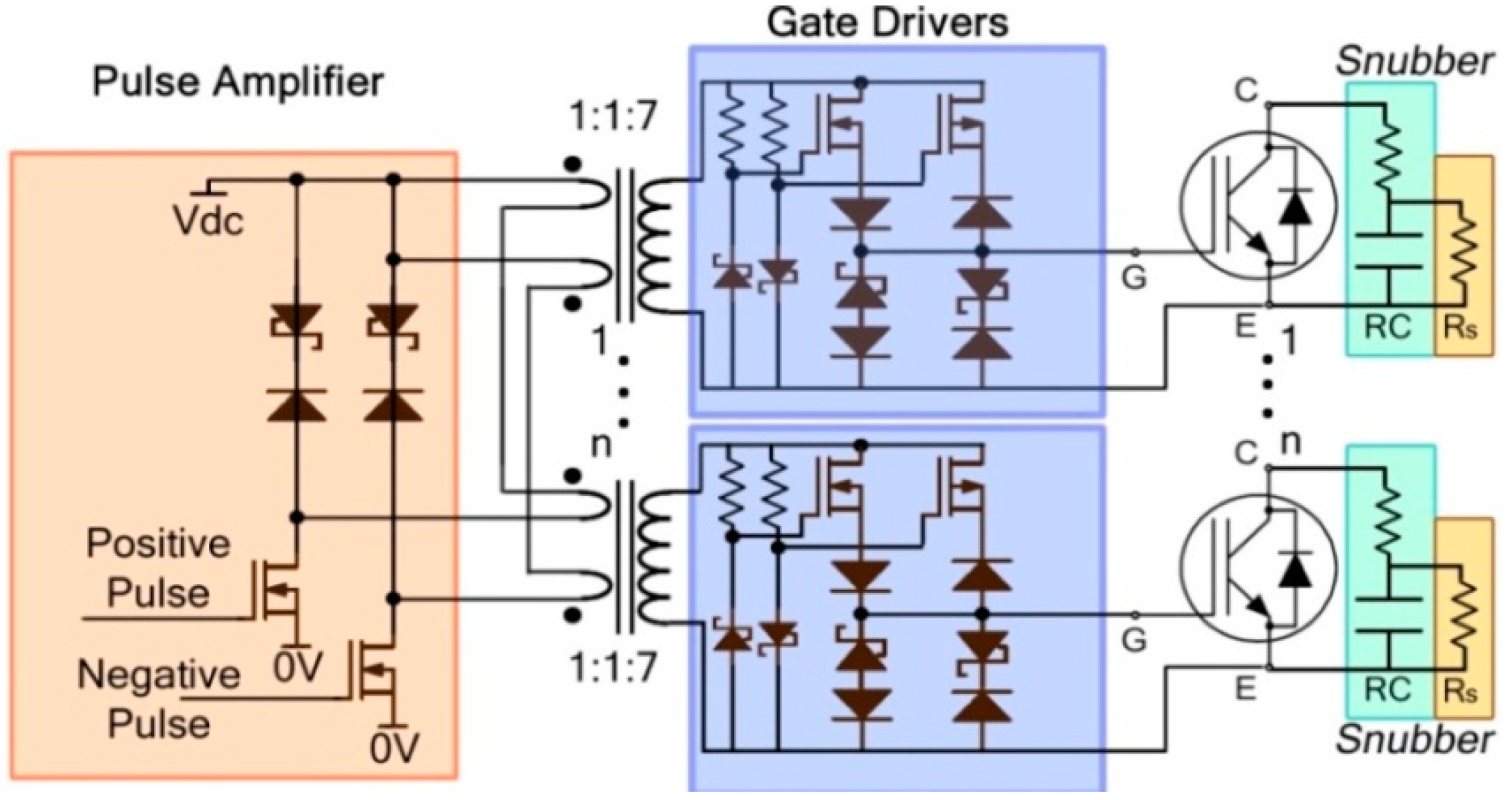

3. Gate Driver

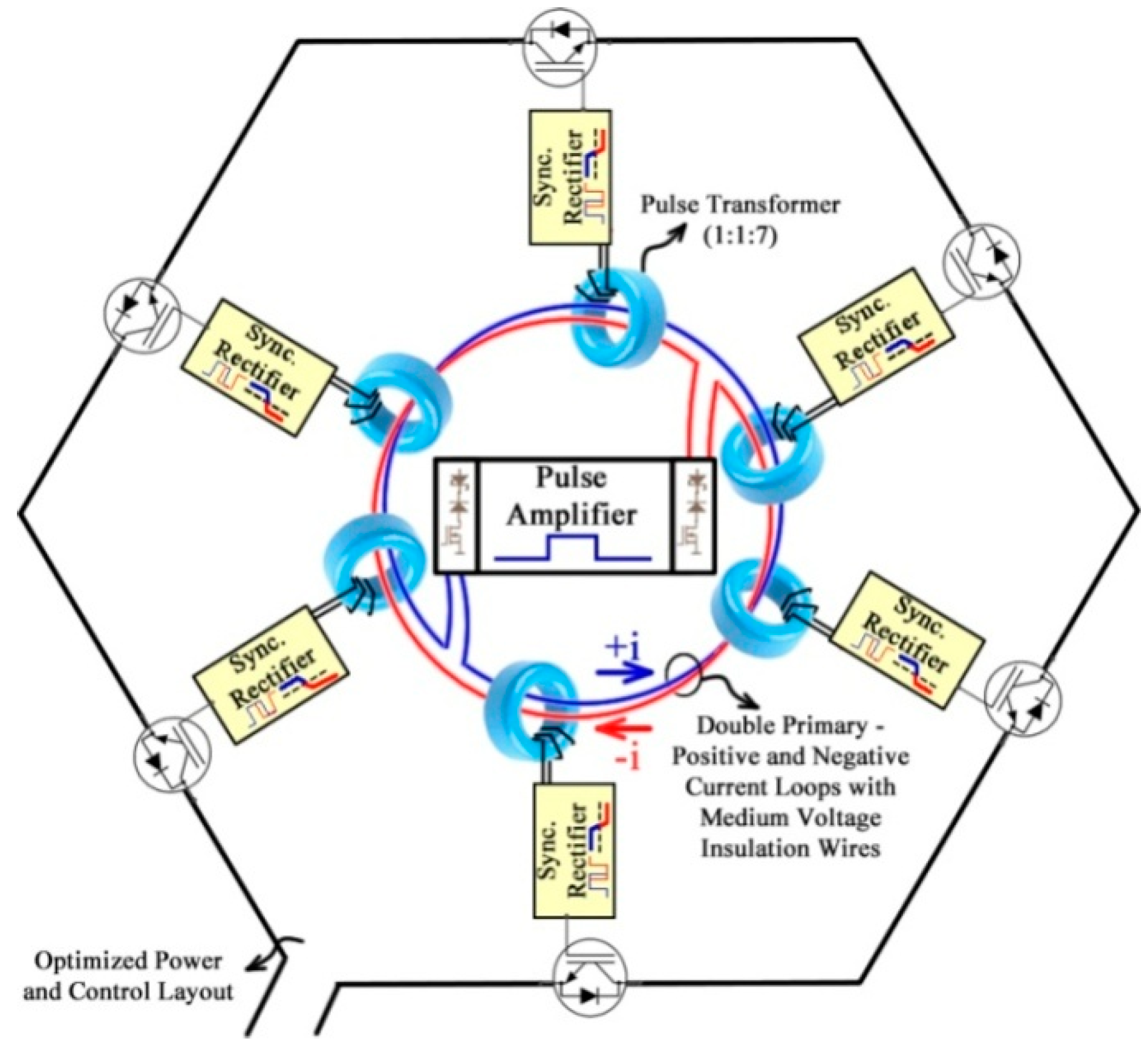

4. Hexagonal Sub-Module

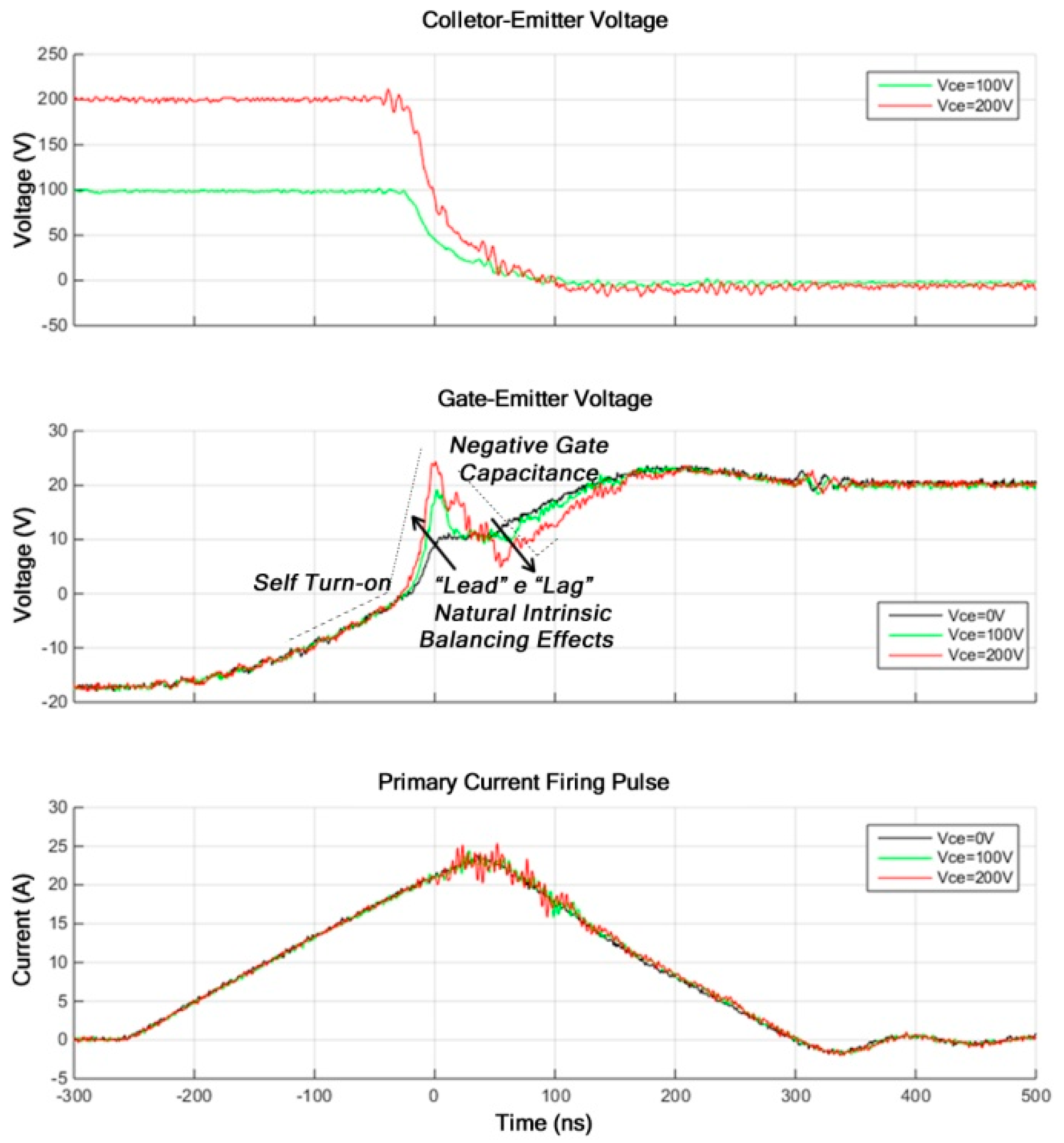

5. Natural Intrinsic Balancing

6. Experimental Results

6.1. Test Bench and Hexagonal Sub-Module

6.2. Gate Command Synchronization

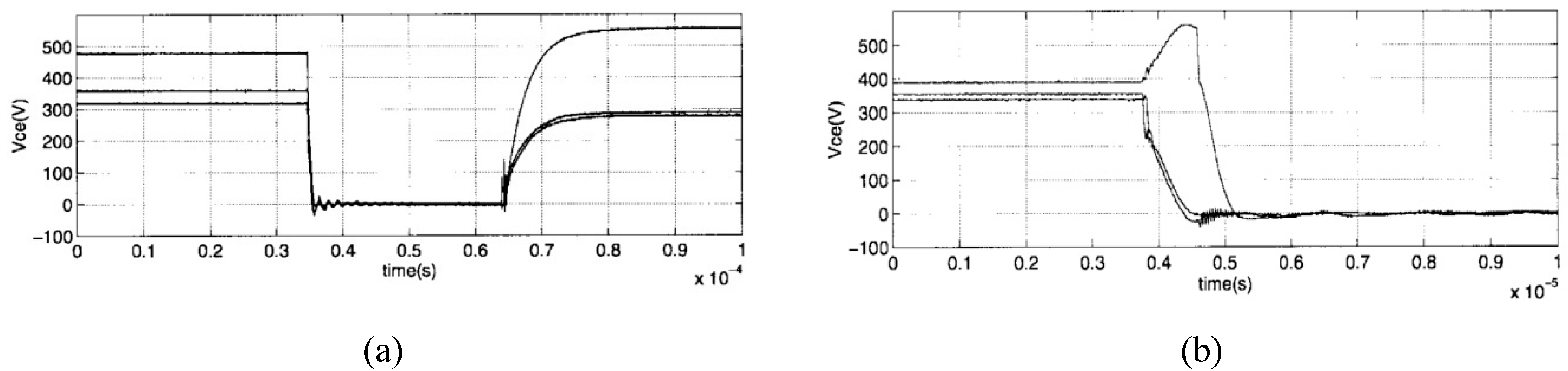

6.3. Natural Intrinsic Balancing without Snubber

6.4. Final Results with Static Analysis

7. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Palmer, P.R.; Githiari, A.N. The series connection of IGBTs with optimized voltage sharing in the switching transient. In Proceedings of the Power Electronics Specialists Conference, PESC’95, Atlanta, GA, USA, 18–22 June 1995; Volume 1, pp. 44–49. [Google Scholar]

- Hong, S.; Chitta, V.; Torrey, D.A. Series connection of IGBT’s with active voltage balancing. IEEE Trans. Ind. Appl. 1999, 35, 917–923. [Google Scholar] [CrossRef]

- Bruckmann, M.; Sommer, R.; Fasching, M.; Sigg, J. Series connection of high voltage IGBT modules. In Proceedings of the Industry Applications Conference, Third IAS Annual Meeting, St. Louis, MO, USA, 12–15 October 1998; Volume 2, pp. 1067–1072. [Google Scholar]

- Palmer, P.R.; Rajamani, H.S.; Dutton, N. Experimental comparison of methods of employing IGBTs connected in series. Proc. Electr. Power Appl. IEEE 2004, 151, 576–582. [Google Scholar] [CrossRef]

- Shammas, N.Y.A.; Withanage, R.; Chamund, D. Review of series and parallel connection of IGBTs. IEE Proc. Circuits Devices Syst. 2006, 153, 34–39. [Google Scholar] [CrossRef]

- Hong, S.; Lee, Y.G. Active gate control strategy of series connected IGBTs for high power PWM inverter. In Proceedings of the IEEE 1999 International Conference on Power Electronics and Drive Systems, Hong Kong, China, 27–29 July 1999; pp. 646–652. [Google Scholar]

- Abbate, C.; Busatto, G.; Lannuzzo, F. High-voltage, high-performance switch using series-connected IGBTs. IEEE Trans. Power Electron. 2010, 25, 2450–2459. [Google Scholar] [CrossRef]

- Lim, T.C.; Williams, B.W.; Finney, S.J.; Palmer, P.R. Series-connected IGBTs using active voltage control technique. IEEE Trans. Power Electron. 2013, 28, 4083–4103. [Google Scholar] [CrossRef]

- Mazuela, M.; Baraia, I.; Sanchez, A.R.; Echeverria, I.; Torre, I.; Atutxa, I. Simple Voltage Balancing Method to Protect Series-Connected Devices Experimentally Verified in a 5L-MPC Converter. IEEE Trans. Ind. Electron. 2018, 65, 3699–3707. [Google Scholar] [CrossRef]

- Zhang, F.; Yang, X.; Ren, Y.; Feng, L.; Chen, W.; Pei, Y. A hybrid active gate drive for switching loss reduction and voltage balancing of series-connected IGBTs. IEEE Trans. Power Electron. 2017, 32, 7469–7481. [Google Scholar] [CrossRef]

- Baraia, I.; Barrena, J.A.; Abad, G.; Segade, J.M.C.; Iraola, U. An experimentally verified active gate control method for the series connection of IGBT/diodes. IEEE Trans. Power Electron. 2012, 27, 1025–1038. [Google Scholar] [CrossRef]

- Yang, X.; Zhang, J.; He, W.; Long, Z.; Palmer, P.R. Physical investigation into effective voltage balancing by temporary clamp technique for the series connection of IGBTs. IEEE Trans. Power Electron. 2018, 33, 248–258. [Google Scholar] [CrossRef]

- Zhang, J.; Palmer, P.; Zhang, X.; He, W. Analysis of an effective voltage sharing method for IGBTs connected in series. In Proceedings of the IECON 2014—40th Annual Conference of the Industrial Electronics Society, Dallas, TX, USA, 29 October–1 November 2014; pp. 1261–1269. [Google Scholar]

- Piazzesi, A.; Meysenc, L. Series connection of 3.3 kV IGBTs with active voltage balancing. In Proceedings of the IEEE 35th Annual Power Electronics Specialists Conference, Aachen, Germany, 20–25 June 2004; Volume 2, pp. 893–898. [Google Scholar]

- Lim, T.C.; Williams, B.W.; Finney, S.J. Active snubber energy recovery circuit for series-connected IGBTs. IEEE Trans. Power Electron. 2011, 26, 1879–1889. [Google Scholar] [CrossRef]

- Yang, L.; Fu, P.; Yao, X.; Wang, J. A module based self-balanced series connection for IGBT. In Proceedings of the Energy Conversion Congress and Exposition, Pittsburgh, PA, USA, 14–18 September 2014; pp. 1953–1958. [Google Scholar]

- Wang, Y.; Khaizaran, M.A.; Palmer, P.R. Controlled switching of high voltage IGBTs in series. In Proceedings of the IEEE Conference on Electron Devices and Solid-State Circuits, Hongkong, China, 16–18 December 2003; pp. 297–300. [Google Scholar]

- Gerster, C. Fast high-power/high-voltage switch using series-connected IGBTs with active gate-controlled voltage-balancing. In Proceedings of the Applied Power IEEE Electronics Conference and Exposition, Orlando, FL, USA, 13–17 February1994; pp. 469–472. [Google Scholar]

- Ji, S.; Lu, T.; Zhao, Z.; Yu, H.; Yuan, L. Series-connected HV-IGBTs using active voltage balancing control with status feedback circuit. IEEE Trans. Power Electron. 2015, 30, 4165–4174. [Google Scholar] [CrossRef]

- Abe, Y.; Maruyama, K. Multi-series connection of high-voltage IGBTs. Fugi Electr. J. 2002, 75, 1–4. [Google Scholar]

- Nguyen, T.; Jeannin, P.O.; Vagnon, E.; Frey, D.; Crebier, J.C. Series connection of IGBT. In Proceedings of the Applied Power Electronics Conference and Exposition (APEC), Palm Springs, CA, USA, 21–25 February 2010; pp. 2238–2244. [Google Scholar]

- Brehaut, S.; Costa, F. Gate driving of high power IGBT through a Double Galvanic Insulation Transformer. In Proceedings of the IEEE Industrial Electronics, IECON 2006–32nd Annual Conference, Paris, France, 7–10 November 2006; pp. 2505–2510. [Google Scholar]

- Palmer, P.R.; Githiari, A.N.; Leedham, R.J. A comparison of IGBT technologies for use in the series connection. In Proceedings of the Power Electronics and Variable Speed Drives Conference, Nottingham, UK, 23–25 September 1996; pp. 236–241. [Google Scholar]

- Consoli, A.; Musumeci, S.; Oriti, G.; Testa, A. Active voltage balancement of series connected IGBTs. In Proceedings of the Industry Applications Conference Thirtieth IAS Annual Meeting, Orlando, FL, USA, 8–12 October 1994; Volume 3, pp. 2752–2758. [Google Scholar]

- Hess, H.L.; Baker, R.J. Transformer less capacitive coupling of gate signals for series operation of power MOS devices. IEEE Trans. Power Electron. 2000, 15, 923–930. [Google Scholar] [CrossRef]

- Maurice, B.; Wuidart, L. Drive Circuits for Power MOSFETs and IGBTs. ST Microelectronics Application Notes. Available online: https://www.st.com (accessed on 10 February 2019).

- Chiola, D.; Husklen, H. 1200 V High Speed 3: IGBT A New IGBT Family Optimized for High-Switching Speed. AN-IGBT-09-2013-V1.1-EN-019. Available online: https://www.infineon.com/ (accessed on 15 March 2019).

- Münster, P.; Schräder, R.; Tran, Q.T.; Gierschner, S.; Eckel, H.G. Influence of gate structures and electrical boundary conditions on self-turn-on of HV IGBTs. In Proceedings of the 19th European Conference on Power Electronics and Applications, Warsaw, Poland, 11–14 September 2017. [Google Scholar]

- Feng, H.; Yang, W.; Onozawa, Y.; Yoshimura, T.; Tamenori, A.; Sin, J.K. Transient turn-on characteristics of the fin p-body IGBT. IEEE Trans. Electron Devices 2015, 62, 2555–2561. [Google Scholar] [CrossRef]

- Omura, I.; Ohashi, H.; Fichtner, W. IGBT negative gate capacitance and related instability effects. IEEE Electron Device Lett. 1997, 18, 622–624. [Google Scholar] [CrossRef]

- Böhmer, J.; Schumann, J.; Eckel, H.G. Negative differential miller capacitance during switching transients of IGBTs. In Proceedings of the 14th European Conference on Power Electronics and Applications, Lappeenranta, Finland, 26–28 August 2014. [Google Scholar]

- Tominaga, S.; Urushibata, H.; Fujita, H.; Akagi, H.; Horiguchi, T.; Kinouchi, S.I.; Oi, T. Modeling of IGBTs with focus on voltage dependency of terminal capacitances. In Proceedings of the 14th European Conference on Power Electronics and Applications, Lappeenranta, Finland, 26–28 August 2014; pp. 1–9. [Google Scholar]

- Baliga, B.J. Fundamentals of Power Semiconductor Devices; Springer Science & Business Media: Berlin, Germany, 2010. [Google Scholar]

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Fortes, G.O.; Mendes, M.A.S.; Cortizo, P.C. Integrated Solution for Driving Series-Connected IGBTs and Its Natural Intrinsic Balancing. Energies 2019, 12, 2406. https://doi.org/10.3390/en12122406

Fortes GO, Mendes MAS, Cortizo PC. Integrated Solution for Driving Series-Connected IGBTs and Its Natural Intrinsic Balancing. Energies. 2019; 12(12):2406. https://doi.org/10.3390/en12122406

Chicago/Turabian StyleFortes, Gustavo O., Marcos A. S. Mendes, and Porfírio C. Cortizo. 2019. "Integrated Solution for Driving Series-Connected IGBTs and Its Natural Intrinsic Balancing" Energies 12, no. 12: 2406. https://doi.org/10.3390/en12122406