Efficiency Optimization for All-Silicon Carbide (SiC) PWM Rectifier Considering the Impact of Gate-Source Voltage Interference

Abstract

:1. Introduction

2. The Impact of Gate-Source Voltage Interference on Loss of All-SiC PWM Rectifier

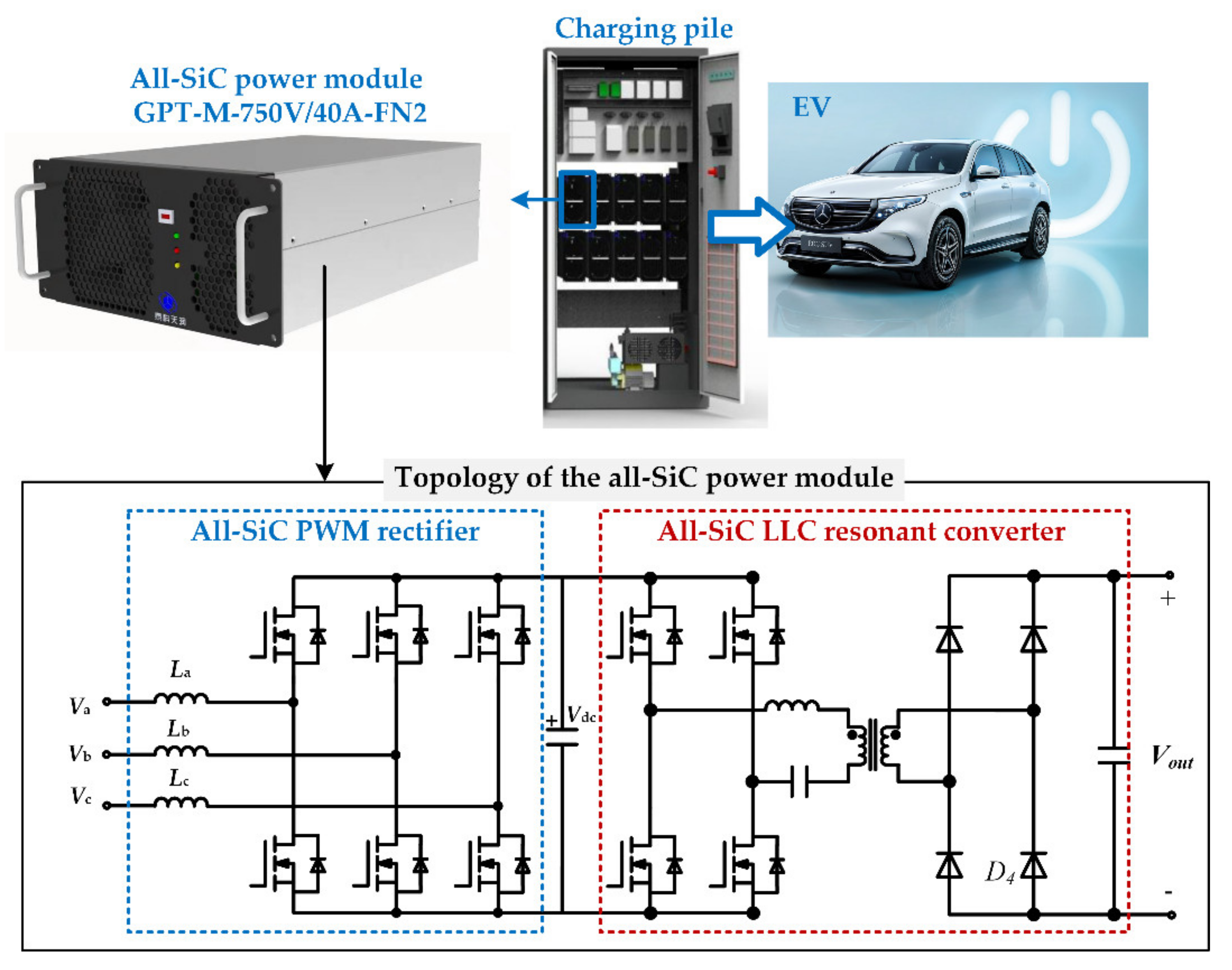

2.1. All-SiC PWM Rectifier for EV charging

2.2. The Impact of Gate-Source Voltage Interference on Loss and Its Suppression Method

3. The Mechanism of 4-pin SiC MOSFETs to Improve System Efficiency

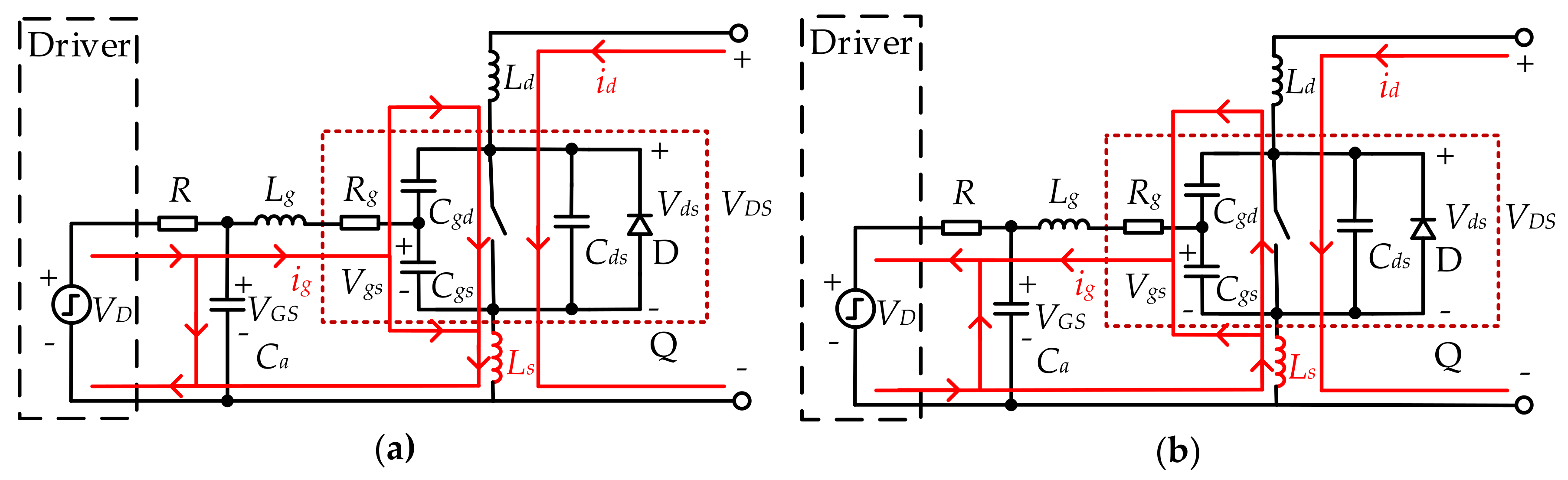

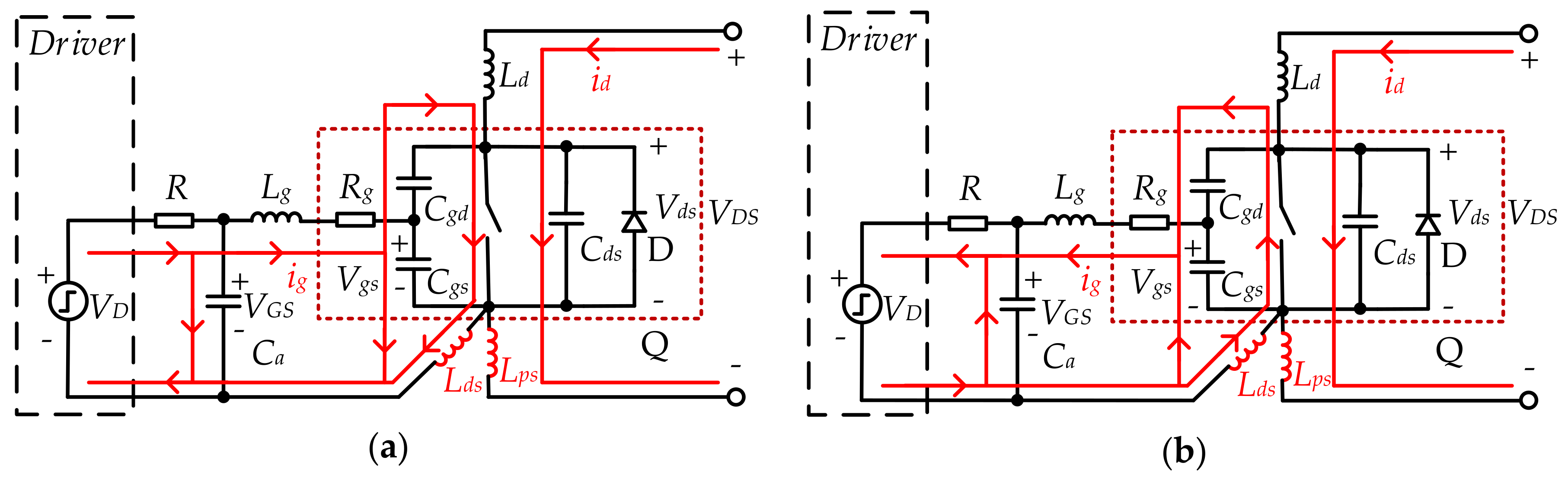

3.1. Analysis of Switching Process of 3-pin SiC MOSFETs

3.2. Analysis of Switching Process of 4-pin Kelvin Package SiC MOSFETs

3.3. Efficiency Improvement Analysis

4. Loss Model Considering the Impact of Gate-Source Voltage Interference

4.1. General Loss Model of 3-pin SiC MOSFETs

4.2. General Loss Model of Magnetic Components

4.3. Loss Model of 4-pin Kelvin Package SiC MOSFETs

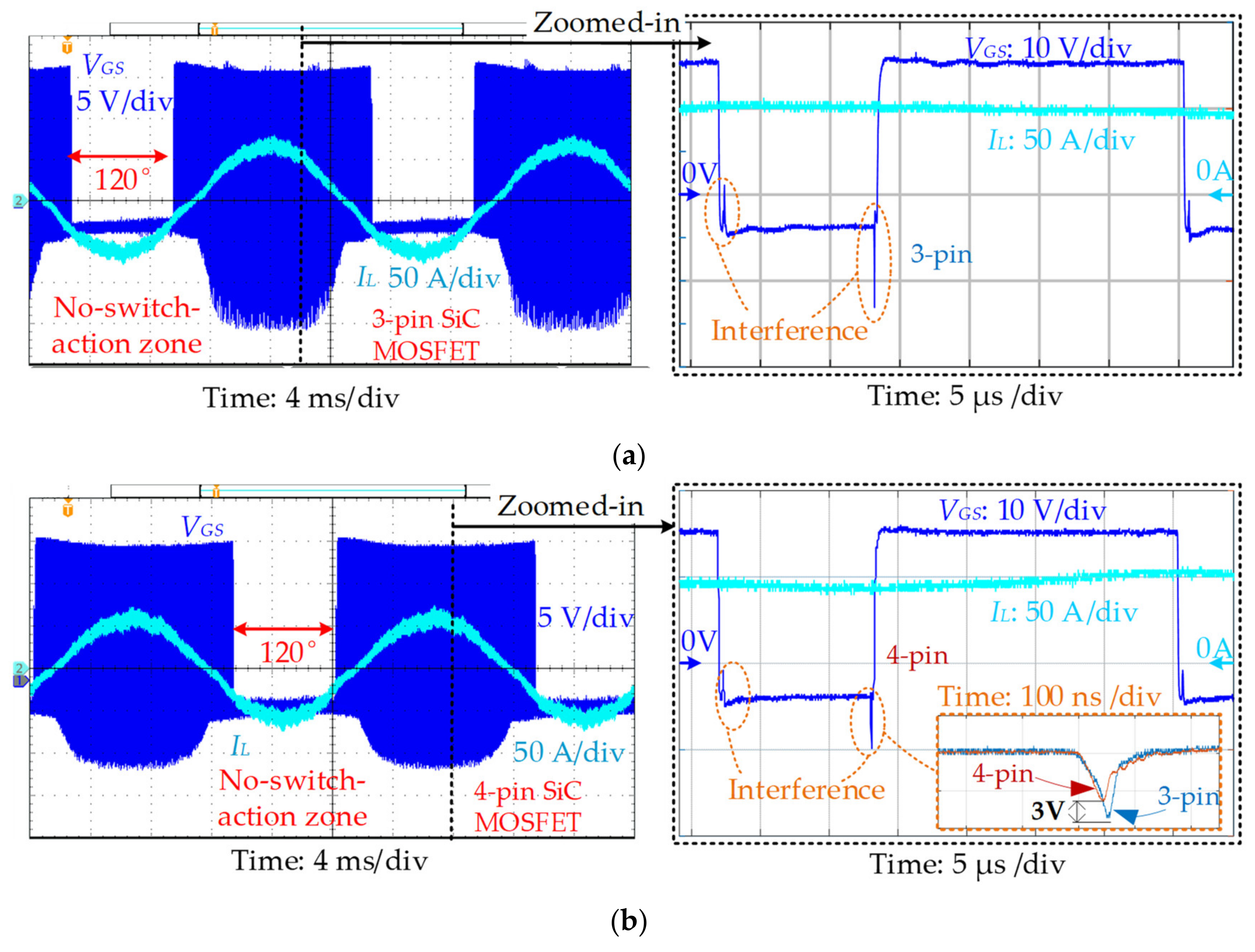

5. Experiments

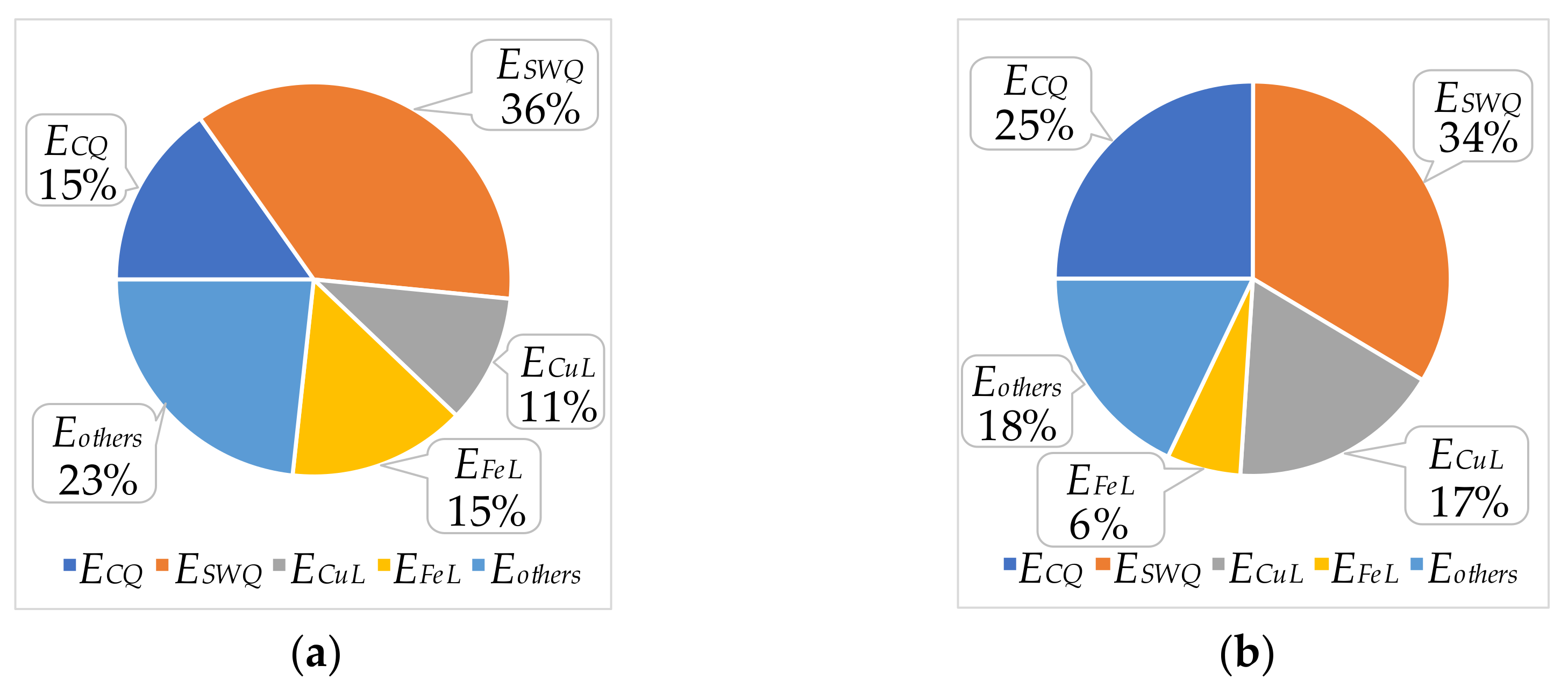

- The switching loss was more than 1/3 of total loss at half-load and full-load conditions for all-SiC PWM rectifiers, and it had become the crucial factor for the efficiency.

- The PWM rectifier using the 4-pin SiC MOSFETs had a reduced total loss under 15 kW and 30 kW conditions than 3-pin SiC MOSFETs. The loss was reduced by about 0.2% at 15 kW and about 0.1% at 30 kW.

- The switching loss proportion of 4-pin SiC MOSFETs PWM rectifier was less than 3-pin SiC MOSFETs (6% less at 15 kW and 2% less at 30 kW).

6. Conclusions

- The rapid change of the main power current (di/dt) induced an electromotive force on the source parasitic inductance of the 3-pin SiC MOSFET, which was opposite to the driving voltage, suppressing the gate-source voltage change and increasing the switching loss.

- The mechanism of improving system efficiency by using the 4-pin Kelvin packaged SiC MOSFETs was theoretically investigated. The drive circuit of SiC MOSFETs could be approximately equivalent to a second-order system, and the switching time could be derived. Moreover, the switching time of 4-pin SiC MOSFETs was theoretically less than that of general 3-pin SiC MOSFETs.

- The loss model of all-SiC PWM rectifier was established by considering the impact of gate-source voltage interference. The switching loss of 4-pin SiC MOSFETs was smaller than 3-pin SiC MOSFETs, so the total loss of the PWM rectifier was decreased, and the system efficiency was improved.

- Based on the industrial product case study, two 30 kW all-SiC PWM rectifier versions were investigated, using 3-pin SiC MOSFETs and 4-pin SiC MOSFETs, respectively. The switching loss was more than 1/3 of the total loss for both of the rectifiers. However, the switching loss proportion of 4-pin SiC MOSFETs PWM rectifier was less than 3-pin SiC MOSFETs (6% less at 15 kW and 2% less at 30 kW).

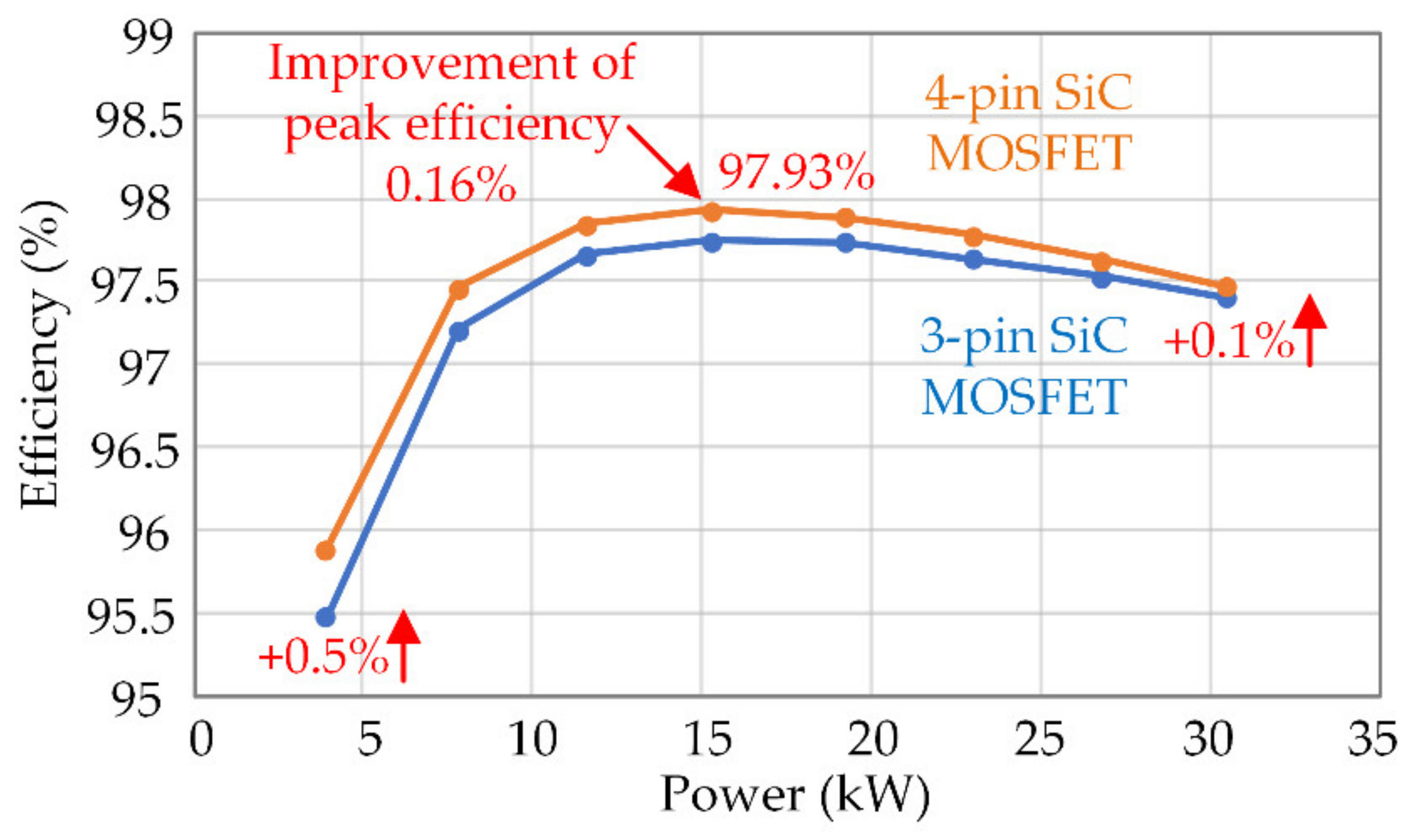

- 4-pin Kelvin package SiC MOSFETs improved the efficiency of the PWM rectifier. Experiment results showed that the efficiency was increased by about 0.5% (20 W) maximally at 4 kW, and about 0.1% (30 W) at 30 kW full-load. The peak efficiency of the PWM rectifier, using 4-pin SiC MOSFETs, was as high as 97.93%, which was 0.16% higher than the peak efficiency of the 3-pin SiC MOSFETs-based PWM rectifier.

Author Contributions

Funding

Conflicts of Interest

References

- Li, F.; Zhang, X.; Zhu, H.; Li, H.; Yu, C. An LCL-LC Filter for Grid-Connected Converter: Topology, Parameter, and Analysis. IEEE Trans. Power Electron. 2014, 30, 5067–5077. [Google Scholar] [CrossRef]

- Shao, T.-C.; Jia, P.; Zheng, P.-Q.; Zheng, T.Q.; Wang, J.; Li, H.; Liang, M.; Zhang, X. A Robust Power Regulation Controller to Enhance Dynamic Performance of Voltage Source Converters. IEEE Trans. Power Electron. 2019, 34, 12407–12422. [Google Scholar] [CrossRef]

- Wang, H.; Mingli, W.; Sun, J.; Wu, M. Analysis of Low-Frequency Oscillation in Electric Railways Based on Small-Signal Modeling of Vehicle-Grid System in dq Frame. IEEE Trans. Power Electron. 2015, 30, 5318–5330. [Google Scholar] [CrossRef]

- Song, K.; Mingli, W.; Yang, S.; Liu, Q.; Agelidis, V.G.; Konstantinou, G.; Wu, M. High-Order Harmonic Resonances in Traction Power Supplies: A Review Based on Railway Operational Data, Measurements, and Experience. IEEE Trans. Power Electron. 2020, 35, 2501–2518. [Google Scholar] [CrossRef]

- Li, Z.; Shao, T.; Zheng, T.Q.; Li, H.; Huang, B. Interference source analysis and EMC design for All-SiC power module in EV charger. Microelectron. Reliab. 2019, 113458. [Google Scholar] [CrossRef]

- Papamanolis, P.; Krismer, F.; Kolar, J.W. 22 kW EV Battery Charger Allowing Full Power Delivery in 3-Phase as well as 1-Phase Operation. In Proceedings of the 10th International Conference on Power Electronics and ECCE Asia (ICPE 2019—ECCE Asia), Busan, South Korea, 27–30 May 2019; pp. 1–8. [Google Scholar]

- Wang, F.; Zhang, Z.; Ericsen, T.; Raju, R.; Burgos, R.; Boroyevich, D. Advances in Power Conversion and Drives for Shipboard Systems. Proc. IEEE 2015, 103, 2285–2311. [Google Scholar] [CrossRef]

- Hamada, K.; Nagao, M.; Ajioka, M.; Kawai, F. SiC—Emerging Power Device Technology for Next-Generation Electrically Powered Environmentally Friendly Vehicles. IEEE Trans. Electron Devices 2014, 62, 278–285. [Google Scholar] [CrossRef]

- Karacolak, T.; Thirumalai, R.V.K.G.; Merrett, J.N.; Koshka, Y.; Topsakal, E. Silicon Carbide (SiC) Antennas for High-Temperature and High-Power Applications. IEEE Antennas Wirel. Propag. Lett. 2013, 12, 409–412. [Google Scholar] [CrossRef]

- Larry, S.; Lucas, L. Silicon, GaN and SiC: There’s Room for All—An application space overview of device considerations. In Proceedings of the 30th International Symposium on Power Semiconductor Devices and ICs, Chicago, IL, USA, 13–17 May 2018; pp. 8–11. [Google Scholar]

- Chow, T.P. Wide Bandgap Semiconductor Power Devices for Energy Efficient Systems. In Proceedings of the IEEE 3rd Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Blacksburg, VA, USA, 2–4 November 2015; pp. 400–405. [Google Scholar]

- Bindra, A. Wide-Bandgap-Based Power Devices: Reshaping the power electronics landscape. IEEE Power Electron. Mag. 2015, 2, 42–47. [Google Scholar] [CrossRef]

- Danan, Y.; Ilovitsh, T.; Ramon, Y.; Malka, D.; Liu, D.; Zalevsky, Z. Silicon-coated gold nanoparticles nanoscopy. J. Nanophotonics 2016, 10, 36015. [Google Scholar] [CrossRef]

- Samoi, E.; Benezra, Y.; Malka, D. An ultracompact 3 × 1 MMI power-combiner based on Si slot-waveguide structures. Photonics Nanostructures Fundam. Appl. 2020, 39, 100780. [Google Scholar] [CrossRef]

- Malka, D.; Berke, B.A.; Tischler, Y.; Zalevsky, Z. Improving Raman spectra of pure silicon using super-resolved method. J. Opt. 2019, 21, 075801. [Google Scholar] [CrossRef]

- Zhang, W.; Huang, X.; Lee, F.C.; Li, Q.I. Gate drive design considerations for high voltage cascode GaN HEMT. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition—APEC, Fort Worth, TX, USA, 16–20 March 2014; pp. 1484–1489. [Google Scholar]

- Analog Devices Inc. Design Fundamentals of Implementing an Isolated Half-Bridge Gate Driver. Available online: https://www.analog.com (accessed on 18 March 2020).

- Liu, P.; Guo, S.; Yu, R.; Huang, A.Q.; Zhang, L. Analysis of Trade-Off Between Noise and Wide Band-Gap (WBG) Device Switching Speed. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Portland, OR, USA, 23–27 September 2018; pp. 3483–3489. [Google Scholar]

- Zhang, Z.; Zhang, W.; Wang, F.; Tolbert, L.M.; Blalock, B.J. Analysis of the switching speed limitation of wide band-gap devices in a phase-leg configuration. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Raleigh, NC, USA, 15–20 September 2012; pp. 3950–3955. [Google Scholar]

- Zhang, Z.; Wang, F.; Tolbert, L.M.; Blalock, B.J. Active Gate Driver for Crosstalk Suppression of SiC Devices in a Phase-Leg Configuration. IEEE Trans. Power Electron 2014, 29, 1986–1997. [Google Scholar] [CrossRef]

- Zhang, Z.; Dix, J.; Wang, F.F.; Blalock, B.J.; Costinett, D.; Tolbert, L.M. Intelligent Gate Drive for Fast Switching and Crosstalk Suppression of SiC Devices. IEEE Trans. Power Electron. 2017, 32, 9319–9332. [Google Scholar] [CrossRef]

- STMicroelectronics Mitigation technique of the SiC MOSFET gate voltage glitches with Miller clamp. Available online: https://www.st.com (accessed on 18 March 2020).

- Burkart, R.M.; Kolar, J.W. Comparative evaluation of SiC and Si PV inverter systems based on power density and efficiency as indicators of initial cost and operating revenue. In Proceedings of the IEEE 14th Workshop on Control and Modeling for Power Electronics (COMPEL), Salt Lake City, UT, USA, 23–26 June 2013; pp. 1–6. [Google Scholar]

- Burkart, R.M.; Kolar, J.W. Comparative Life Cycle Costs Analysis of Si and SiC PV Converter Systems Based on Advanced η-ρ-σ Multi-Objective Optimization Techniques. IEEE Trans. Power Electron. 2017, 32, 4344–4358. [Google Scholar] [CrossRef]

- Burkart, R.M.; Kolar, J.W. Comparative η-ρ-σ Pareto Optimization of Si and SiC Multilevel Dual-Active-Bridge Topologies With Wide Input Voltage Range. IEEE Trans. Power Electron. 2017, 32, 5258–5270. [Google Scholar] [CrossRef]

- Xie, R.; Wang, H.; Tang, G.; Yang, X.; Chen, K.J. An Analytical Model for False Turn-On Evaluation of High-Voltage Enhancement-Mode GaN Transistor in Bridge-Leg Configuration. IEEE Trans. Power Electron. 2017, 32, 6416–6433. [Google Scholar] [CrossRef]

- Ren, Y.; Xu, M.; Zhou, J.; Lee, F. Analytical loss model of power MOSFET. IEEE Trans. Power Electron. 2006, 21, 310–319. [Google Scholar]

- Trzynadlowski, A.; Kirlin, R.; Legowski, S. Space vector PWM technique with minimum switching losses and a variable pulse rate [for VSI]. IEEE Trans. Ind. Electron. 1997, 44, 173–181. [Google Scholar] [CrossRef]

| Terms | Content | Terms | Content |

|---|---|---|---|

| Basic Index | Output Characteristic | ||

| Size | 133 mm (H) × 242 mm (W) × 395 mm (D) | Rated voltage | 750 VDC |

| Weight | ≤ 15.5 kg | Rated current | 40 A |

| Operation temperature | −25 °C ~ + 75 °C −25 °C ~+ 65 °C fully output +65 °C ~ + 75 °C limited output | Max. current | 50 A |

| Storage temperature | −40 °C ~ + 75 °C | Voltage range | 300 V ~ 750 V |

| Relative humidity | 5% RH ~ 95% RH (no condensation) | Max. power | 30 kW |

| Altitude | ≤2000 m (limited function over 2000 m) | Voltage accuracy | ≤ ± 0.5% |

| Cooling mode | Intelligent air cooling | Current accuracy | ≤ ± 1% |

| Communication bus protocol | CAN | Current error | ≤ ± 0.5% |

| Max. NO. for parallel | 32 | Voltage error | ≤ ± 1% |

| Input Characteristic | Output ripple | Peak coefficient < 1% Root Mean Square (RMS) coefficient < 0.5% | |

| Operation voltage | 270 VAC ~ 450 VAC 270 VAC ~ 320 VAC limited output; 320 VAC ~ 450 VAC fully output | Starting impulse current | ≤ 110% |

| Frequency | 45 Hz ~ 65 Hz, 50 Hz/60 Hz rated | Peak efficiency | ≥ 97% |

| Input current | ≤ 60 A | Boot time | 3 s ~ 8 s |

| Power factor | ≥ 0.98 (loaded rate 50% ~ 100%) | Noise | < 65 dB (measurement distance 1 m) |

| Current THD | ≤ 5% (loaded rate 50% ~ 100%) | Stand-by loss | ≤ 25 W (380 VAC input) |

| Component | Manufacturer | Model | Parameters |

|---|---|---|---|

| 3-pin SiC MOSFET | Global Power Technology | GIM040120B | 1200 V 40 mΩ |

| 4-pin SiC MOSFET | Global Power Technology | GIM040120E | 1200 V 40 mΩ |

| AC side inductance | — | — | 225 μH |

| Parameter | Value | Unit | Note |

|---|---|---|---|

| Rated power | 30 | kW | — |

| AC voltage | 380 | V | Three-phase |

| DC voltage | 750 | V | — |

| Switching Frequency | 30 | kHz | — |

| AC side inductance | 225 | μH | 225 μH |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, Z.; Wang, Z.; Zheng, T.; Li, H.; Huang, B.; Shao, T. Efficiency Optimization for All-Silicon Carbide (SiC) PWM Rectifier Considering the Impact of Gate-Source Voltage Interference. Energies 2020, 13, 1421. https://doi.org/10.3390/en13061421

Li Z, Wang Z, Zheng T, Li H, Huang B, Shao T. Efficiency Optimization for All-Silicon Carbide (SiC) PWM Rectifier Considering the Impact of Gate-Source Voltage Interference. Energies. 2020; 13(6):1421. https://doi.org/10.3390/en13061421

Chicago/Turabian StyleLi, Zhijun, Zuoxing Wang, Trillion Zheng, Hong Li, Bo Huang, and Tiancong Shao. 2020. "Efficiency Optimization for All-Silicon Carbide (SiC) PWM Rectifier Considering the Impact of Gate-Source Voltage Interference" Energies 13, no. 6: 1421. https://doi.org/10.3390/en13061421