Gate Current in p-GaN Gate HEMTs as a Channel Temperature Sensitive Parameter: A Comparative Study between Schottky- and Ohmic-Gate GaN HEMTs

Abstract

:1. Introduction

- (i)

- Discussing the requirements of the gate-driver circuit for the two different classes of normally-off GaN HEMTs with p-type gate;

- (ii)

- Given the sensitivity of the gate current to the channel temperature [17], discussing the viability of using it as a temperature-sensitive electrical parameter (TSEP) and proposing a sensing circuit for its online monitoring.

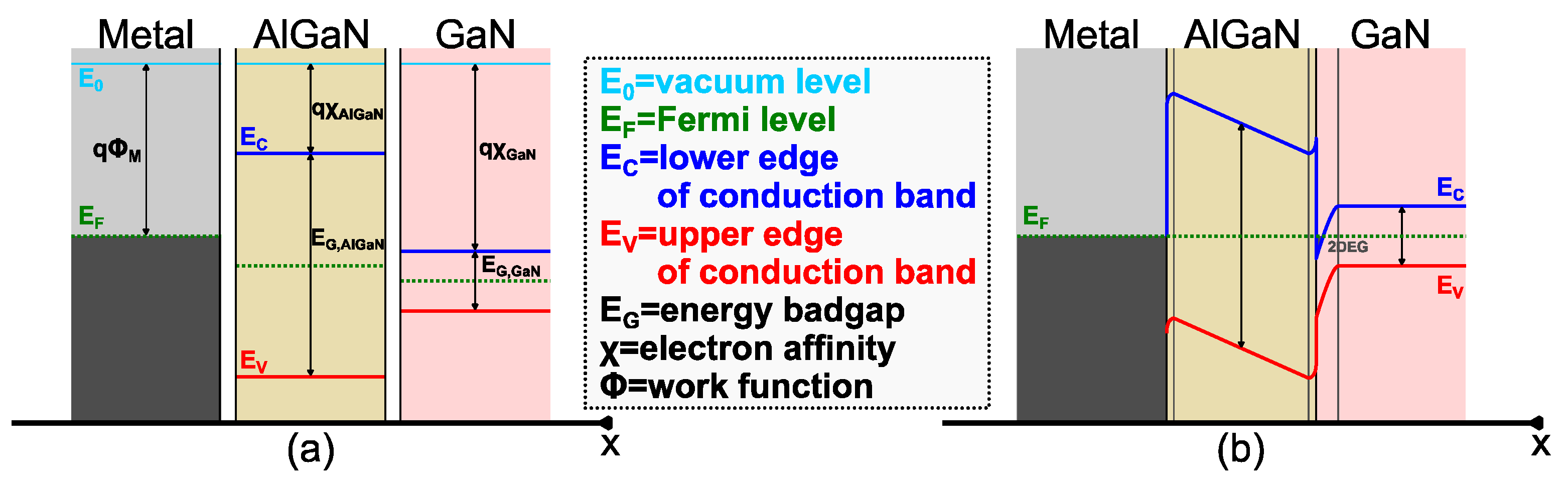

2. Gate Contact Types in Normally-Off p-GaN HEMTs

Experimental Investigation of Gate Leakage Current

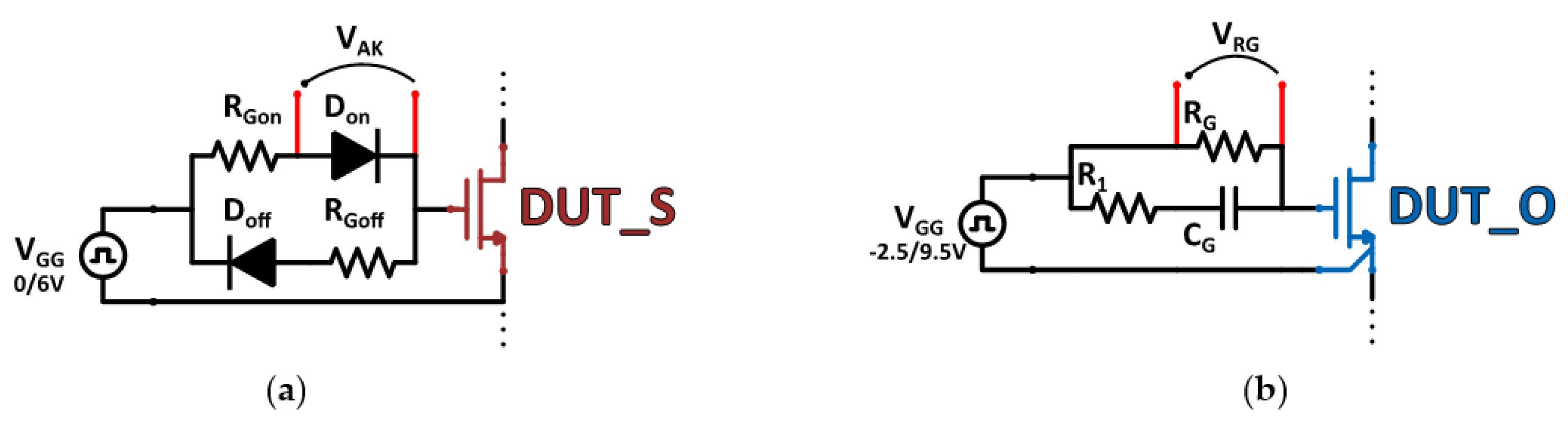

3. Gate-Driving Circuits for Schottky- and Ohmic-Gate p-GaN HEMTs

4. Experimental Results

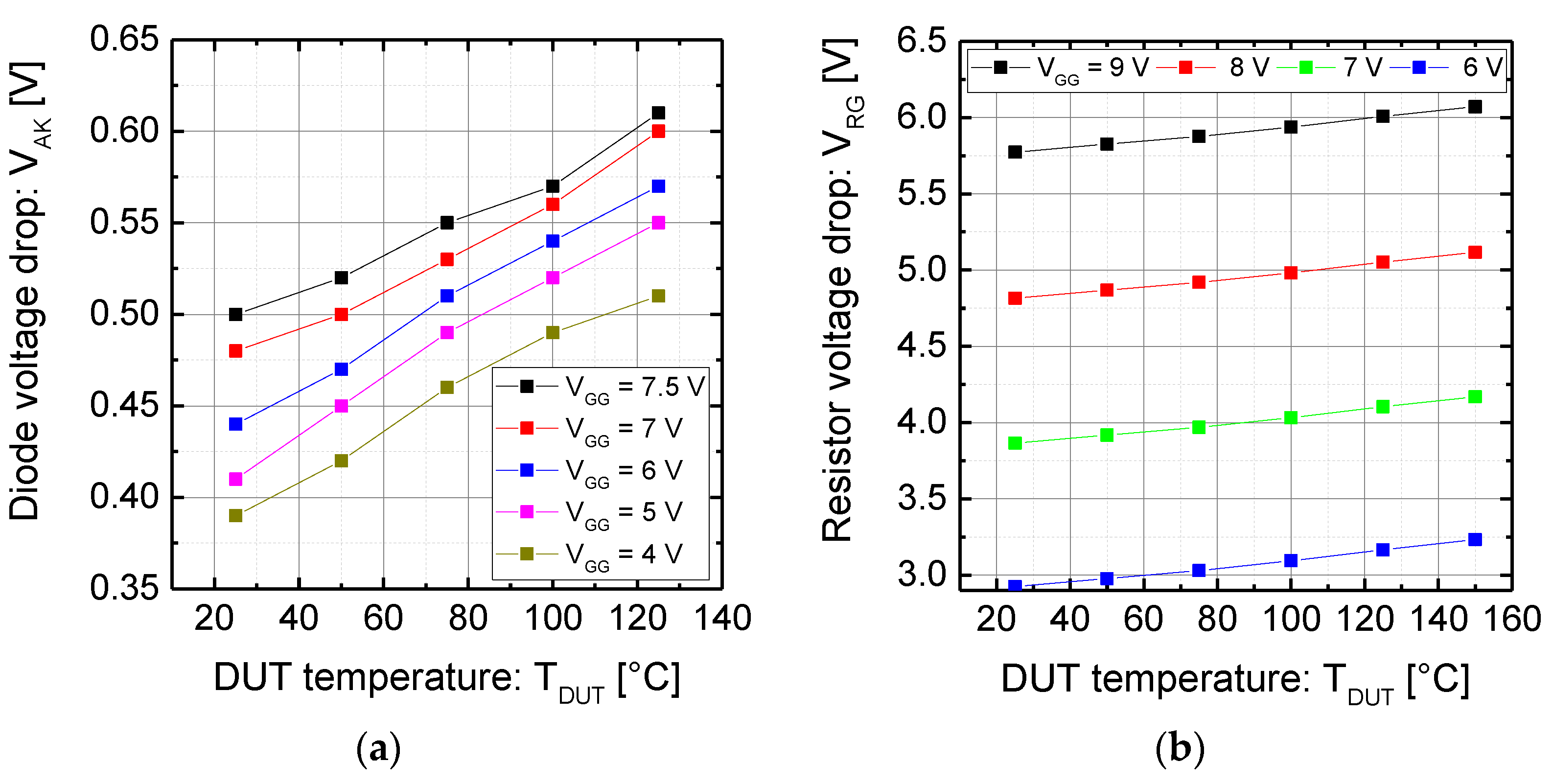

4.1. Gate Driver Circuit for Schottky-Gate p-GaN HEMTs and Monitoring of Gate Current

4.2. Gate Driver Circuit for Ohmic-Gate p-GaN HEMTs and Monitoring of Gate Current

5. Summary

Author Contributions

Funding

Conflicts of Interest

References

- Meneghini, M.; Meneghesso, G.; Zanoni, E. (Eds.) Power GaN Devices; Springer International Publishing: Cham, Switzerland, 2017. [Google Scholar] [CrossRef]

- Yu, H.A.; Duan, T. Gallium Nitride Power Devices, 1st ed.; Pan Stanford Publishing: Singapore, 2017. [Google Scholar]

- Kumar, V.; Kuliev, A.; Tanaka, T.; Otoki, Y.; Adesida, I. High transconductance enhancement-mode AlGaN/GaN HEMTs on SiC substrate. Electron. Lett. 2003, 39, 1758–1760. [Google Scholar] [CrossRef]

- Saito, W.; Takada, Y.; Kuraguchi, M.; Tsuda, K.; Omura, I. Recessed-gate structure approach toward normally off high-Voltage AlGaN/GaN HEMT for power electronics applications. IEEE Trans. Electron Devices 2006, 53, 356–362. [Google Scholar] [CrossRef]

- Cai, Y.; Zhou, Y.; Chen, K.J.; Lau, K.M. High-performance enhancement-mode AlGaN/GaN HEMTs using fluoride-based plasma treatment. IEEE Trans. Electron Devices 2005, 26, 435–437. [Google Scholar] [CrossRef]

- Cai, Y.; Zhou, Y.; Lau, K.M.; Chen, K.J. Control of threshold voltage of AlGaN/GaN HEMTs by fluoride-based plasma treatment: From depletion mode to enhancement mode. IEEE Trans. Electron Devices 2006, 53, 2207–2215. [Google Scholar] [CrossRef]

- Zhang, Y.; Sun, M.; Joglekar, S.J.; Fujishima, T.; Palacios, T. Threshold voltage control by gate oxide thickness in fluorinated GaN metal-oxide-semiconductor high-electron-mobility transistors. Appl. Phys. Lett. 2013, 103, 33524. [Google Scholar] [CrossRef]

- FRoccaforte, F.; Greco, G.; Fiorenza, P.; Iucolano, F. An overview of normally-off GaN-based high electron mobility transistors. Materials 2019, 12, 1599. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Jones, E.A.; Wang, F.F.; Costinett, D. Review of commercial GaN power devices and GaN-based converter design challenges. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 707–719. [Google Scholar] [CrossRef]

- Uemoto, Y.; Hikita, M.; Ueno, H.; Matsuo, H.; Ishida, H.; Yanagihara, M.; Ueda, T.; Tanaka, T.; Ueda, D. Gate injection transistor (GIT)—A normally-off AlGaN/GaN power transistor using conductivity modulation. IEEE Trans. Electron Devices 2007, 54, 3393–3399. [Google Scholar] [CrossRef]

- Efthymiou, L.; Longobardi, G.; Camuso, G.; Chien, T.; Chen, M.; Udrea, F. On the physical operation and optimization of the p-GaN gate in normally-off GaN HEMT devices. Appl. Phys. Lett. 2017, 110, 123502. [Google Scholar] [CrossRef]

- Tokuda, H.; Asubar, J.T.; Kuzuhara, M. Design considerations for normally-off operation in Schottky gate p-GaN/AlGaN/GaN HEMTs. Jpn. J. Appl. Phys. 2020, 59, 084002. [Google Scholar] [CrossRef]

- Wu, H.; Fayyaz, A.; Castellazzi, A. P-gate GaN HEMT gate-driver design for joint optimization of switching performance, freewheeling conduction and short-circuit robustness. In Proceedings of the 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, USA, 13–17 May 2018; pp. 232–235. [Google Scholar] [CrossRef]

- Wang, M.; Zhang, W.J.; Liang, J.; Cui, W.T.; Ng, W.T.; Nishio, H.; Sumida, H.; Nakajima, H. A smart gate driver for SiC power MOSFETS with aging compensation and ringing suppression. In Proceedings of the 2021 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Nagoya, Japan, 30 May–3 June 2021. [Google Scholar] [CrossRef]

- Zhang, W.J.; Yu, J.; Cui, W.T.; Leng, Y.; Liang, J.; Hsieh, Y.-T.; Tsai, H.-H.; Juang, Y.-Z.; Yeh, W.-K.; Ng, W.T. A smart gate driver IC for GaN power HEMTs with dynamic ringing suppression. IEEE Trans. Power Electron. 2021, 36, 14119–14132. [Google Scholar] [CrossRef]

- Weckbrodt, J.; Ginot, N.; Batard, C.; Azzopardi, S. Monitoring of gate leakage current on SiC power MOSFETs: An estimation method for smart gate drivers. IEEE Trans. Power Electron. 2021, 36, 8752–8760. [Google Scholar] [CrossRef]

- Stockman, A.; Masin, F.; Meneghini, M.; Zanoni, E.; Meneghesso, G.; Bakeroot, B.; Moens, P. Gate conduction mechanisms and lifetime modeling of p-Gate AlGaN/GaN high-electron-mobility transistors. IEEE Trans. Electron Devices 2018, 65, 5365–5372. [Google Scholar] [CrossRef]

- Kittel, C. Introduction to Solid State Physics, 8th ed.; Wiley Publishing: Hoboken, NJ, USA, 1996; ISBN 978-0-471-41526-8. [Google Scholar]

- Bernardini, F.; Fiorentini, V.; Vanderbilt, D. Spontaneous polarization and piezoelectric constants of III-V nitrides. Phys. Rev. B Condens. Matter Mater. Phys. 1997, 56, R10024–R10027. [Google Scholar] [CrossRef] [Green Version]

- Ambacher, O.; Smart, J.; Shealy, J.R.; Weimann, N.G.; Chu, K.; Murphy, M.; Schaff, W.J.; Eastman, L.F.; Dimitrov, R.; Wittmer, L.; et al. Two-dimensional electron gases induced by spontaneous and piezoelectric polarization charges in N- And Ga-face AIGaN/GaN heterostructures. J. Appl. Phys. 1999, 85, 3222–3233. [Google Scholar] [CrossRef] [Green Version]

- Wu, Y.R.; Singh, M.; Singh, J. Gate leakage suppression and contact engineering in nitride heterostructures. J. Appl. Phys. 2003, 94, 5826–5831. [Google Scholar] [CrossRef] [Green Version]

- Fujii, T.; Tsuyukuchi, N.; Hirose, Y.; Iwaya, M.; Kamiyama, S.; Amano, H.; Akasaki, I. Control of threshold voltage of enhancement-mode AlxGa1-xN/GaN junction heterostructure field-effect transistors using p-GaN gate contact. Jpn. J. Appl. Phys. 2007, 46, 115. [Google Scholar] [CrossRef]

- Lee, F.; Su, L.-Y.; Wang, C.-H.; Wu, Y.-R.; Huang, J.J. Impact of gate metal on the performance of p-GaN/AlGaN/GaN high electron mobility transistors. IEEE Trans. Electron Devices 2015, 36, 232–234. [Google Scholar] [CrossRef]

- Bakeroot, B.; Stockman, A.; Posthuma, N.; Stoffels, S.; Decoutere, S. Analytical model for the threshold voltage of p-(Al)GaN high-electron-mobility transistors. IEEE Trans. Electron Devices 2018, 65, 79–86. [Google Scholar] [CrossRef]

- GaN Systems. GS66508T top-side cooled 650 V E-mode GaN transistor. In GS66508T Data Sheet; GaN Systems: Kanata, ON, Canada, 2020; rev. 200402. [Google Scholar]

- Infineon. 600V CoolGaN™ enhancement-mode power transistor. In IGOT60R070D1 Data Sheet; Infineon: Neubiberg, Germany, 2020; rev. 2.12. [Google Scholar]

- Borghese, A.; Riccio, M.; Longobardi, G.; Maresca, L.; Breglio, G.; Irace, A. Gate leakage current sensing for in situ temperature monitoring of p-GaN gate HEMTs. Microelectron. Reliab. 2020, 114, 113762. [Google Scholar] [CrossRef]

- Borghese, A.; Riccio, M.; Maresca, L.; Breglio, G.; Irace, A. Gate driver for p-GaN HEMTs with real-time monitoring capability of channel temperature. In Proceedings of the 2021 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Nagoya, Japan, 30 May–3 June 2021; pp. 63–66. [Google Scholar] [CrossRef]

- Fernandez, M.; Perpina, X.; Roig, J.; Vellvehi, M.; Bauwens, F.; Jorda, X.; Tack, M. P-GaN HEMTs drain and gate current analysis under short-circuit. IEEE Trans. Electron Devices 2017, 38, 505–508. [Google Scholar] [CrossRef]

- Riccio, M.; Romano, G.; Maresca, L.; Breglio, G.; Irace, A.; Longobardi, G. Short circuit robustness analysis of new generation Enhancement-mode p-GaN power HEMTs. In Proceedings of the 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, USA, 13–17 May 2018; pp. 104–107. [Google Scholar] [CrossRef]

- GaN Systems. How to drive GaN Enhancement mode HEMT. In Application Note GN001; GaN Systems: Kanata, ON, Canada, 2016. [Google Scholar]

- He, J.; Tang, G.; Chen, K.J. VTH instability of p-GaN gate HEMTs under static and dynamic gate stress. IEEE Trans. Electron Devices 2018, 39, 1576–1579. [Google Scholar] [CrossRef]

- Gonzalez, J.O.; Etoz, B.; Alatise, O. Characterizing threshold voltage shifts and recovery in Schottky gate and ohmic gate GaN HEMTs. In Proceedings of the 2020 IEEE Energy Conversion Congress and Exposition (ECCE), Detroit, MI, USA, 11–15 October 2020; pp. 217–224. [Google Scholar] [CrossRef]

- Zeng, C.; Xu, W.; Xia, Y.; Pan, D.; Wang, Y.; Wang, Q.; Zhu, Y.; Ren, F.; Zhou, D.; Ye, J.; et al. Investigations of the gate instability characteristics in Schottky/ohmic type p-GaN gate normally-off AlGaN/GaN HEMTs. Appl. Phys. Express 2019, 12, 121005. [Google Scholar] [CrossRef]

- Shi, Y.; Zhou, Q.; Cheng, Q.; Wei, P.; Zhu, L.; Wei, D.; Zhang, A.; Chen, W.; Zhang, B. Carrier transport mechanisms underlying the bidirectional VTH shift in p-GaN gate HEMTs under forward gate stress. IEEE Trans. Electron Devices 2019, 66, 876–882. [Google Scholar] [CrossRef]

- Stockman, A.; Moens, P. ON-state gate stress induced threshold voltage instabilities in p-GaN Gate AlGaN/GaN HEMTs. In Proceedings of the 2020 IEEE International Integrated Reliability Workshop (IIRW), South Lake Tahoe, CA, USA, 4–8 October 2020; pp. 1–4. [Google Scholar] [CrossRef]

- Gurpinar, E.; Castellazzi, A. Single-phase T-type inverter performance benchmark using Si IGBTs, SiC MOSFETs, and GaN HEMTs. IEEE Trans. Power Electron. 2016, 31, 7148–7160. [Google Scholar] [CrossRef]

- Zojer, B. Driving 600 V CoolGaN™ high electron mobility transistors. In Application Note AN_201702_PL52_012; Infineon Technologies AG: Neubiberg, Germany, 2018. [Google Scholar]

- Garcia Mora, R.A.; Haksoz, Y.; Persson, E. How to parallel CoolGaN™ 600 V HEMT in half-bridge configurations for higher-power applications. In Engineering Report V1.0; Infineon Technologies AG: Neubiberg, Germany, 2020. [Google Scholar]

| Parameter | Value | Unit |

|---|---|---|

| VDC,in | 20 to 120 | [V] |

| fsw | 500 | [kHz] |

| CDC | 100 | [µF] |

| RLOAD | 50 | [Ω] |

| L1 | 240 | [µH] |

| RG | 470 | [Ω] |

| CG | 3 | [nF] |

| R1 | 10 | [Ω] |

| R2, R3 | 1 | [Ω] |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Borghese, A.; Di Costanzo, A.; Riccio, M.; Maresca, L.; Breglio, G.; Irace, A. Gate Current in p-GaN Gate HEMTs as a Channel Temperature Sensitive Parameter: A Comparative Study between Schottky- and Ohmic-Gate GaN HEMTs. Energies 2021, 14, 8055. https://doi.org/10.3390/en14238055

Borghese A, Di Costanzo A, Riccio M, Maresca L, Breglio G, Irace A. Gate Current in p-GaN Gate HEMTs as a Channel Temperature Sensitive Parameter: A Comparative Study between Schottky- and Ohmic-Gate GaN HEMTs. Energies. 2021; 14(23):8055. https://doi.org/10.3390/en14238055

Chicago/Turabian StyleBorghese, Alessandro, Alessandro Di Costanzo, Michele Riccio, Luca Maresca, Giovanni Breglio, and Andrea Irace. 2021. "Gate Current in p-GaN Gate HEMTs as a Channel Temperature Sensitive Parameter: A Comparative Study between Schottky- and Ohmic-Gate GaN HEMTs" Energies 14, no. 23: 8055. https://doi.org/10.3390/en14238055