Comprehensive Modulation Strategies for Synchronous Reluctance Motor Drives Used in Weak Grids

Abstract

:1. Introduction

- (a)

- A carrier-based power-factor adaptive PWM (PFA-DPWM) implementation was proposed to improve motor and drive efficiency;

- (b)

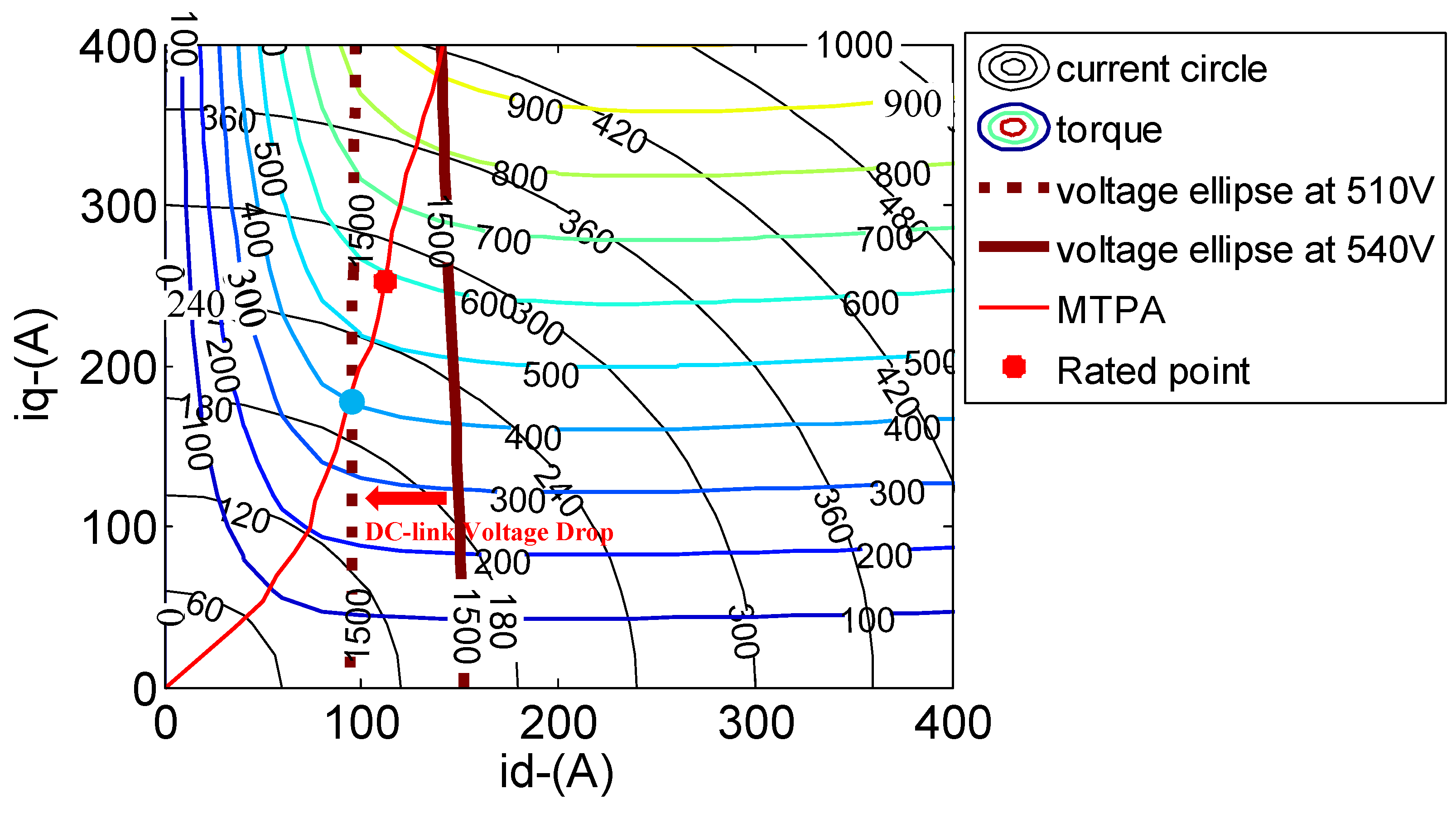

- The speed/torque limits for different DC-link voltages considering the nonlinear cross-coupled mode were comprehensively evaluated;

- (c)

- The optimal appropriate modulation strategies for a specific SynRM were selected.

2. Voltage Utilization Issue Statement on Specific SynRMs

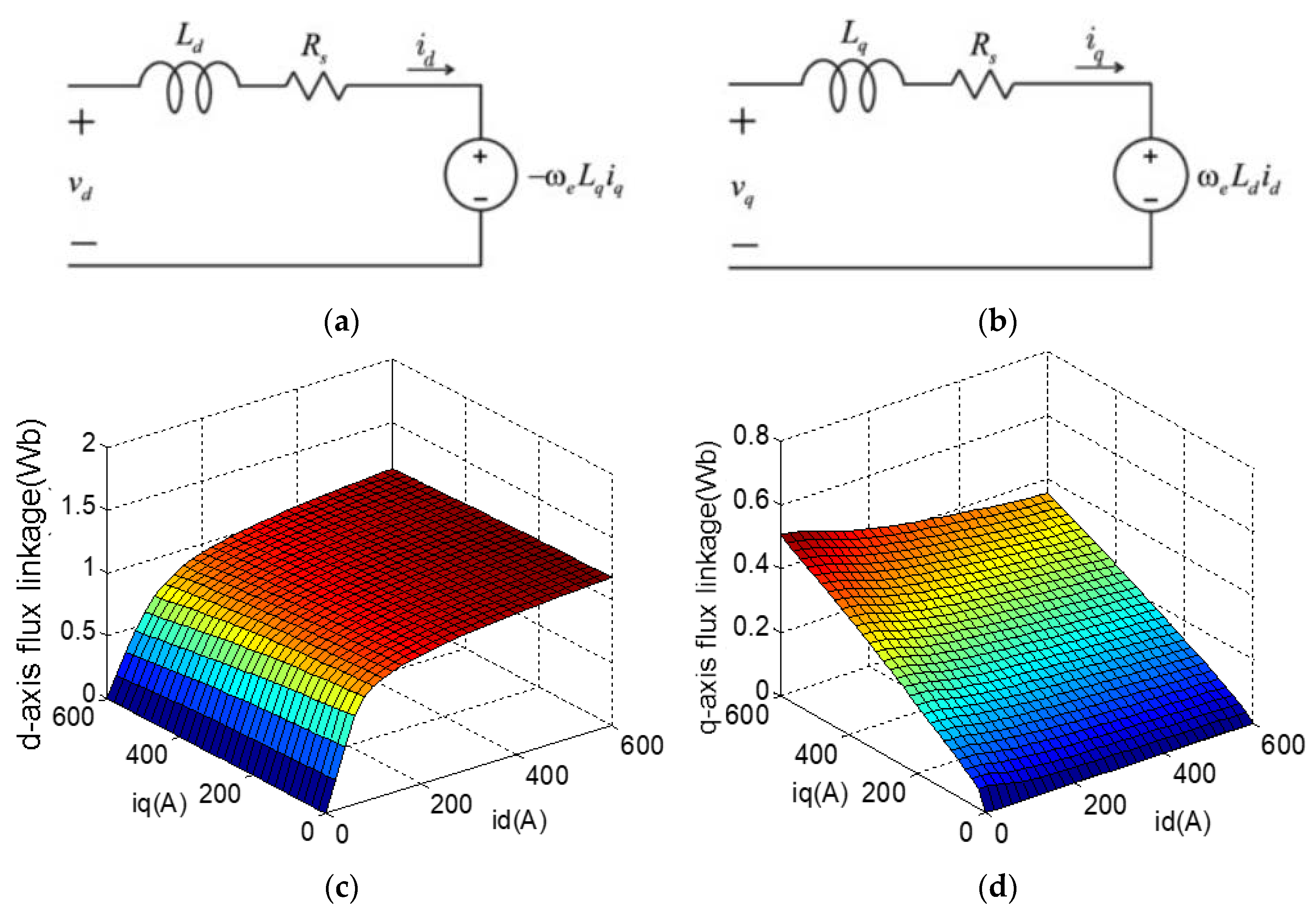

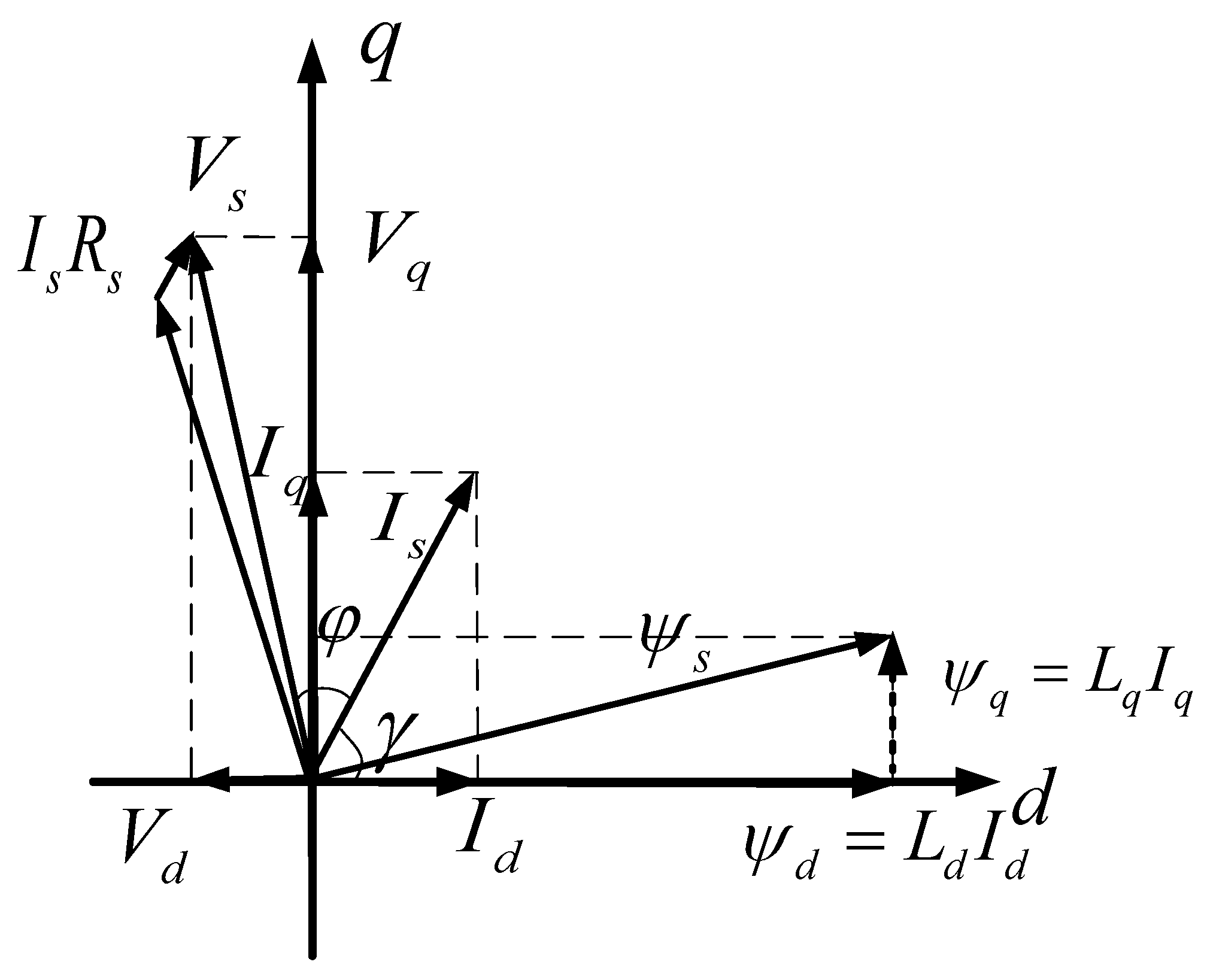

2.1. SynRM Modeling

2.2. Speed Limit at Specific DC-Link Voltage

- (a)

- The input voltage can drop because of a weak grid, and a 5–6% input ripple voltage exists when connected to a weak grid, as mentioned in [2].

- (b)

- Considering the volume and cost, the drive size is usually designed to be highly compact and leads to a limited capacitor volume. In our case, the DC-link voltage was connected in parallel with four electrolytic capacitors (two in series and then in parallel, 8200 µF/400 V × 4; 8200 µF in total), as shown in Figure 3. The DC-link voltage may drop when the output mechanical power increases as discussed in [3].

- (c)

- The induced voltage for the SynRM was designed to be close to the available DC-link voltage; for example, the phase voltages, in our case, were intended to be approximately 210 V-RMS.

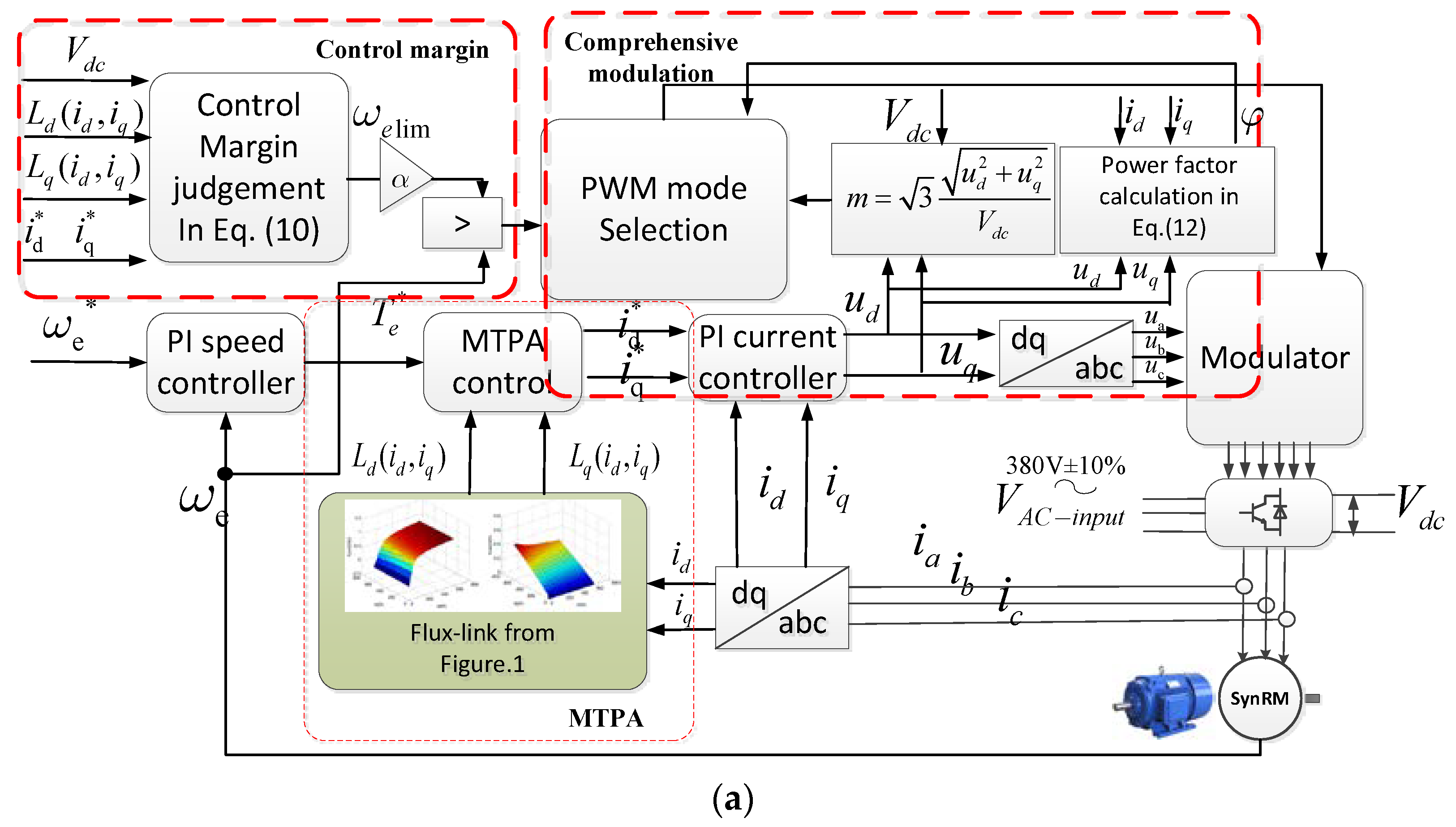

3. Proposed Comprehensive Modulation Strategy Used for SynRMs

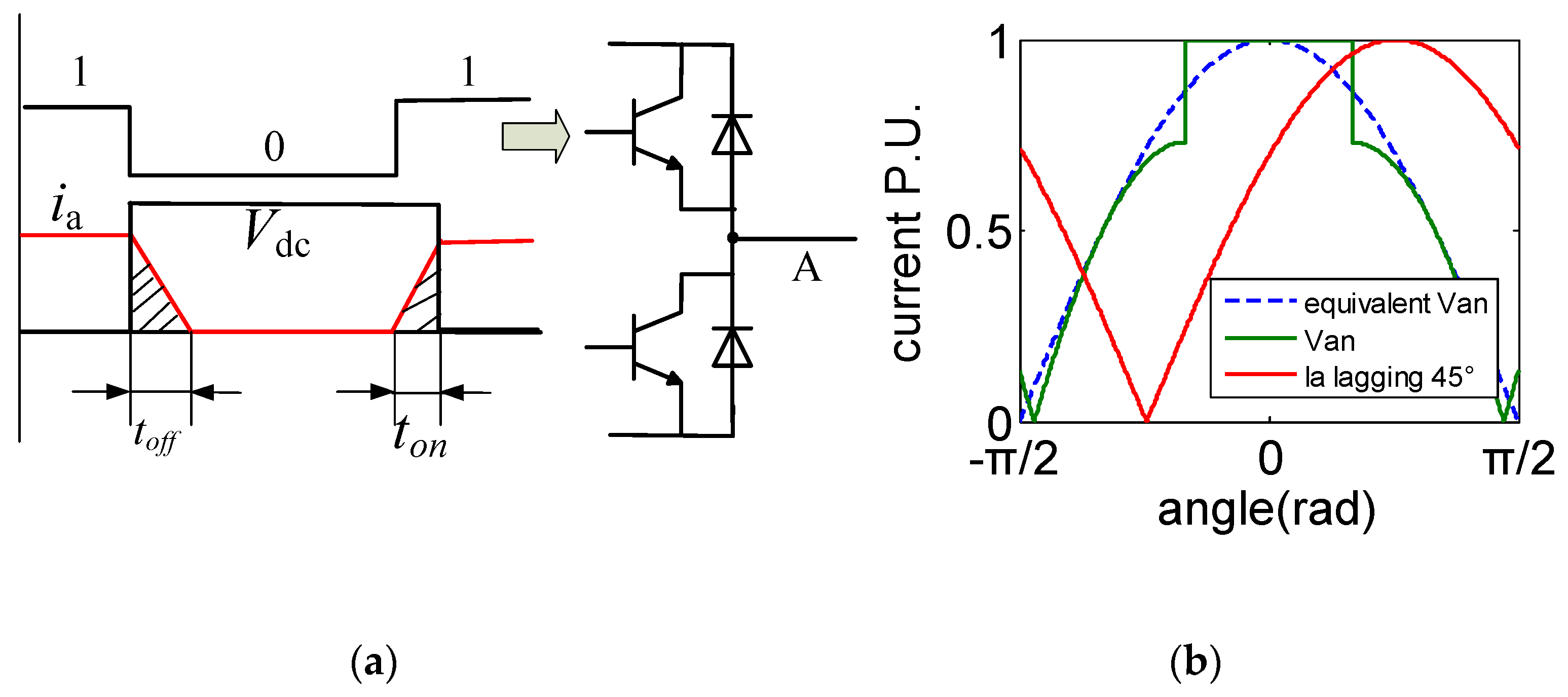

3.1. Proposed Power Factor Adaptive Discontinuous PWM Strategy

- (a)

- The ratio of the fundamental component magnitude of the phase output voltage to the DC-link voltage is termed the modulation index in m = Vs/(Vdc).

- (b)

- The three-phase voltage modulation signals are marked as Vx (x = a,b,c), representing (Va, Vb, Vc) with a mutual difference of 120° in Equation (13), where Ma is equal to Vs/(0.5Vdc) as the normalizing coefficient. The zero-voltage vector Vzc was superimposed on the original voltage signal, Vx (x = a,b,c), and did not influence the line-to-line voltage. Therefore, abundant control effects can be achieved by injecting different forms of sequence voltage vectors.

- (c)

- The power factor angle φ is shown in rad units, and the degree (unit) can be obtained from 180/π times rad (unit).

- (d)

- Design functions include:

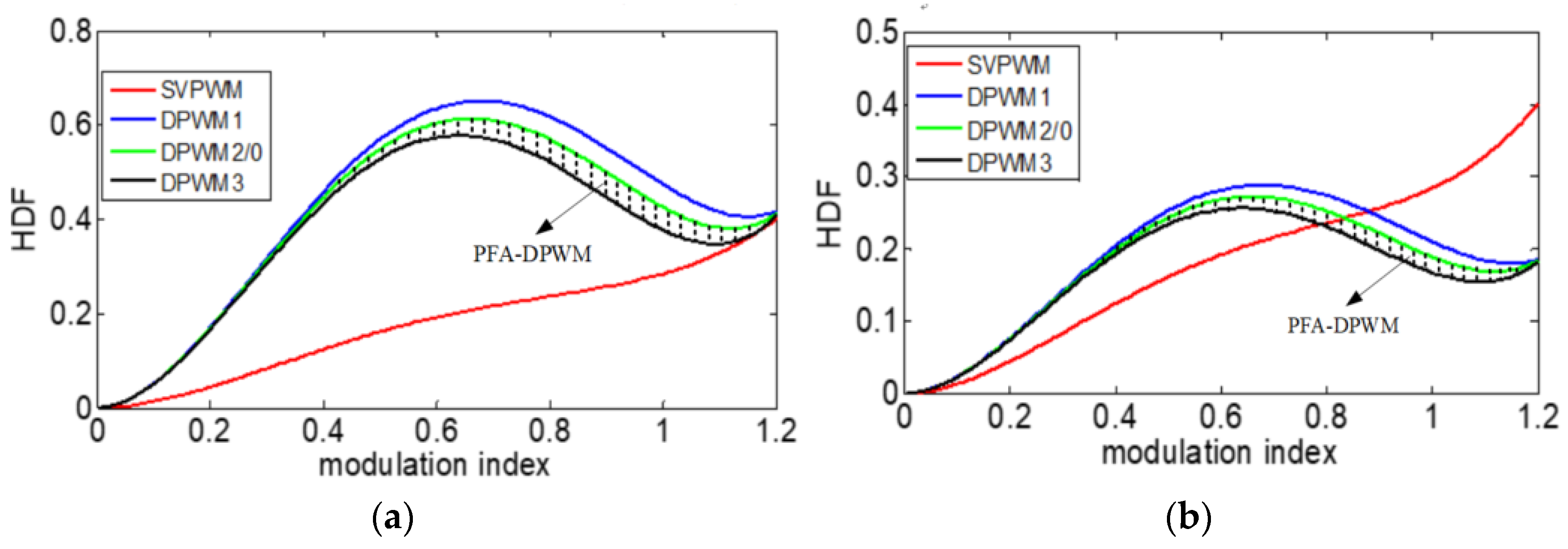

3.2. Proposed PFA-DPWM Switching Loss Analysis

- φ ∈ [π/6, π/3] PFA-DPWM generates the DPWM2 pattern (marked as ③ in Figure 8). The switching losses were 0.5–0.567 times that of the SVPWM.

- φ ∈ [π/3, π/2] PFA-DPWM generates a split-clamp pattern (marked as ④ in Figure 8); the switching losses were 0.567–0.634 times that of the SVPWM.

- φ = π/2, the PFA-DPWM generates a DPWM3 pattern (marked as ⑤ in Figure 8). The switching losses were 0.634 times that of the SVPWM.

3.3. Proposed PFA-DPWM Harmonics and DCVU Analysis

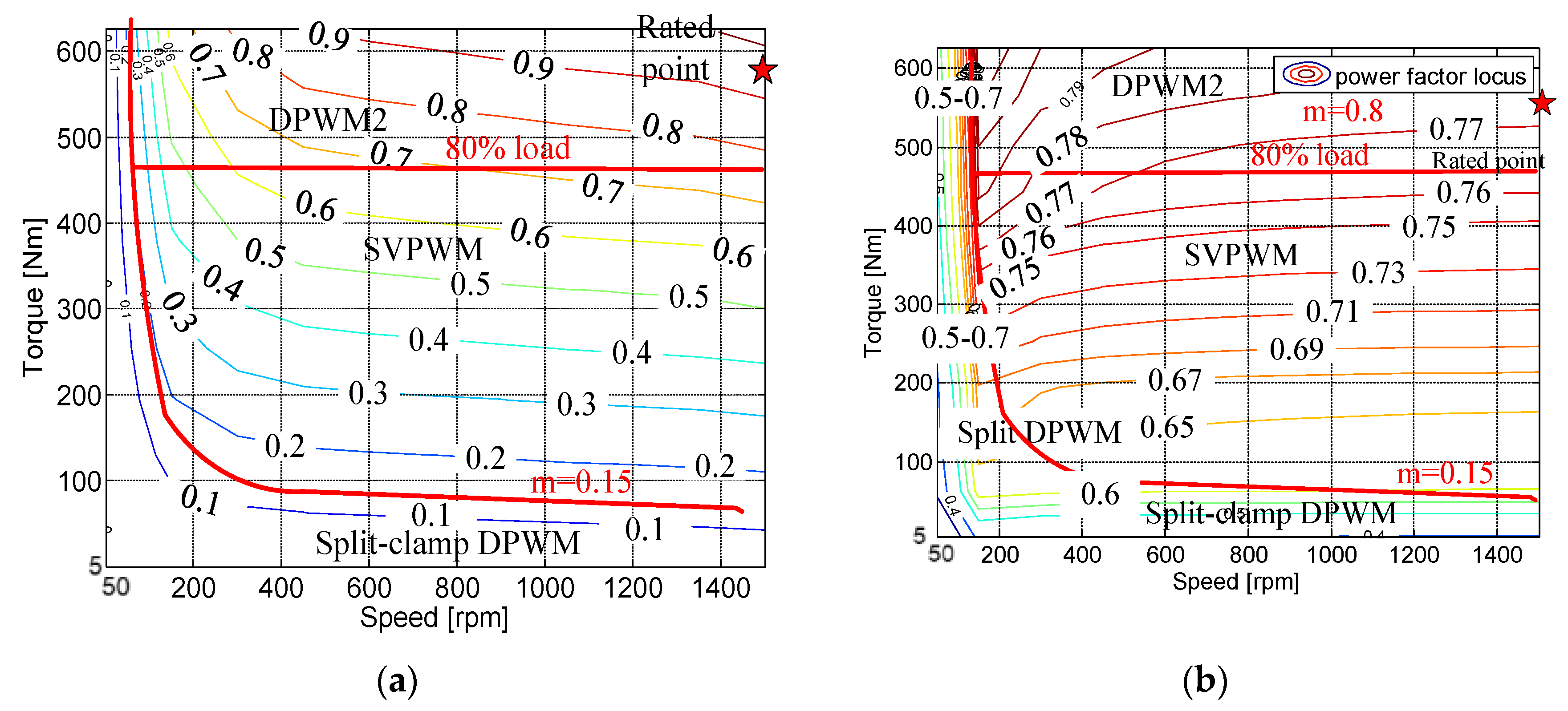

3.4. Modulation Strategy Selection for SynRM

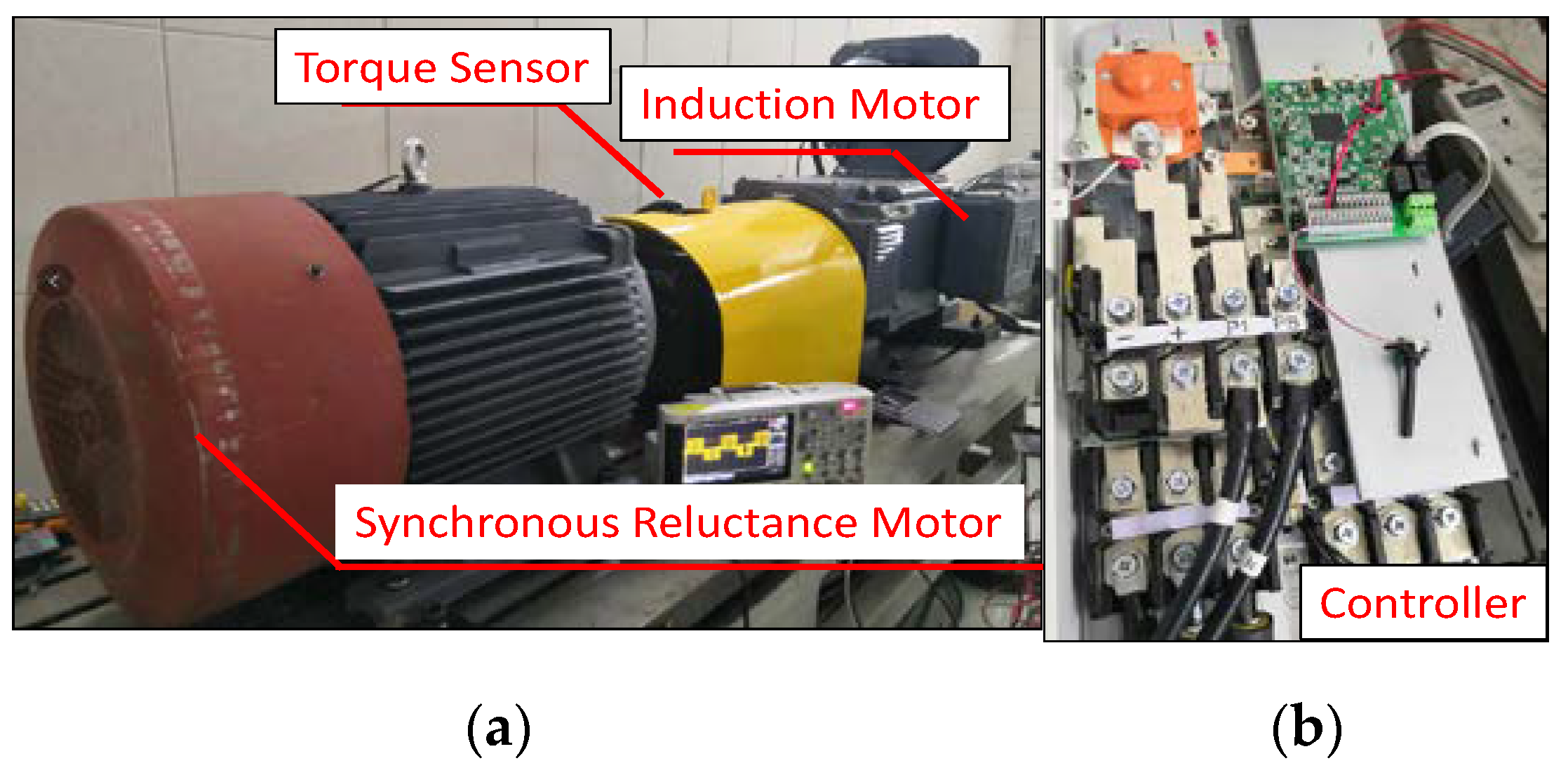

4. Experimental Results and Discussion

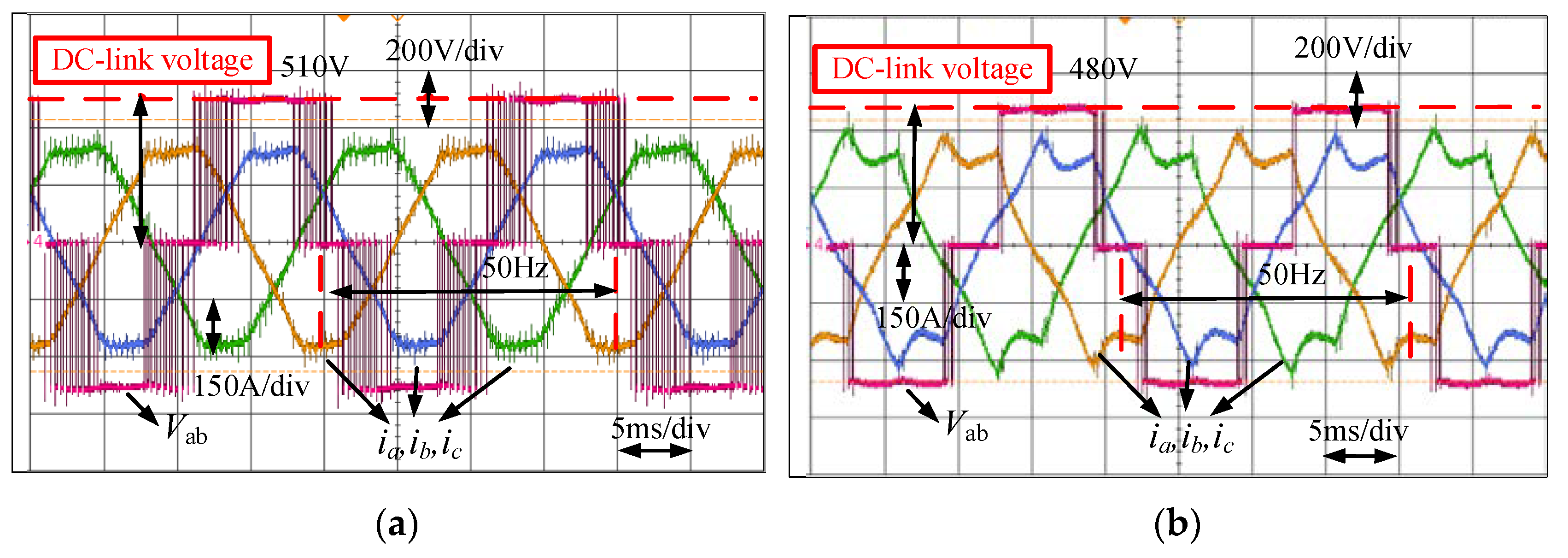

4.1. PWM Pattern Comparison

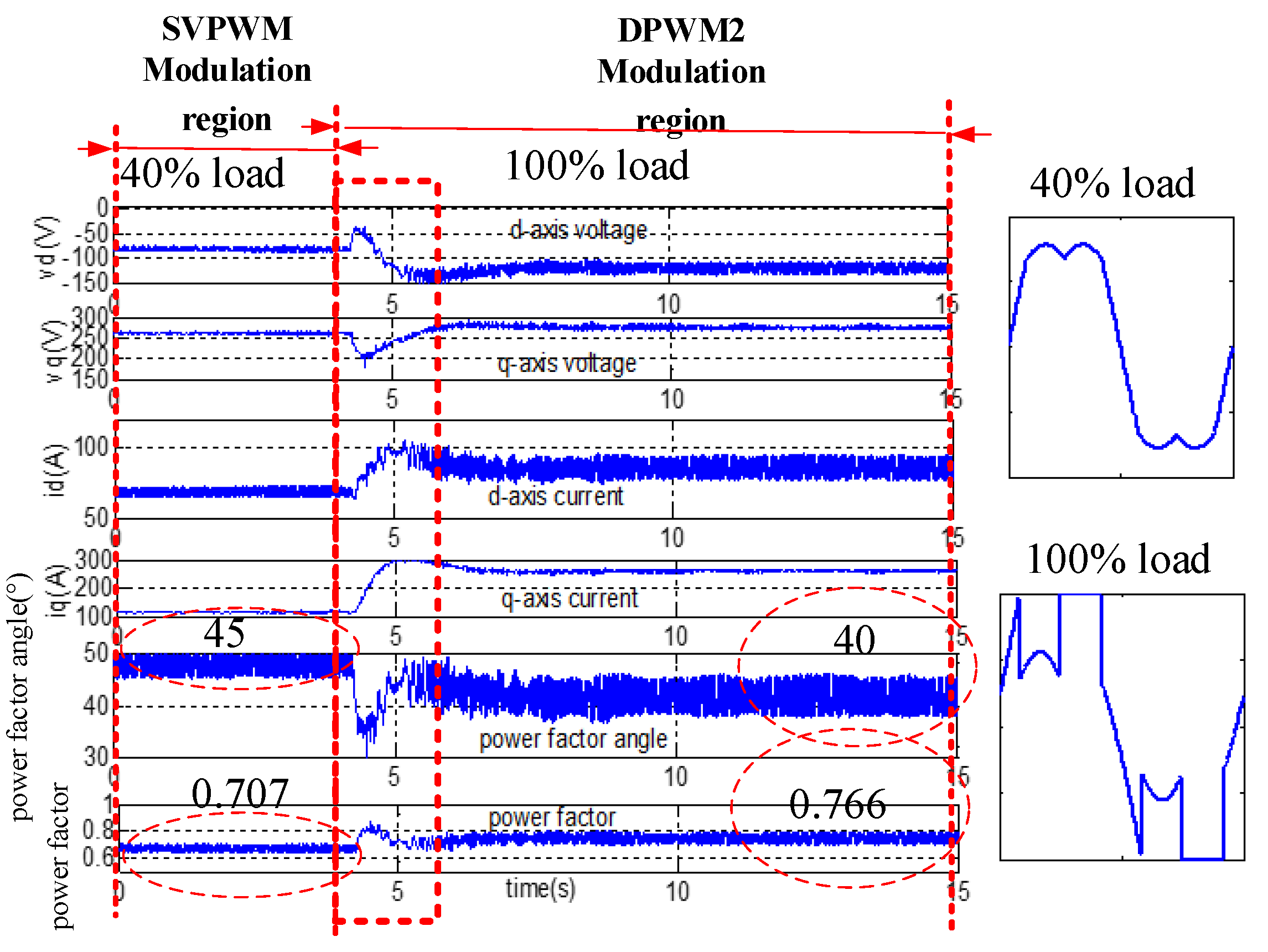

4.2. PWM Modulation Dynamical Experimental Results

4.3. Modulation Patterns Dealing with Voltage Drop

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Ghosh, P.R.; Das, A.; Bhuvaneswari, G. Analysis and implementation of a new method to retain the original speed and torque of synchronous reluctance motor during sustained voltage dip. IET Electr. Power Appl. 2019, 13, 1365–1377. [Google Scholar] [CrossRef]

- Kim, J.; Jeong, I.; Lee, K.; Nam, K. Fluctuating current control method for a PMSM along constant torque contours. IEEE Trans. Power Electron. 2014, 29, 6064–6073. [Google Scholar] [CrossRef]

- Mathe, L.; Torok, L.; Wang, D.; Sera, D. Resonance reduction for AC drives with small capacitance in the DC link. IEEE Trans. Ind. Appl. 2017, 53, 3814–3820. [Google Scholar] [CrossRef]

- Ding, D.; Wang, G.; Zhao, N.; Zhang, G.; Xu, D. Enhanced Flux-Weakening Control Method for Reduced DC-Link Capacitance IPMSM Drives. IEEE Trans. Power Electron. 2018, 34, 7788–7799. [Google Scholar] [CrossRef]

- Lee, D.C.; Lee, G.M. A novel overmodulation technique for space-vector PWM inverters. IEEE Trans. Power Electron. 1998, 13, 1144–1151. [Google Scholar]

- Cong, W.; Qiwei, L. Analysis of naturally sampled space vector modulation PWM in overmodulation region. In Proceedings of the IEEE International Power Electronics and Motion Control Conference, Xi’an, China, 14–16 August 2004. [Google Scholar]

- Olarescu, N.V.; Musuroi, S.; Sorandaru, C.; Weinmann, M.; Zeh, S. Optimum current control for wide speed range operation of PMSM drive without regenerative unit utilizing PWM-VSI overmodulation. In Proceedings of the IEEE Energy Conversion Congress & Exposition (ECCE), Raleigh, NC, USA, 16–20 September 2012. [Google Scholar]

- Fang, X.; Tian, Z.; Li, H.; Yang, Z.; Lin, F.; Hillmansen, S. Current closed-loop control and field orientation analysis of an induction motor in six-step operation for railway applications. IET Power Electron. 2019, 12, 1462–1469. [Google Scholar] [CrossRef]

- Masisi, L.; Pillay, P.; Williamson, S.S. A modulation strategy for a three-level inverter synchronous reluctance motor (SynRM) drive. IEEE Trans. Ind. Appl. 2015, 52, 1874–1881. [Google Scholar] [CrossRef]

- Hava, A.M.; Kerkman, R.J. A high-performance generalized discontinuous PWM algorithm. IEEE Trans. Ind. Appl. 1998, 34, 1059–1071. [Google Scholar] [CrossRef]

- Hava, A.M.; Çetin, N.O. A Generalized Scalar PWM Approach with Easy Implementation Features for Three-Phase, Three-Wire Voltage-Source Inverters. IEEE Trans. Power Electron. 2011, 26, 1385–1395. [Google Scholar] [CrossRef]

- An, S.L.; Sun, X.D.; Zhang, Q.; Zhong, Y.R.; Ren, B.Y. Study on the Novel Generalized Discontinuous SVPWM Strategies for Three-Phase Voltage Source Inverters. IEEE Trans. Ind. Inform. 2013, 9, 781–789. [Google Scholar] [CrossRef]

- Masisi, L.; Pillay, P.; Williamson, S. Comparison of two modulation strategies for a three level inverter synchronous reluctance motor (SynRM) drive. In Proceedings of the 2014 IEEE Industry Application Society Annual Meeting, Vancouver, BC, Canada, 5–9 October 2014; IEEE: Piscataway, NJ, USA, 2014; pp. 1–7. [Google Scholar]

- Wu, Y.; Shafi, M.A.; Knight, A.M.; McMahon, R.A. Comparison of the Effects of Continuous and Discontinuous PWM Schemes on Power Losses of Voltage-Sourced Inverters for Induction Motor Drives. IEEE Trans. Power Electron. 2011, 26, 182–191. [Google Scholar] [CrossRef]

- Holtz, J.; Lotzkat, W.; Khambadkone, A.M. On continuous control of PWM inverters in the overmodulation range including six-step. IEEE Trans. Power Electron. 1993, 8, 546–553. [Google Scholar] [CrossRef]

- Zhou, K.; Wang, D. Relationship between space-vector modulation and three-phase carrier-based PWM: A comprehensive analysis. IEEE Trans. Ind. Electron. 2002, 49, 186–196. [Google Scholar] [CrossRef]

- Park, H.J.; Youn, M.J. A new time-domain discontinuous space-vector PWM technique in overmodulation region. IEEE Trans. Ind. Electron. 2003, 50, 349–355. [Google Scholar] [CrossRef]

- Holmes, D.G.; Lipo, T.A. Pulse Width Modulation for Power Converters: Principles and Practice; Wiley-IEEE Press: Hoboken, NJ, USA, 2003. [Google Scholar]

- Narayanan, G.; Krishnamurthy, H.K.; Zhao, D.; Ayyanar, R. Advanced bus-clamping PWM techniques based on space vector approach. IEEE Trans. Power Electron. 2006, 21, 974–984. [Google Scholar] [CrossRef]

- Nguyen, T.D.; Hobraiche, J.; Patin, N.; Friedrich, G.; Vilain, J.-P. A direct digital technique implementation of general discontinuous pulse width modulation strategy. IEEE Trans. Ind. Electron. 2010, 58, 4445–4454. [Google Scholar] [CrossRef]

- Zhao, D.; Hari, V.S.S.P.K.; Narayanan, G.; Ayyanar, R. Space-vector-based hybrid pulsewidth modulation techniques for reduced harmonic distortion and switching loss. IEEE Trans. Power Electron. 2009, 25, 760–774. [Google Scholar] [CrossRef]

- Biswas, J.; Nair, M.D.; Gopinath, V.; Barai, M. An optimized hybrid SVPWM strategy based on multiple division of active vector time (MDAVT). IEEE Trans. Power Electron. 2016, 32, 4607–4618. [Google Scholar] [CrossRef]

- Hari, V.S.S.P.K.; Narayanan, G. Theoretical and experimental evaluation of pulsating torque produced by induction motor drives controlled with advanced bus-clamping pulsewidth modulation. IEEE Trans. Ind. Electron. 2015, 63, 1404–1413. [Google Scholar] [CrossRef]

- Wu, X.; Tan, G.; Ye, Z.; Liu, Y.; Xu, S. Optimized common-mode voltage reduction PWM for three-phase voltage-source inverters. IEEE Trans. Power Electron. 2015, 31, 2959–2969. [Google Scholar] [CrossRef]

- Da Silva, E.R.C.; dos Santos, E.C.; Jacobina, B. Pulsewidth modulation strategies. IEEE Ind. Electron. Mag. 2011, 5, 37–45. [Google Scholar] [CrossRef]

- Wang, S.; Kang, J.; Degano, M.; Galassini, A.; Gerada, C. An Accurate Wide-speed Range Control Method of IPMSM Considering Resistive Voltage Drop and Magnetic Saturation. IEEE Trans. Ind. Electron. 2019, 67, 2630–2641. [Google Scholar] [CrossRef]

- Wang, S.; Degano, M.; Kang, J.; Galassini, A.; Gerada, C. A novel Newton-Raphson-based searching method for the MTPA control of PMaSynRM considering magnetic and cross saturation. In Proceedings of the 2018 XIII International Conference on Electrical Machines (ICEM), Alexandroupoli, Greece, 3–6 September 2018; pp. 1360–1366. [Google Scholar]

- Aparaschivei, A.; Chiriac, G.; Lucache, D.D. Starting of large compressor motors on a weak grid-Case study. In Proceedings of the International Conference and Exposition On Electrical And Power Engineering (EPE), Iasi, Romania, 16–18 October 2014; pp. 693–698. [Google Scholar]

- Mahmoud, H.; Bacco, G.; Degano, M.; Bianchi, N.; Gerada, C. Synchronous Reluctance Motor Iron losses: Considering Machine Non-Linearity at MTPA, FW, and MTPV Operating Conditions. IEEE Trans. Eng. Convers. 2018, 33, 1402–1410. [Google Scholar] [CrossRef]

- Farhan, A.; Saleh, A.; Shaltout, A. High performance reluctance synchronous motor drive using field oriented control. In Proceedings of the 2013 5th International Conference on Modelling, Identification and Control (ICMIC), Cairo, Egypt, 31 August–2 September 2013; IEEE: Piscataway, NJ, USA, 2013; pp. 181–186. [Google Scholar]

- Moghaddam, R.R. Synchronous Reluctance Machine (SynRM) Design. Master’s Thesis, KTH Royal Institute of Technology, Stockholm, Sweden, 2007. [Google Scholar]

- Moghaddam, R.R.; Magnussen, F.; Sadarangani, C.; Lendenmann, H. New theoretical approach to the synchronous reluctance machine behavior and performance. In Proceedings of the 2008 18th International Conference on Electrical Machines, Vilamoura, Portugal, 6–9 September 2008; IEEE: Piscataway, NJ, USA, 2008; pp. 1–6. [Google Scholar]

- Armando, E.; Bojoi, R.I.; Guglielmi, P.; Pellegrino, G.; Pastorelli, M. Experimental Identification of the Magnetic Model of Synchronous Machines. IEEE Trans. Ind. Appl. 2013, 49, 2116–2125. [Google Scholar] [CrossRef]

- Wang, S.; Kang, J.; Degano, M.; Buticchi, G. A resolver-to-digital conversion method based on third-order rational fraction polynomial approximation for PMSM control. IEEE Trans. Ind. Electron. 2018, 66, 6383–6392. [Google Scholar] [CrossRef]

- Kwon, B.H.; Kim, T.W.; Youm, J.H. A novel SVM-based hysteresis current controller. IEEE Trans. Power Electron. 1998, 13, 297–307. [Google Scholar] [CrossRef]

- Pan, C.T.; Chang, T.Y. An improved hysteresis current controller for reducing switching frequency. IEEE Trans. Power Electron. 1994, 9, 97–104. [Google Scholar]

- Vahedi, H.; Sheikholeslami, A.; Tavakoli Bina, M.; Vahedi, M. Review and simulation of fixed and adaptive hysteresis current control considering switching losses and high-frequency harmonics. Adv. Power Electron. 2011, 2011, 397872. [Google Scholar] [CrossRef]

- Zhang, J.; Li, L.; Zhang, L.; Dorrell, D.G. Hysteresis band current controller based field-oriented control for an induction motor driven by a direct matrix converter. In Proceedings of the IECON 2017—43rd Annual Conference of the IEEE Industrial Electronics Society, Beijing, China, 29 October–1 November 2017; IEEE: Piscataway, NJ, USA, 2017; pp. 4633–4638. [Google Scholar]

- Agustin, C.A.; Yu, J.T.; Cheng, Y.S.; Lin, C.K.; Huang, H.Q.; Lai, Y.S. Model-free predictive current control for SynRM drives based on optimized modulation of triple-voltage-vector. IEEE Access 2021, 9, 130472–130483. [Google Scholar] [CrossRef]

- Lin, C.K.; Yu, J.T.; Huang, H.Q.; Wang, J.T.; Yu, H.C.; Lai, Y.S. A dual-voltage-vector model-free predictive current controller for synchronous reluctance motor drive systems. Energies 2018, 11, 1743. [Google Scholar] [CrossRef]

- IEC 60034-30-2:2016; Rotating Electrical Machines—Part 30-2: Efficiency Classes of Variable Speed AC Motors (IE-Code). IEC: Geneva, Switzerland, 2016. Available online: https://webstore.iec.ch/publication/30830 (accessed on 27 November 2019).

| Parameter | Value | Unit |

|---|---|---|

| Rated mechanic power | 90 | kW |

| Rated torque | 573 | Nm |

| Rated speed | 1500 | rpm |

| Rated phase current | 193 | A-RMS |

| Rated phase voltage | 210 | V-RMS |

| Stator resistance | 0.0152 | Ω |

| Pole pairs | 2 |

| Parameter | Value | Unit |

|---|---|---|

| PWM frequency | 5 | kHz |

| Dead time | 4 | µs |

| Input phase voltage | 220 | V-rms |

| DC-link capacitors | 8200 | µF |

| Item | DPWM2 | SVPWM |

|---|---|---|

| Current THD | 2.2% | 1.8% |

| Drive efficiency | 97.5% | 97% |

| Motor efficiency | 96.16% | 96.22% |

| System efficiency | 93.75% | 93.33% |

| Temperature (2 h run time) | 76 °C | 81 °C |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, S.; Prystupa, D.; Bao, Y.; Varvolik, V.; Buticchi, G.; Zhang, H.; Degano, M. Comprehensive Modulation Strategies for Synchronous Reluctance Motor Drives Used in Weak Grids. Energies 2024, 17, 615. https://doi.org/10.3390/en17030615

Wang S, Prystupa D, Bao Y, Varvolik V, Buticchi G, Zhang H, Degano M. Comprehensive Modulation Strategies for Synchronous Reluctance Motor Drives Used in Weak Grids. Energies. 2024; 17(3):615. https://doi.org/10.3390/en17030615

Chicago/Turabian StyleWang, Shuo, Dmytro Prystupa, Yuli Bao, Vasyl Varvolik, Giampaolo Buticchi, He Zhang, and Michele Degano. 2024. "Comprehensive Modulation Strategies for Synchronous Reluctance Motor Drives Used in Weak Grids" Energies 17, no. 3: 615. https://doi.org/10.3390/en17030615