Analysis of Circuit Simulation Considering Total Ionizing Dose Effects on FinFET and Nanowire FET

Abstract

:1. Introduction

2. Methodology of TID Simulation

2.1. Device Structure Design

2.2. Condition of TID Simulation

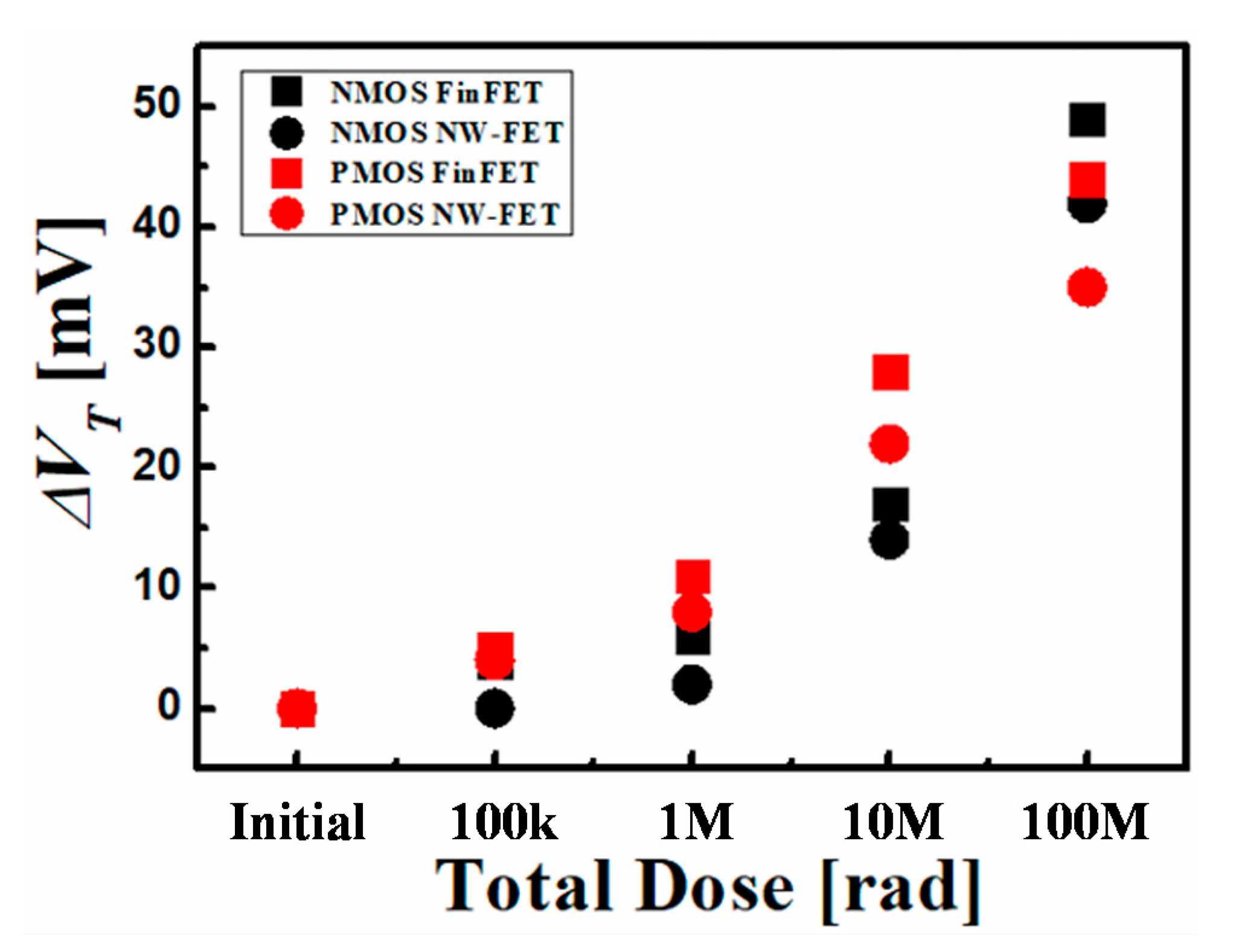

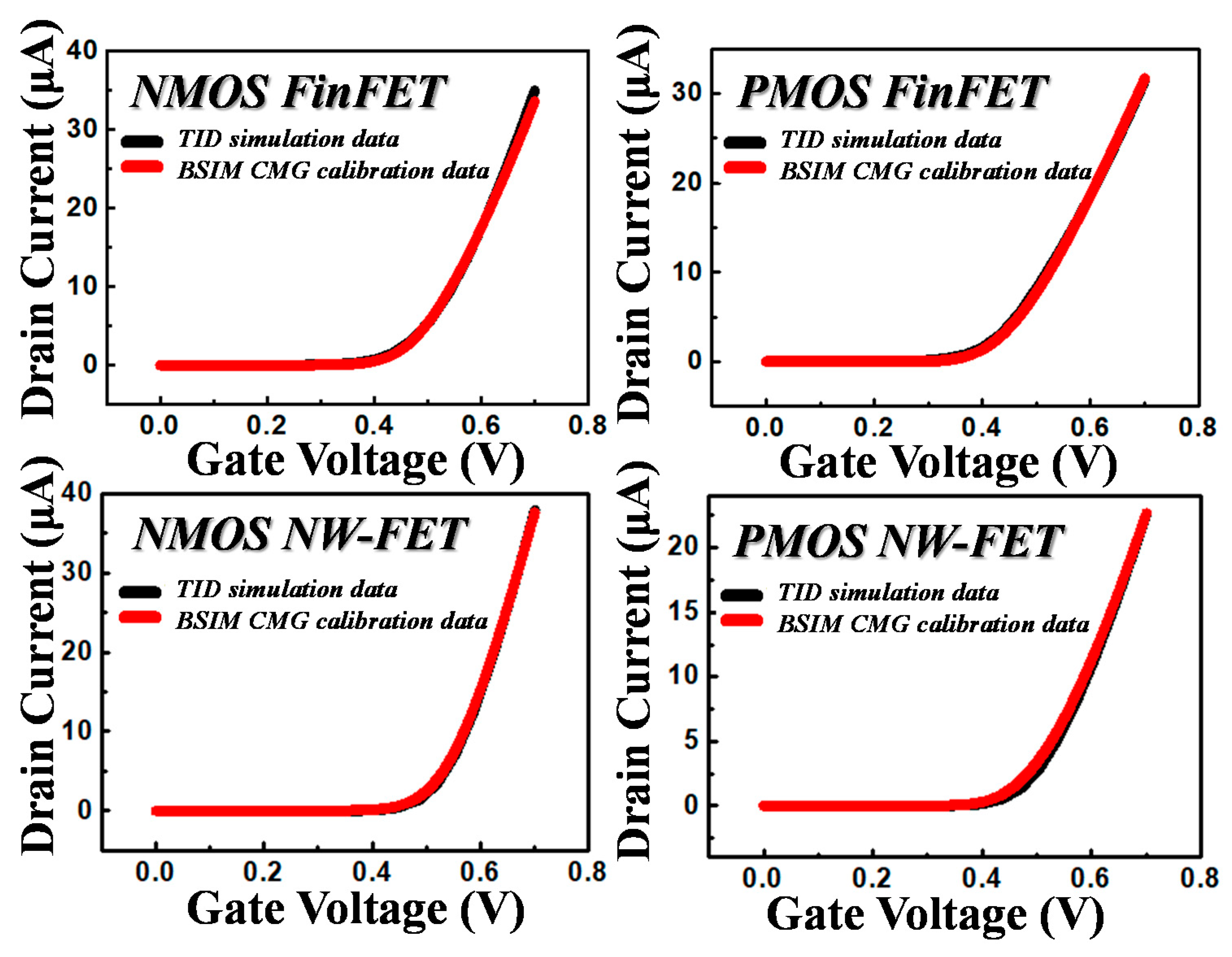

3. TID Simulation Results and Procedure of Compact Modeling with TID

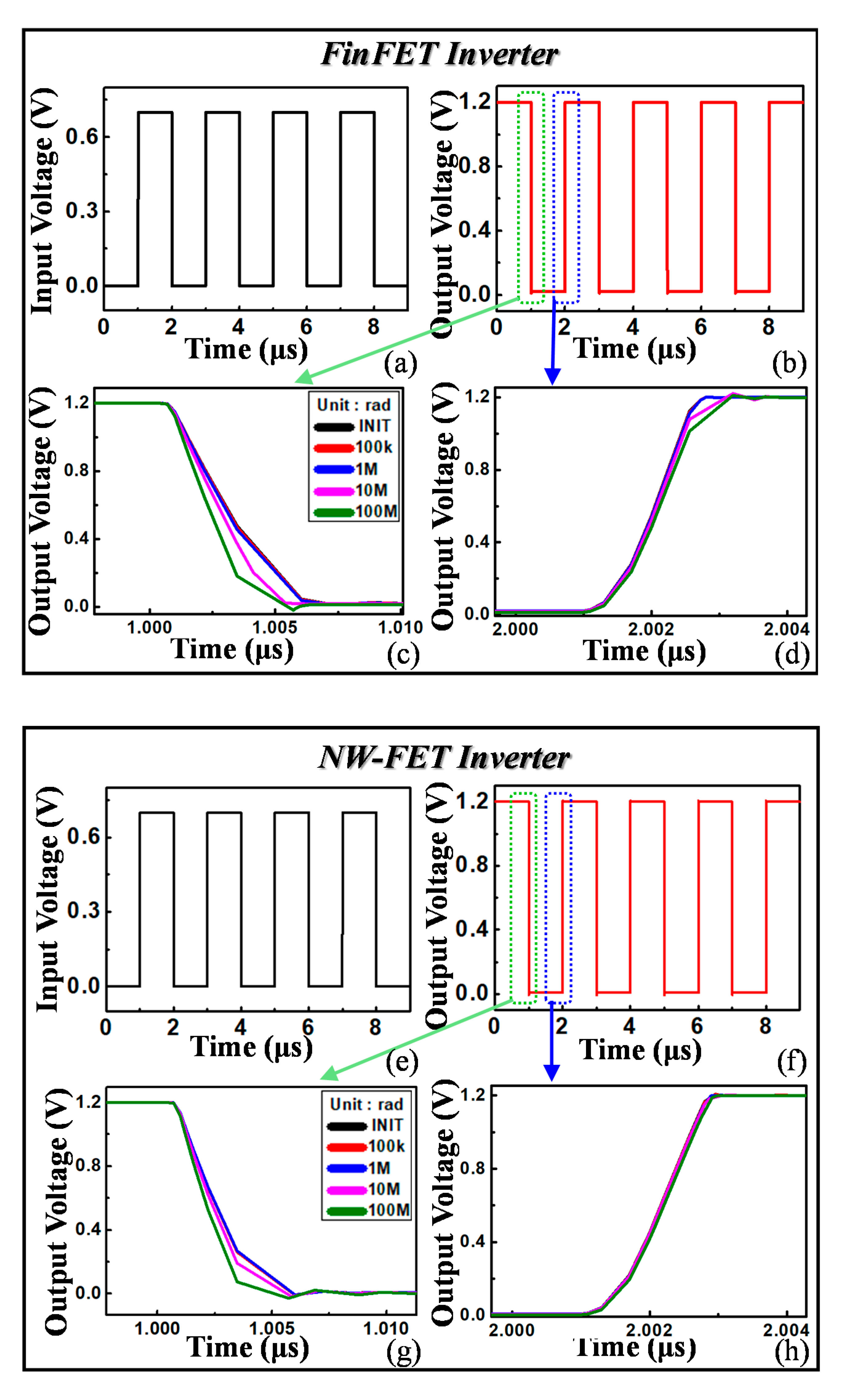

4. Circuit Characteristics with the TID Effect

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Leroux, P.; Van Koeckhoven, W.; Verbeeck, J.; Van Uffelen, M.; Esqué, S.; Ranz, R.; Damiani, C.; Hamilton, D. Design of a MGy radiation tolerant resolver-to-digital convertor IC for remotely operated maintenance in harsh environments. Fusion Eng. Des. 2014, 89, 2314–2319. [Google Scholar] [CrossRef]

- Haddad, N.F.; Kelly, A.T.; Lawrence, R.K.; Li, B.; Rodgers, J.C.; Ross, J.F.; Warren, K.M.; Weller, R.A.; Mendenhall, M.H.; Reed, R.A. Incremental enhancement of SEU hardened 90 nm CMOS memory cell. IEEE Trans. Nuclear Sci. 2011, 58, 975–980. [Google Scholar] [CrossRef]

- Clark, L.T.; Mohr, K.C.; Holbert, K.E.; Yao, X.; Knudsen, J.; Shah, H. Optimizing radiation hard by design SRAM cells. IEEE Trans. Nuclear Sci. 2007, 54, 2028–2036. [Google Scholar] [CrossRef]

- Gatti, U.; Calligaro, C.; Pikhay, E.; Roizin, Y. Radiation-hardened techniques for CMOS flash ADC. In Proceedings of the IEEE International Conference on Electronics Circuits and Systems, Marseille, France, 7–10 December 2014; pp. 1–4. [Google Scholar]

- Verbeeck, J.; Van Uffelen, M.; Steyaert, M.; Leroux, P. 17 bit 4.35 mW 1 kHz delta sigma ADC and 256-to-1 multiplexer for remote handling instrumentation equipment. Fusion Eng. Des. 2013, 88, 1942–1946. [Google Scholar] [CrossRef]

- Cao, Y.; Cock, W.D.; Steyaert, M.; Leroux, P. A 4.5 MGy TID-tolerant CMOS bandgap reference circuit using a dynamic base leakage compensation technique. IEEE Trans. Nuclear Sci. 2013, 60, 2819–2824. [Google Scholar] [CrossRef] [Green Version]

- Virmontois, C.; Goiffon, V.; Magnan, P.; Girard, S.; Inguimbert, C.; Petit, S.; Rolland, G.; Saint-Pé, O. Displacement damage effects due to neutron and proton irradiations on CMOS image sensors manufactured in deep submicron technology. IEEE Trans. Nuclear Sci. 2010, 57, 3101–3108. [Google Scholar] [CrossRef] [Green Version]

- Barnaby, H.J. Total-ionizing-dose effects in modern CMOS technologies. IEEE Trans. Nuclear Sci. 2006, 53, 3103–3121. [Google Scholar] [CrossRef]

- Martin, H.; Martin-Holgado, P.; Morilla, Y.; Entrena, L.; San-Millan, E. Total ionizing dose effects on a delay-based physical unclonable function implemented in FPGAs. Electronics 2018, 7, 163. [Google Scholar] [CrossRef] [Green Version]

- Oldham, T.R.; MeLean, F.B. Total ionizing dose effects in MOS oxides and devices. IEEE Trans. Nuclear Sci. 2003, 50, 483–499. [Google Scholar] [CrossRef] [Green Version]

- Gennady, Z. Static and dynamic oxide-trapped-charge-induced variability in nanoscale CMOS circuits. IEEE Trans. Electron Devices 2019, 66, 2483–2488. [Google Scholar]

- Brucker, G.J.; Gunten, O.V.; Stassinopoulos, E.G.; Shapiro, P.; August, L.S.; Jordan, T.M. Recovery of damage in rad-hard MOS devices during and after irradiation by electrons, protons, alphas, and gamma rays. IEEE Trans. Nuclear Sci. 1983, 30, 4157. [Google Scholar] [CrossRef]

- Johnston, A.H. Super recovery of total dose damage in MOS devices. IEEE Trans. Nuclear Sci. 1984, 31, 1427. [Google Scholar] [CrossRef]

- Colinge, J.-P. FinFETs and Other Multi-Gate Transistors; Springer: Berlin/Heidelberg, Germany, 2008; Volume 73. [Google Scholar]

- Nagy, D.; Indalecio, G.; García-Loureiro, A.J.; Elmessary, M.A.; Kalna, K.; Seoane, N. FinFET versus gate-all-around nanowire FET: Performance, scaling, and variability. IEEE J. Electron Devices Soc. 2018, 6, 332–340. [Google Scholar] [CrossRef]

- Pott, V.; Moselund, K.E.; Bouvet, D.; De Michielis, L.; Ionescu, A.M. Fabrication and characterization of gate-all-around silicon nanowires on bulk silicon. IEEE Trans. Nanotechnol. 2008, 7, 733–744. [Google Scholar] [CrossRef]

- Takato, H.; Sunouchi, K.; Okabe, N.; Nitayama, A.; Hieda, K.; Horiguchi, F.; Masuoka, F. Impact of surrounding gate transistor (SGT) for ultra-high-density LSI’s. IEEE Trans. Electron Devices 1991, 38, 573–578. [Google Scholar] [CrossRef]

- Zhai, Y.; Mathew, L.; Rao, R.; Palard, M.; Chopra, J.S.; Ekerdt, G.; Register, L.F.; Banerjee, S.K. High-performance vertical gate-all-around silicon nanowire FET with high-k/metal gate. IEEE Trans. Electron Devices 2014, 61, 3896–3900. [Google Scholar] [CrossRef]

- Song, J.Y.; Choi, W.Y.; Park, J.H.; Lee, J.D.; Park, B.G. Design optimization of gate-all-around (GAA) MOSFETs. IEEE Trans. Nanotechnol. 2006, 5, 186–191. [Google Scholar] [CrossRef]

- Bangsaruntip, S.; Cohen, G.M.; Majumdar, A.; Sleight, J.W. Universality of short-channel effects in undoped-body silicon nanowire MOSFETs. IEEE Electron Device Lett. 2010, 31, 903–905. [Google Scholar] [CrossRef]

- Ko, K.; Kang, M.; Jeon, J.; Shin, H. Compact model strategy of metal-gate work-function variation for ultrascaled FinFET and vertical GAA FETs. IEEE Trans. Electron Devices 2019, 66, 1613–1615. [Google Scholar] [CrossRef]

- Won, H.; Ham, I.; Jeong, Y.; Kang, M. Comparison of various factors affected TID tolerance in FinFET and nanowire FET. Appl. Sci. 2019, 9, 3163. [Google Scholar] [CrossRef] [Green Version]

- The International Technology Roadmap for Semiconductors; Semiconductor Industry Association: Washington, DC, USA, 2015.

- Victory Device User’s Manual, Silvaco Version. Available online: https://www.silvaco.com/products/tcad/device_simulation/victory_device/victory_device.html (accessed on 26 January 2015).

- Klaassen, D.B.M. Physical modeling bipolar device simulation. In Simulation of Semiconductor Devices and Processes; Fichtner, W., Aemmer, D., Eds.; Hartung-Gorre Verlag: Konstanz, Germany, 1991; Volume 4, pp. 23–43. [Google Scholar]

- Klaassen, D.B.M. A unified mobility model for device simulation—I. Model equations and concentration dependence. Solid-State Electron. 1992, 35, 953–959. [Google Scholar]

- Klaassen, D.B.M. A unified mobility model for device simulation—II. Temperature dependence of carrier mobility and lifetime. Solid-State Electron. 1992, 35, 961–967. [Google Scholar] [CrossRef]

- Klaassen, D.B.M.; Slotboom, J.W.; De Graaff, H.C. Unified apparent bandgap narrowing in n- and p-type silicon. Solid-State Electron. 1992, 35, 125–129. [Google Scholar] [CrossRef]

- Hurkx, G.A.M.; Klaassen, D.B.M.; Knuvers, M.P.G. A new recombination model for device simulation including tunneling. IEEE Trans. Electron Devices 1992, 39, 331–338. [Google Scholar] [CrossRef]

- Derek, K.; John, K. A simple trap–detrap model for accurate prediction of radiation induced threshold voltage shifts in radiation tolerant oxides for all static or time variant oxide fields. Solid-State Electron. 1994, 37, 153–158. [Google Scholar]

- Cho, J.W. Sensor and Communication Network Technology for Harsh Environments in the Nuclear Power Plant. In IAEA International Nuclear Information System; KAERI/AR-795/2008; International Atomic Energy Agency: Vienna, Austria, 2008; Volume 39, pp. 1–133. [Google Scholar]

- Gaillardin, M.; Marcandella, C.; Martinez, M.; Duhamel, O.; Lagutere, T.; Paillet, P.; Raine, M.; Richard, N.; Andrieu, F.; Barraud, S.; et al. Total ionizing dose response of multiple-gate nanowire field effect transistors. IEEE Trans. Nuclear Sci. 2017, 64, 2061–2068. [Google Scholar] [CrossRef]

- Riffaud, J.; Gaillardin, M.; Marcandella, C.; Martinez, M.; Paillet, P.; Duhamel, O.; Lagutere, T.; Raine, M.; Richard, N.; Andrieu, F.; et al. Investigations on the geometry effects and bias configuration on the TID response of NMOS SOI tri-gate nanowire field effect transistors. IEEE Trans. Nuclear Sci. 2017, 65, 39–45. [Google Scholar] [CrossRef]

- Nam, J.; Kang, C.Y.; Kim, K.P.; Yeo, H.; Lee, B.J.; Seo, S.; Yang, J.W. Influence of ionizing radiation on short-channel effects in low-doped multi-gate MOSFETs. IEEE Trans. Nuclear Sci. 2012, 59, 3021–3026. [Google Scholar]

| Design Factor | FinFET | NW-FET |

|---|---|---|

| Channel length | 12 nm | 12 nm |

| FinFET’s width and NW-FET’s diameter | 6 nm | 6 nm |

| Height (NW-FET total height) | 42 nm | 30 nm |

| Total area | 489.5 nm2 | 474.9 nm2 |

| S/D doping | 1 × 1021 cm−3 | 1 × 1021 cm−3 |

| Channel doping | 1 × 1016 cm−3 | 1 × 1016 cm−3 |

| Oxide area | 237.5 nm2 | 333.6 nm2 |

| EOT | 0.812 nm | 0.812 nm |

| VDD = 0.65 V | FinFET (VT) | NW-FET (VT) |

|---|---|---|

| NMOS | 0.33 V | 0.4 V |

| PMOS | 0.3 V | 0.38 V |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Won, H.; Kang, M. Analysis of Circuit Simulation Considering Total Ionizing Dose Effects on FinFET and Nanowire FET. Appl. Sci. 2021, 11, 894. https://doi.org/10.3390/app11030894

Won H, Kang M. Analysis of Circuit Simulation Considering Total Ionizing Dose Effects on FinFET and Nanowire FET. Applied Sciences. 2021; 11(3):894. https://doi.org/10.3390/app11030894

Chicago/Turabian StyleWon, Hyeonjae, and Myounggon Kang. 2021. "Analysis of Circuit Simulation Considering Total Ionizing Dose Effects on FinFET and Nanowire FET" Applied Sciences 11, no. 3: 894. https://doi.org/10.3390/app11030894