Analysis of Ruggedness of 4H-SiC Power MOSFETs with Various Doping Parameters

Abstract

:1. Introduction

2. Materials and Methods

2.1. Unclamped Inductive Switching (UIS) Circuit Test

2.2. Device Failure Mechanisms

2.3. Device Description

3. TCAD Simulation Results

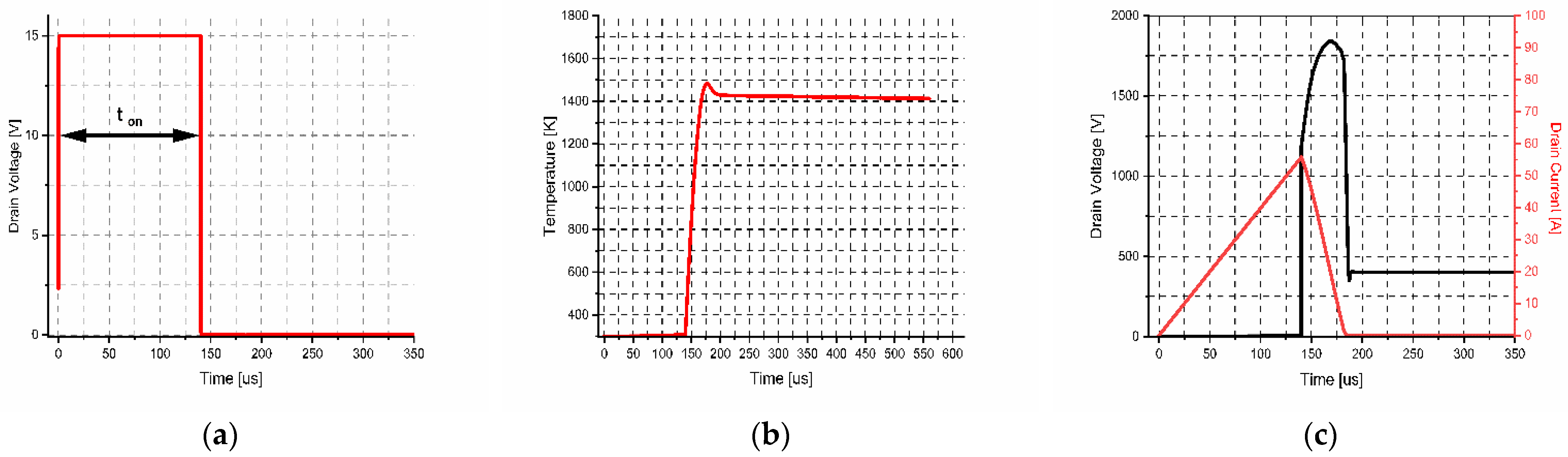

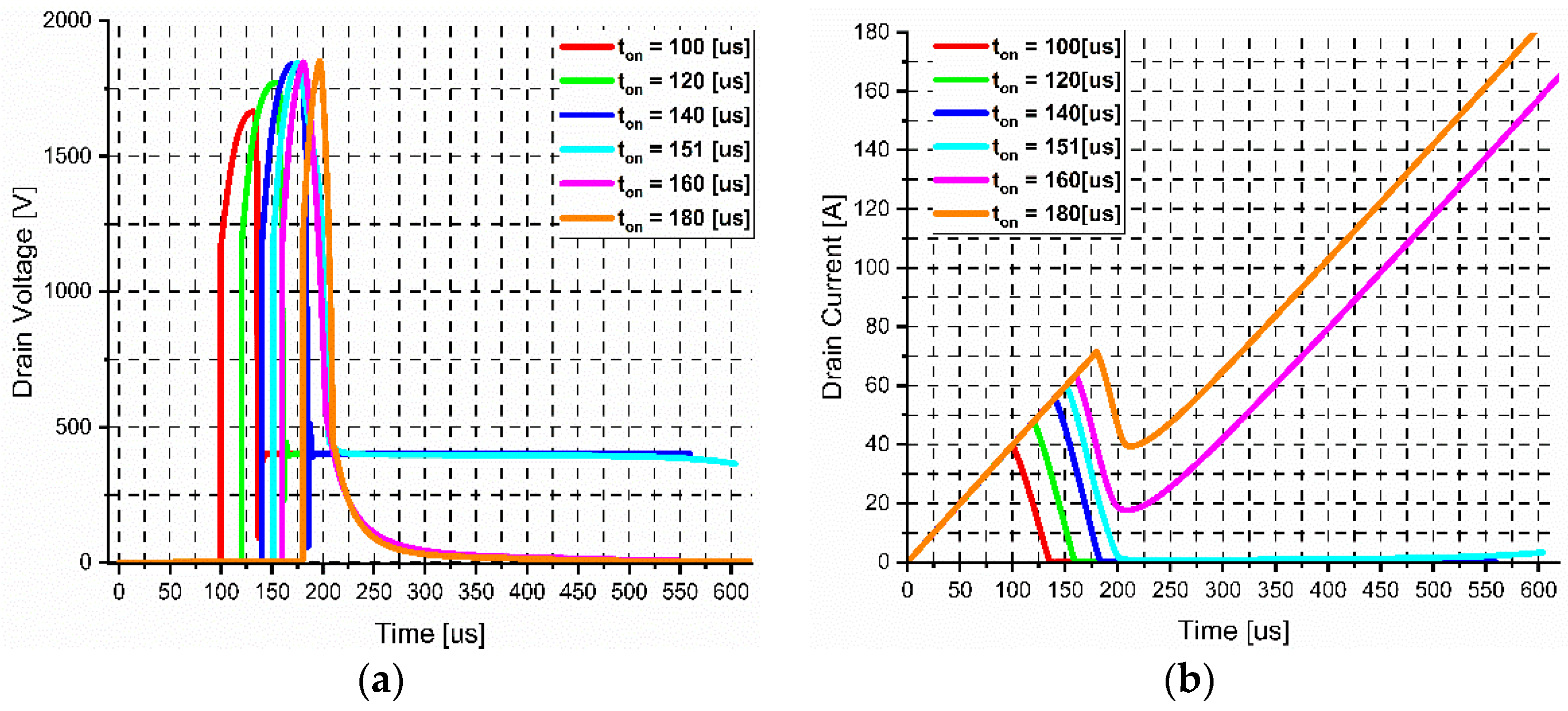

3.1. UIS Circuit Simulation for 4H-SiC Power MOSFET

3.2. UIS Circuit Simulation for Various Doping Concentrations

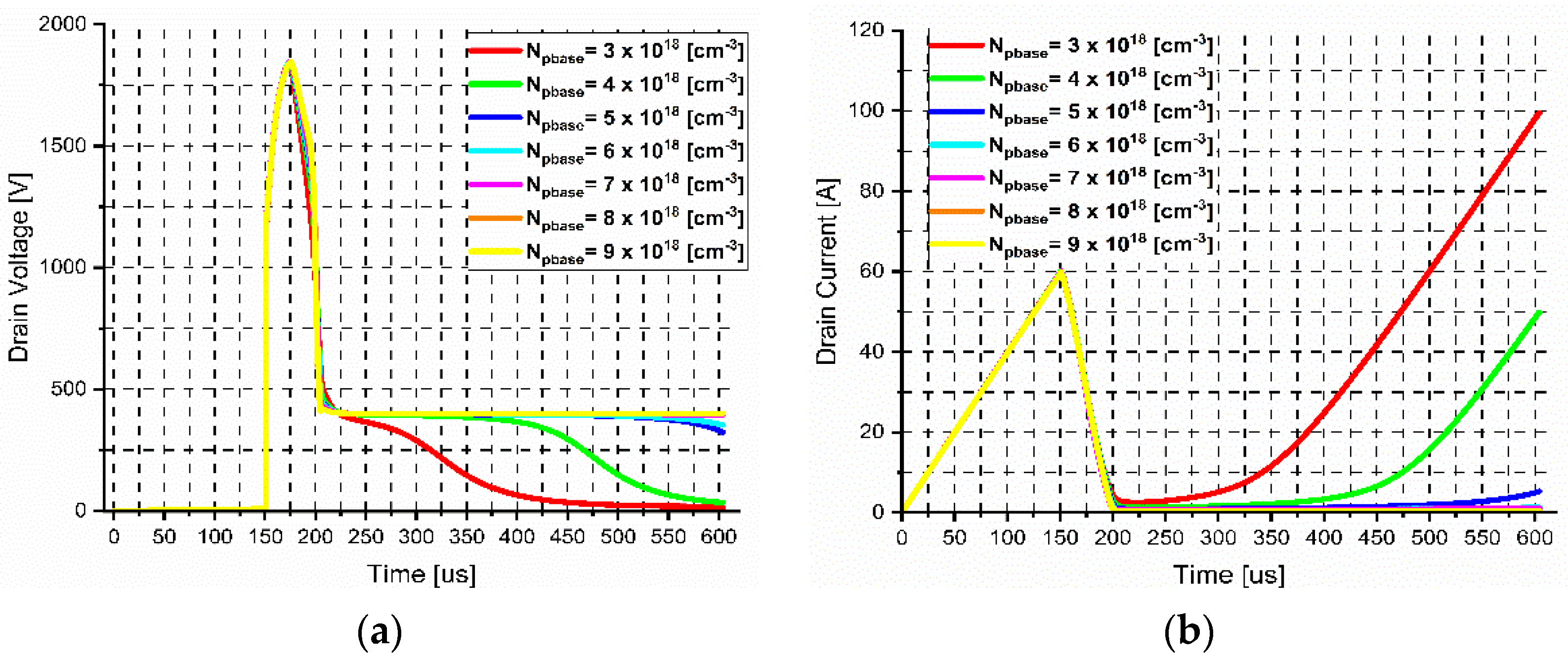

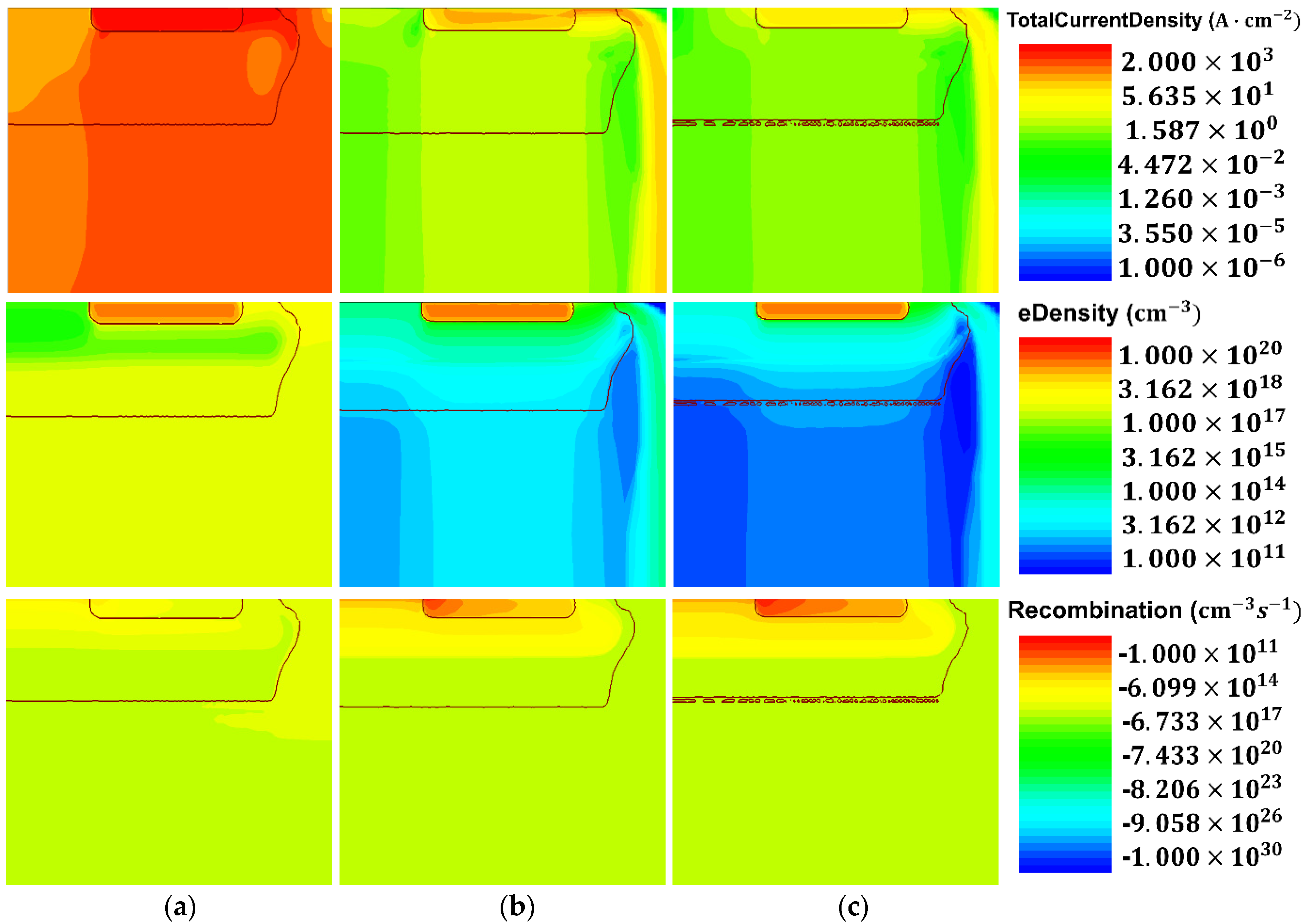

3.2.1. P-Base Region

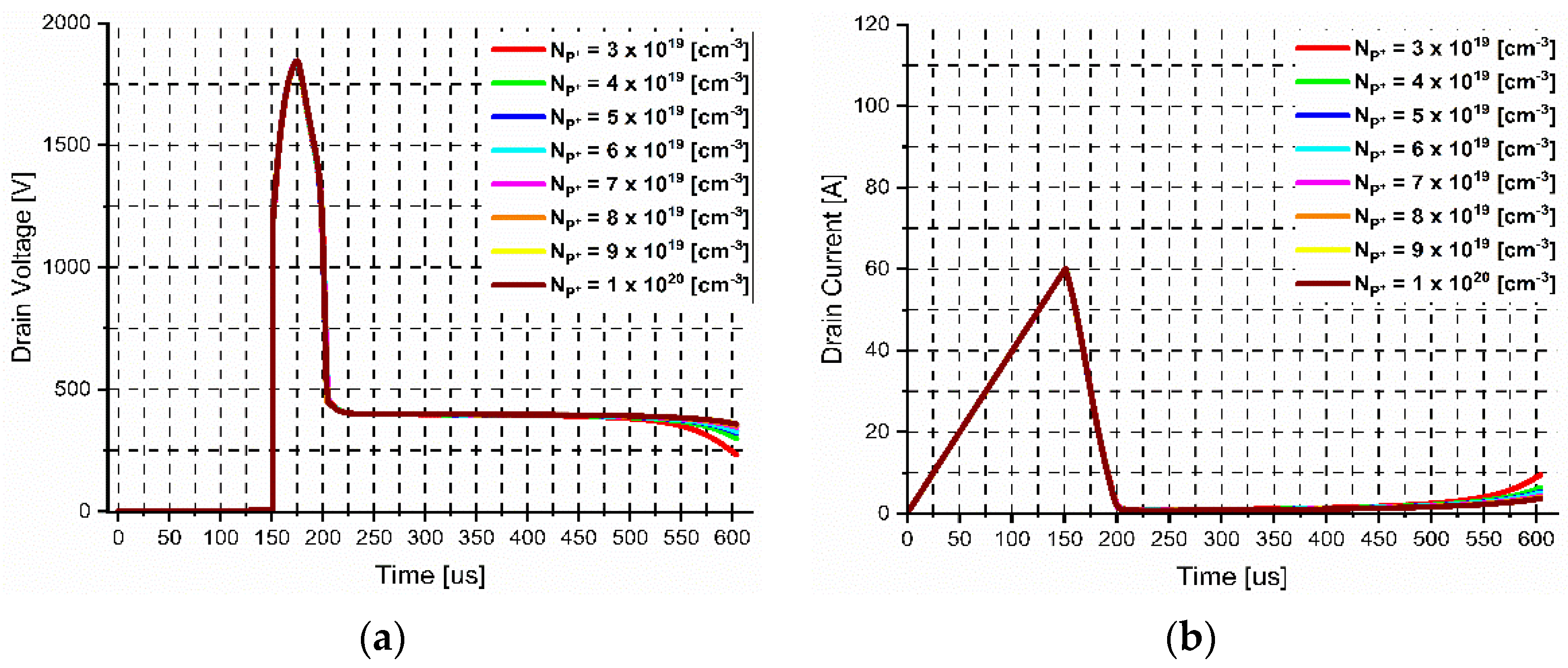

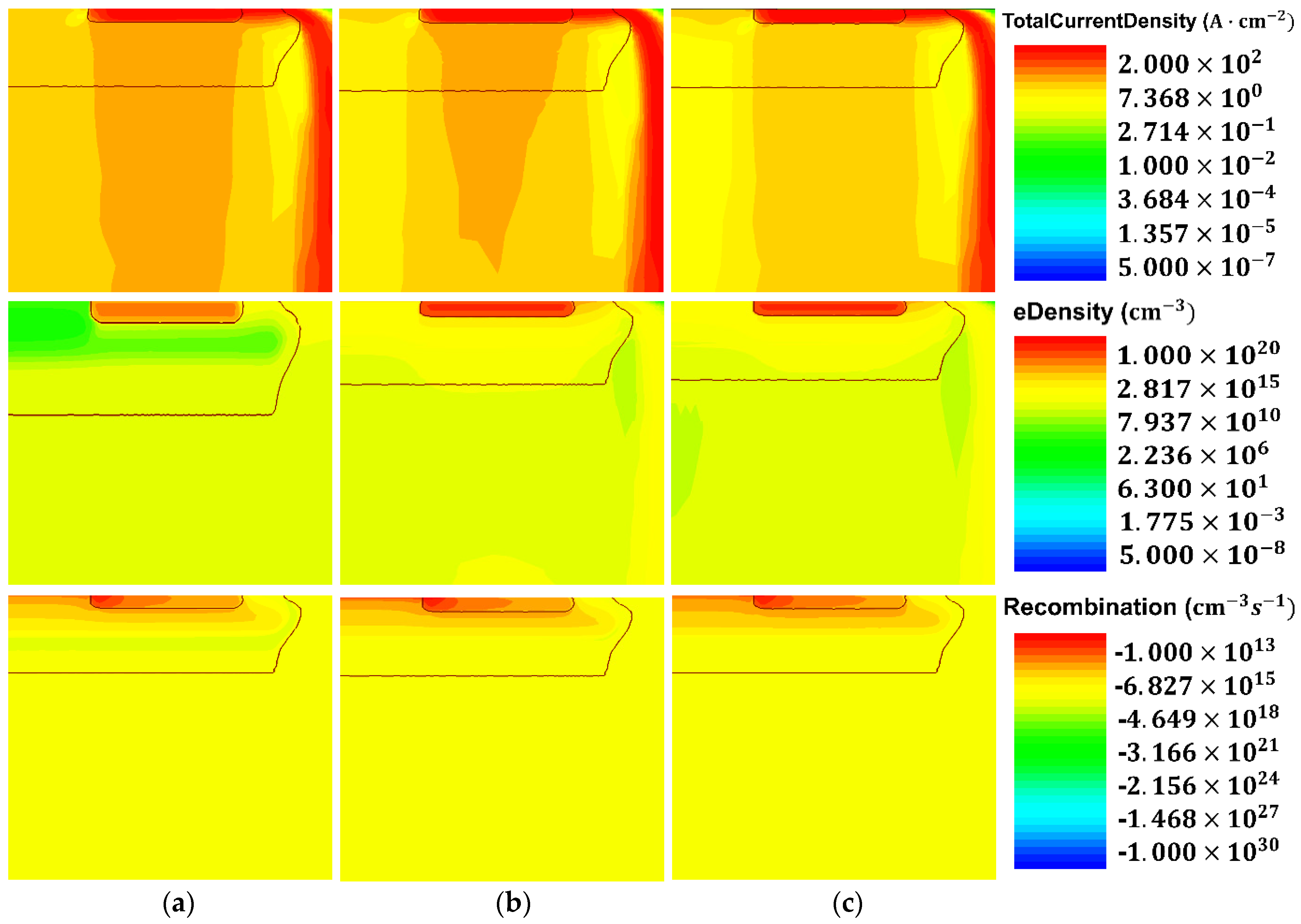

3.2.2. P+ Source Region

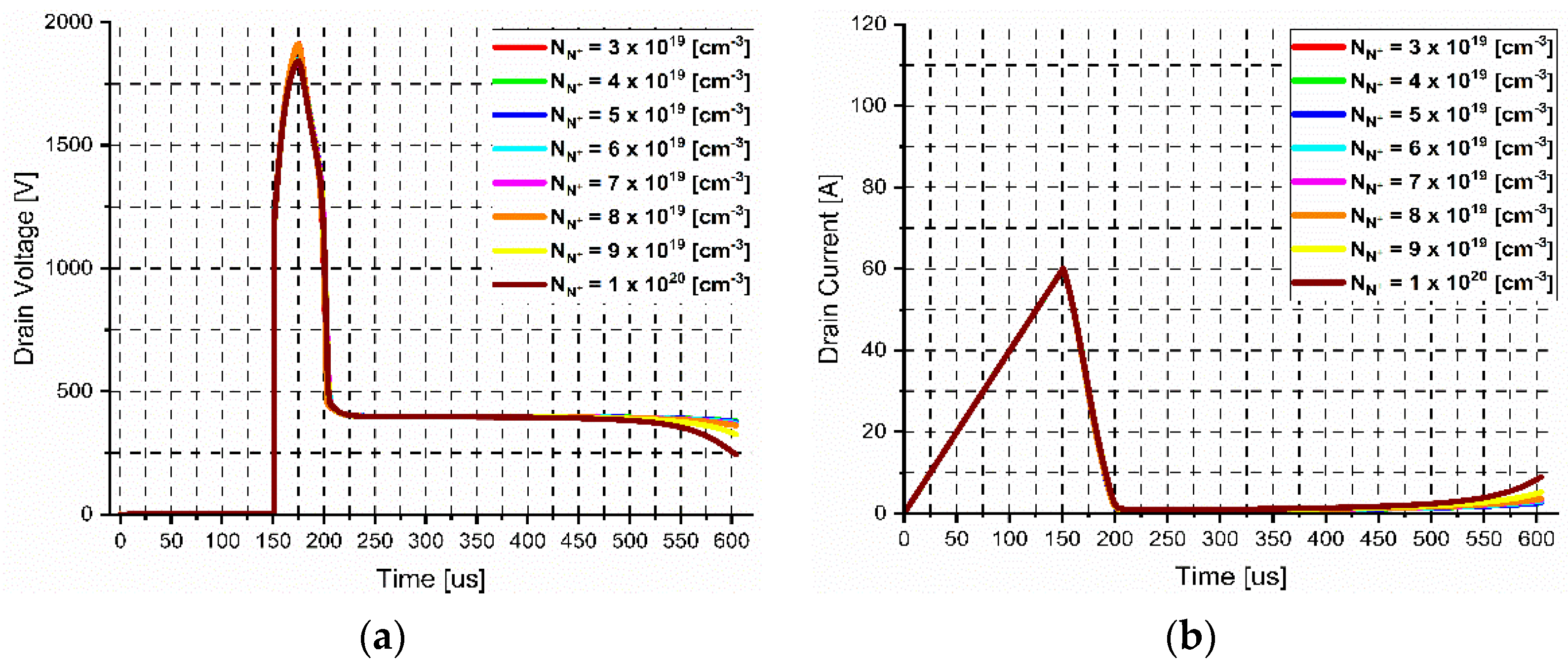

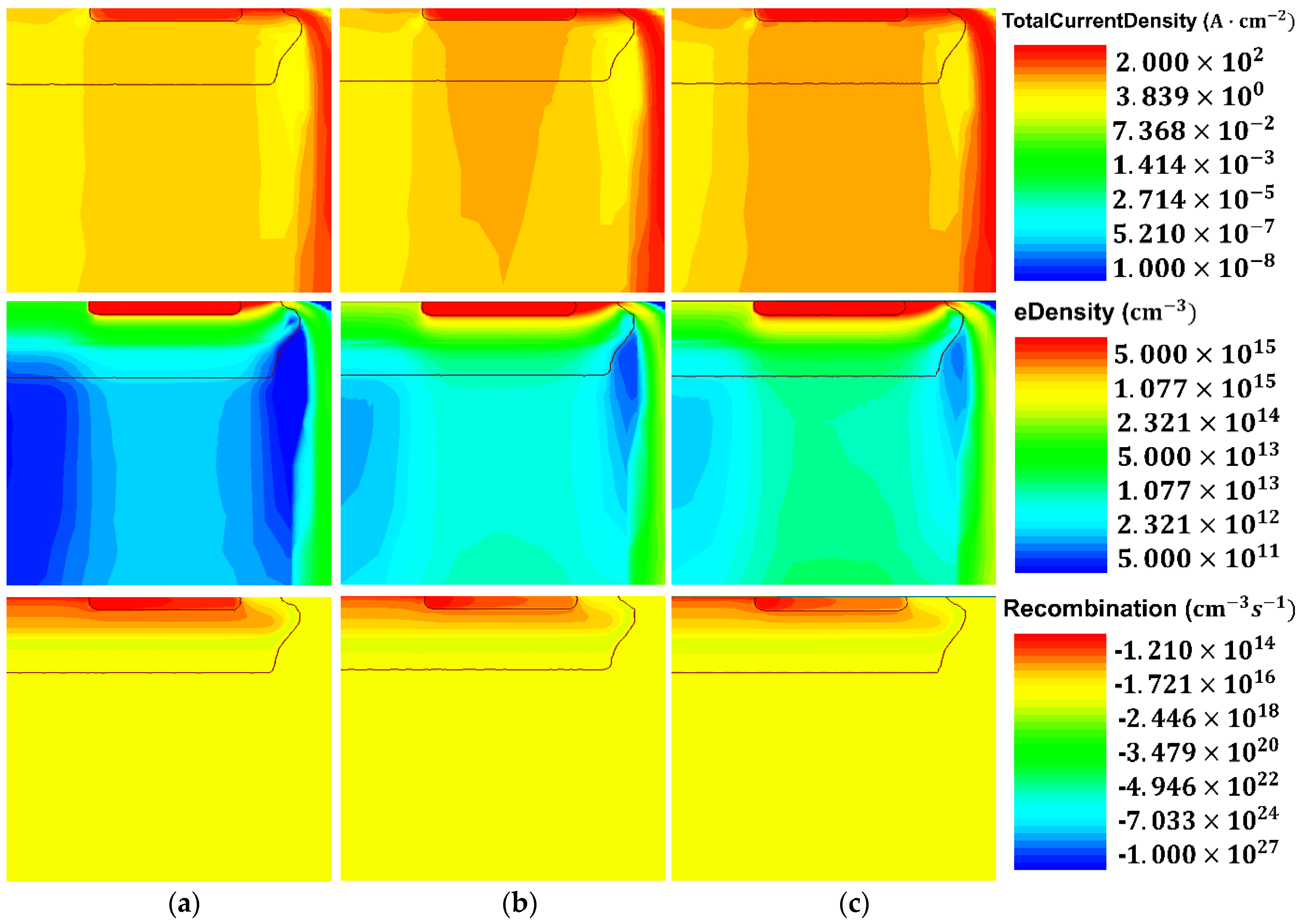

3.2.3. N+ Source Region

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Baliga, B.J. Fundamentals of Power Semiconductor Devices; Springer: Berlin/Heidelberg, Germany, 2019. [Google Scholar]

- Elasser, A.; Chow, T.P. Silicon carbide benefits and advantages for power electronics circuits and systems. Proc. IEEE 2002, 90, 969–986. [Google Scholar] [CrossRef]

- Kimoto, T.; Cooper, J.A. Fundamentals of Silicon Carbide Technology: Growth, Characterization, Devices and Applications; Wiley: Hoboken, NJ, USA, 2014. [Google Scholar]

- Baliga, B.J. Gallium Nitride and Silicon Carbide Power Devices; World Scientific Publishing: Singapore, 2017; pp. 347–349. [Google Scholar]

- She, X.; Huang, A.Q.; Lucia, O.; Ozpineci, B. Review of silicon carbide power devices and their applications. IEEE Trans. Ind. Electron. 2017, 64, 8193–8205. [Google Scholar] [CrossRef]

- Roccaforte, F.; Fiorenza, P.; Greco, G.; Nigro, R.L.; Giannazzo, F.; Iucolano, F.; Saggio, M. Emerging trends in wide band gap semiconductors (SiC and GaN) technology for power devices. Microelectron. Eng. 2018, 187–188, 66–77. [Google Scholar] [CrossRef]

- Bai, Z.; Tang, X.; Xie, S.; He, Y.; Yuan, H.; Song, Q.; Zhang, Y. Investigation on Single Pulse Avalanche Failure of 1200-V SiC MOSFETs via Optimized Thermoelectric Simulation. IEEE Trans. Electron Devices 2021, 6, 1168–1175. [Google Scholar] [CrossRef]

- Dchar, I.; Zolkos, M. Robustness of SiC MOSFET under Avalanche Conditions. In Proceedings of the Annual IEEE Conference on Applied Power Electronics Conference and Exposition (APEC), Orlando, FL, USA, 19–23 March 2017. [Google Scholar]

- Fischer, K.; Shenai, K. Dynamics of power MOSFET switching under unclamped inductive loading conditions. IEEE Trans. Electron Devices 1996, 43, 1007–1015. [Google Scholar] [CrossRef]

- Fayyaz, A.; Yang, L.; Castellazzi, A. Transient robustness testing of silicon carbide (SiC) power MOSFETs. In Proceedings of the Power Electronics and Applications (EPE), Lille, France, 2–6 September 2013; pp. 1–10. [Google Scholar] [CrossRef]

- Castellazzi, A.; Kartal, V.; Kraus, R.; Seliger, N.; Honsberg-Riedl, M.; Schmitt-Landsiedel, D. Hotspot Meaurements and Analysis of ElectroThermal Effects in Low-Voltage Power-MOSFET’s. Microelectron. Reliab. 2003, 43, 1877–1882. [Google Scholar] [CrossRef]

- Ren, N.; Wang, K.L.; Wu, J.; Xu, H.; Sheng, K. Failure mechanism analysis of SiC MOSFETs in unclamped inductive switching conditions. In Proceedings of the International Symposium on Power Semiconductor Devices and ICs (ISPSD), Shanghai, China, 19–23 May 2019; pp. 183–186. [Google Scholar] [CrossRef]

- Castellazzi, A.; Romano, G.; Urresti, J. UIS failure mechanism of SiC power MOSFETs. In Proceedings of the 4th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Fayetteville, AR, USA, 7–9 November 2016; IEEE Publications: New York, NY, USA, 2016. [Google Scholar]

- Lien, W.; Damrongplasit, N.; Paredes, J.H.; Senesky, D.G.; Liu, T.K.; Pisano, A.P. 4H-SiC N-Channel JFET for operation in high-temperature environments. IEEE J. Electron Devices Soc. 2014, 2, 164–167. [Google Scholar] [CrossRef]

- Touloukian, Y.S.; Buyco, E.H. Specific heat nonmetallic solids. In Thermophysical Properties Matter; IFI/Plenum: New York, NY, USA, 1970; Volume 5, pp. 448–450. [Google Scholar]

- An, J.; Namai, M.; Okamoto, D.; Yano, H.; Tadano, H.; Iwamuro, N. Investigation of Maximum Junction Temperature for 4H‐SiC MOSFET During Unclamped Inductive Switching Test. Electron. Commun. Jpn. 2018, 101, 24–31. [Google Scholar] [CrossRef]

- Kakarla, B.; Nida, S.; Mueting, J.; Ziemann, T.; Kovacevic-Badstuebner, I.; Grossner, U. Trade-off analysis of the p-base doping on ruggedness of SiC MOSFETs. Microelectron. Reliab. 2017, 76–77, 267–271. [Google Scholar] [CrossRef]

| Heat Capacity | |

|---|---|

| a | |

| b | |

| c | |

| d | |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jang, M.-S.; Jeong, J.-H.; Lee, H.-J. Analysis of Ruggedness of 4H-SiC Power MOSFETs with Various Doping Parameters. Appl. Sci. 2023, 13, 427. https://doi.org/10.3390/app13010427

Jang M-S, Jeong J-H, Lee H-J. Analysis of Ruggedness of 4H-SiC Power MOSFETs with Various Doping Parameters. Applied Sciences. 2023; 13(1):427. https://doi.org/10.3390/app13010427

Chicago/Turabian StyleJang, Min-Seok, Jee-Hun Jeong, and Ho-Jun Lee. 2023. "Analysis of Ruggedness of 4H-SiC Power MOSFETs with Various Doping Parameters" Applied Sciences 13, no. 1: 427. https://doi.org/10.3390/app13010427