Analysis and Compensation of Dead-Time Effect of a ZVT PWM Inverter Considering the Rise- and Fall-Times

Abstract

:1. Introduction

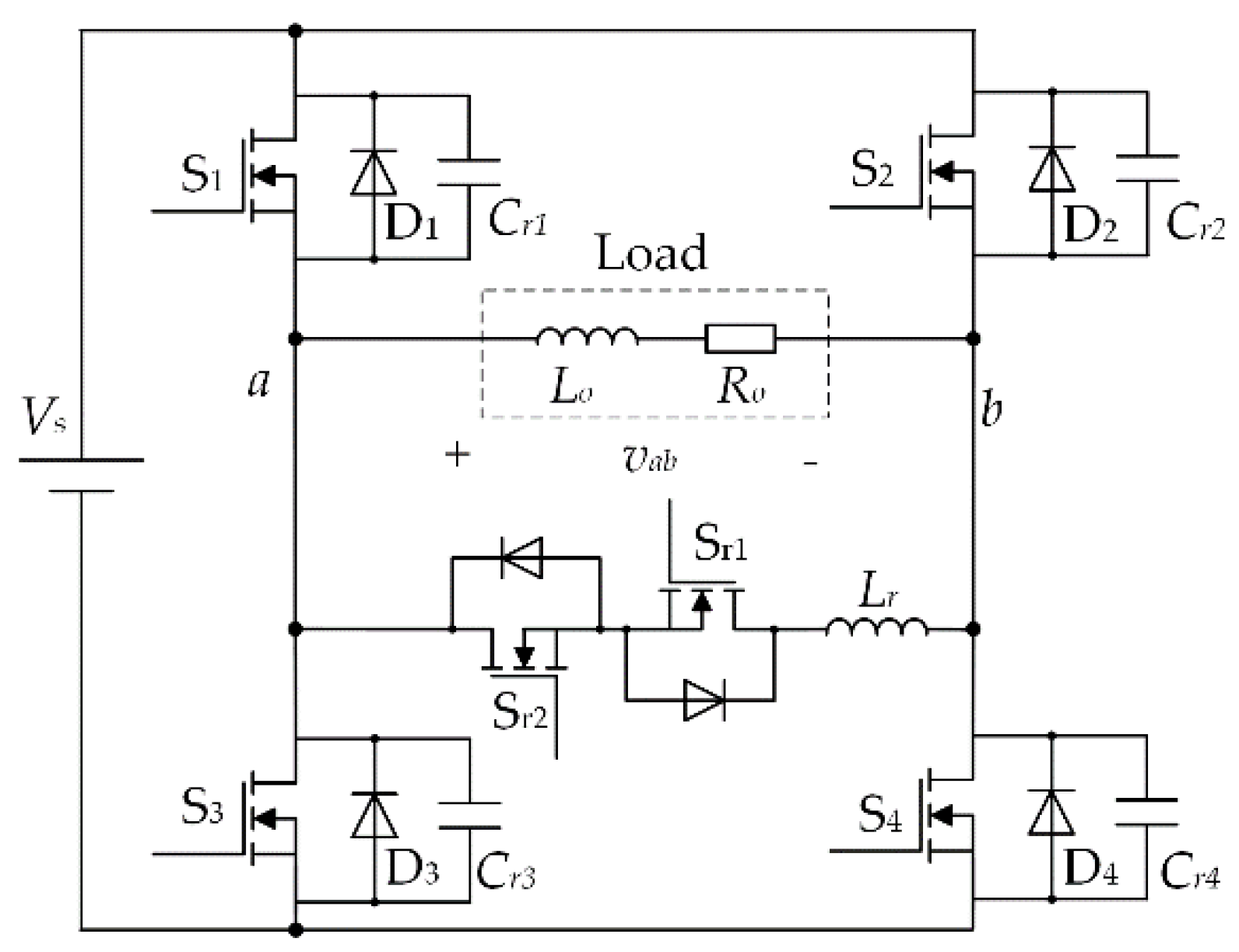

2. Dead-Time Effect of the Auxiliary Resonant Snubber Inverter (ARSI)

2.1. Principle

- (1)

- All components and devices are ideal;

- (2)

- The gate signals of the MOSFETs are ideal square-wave;

- (3)

- The output inductor Lo is high enough to be a constant current source.

2.1.1. Heavy Load Condition

2.1.2. Light Load Condition

2.2. Compared with the Hard-Switching Inverter

3. Compensation Method

4. Simulation and Experiment

5. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Leggate, D.; Kerkman, R. Pulse-based dead-time compensator for PWM voltage inverters. IEEE Trans. Ind. Electron. 1997, 38, 191–197. [Google Scholar] [CrossRef]

- Zhang, Z.; Xu, L. Dead-time compensation of inverters considering snubber and parasitic capacitance. IEEE Trans. Power Electron. 2014, 29, 3179–3187. [Google Scholar] [CrossRef]

- Mannen, T.; Fujita, H. Dead-time compensation method based on current ripple estimation. IEEE Trans. Power Electron. 2015, 30, 4016–4024. [Google Scholar] [CrossRef]

- Pellegrino, G.; Bojoi, R.I.; Guglielmi, P.; Cupertino, F. Accurate inverter error compensation and related self-commissioning scheme in sensorless induction motor drives. IEEE Trans. Ind. Appl. 2010, 46, 1970–1978. [Google Scholar] [CrossRef]

- Berkhout, M. A class D output stage with zero dead time. In Proceedings of the International Solid-State Circuits Conference, San Francisco, CA, USA, 13 February 2003; pp. 134–135.

- Lin, Y.K.; Lai, Y.S. Dead-time elimination of PWM-controlled inverter/converter without separate power sources for current polarity detection circuit. IEEE Trans. Ind. Electron. 2009, 56, 2121–2127. [Google Scholar]

- Chen, L.; Peng, F.Z. Dead-time elimination for voltage source inverters. IEEE Trans. Power Electron. 2008, 23, 574–580. [Google Scholar] [CrossRef]

- Ben-Brahim, L. On the compensation of dead time and zero-current crossing for a PWM-inverter-controlled AC servo drive. IEEE Trans. Ind. Electron. 2004, 51, 1113–1117. [Google Scholar] [CrossRef]

- Summers, T.J.; Betz, R.E. Dead-time issues in predictive current control. IEEE Trans. Ind. Appl. 2004, 40, 835–844. [Google Scholar] [CrossRef]

- Zhang, L.; Gu, B.; Dominic, J.; Chen, B.; Zheng, C.; Lai, J. A dead-time compensation method for parabolic current control with improved current tracking and enhanced stability range. IEEE Trans. Power Electron. 2015, 30, 3892–3902. [Google Scholar] [CrossRef]

- Guo, Z.; Kurokawa, F. A new hybrid current control scheme for deadtime compensation of inverters with LC filter. In Proceedings of the 13th European Conference on Power Power Electronics and Applications, Barcelona, Spain, 8–10 September 2009; pp. 1–10.

- Nielsen, K. Linearity and efficiency performance of switching audio power amplifier output stages-a fundamental analysis. In Proceedings of the 105th Audio Engineering Society Convention, San Francisco, CA, USA, 26–29 September 1998.

- McMurray, W. Resonant snubbers with auxiliary switches. IEEE Trans. Ind. Appl. 1993, 29, 355–362. [Google Scholar] [CrossRef]

- DeDonker, R.W.; Lyons, J.P. The auxiliary resonant commutated pole converter. In Proceedings of the Industry Applications Society Annual Meeting, Seattle, WA, USA, 7–12 October 1990; pp. 1228–1235.

- Lai, J.S. Resonant snubber-based soft-switching inverters for electric propulsion drives. IEEE Trans. Ind. Electron. 1997, 44, 71–80. [Google Scholar]

- Lai, J.S.; Young, R.W.; Ott, G.W.; McKeever, J.W.; Peng, F.Z. A delta-configured auxiliary resonant snubber inverter. IEEE Trans. Ind. Appl. 1996, 32, 518–525. [Google Scholar]

- Yuan, X.; Barbi, I. Analysis, designing, and experimentation of a transformer-assisted PWM zero-voltage switching pole inverter. IEEE Trans. Power Electron. 2000, 15, 950–950. [Google Scholar]

- Russi, J.L.; da Silva Martins, M.L.; Hey, H.L. Coupled-filter-inductor soft-switching techniques: Principles and topologies. IEEE Trans. Ind. Electron. 2008, 55, 3361–3373. [Google Scholar] [CrossRef]

- Yu, W.; Lai, J.; Park, S. An improved zero-voltage switching inverter using two coupled magnetics in one resonant pole. IEEE Trans. Power Electron. 2010, 25, 952–961. [Google Scholar]

- Beltrame, R.C.; Rakoski Zientarski, J.R.; da Silva Martins, M.L.; Pinheiro, J.R.; Hey, H.L. Simplified zero-voltage-rransition circuits applied to bidirectional poles: Concept and synthesis methodology. IEEE Trans. Power Electron. 2011, 26, 1765–1776. [Google Scholar] [CrossRef]

- Russi, J.L.; da Silva Martins, M.L.; Schuch, L.; Pinheiro, J.R.; Hey, H.L. Synthesis methodology for multipole ZVT converters. IEEE Trans. Ind. Electron. 2007, 54, 1783–1795. [Google Scholar] [CrossRef]

- Kou, B.; Zhang, H.; Jin, Y.; Zhang, H. An Improved Control Scheme for Single-Phase Auxiliary Resonant Snubber Inverter. In Proceedings of the IEEE 8th International Power Electronics and Motion Control Conference, Hefei, China, 22–26 May 2016; pp. 1259–1263.

| Type | io < –Ith | –Ith ≤ io ≤ Ith | io > Ith |

|---|---|---|---|

| S2 and S3 | AZVS (Sr2) | AZVS (Sr2) | NZVS |

| S1 and S4 | NZVS | AZVS (Sr1) | AZVS (Sr1) |

| Load Condition | Heavy Load | Light Load | Heavy Load |

| Parameter | Value |

|---|---|

| DC voltage Vs | 80 V |

| Switching frequency fs | 200 kHz |

| Dead-time tdead | 0.5 μs |

| Load | 3.7 Ω, 4.87 mH |

| Resonant inductor Lr | 4.4 μH |

| Resonant capacitor Cr | 4.7 nF |

| Threshold current Ith | 3 A |

| Iboost | 4 A |

© 2016 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC-BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, H.; Kou, B.; Zhang, L.; Zhang, H. Analysis and Compensation of Dead-Time Effect of a ZVT PWM Inverter Considering the Rise- and Fall-Times. Appl. Sci. 2016, 6, 344. https://doi.org/10.3390/app6110344

Zhang H, Kou B, Zhang L, Zhang H. Analysis and Compensation of Dead-Time Effect of a ZVT PWM Inverter Considering the Rise- and Fall-Times. Applied Sciences. 2016; 6(11):344. https://doi.org/10.3390/app6110344

Chicago/Turabian StyleZhang, Hailin, Baoquan Kou, Lu Zhang, and He Zhang. 2016. "Analysis and Compensation of Dead-Time Effect of a ZVT PWM Inverter Considering the Rise- and Fall-Times" Applied Sciences 6, no. 11: 344. https://doi.org/10.3390/app6110344