Multidimensional-DSP Beamformers Using the ROACH-2 FPGA Platform

Abstract

:1. Introduction

2. MD Frequency-Planar IIR Beam Filters

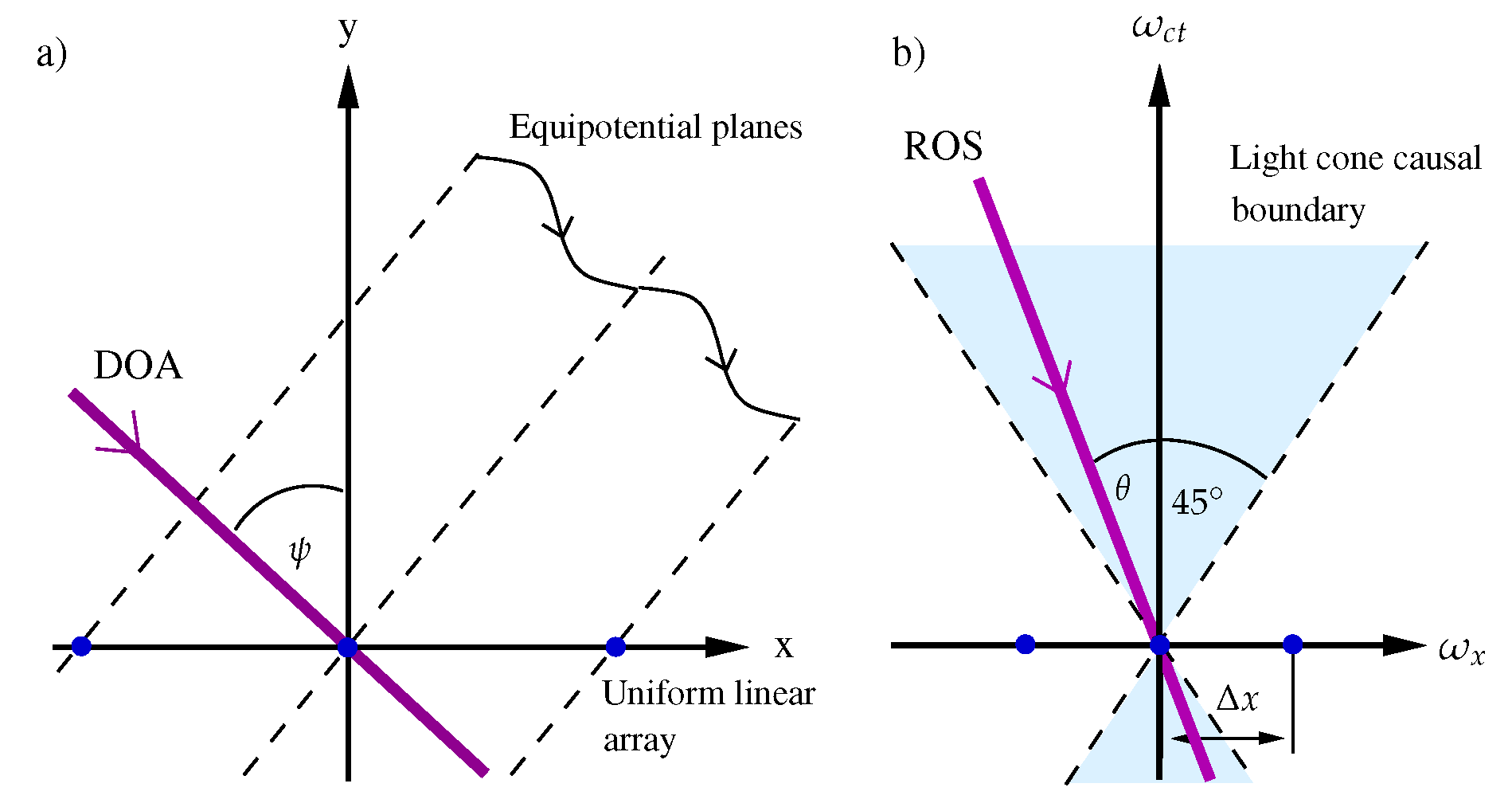

2.1. 2D Plane Wave Signals

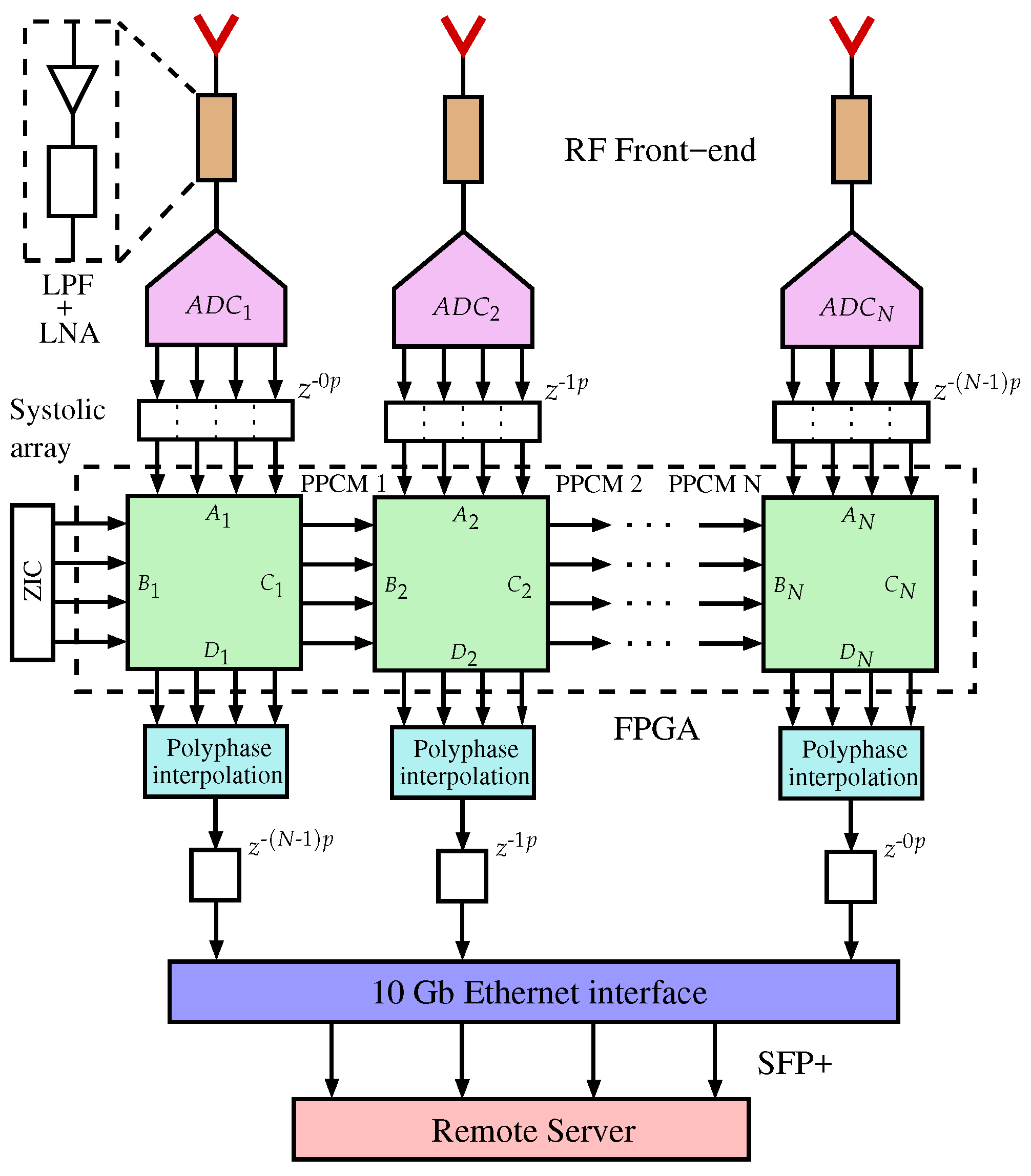

2.2. Defining 3D Plane Wave Signals from 2D Analogy

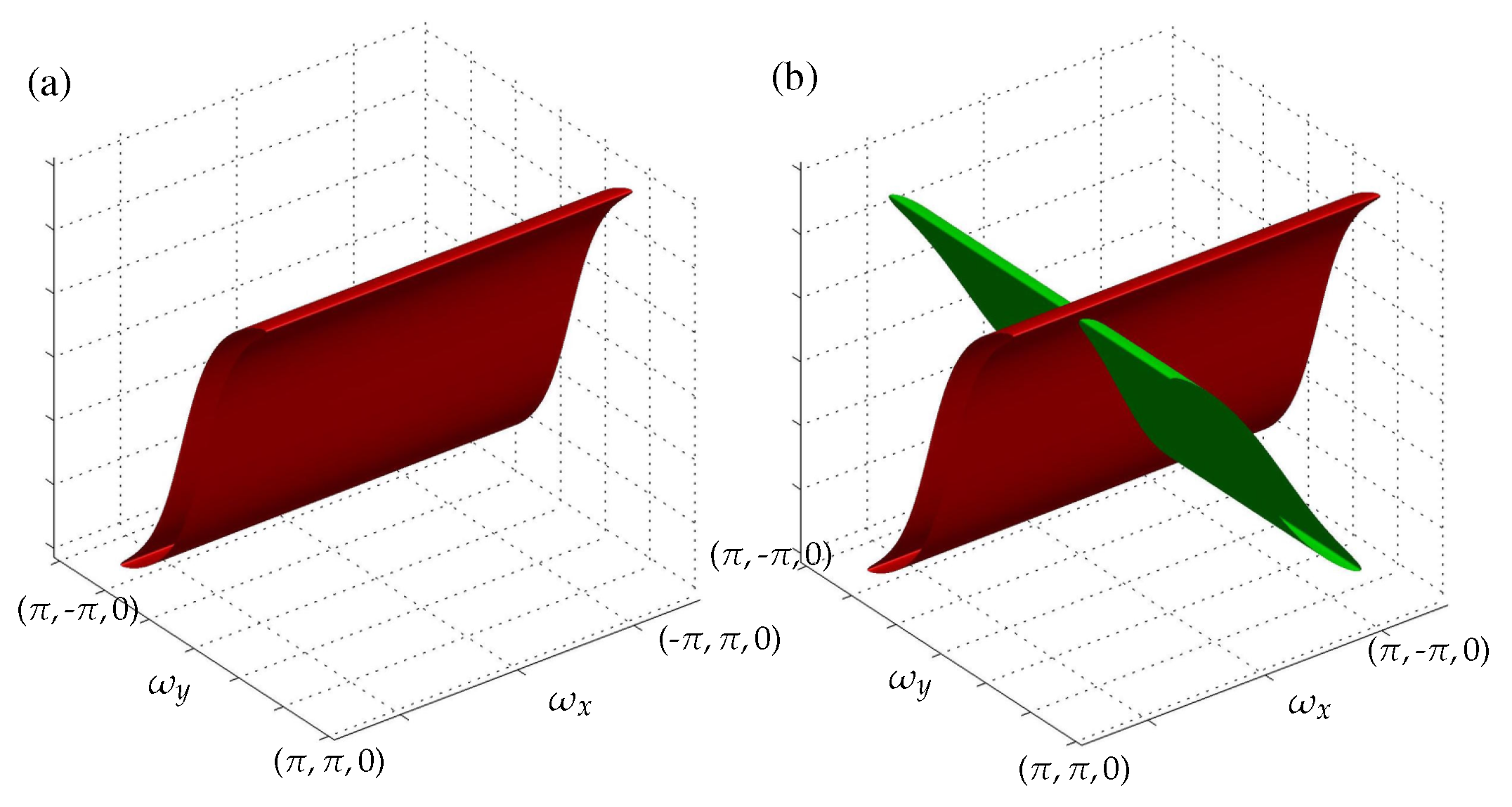

2.3. Network Resonant 2D IIR Digital Beam Filters

3. Polyphase Differential-Form Transfer-Function

4. Cascaded Beam Filters for 3D Beamformers

5. System Architecture

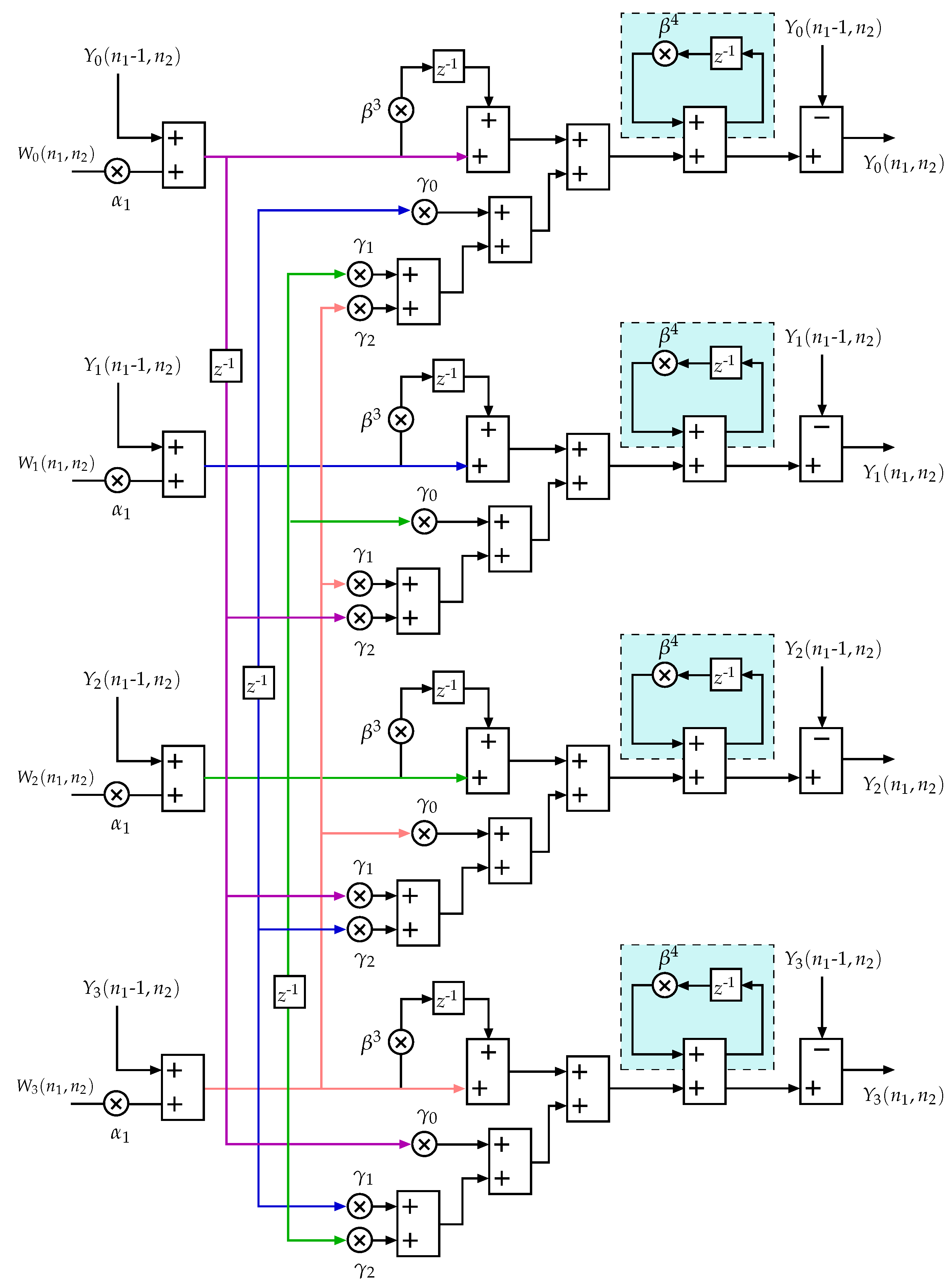

5.1. PPCM Block

6. Simulation and Results

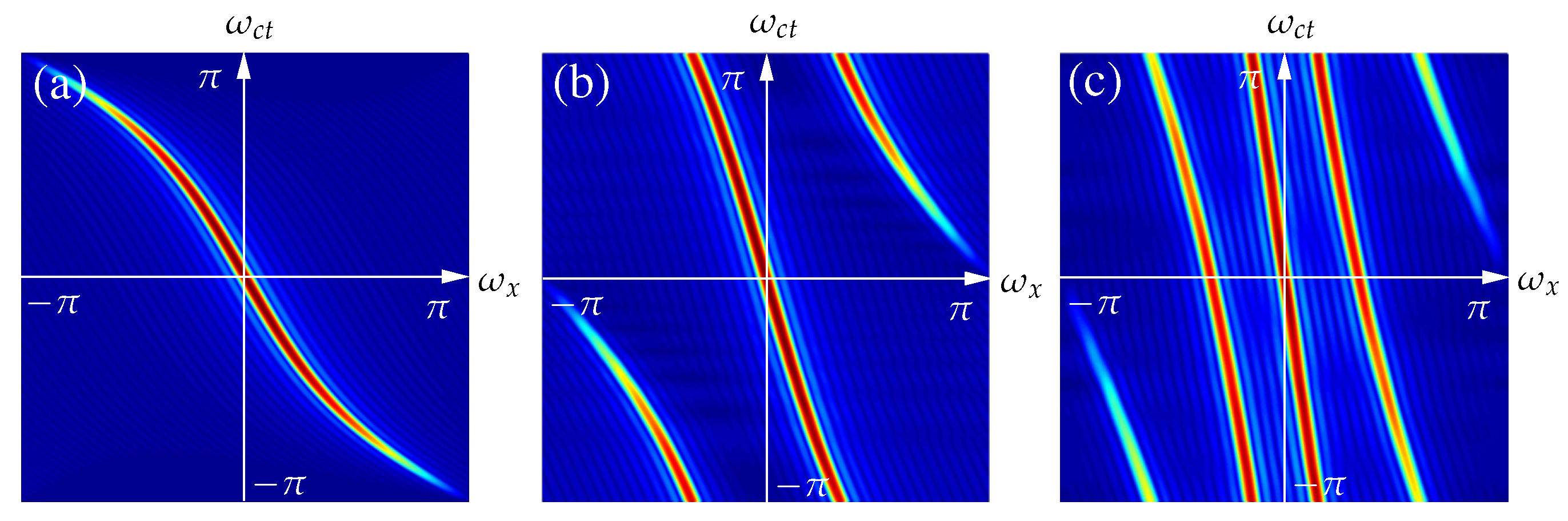

6.1. Filter Response of Four-Phase Polyphase 2D IIR Beam Filter

6.2. PPCM Digital Design Complexity

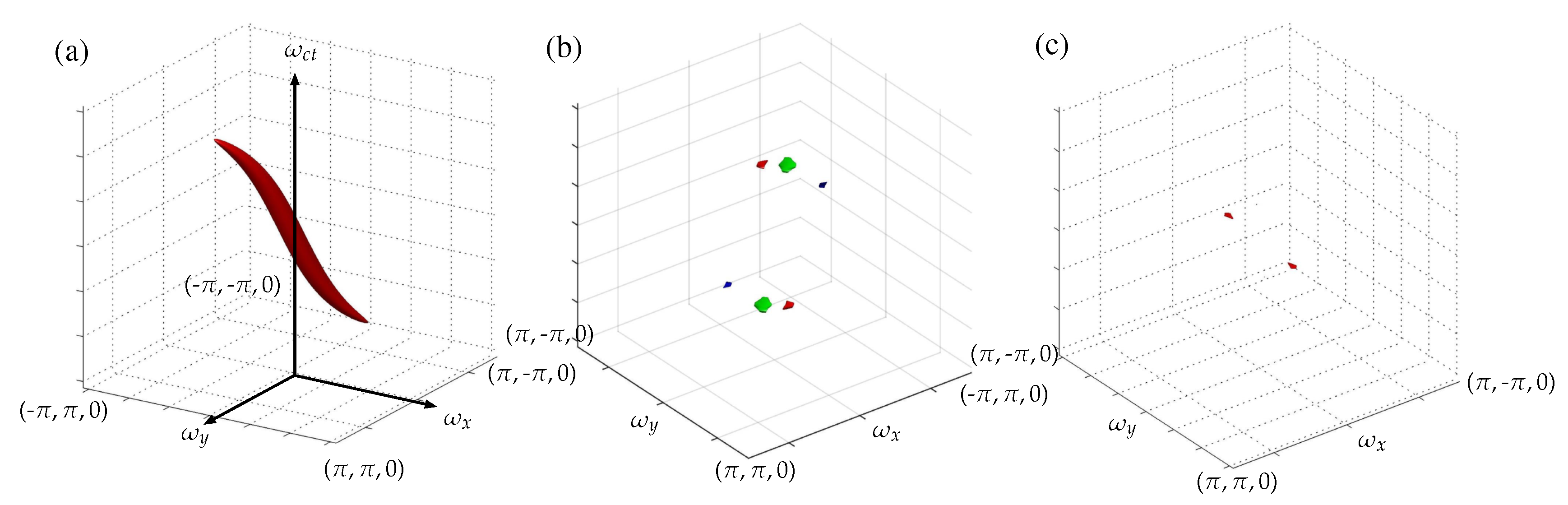

6.3. Frequency Response of the 3D IIR Beam Filter

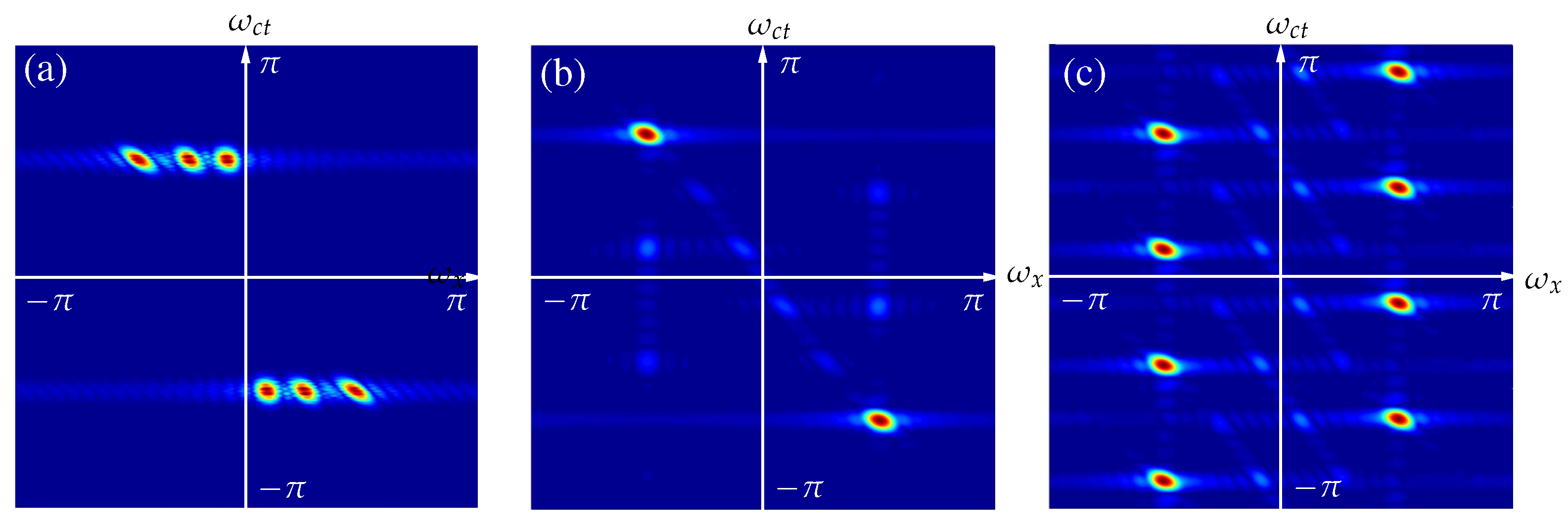

6.4. Directional Enhancement Properties

6.5. FPGA Implementation

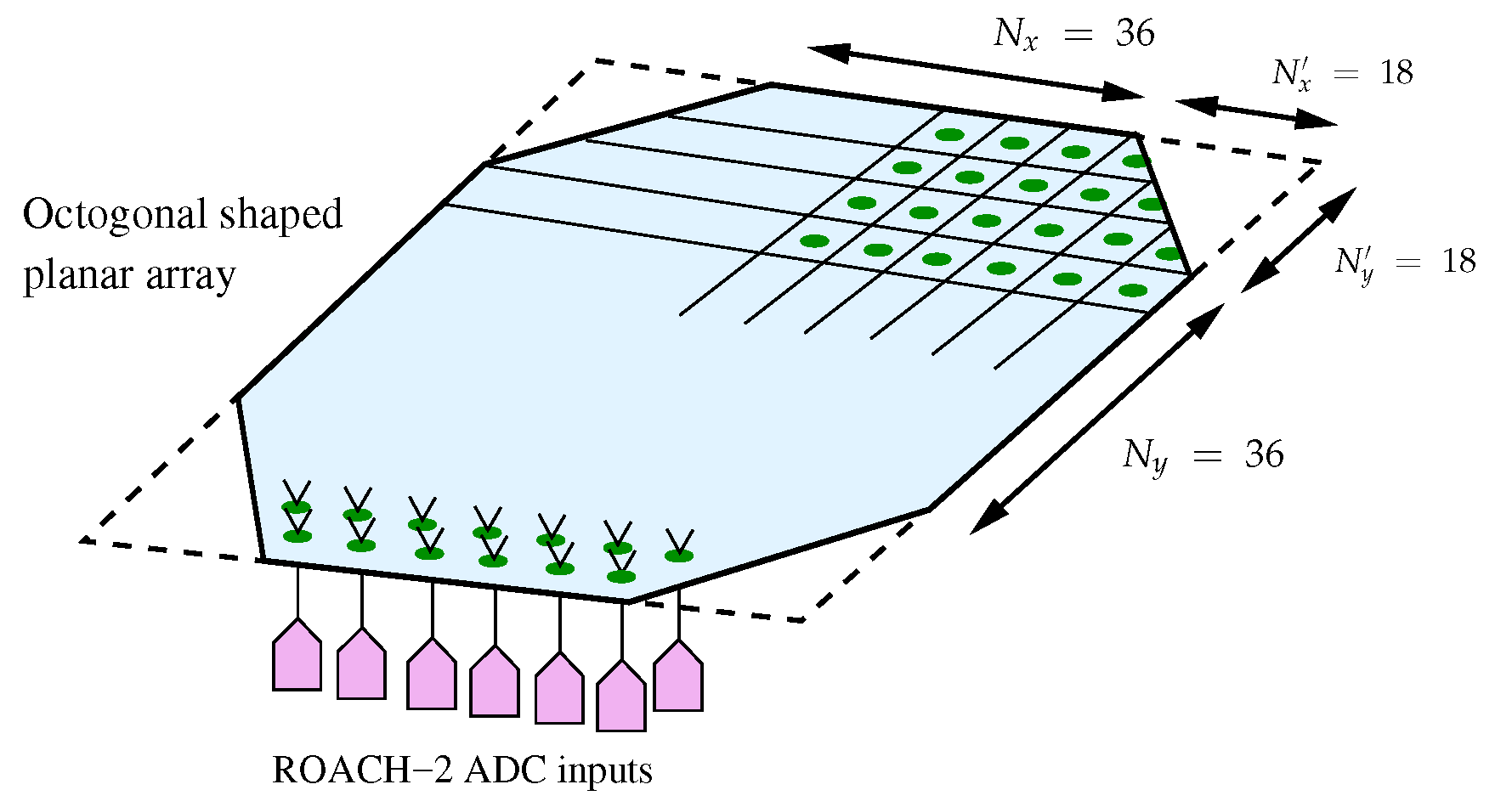

7. Military Radar Application Based on 3D IIR Beam Filters

8. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Kant, G.W.; Patel, P.D.; Wijnholds, S.J.; Ruiter, M.; van der Wal, E. EMBRACE: A Multi-Beam 20,000-Element Radio Astronomical Phased Array Antenna Demonstrator. IEEE Trans. Antennas Propag. 2011, 59, 1990–2003. [Google Scholar] [CrossRef]

- Krishnaswamy, H.; Hashemi, H. A 4-channel 4-beam 24-to-26 GHz spatio-temporal RAKE radar transceiver in 90nm CMOS for vehicular radar applications. In Proceedings of the 2010 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 7–11 February 2010; pp. 214–215. [Google Scholar]

- Madanayake, A.; Wijenayake, C.; Dansereau, D.G.; Gunaratne, T.K.; Bruton, L.T.; Williams, S.B. Multidimensional (MD) circuits and systems for emerging applications including cognitive radio, radio astronomy, robot vision and imaging. IEEE Circuits Syst. Mag. 2013, 13, 10–43. [Google Scholar] [CrossRef]

- Bosse, S.; Barth, S.; Torchinsky, S.; Da Silva, B. Beamformer ASIC in UHF-L band for the square kilometer array international project. In Proceedings of the IEEE European Microwave Integrated Circuits Conference (EuMIC), Paris, France, 27–28 September 2010; pp. 106–109. [Google Scholar]

- Elmer, M.; Jeffs, B.D.; Warnick, K.F.; Fisher, J.R.; Norrod, R.D. Beamformer Design Methods for Radio Astronomical Phased Array Feeds. IEEE Trans. Antennas Propag. 2012, 60, 903–914. [Google Scholar] [CrossRef]

- Li, T.; Rao, Y.; Niu, Z. Analysis and Design of UWB Vivaldi Antenna. In Proceedings of the International Symposium on Microwave, Antenna, Propagation and EMC Technologies for Wireless Communications, Hangzhou, China, 16–17 August 2007; pp. 579–581. [Google Scholar]

- Madanayake, A.; Wijenayake, C.; Belostotski, L.; Bruton, L.T. An overview of multi-dimensional RF signal processing for array receivers. In Proceedings of the Moratuwa Engineering Research Conference (MERCon), Moratuwa, Sri Lanka, 7–8 April 2015; pp. 255–259. [Google Scholar]

- Wijenayake, C.; Madanayake, A.; Bruton, L.T. Broadband Multiple Cone-Beam 3-D IIR Digital Filters Applied to Planar Dense Aperture Arrays. IEEE Trans. Antennas Propag. 2012, 60, 5136–5146. [Google Scholar] [CrossRef]

- Ghavami, M.; Kohno, R. Frequency selective broadband beamforming using 2D digital filters. In Proceedings of the IEEE 51st Vehicular Technology Conference Proceedings, Tokyo, Japan, 15–18 May 2000; Volume 3, pp. 2522–2526. [Google Scholar]

- Zhang, Y.; Bruton, L.T. Applications of 3D LCR networks in the design of 3D recursive filters for processing image sequences. IEEE Trans. Circuits Syst. Video Technol. 1994, 4, 369–382. [Google Scholar] [CrossRef]

- Agathoklis, P.; Bruton, L.T. Practical-BIBO stability of N-dimensional discrete systems. IEE Proc. G Electron. Circuits Syst. IET 1983, 130, 236–242. [Google Scholar] [CrossRef]

- Bruton, L.; Bartley, N. Three-dimensional image processing using the concept of network resonance. IEEE Trans. Circuits Syst. 1985, 32, 664–672. [Google Scholar] [CrossRef]

- Madanayake, A.; Hum, S.V.; Bruton, L.T. A Systolic Array 2-D IIR Broadband RF Beamformer. IEEE Trans. Circuits Syst. II Express Briefs 2008, 55, 1244–1248. [Google Scholar] [CrossRef]

- CASPER Group. Berkeley Wireless Research Center. The University of California, Berkeley. Available online: https://casper.berkeley.edu (accessed on 1 July 2017).

- Casper ROACH-2 Revision 2. CASPER Group Berkeley Wireless Research Center. The University of California, Berkeley. Available online: https://casper.berkeley.edu/wiki/ROACH2 (accessed on 1 July 2017).

- Seneviratne, V.; Madanayake, A.; Udayanga, N. Wideband 32-element 200 MHz 2-D IIR beam filters using ROACH-2 Virtex-6 sx475t FPGA. In Proceedings of the IEEE 9th International Workshop on Multidimensional (nD) Systems (nDS), Vila Real, Portugal, 7–9 September 2015; pp. 1–5. [Google Scholar]

- ADC16x250-8 RJ45 rev 1. Hittite Microwave Corporation. Available online: https://casper.berkeley.edu/wiki/ADC16x250-8 (accessed on 1 July 2017).

- ADC4x250-8. Hittite Microwave Corporation. Available online: https://casper.berkeley.edu/wiki/ADC4x250-8 (accessed on 1 July 2017).

- Seneviratne, V.; Madanayake, A.; Bruton, L.T. A 480MHz ROACH-2 FPGA realization of 2-phase 2D IIR beam filters for digital RF apertures. In Proceedings of the 2016 Moratuwa Engineering Research Conference (MERCon), Moratuwa, Sri Lanka, 5–6 April 2016; pp. 120–125. [Google Scholar]

- Vaidyanathan, P.P. Multirate digital filters, filter banks, polyphase networks, and applications: A tutorial. Proc. IEEE 1990, 78, 56–93. [Google Scholar] [CrossRef]

- Franca, J.; Petraglia, A.; Mitra, S.K. Multirate analog-digital systems for signal processing and conversion. Proc. IEEE 1997, 85, 242–262. [Google Scholar] [CrossRef]

- Vaidyanathan, P.P. Multirate Systems and Filter Banks; Pearson Education India: Delhi, India, 1993. [Google Scholar]

- Madanayake, A.; Gunaratne, T.K.; Bruton, L.T. Massively parallel systolic-array architectures for 2-D IIR polyphase space-time plane-wave beam digital filters. Int. J. Circuit Theory Appl. 2012, 40, 455–475. [Google Scholar] [CrossRef]

- Udayanga, N.; Madanayake, A.; Wijenayake, C.; Acosta, R. Applebaum adaptive array apertures with 2-D IIR space-time circuit-network resonant pre-filters. In Proceedings of the IEEE Radar Conference (RadarCon), Arlington, VA, USA, 10–15 May 2015; pp. 0611–0615. [Google Scholar]

- Roderick, J.; Krishnaswamy, H.; Newton, K.; Hashemi, H. Silicon-Based Ultra-Wideband Beam-Forming. IEEE J. Solid-State Circuits 2006, 41, 1726–1739. [Google Scholar] [CrossRef]

- Khademi, L. Reducing the Computational Complexity of FIR 2-D Fan and 3-D Cone Filters. Master’s Thesis, Department of Electrical and Computer Engineering University of Calgary, Calgary, AB, Canada, 2004. [Google Scholar]

- Madanayake, A.; Bruton, L.T. Radio-Frequency (RF) Beamforming Using Systolic FPGA-Based Two Dimensional (2D) IIR Space-Time Filters; INTECH Open Access Publisher: Rijeka, Croatia, 2010. [Google Scholar]

- Bruton, L.T.; Madanayake, A.; Wijenayake, C.; Maini, M. Continuous-Time Analog Two-Dimensional IIR Beam Filters. IEEE Trans. Circuits Syst. II Express Briefs 2012, 59, 419–423. [Google Scholar] [CrossRef]

- Madanayake, A.; Bruton, L.T. A Speed-Optimized Systolic Array Processor Architecture for Spatio-Temporal 2-D IIR Broadband Beam Filters. IEEE Trans. Circuits and Syst. I Regul. Pap. 2008, 55, 1953–1966. [Google Scholar] [CrossRef]

- Madanayake, A.; Bruton, L.T. Low-complexity distributed parallel processor for 2-D IIR broadband beam plane-wave filters. Can. J. Electr. Comput. Eng. 2007, 32, 123–131. [Google Scholar] [CrossRef]

- Madanayake, A.; Bruton, L.T. FPGA Prototyping of Spatio-temporal 2-D IIR Broadband Beam Plane-wave Filters. In Proceedings of the IEEE Asia Pacific Conference on Circuits and Systems, Singapore, 4–7 December 2006; pp. 542–545. [Google Scholar]

- Parhi, K.; Messerschmitt, D. Look-ahead computation: Improving iteration bound in linear recursions. In Proceedings of the IEEE International Conference on Acoustics, Speech, and Signal Processing, Dallas, TX, USA, 6–9 April 1987; Volume 12, pp. 1855–1858. [Google Scholar]

- Madanayake, A.; Gunaratne, T.K.; Bruton, L.T. Reducing the Multiplier-Complexity of Massively Parallel Polyphase 2-D IIR Broadband Beam Filters. Circuits Syst. Signal Proc. 2012, 31, 1229–1243. [Google Scholar] [CrossRef]

- Bruton, L.T. Three-dimensional cone filter banks. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 2003, 50, 208–216. [Google Scholar] [CrossRef]

- HMCAD1520 ADC Chip Datasheet. Hittite Microwave Corporation. Available online: http://www.analog.com/media/en/technical-documentation/data-sheets/hmcad1520.pdf (accessed on 1 July 2017).

- MSSGE Toolflow Setup. Available online: https://casper.berkeley.edu/wiki/MSSGE_Toolflow_Setup (accessed on 1 July 2017).

- Dranidis, D.V. Airborne Stealth in a Nutshell-part I. the Magazine of the Computer Harpoon Community. 2012. Available online: http://www.harpoonhq.com/waypoint/ (accessed on 1 February 2009).

- ADC1x5000-8. ev2 Semiconductors. Available online: https://casper.berkeley.edu/wiki/ADC1x5000-8 (accessed on 1 July 2017).

- KatADC (ADC08D1520). Texas Instruments Inc. Available online: https://casper.berkeley.edu/wiki/KatADC (accessed on 1 July 2017).

- SKA Aperture Arrays. SKA Organization. Available online: https://www.skatelescope.org/aperture-arrays/ (accessed on 1 July 2017).

- Hansen, R.C. Phased Array Antennas; John Wiley & Sons: Hoboken, NJ, USA, 2009; Volume 213. [Google Scholar]

- Schelkunoff, S.A. A mathematical theory of linear arrays. Bell Labs Tech. J. 1943, 22, 80–107. [Google Scholar] [CrossRef]

- Balanis, C.A. Antenna Theory: Analysis and Design; John Wiley & Sons: Hoboken, NJ, USA, 2016. [Google Scholar]

| M-Phases | Multipliers (DRF) | Multipliers (DFF) | Relative Reduction | Frame Rate |

|---|---|---|---|---|

| 1 | 3 | 2 | 33% | |

| 2 | 10 | 8 | 20% | |

| 3 | 21 | 15 | 28.6% | |

| 4 | 36 | 24 | 33.3% |

| Resources | 16-Bits | 32-Bits |

|---|---|---|

| Slice registers | 13,957 | 28,167 |

| Slice LUTs | 30,132 | 69,220 |

| Occupied slices | 9586 | 21,565 |

| LUT-FF pairs | 9089 | 11,005 |

| () | 1.137 | 1.169 |

| Max. frequency () | 879.51 | 855.43 |

| ADC Board | ADC Inputs | Polyphase Freq., (GHz) | Sampling Freq., (GHz) | Operating Freq., (GHz) | Antenna Space, (mm) |

|---|---|---|---|---|---|

| ADC16x250-8 | 4 | 0.96 | 3.84 | 1.98 | 75.76 |

| Kat-7 ADC | 2 | 1.5 | 6 | 3.00 | 50 |

| ADC1x5000-8 | 2 | 2.5 | 10 | 5.00 | 30 |

| ADC Board | Total No. of ROACH-2 Boards | Array Size (m) |

|---|---|---|

| ADC16x250-8 | 1032 | |

| Kat-7 ADC | 1829 | |

| ADC1x5000-8 | 2286 |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Seneviratne, V.; Madanayake, A.; Bruton, L.T. Multidimensional-DSP Beamformers Using the ROACH-2 FPGA Platform. Electronics 2017, 6, 49. https://doi.org/10.3390/electronics6030049

Seneviratne V, Madanayake A, Bruton LT. Multidimensional-DSP Beamformers Using the ROACH-2 FPGA Platform. Electronics. 2017; 6(3):49. https://doi.org/10.3390/electronics6030049

Chicago/Turabian StyleSeneviratne, Vishwa, Arjuna Madanayake, and Len T. Bruton. 2017. "Multidimensional-DSP Beamformers Using the ROACH-2 FPGA Platform" Electronics 6, no. 3: 49. https://doi.org/10.3390/electronics6030049