Effects of Gate-Length Scaling on Microwave MOSFET Performance

Abstract

:1. Introduction

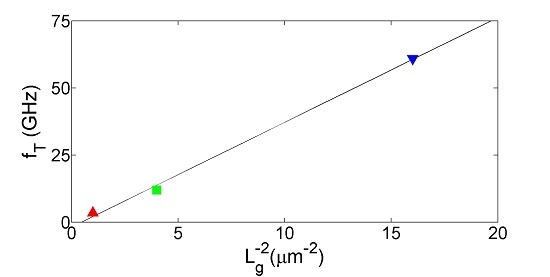

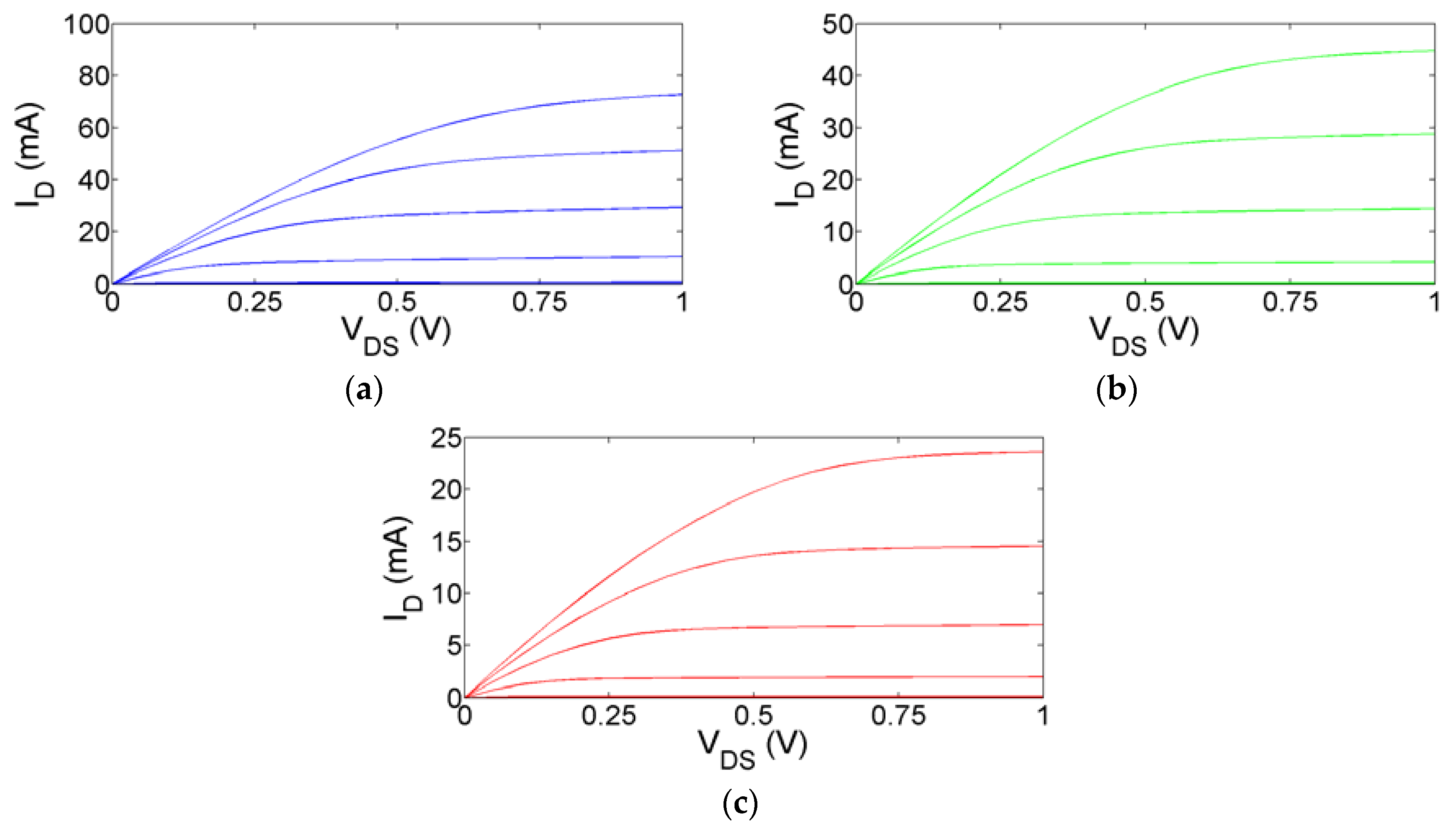

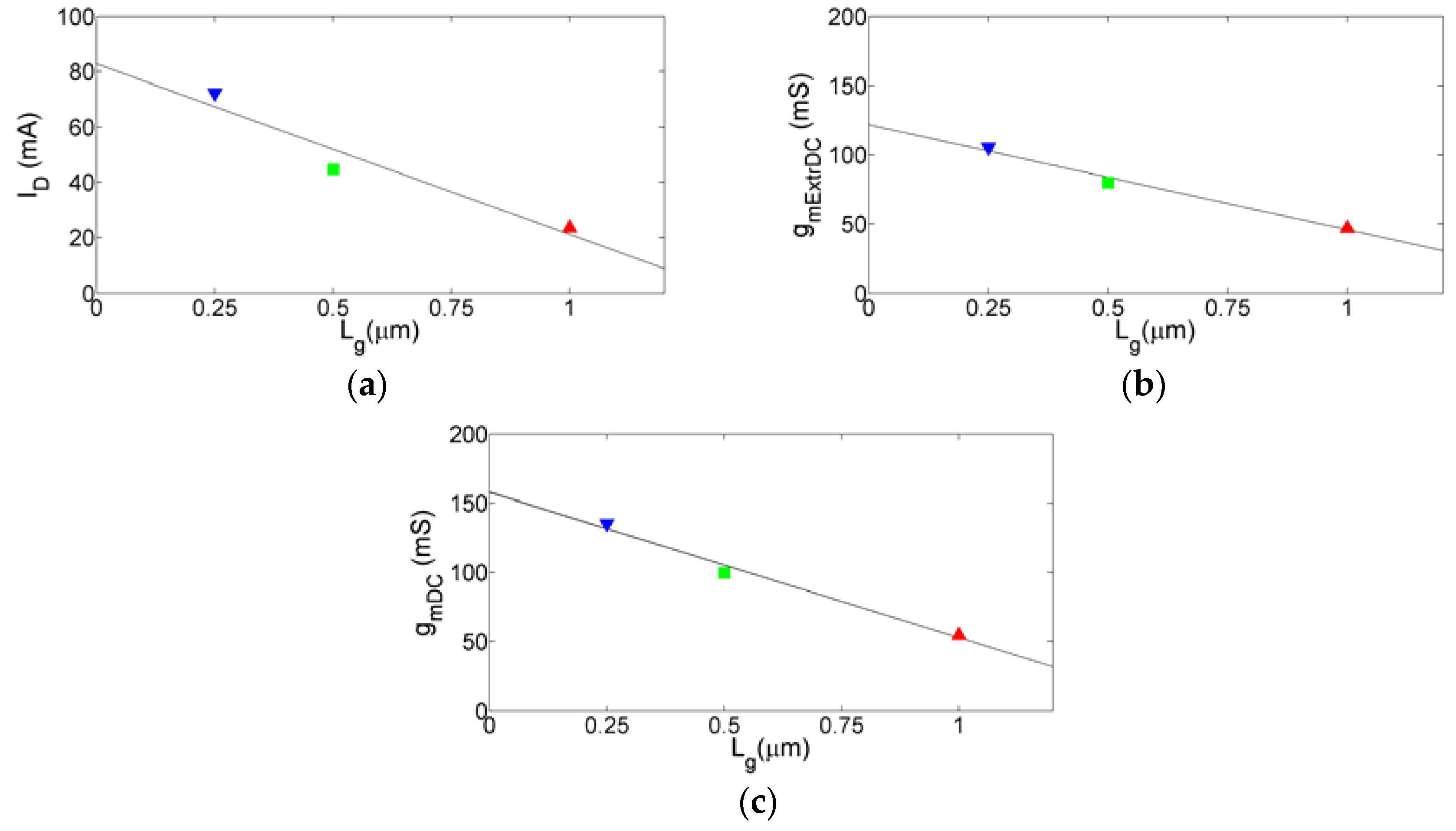

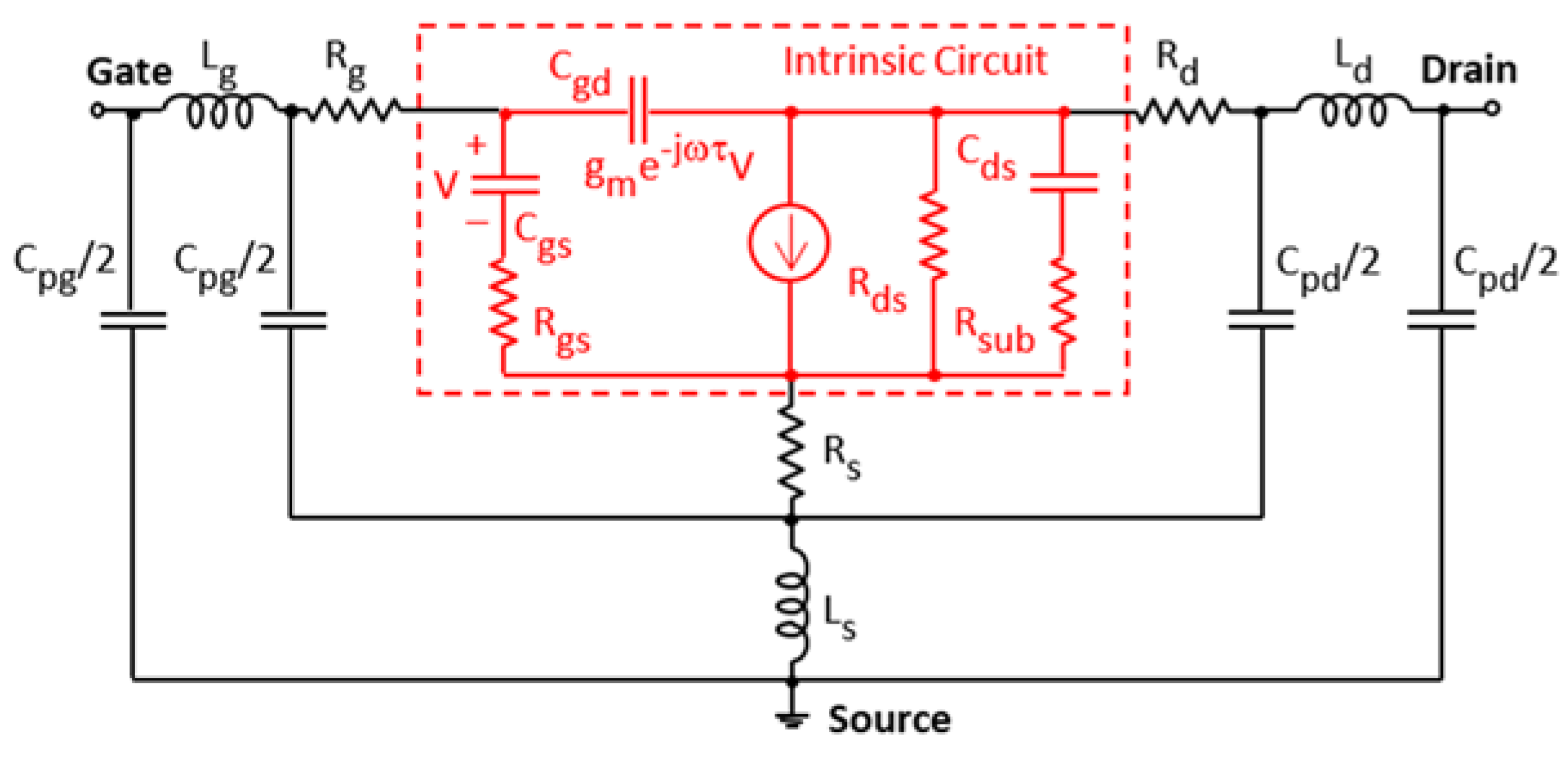

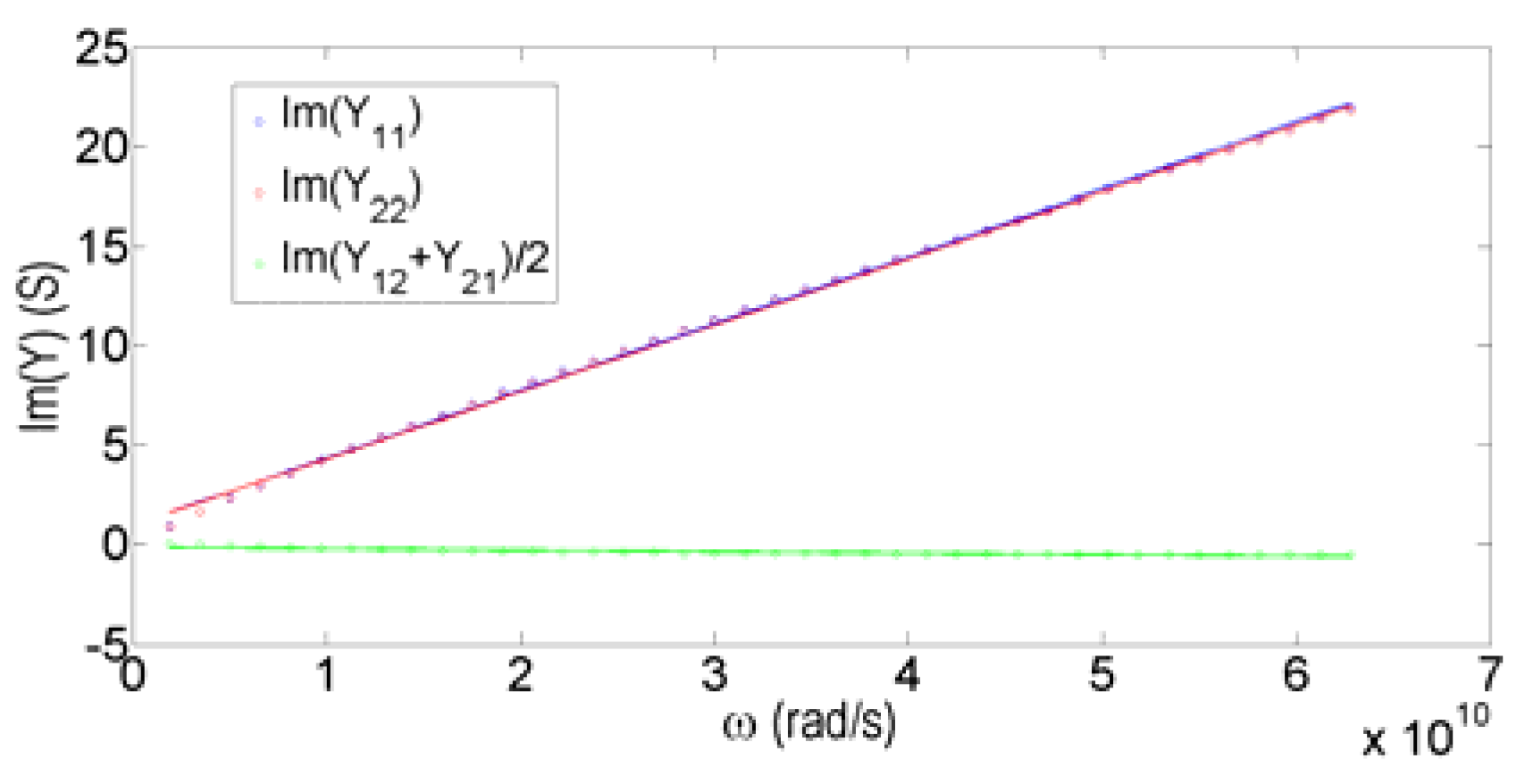

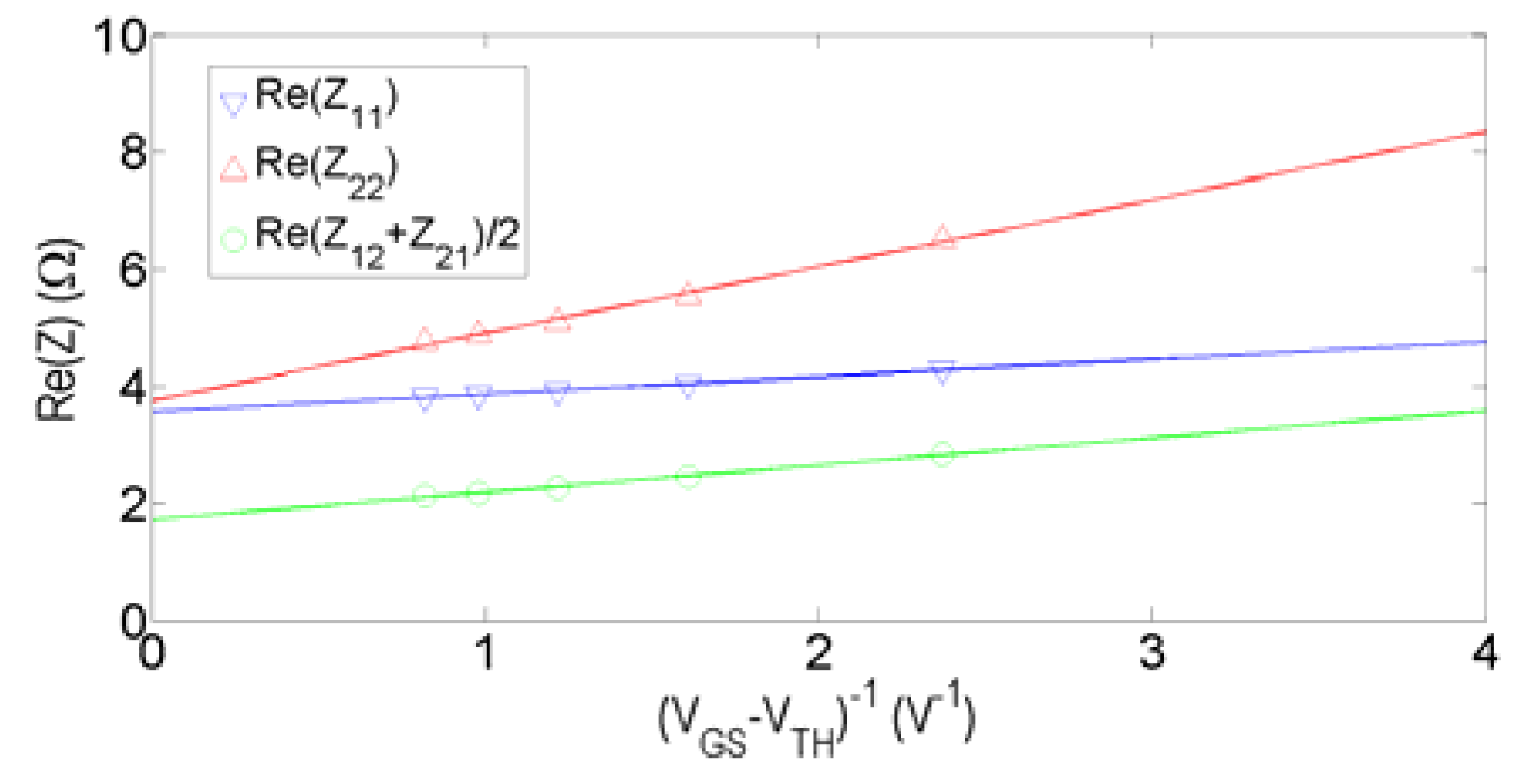

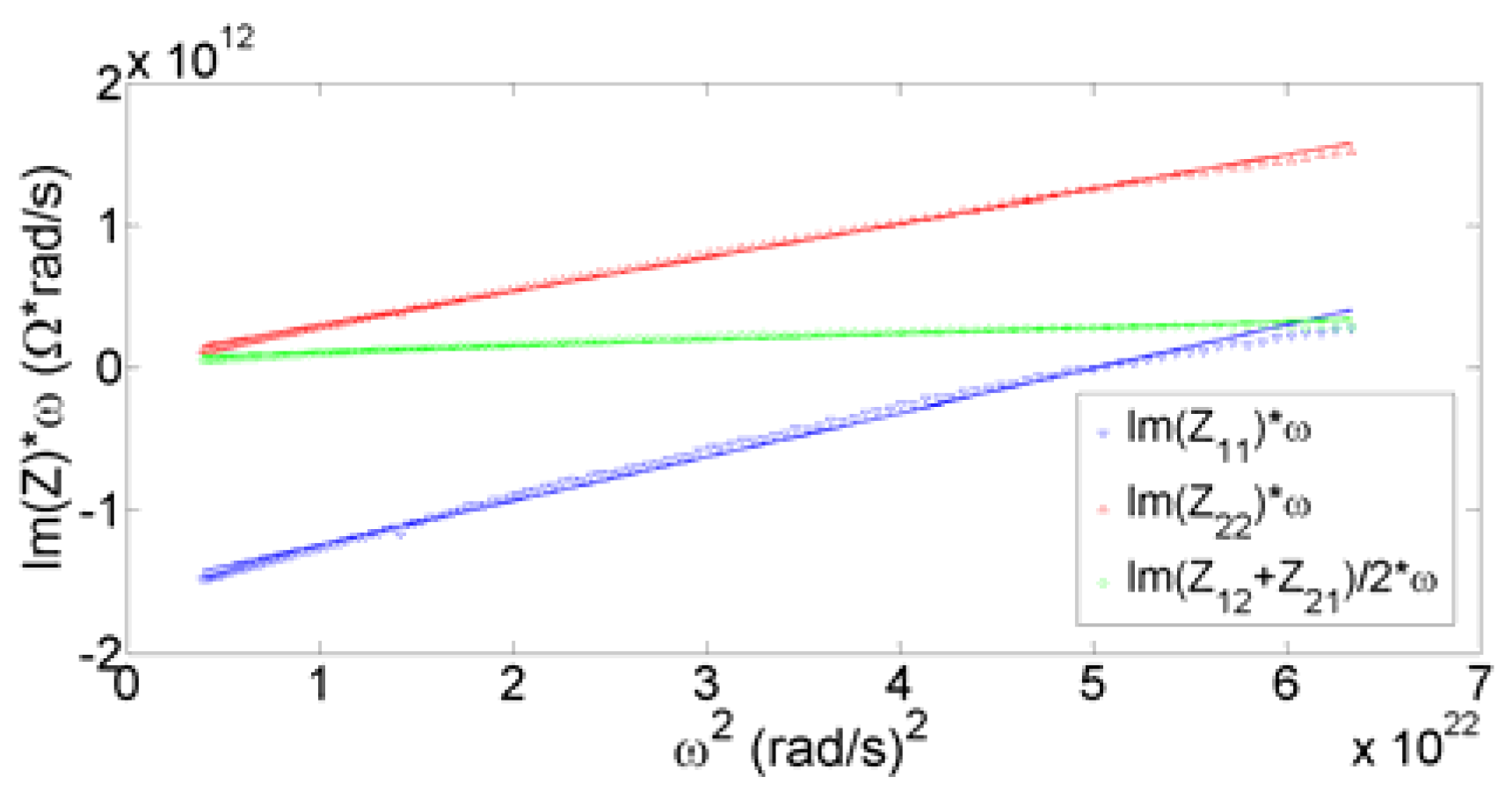

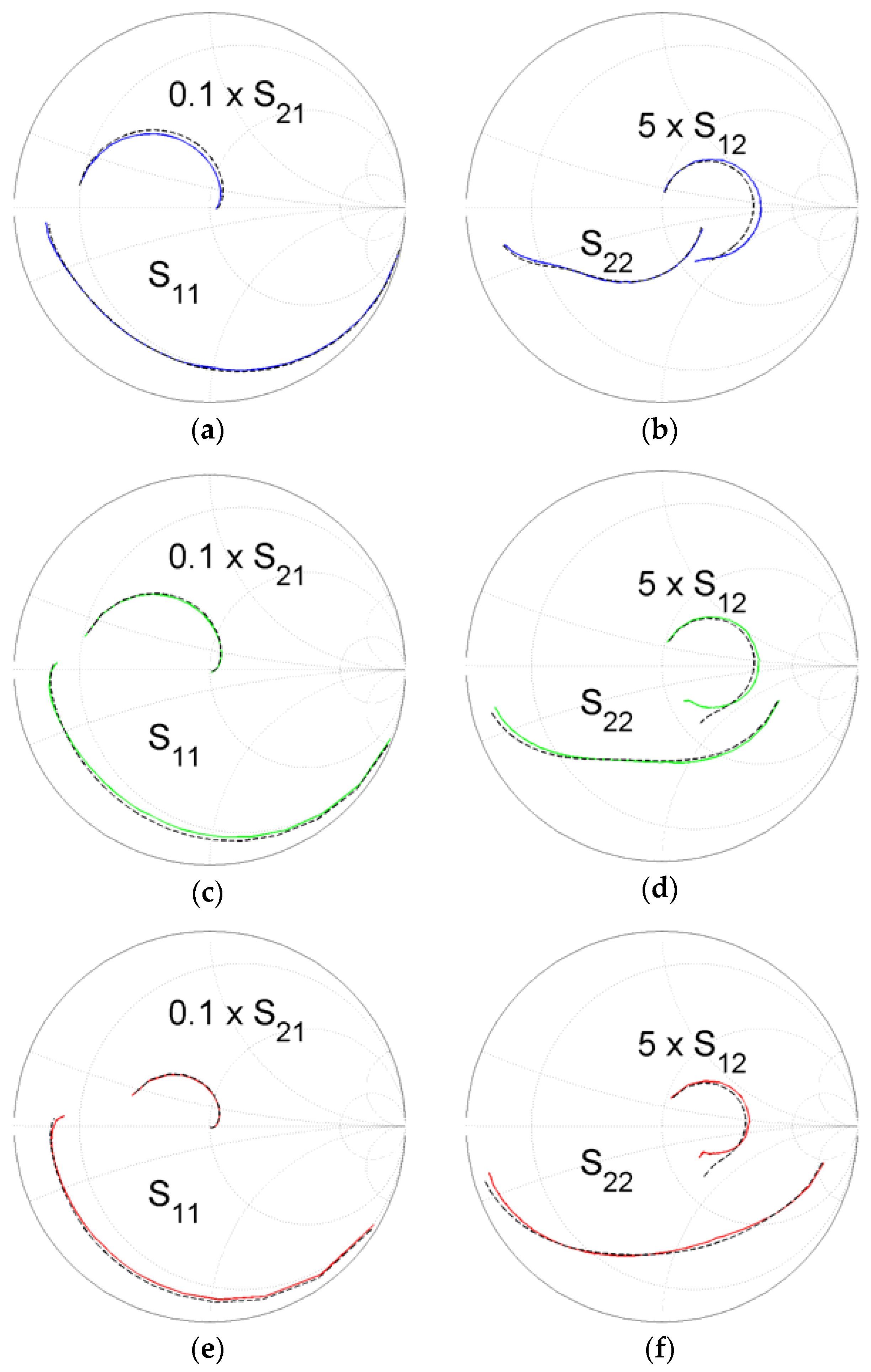

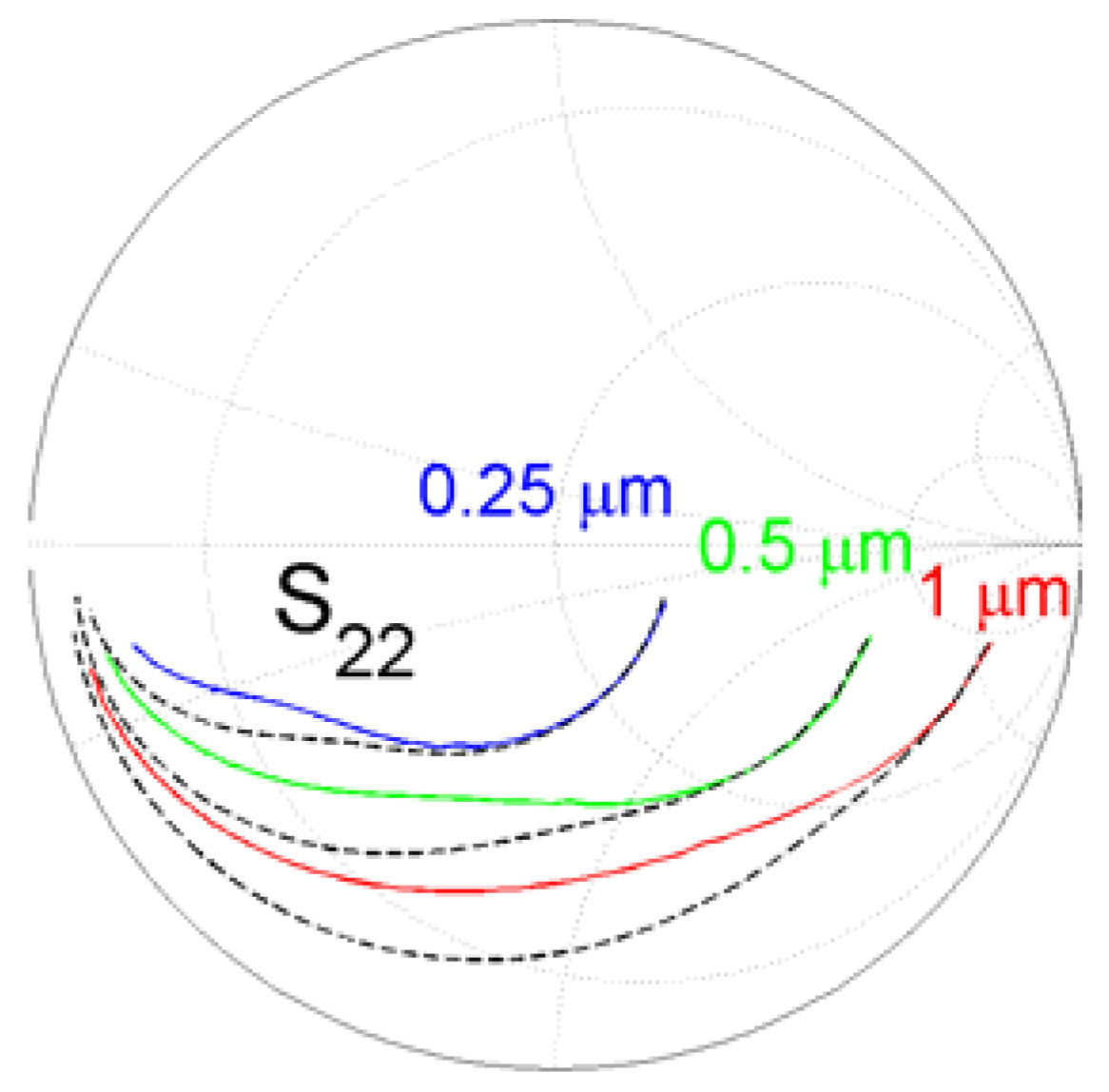

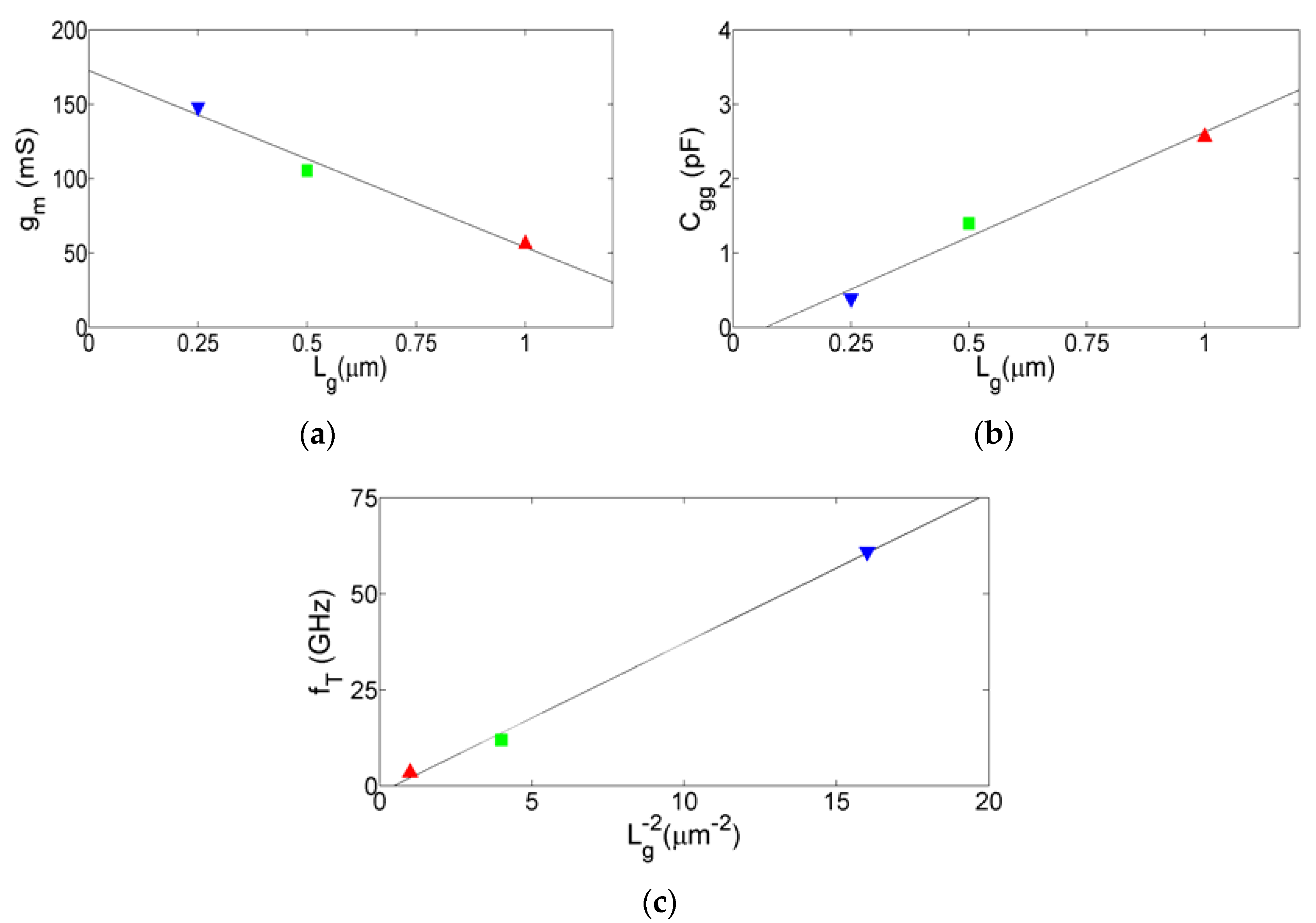

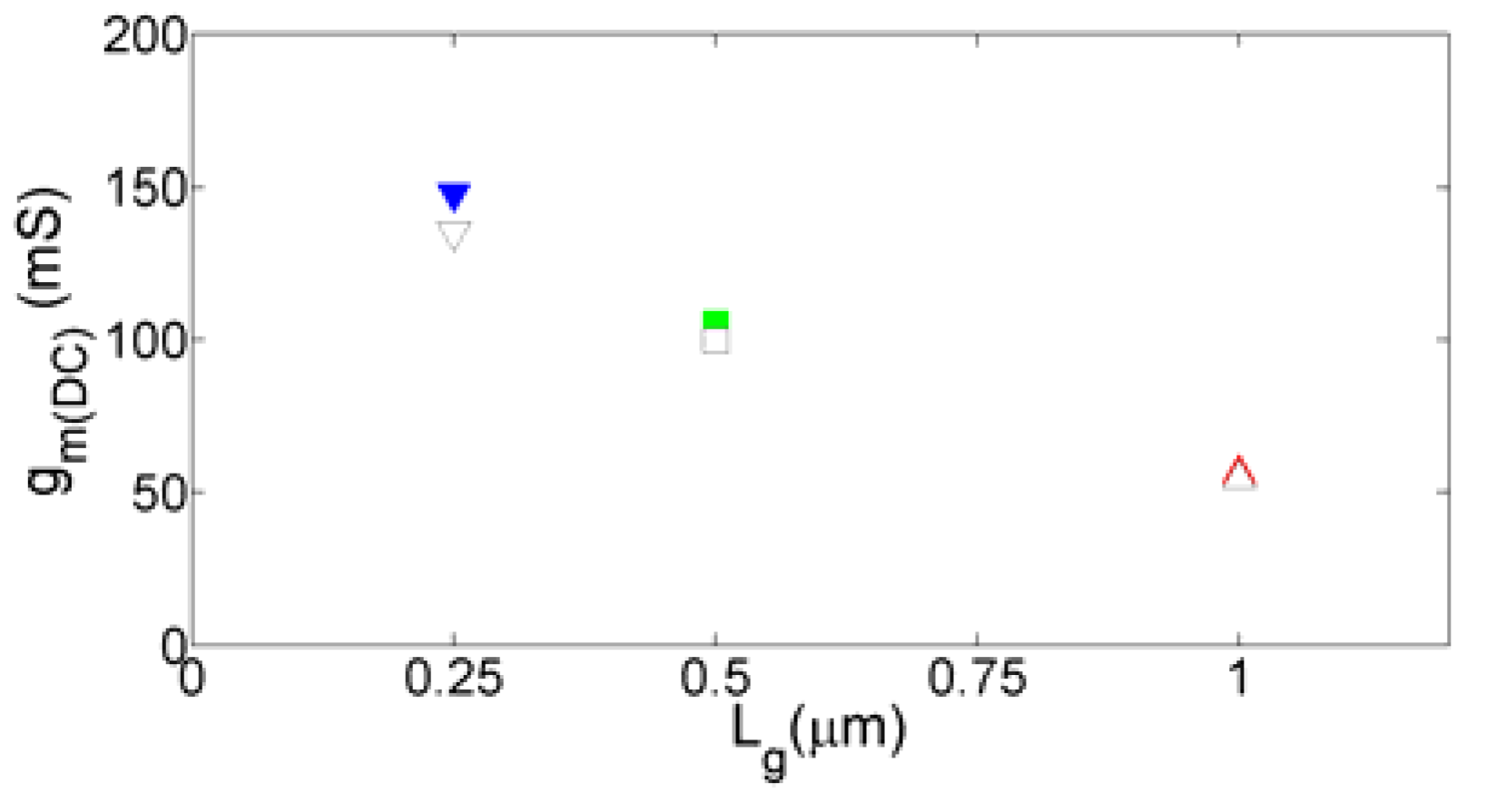

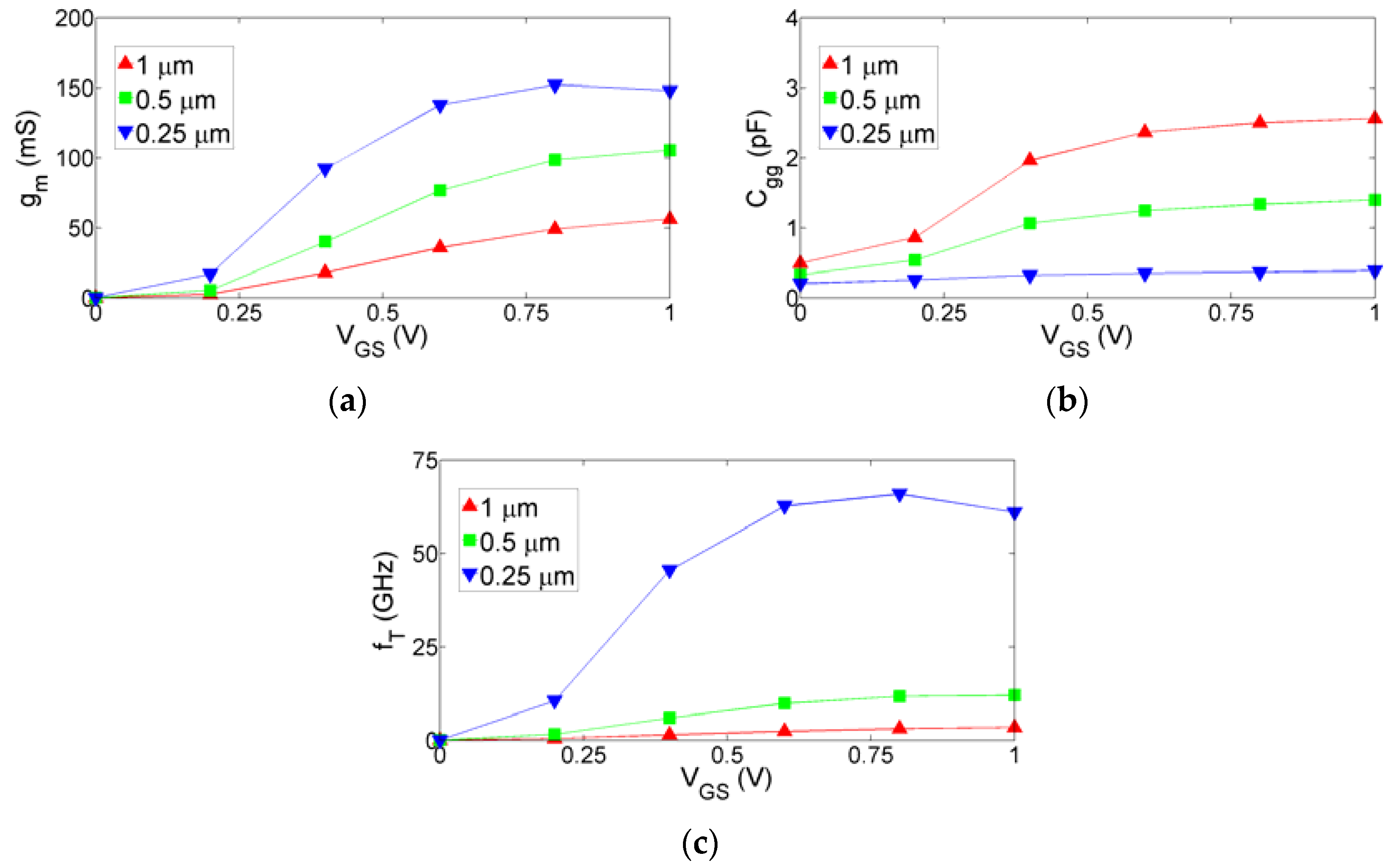

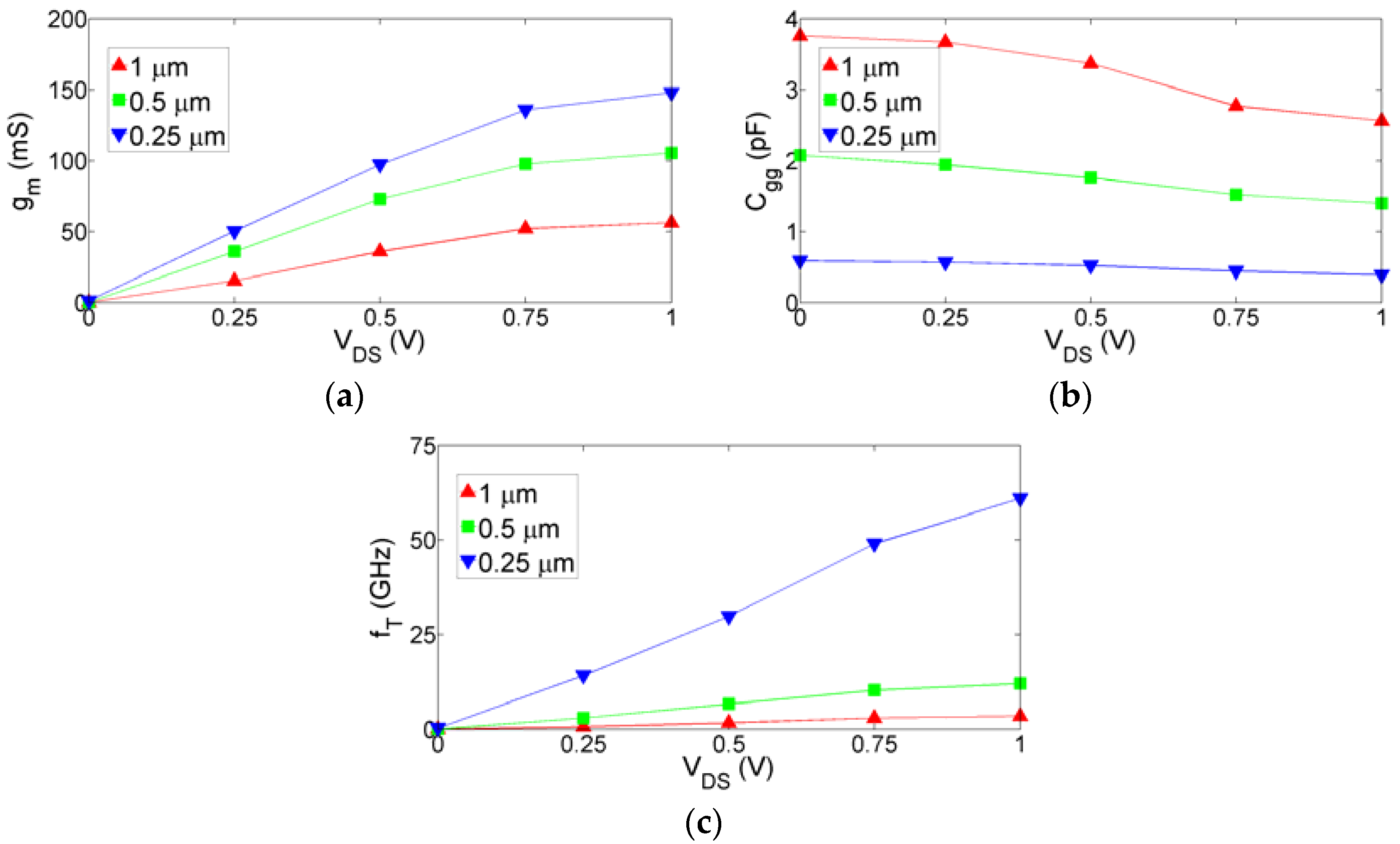

2. Model Extraction

3. Model Validation and Discussion

4. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Takagi, S.; Kim, S.-H.; Yokoyama, M.; Zhang, R.; Taoka, N.; Urabe, Y.; Yasuda, T.; Yamada, H.; Ichikawa, O.; Fukuhara, N.; et al. High mobility CMOS technologies using III-V/Ge channels on Si platform. Solid-State Electron. 2013, 88, 2–8. [Google Scholar] [CrossRef]

- Shi, M.; Saint-Martin, J.; Bournel, A.; Querlioz, D.; Wichmann, N.; Bollaert, S.; Danneville, F.; Dollfus, P. Monte Carlo analysis of the dynamic behavior of III-V MOSFETs for low-noise RF applications. Solid-State Electron. 2013, 87, 51–57. [Google Scholar] [CrossRef]

- Li, Z.; Niu, G.; Liang, Q.; Imura, K. Intermodulation linearity in high-k/metal gate 28 nm RF CMOS transistors. Electronics 2015, 4, 614–622. [Google Scholar] [CrossRef]

- Colinge, J.-P. Multiple-gate SOI MOSFETs. Microelectron. Eng. 2007, 84, 2071–2076. [Google Scholar] [CrossRef]

- Zota, C.B.; Lindelöw, F.; Wernersson, L.-E.; Lind, E. High-frequency InGaAs tri-gate MOSFETs with fmax of 400 GHz. Electron. Lett. 2016, 52, 1869–1871. [Google Scholar] [CrossRef]

- Li, S.; Cheng, J.; Han, B.; Gao, J. Bias-dependent small-signal modeling based on neuro-space mapping for MOSFET. Int. J. RF Microw. Comput.-Aided Eng. 2011, 12, 182–189. [Google Scholar] [CrossRef]

- Marinković, Z.; Markovic, V. Temperature-dependent models of low-noise microwave transistors based on neural networks. Int. J. RF Microw. Comput.-Aided Eng. 2005, 15, 567–577. [Google Scholar] [CrossRef]

- Marinković, Z.; Crupi, G.; Caddemi, A.; Marković, V. Comparison between analytical and neural approaches for multibias small signal modeling of microwave scaled FETs. Microw. Opt. Technol. Lett. 2010, 52, 2238–2244. [Google Scholar] [CrossRef]

- Colangeli, S.; Ciccognani, W.; Cleriti, R.; Palomba, M.; Limiti, E. Optimization-based approach for scalable small-signal and noisemodel extraction of GaN-on-SiC HEMTs. Int. J. Numer. Model Electron. Netw. Dev. Field 2017, 30, e2135. [Google Scholar] [CrossRef]

- Dambrine, G.; Cappy, A.; Heliodore, F.; Playez, E. A new method for determining the FET small-signal equivalent circuit. IEEE Trans. Microw. Theory Tech. 1988, 36, 1151–1159. [Google Scholar] [CrossRef]

- Alim, M.A.; Rezazadeh, A.A.; Gaquiere, C. Small signal model parameters analysis of GaN and GaAs based HEMTs over temperature for microwave applications. Solid-State Electron. 2016, 19, 11–18. [Google Scholar] [CrossRef]

- Crupi, G.; Raffo, A.; Avolio, G.; Schreurs, D.M.M.-P.; Vannini, G.; Caddemi, A. Temperature influence on GaN HEMT equivalent circuit. IEEE Microw. Wireless Comp. Lett. 2016, 26, 813–815. [Google Scholar] [CrossRef]

- Pascht, A.; Grözing, M.; Wiegner, D.; Berroth, M. Small-signal and temperature noise model for MOSFETs. IEEE Trans. Microw. Theory Tech. 2002, 50, 1927–1934. [Google Scholar] [CrossRef]

- Crupi, G.; Schreurs, D.M.M.-P.; Parvais, B.; Caddemi, A.; Mercha, A.; Decoutere, S. Scalable and multibias high frequency modeling of multi fin FETs. Solid-State Electron. 2006, 50, 1780–1786. [Google Scholar] [CrossRef]

- Zarate-Rincon, F.; Torres-Torres, R.; Murphy-Arteaga, R.S. Consistent DC and RF MOSFET modeling using an S-parameter measurement-based parameter extraction method in the linear region. IEEE Trans. Microw. Theory Tech. 2015, 63, 4255–4262. [Google Scholar] [CrossRef]

- Yu, P.; Zhou, Y.; Sun, L.; Gao, J. A novel approach to extracting extrinsic resistances for equivalent circuit model of nanoscale MOSFET. Int. J. Numer. Model Electron. Netw. Dev. Field 2016, 29, 1044–1054. [Google Scholar] [CrossRef]

- Saavedra-Gomez, H.J.; Loo-Yau, J.R.; Reynoso-Hernandez, J.A.; Moreno, P.; del Valle-Padilla, J.L. A simple and reliable method to extract the electrical equivalent circuits of CMOS pads. Microw. Opt. Technol. Lett. 2013, 55, 3033–3037. [Google Scholar] [CrossRef]

- Choi, W.; Jung, G.; Kim, J.; Kwon, Y. Scalable small-signal modeling of RF CMOS FET based on 3-D EM-based extraction of parasitic effects and its application to millimeter-wave amplifier design. IEEE Trans. Microw. Theory Tech. 2009, 57, 3345–3353. [Google Scholar] [CrossRef]

- Resca, D.; Santarelli, A.; Raffo, A.; Cignani, R.; Vannini, G.; Filicori, F.; Schreurs, D.M.M.-P. Scalable nonlinear FET model based on a distributed parasitic network description. IEEE Trans. Microw. Theory Tech. 2008, 56, 755–766. [Google Scholar] [CrossRef]

- Resca, D.; Raffo, A.; Santarelli, A.; Vannini, G.; Filicori, F. Scalable equivalent circuit FET model for MMIC design identified through FW-EM analyses. IEEE Trans. Microw. Theory Tech. 2009, 57, 245–253. [Google Scholar] [CrossRef]

- Jia, Y.; Xu, Y.; Xu, R.; Li, Y. An accurate parasitic parameters extraction method based on FW-EM for AlGaN/GaN HEMT up to 110 GHz. Int. J. Numer. Model Electron. Netw. Dev. Field 2017, e2270. [Google Scholar] [CrossRef]

- White, P.M.; Healy, R.M. Improved equivalent circuit for determination of MESFET and HEMT parasitic capacitances from “Coldfet” measurements. IEEE Microw. Guided Wave Lett. 1993, 3, 453–454. [Google Scholar] [CrossRef]

- Crupi, G.; Avolio, G.; Raffo, A.; Barmuta, P.; Schreurs, D.M.M.-P.; Caddemi, A.; Vannini, G. Investigation on the thermal behavior for microwave GaN HEMTs. Solid-State Electron. 2011, 64, 28–33. [Google Scholar] [CrossRef]

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Crupi, G.; Schreurs, D.M.M.-P.; Caddemi, A. Effects of Gate-Length Scaling on Microwave MOSFET Performance. Electronics 2017, 6, 62. https://doi.org/10.3390/electronics6030062

Crupi G, Schreurs DMM-P, Caddemi A. Effects of Gate-Length Scaling on Microwave MOSFET Performance. Electronics. 2017; 6(3):62. https://doi.org/10.3390/electronics6030062

Chicago/Turabian StyleCrupi, Giovanni, Dominique M. M.-P. Schreurs, and Alina Caddemi. 2017. "Effects of Gate-Length Scaling on Microwave MOSFET Performance" Electronics 6, no. 3: 62. https://doi.org/10.3390/electronics6030062