Efficient Fault Localization and Failure Analysis Techniques for Improving IC Yield

Abstract

:1. Introduction

2. Fabrication Centric Solutions for Process/Product Ramp and Production

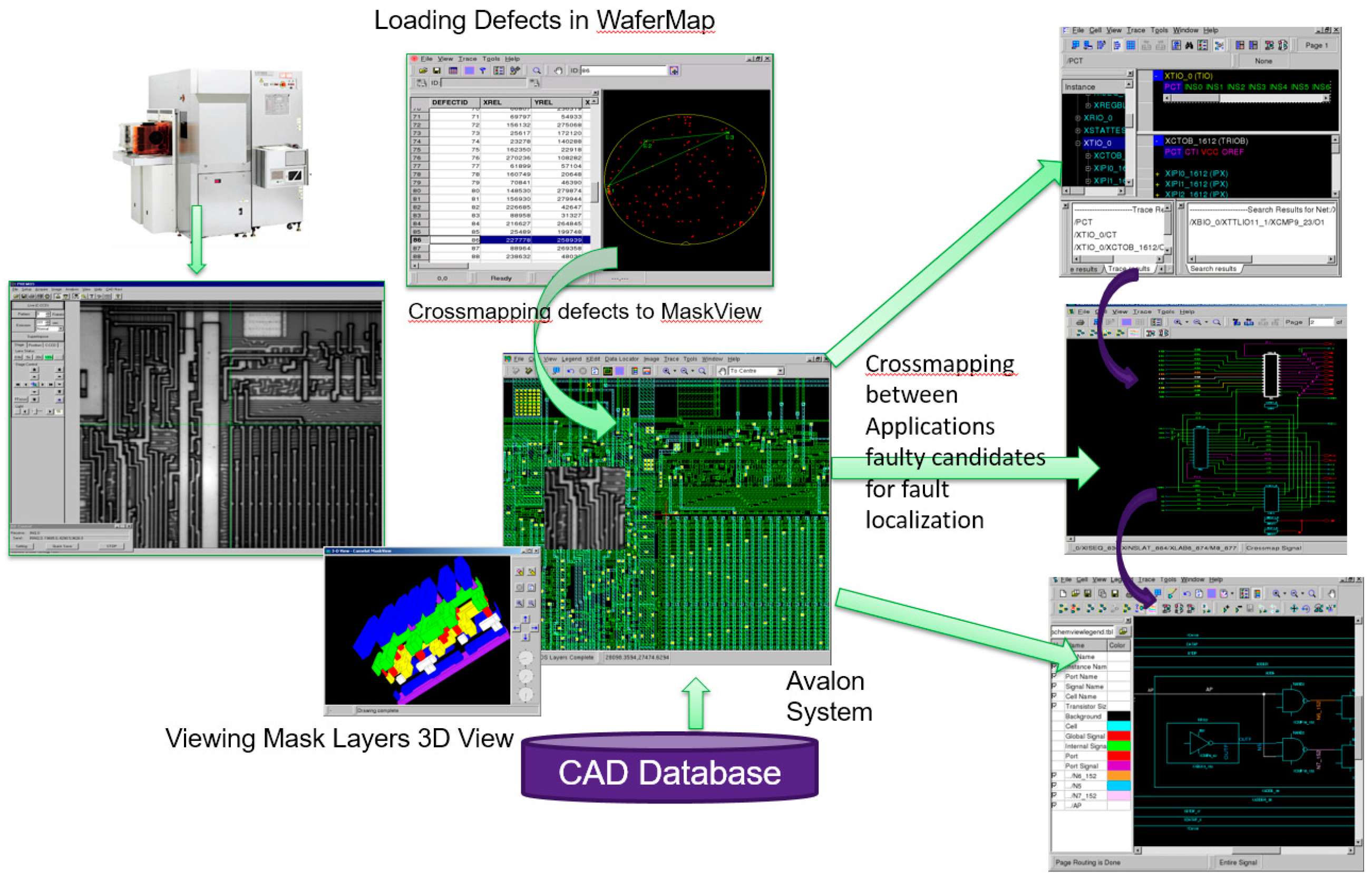

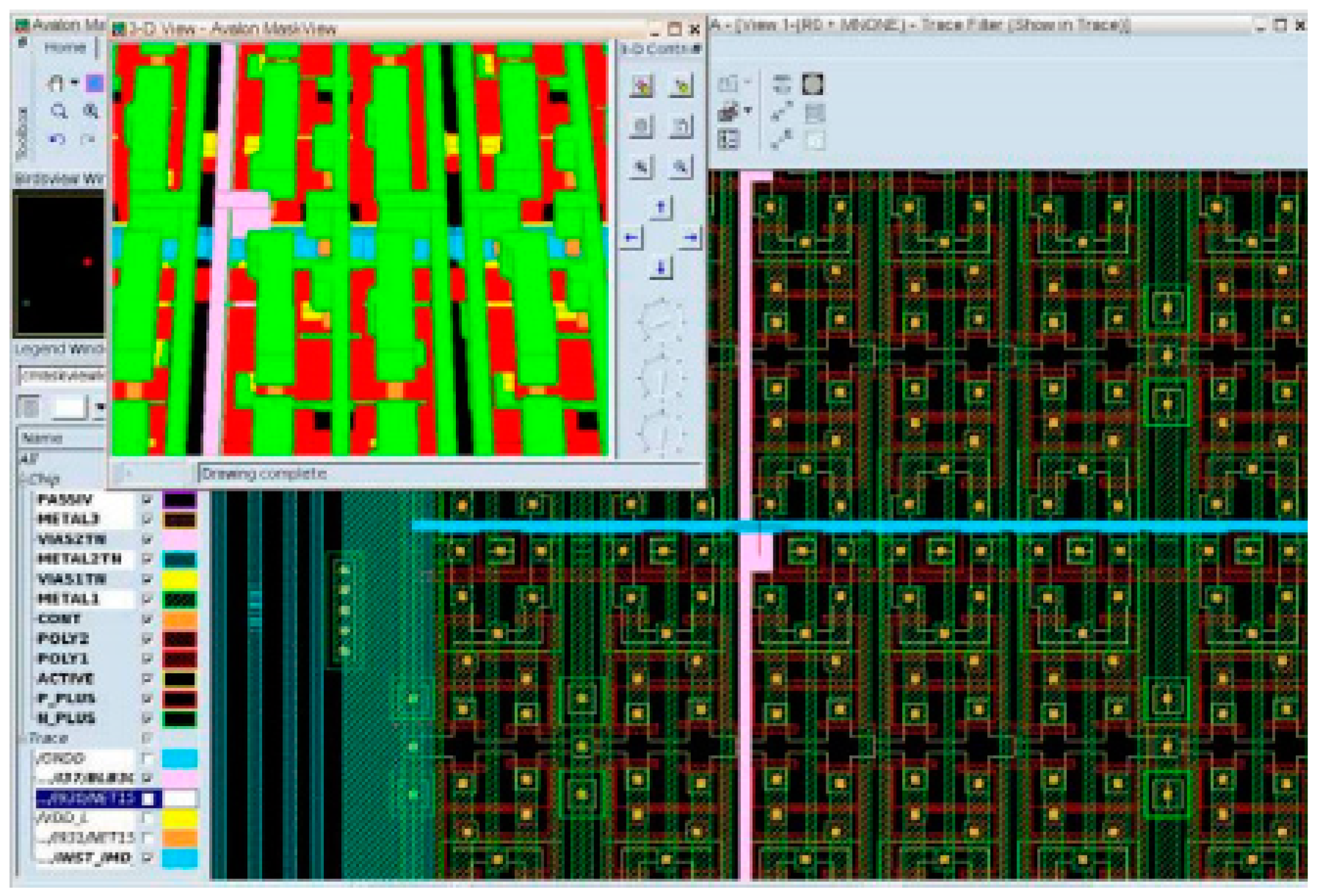

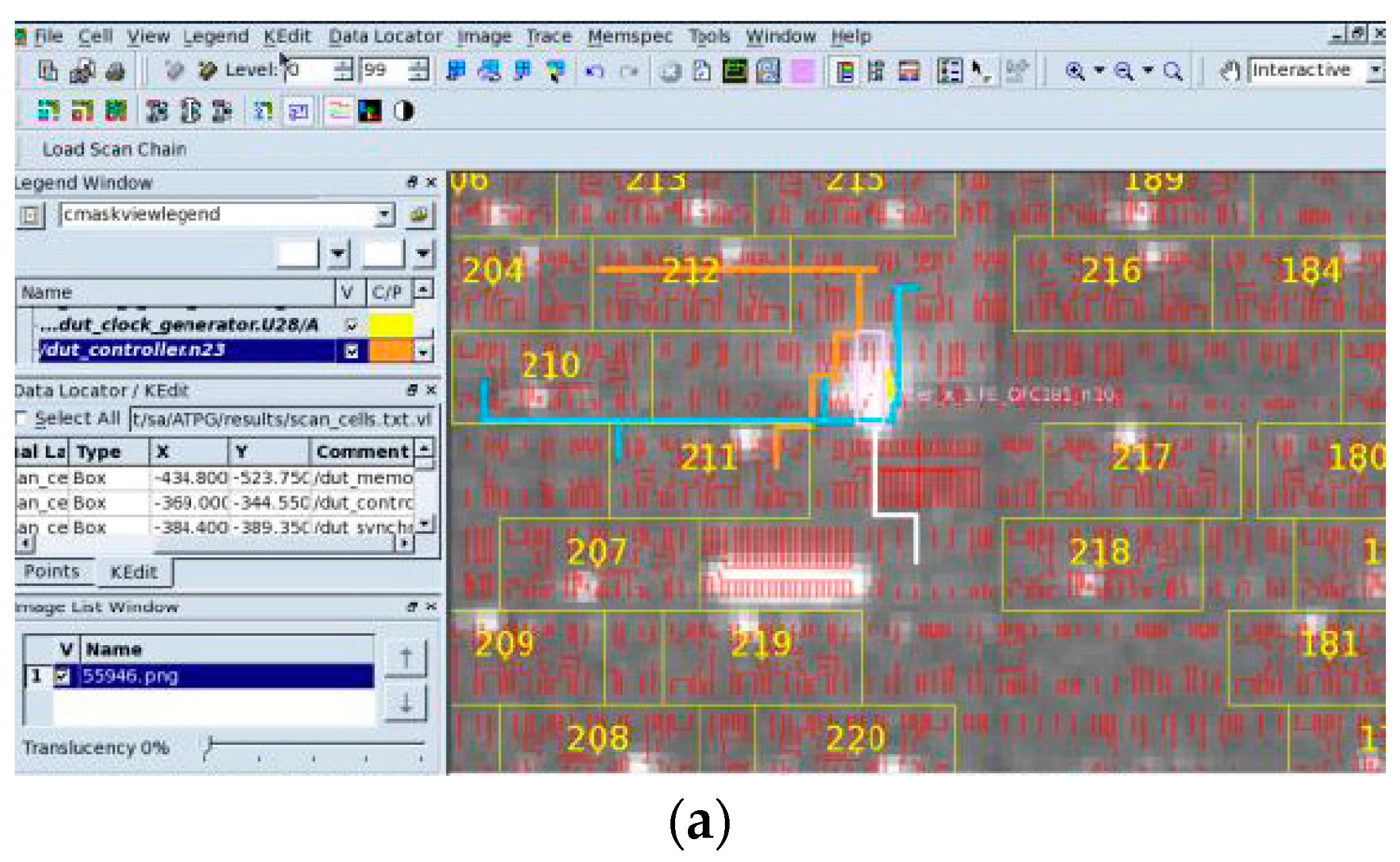

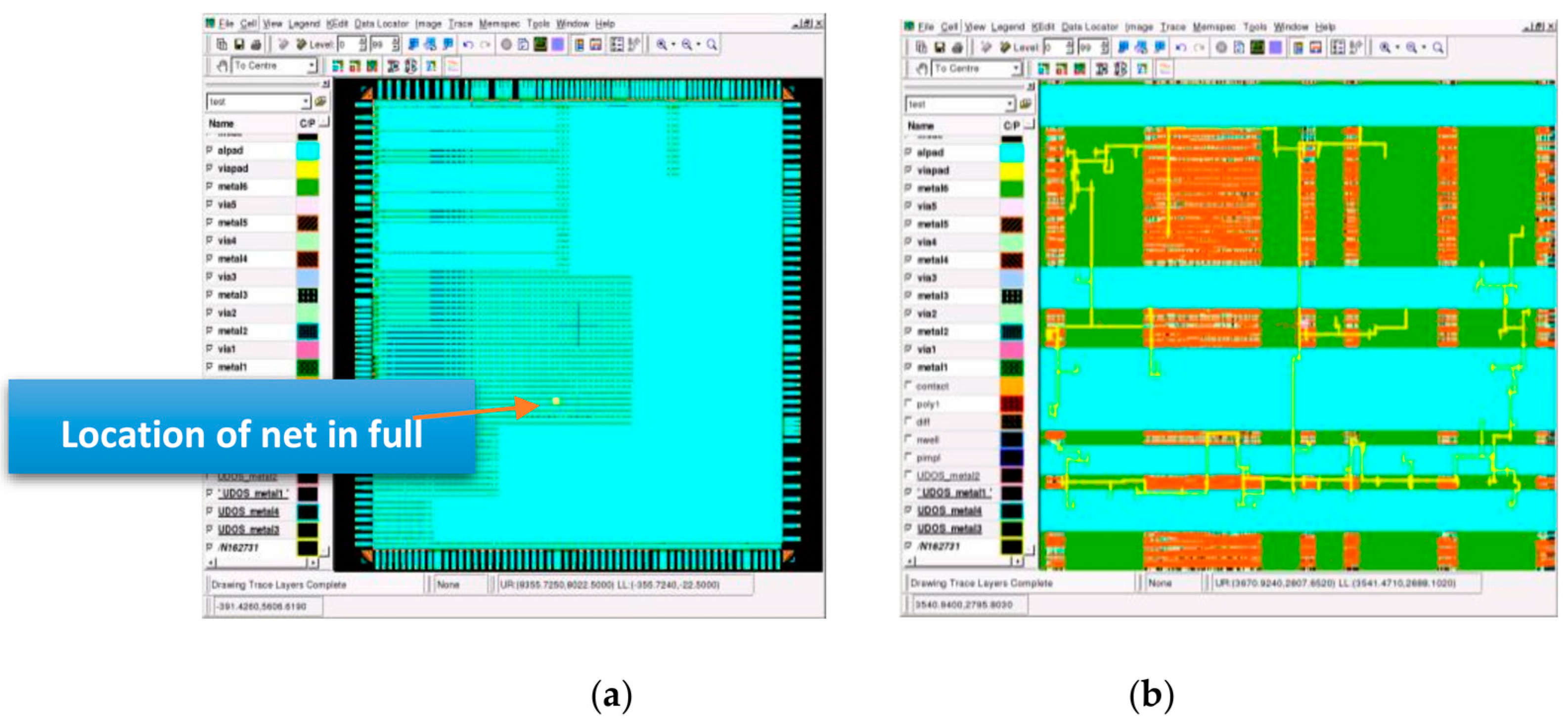

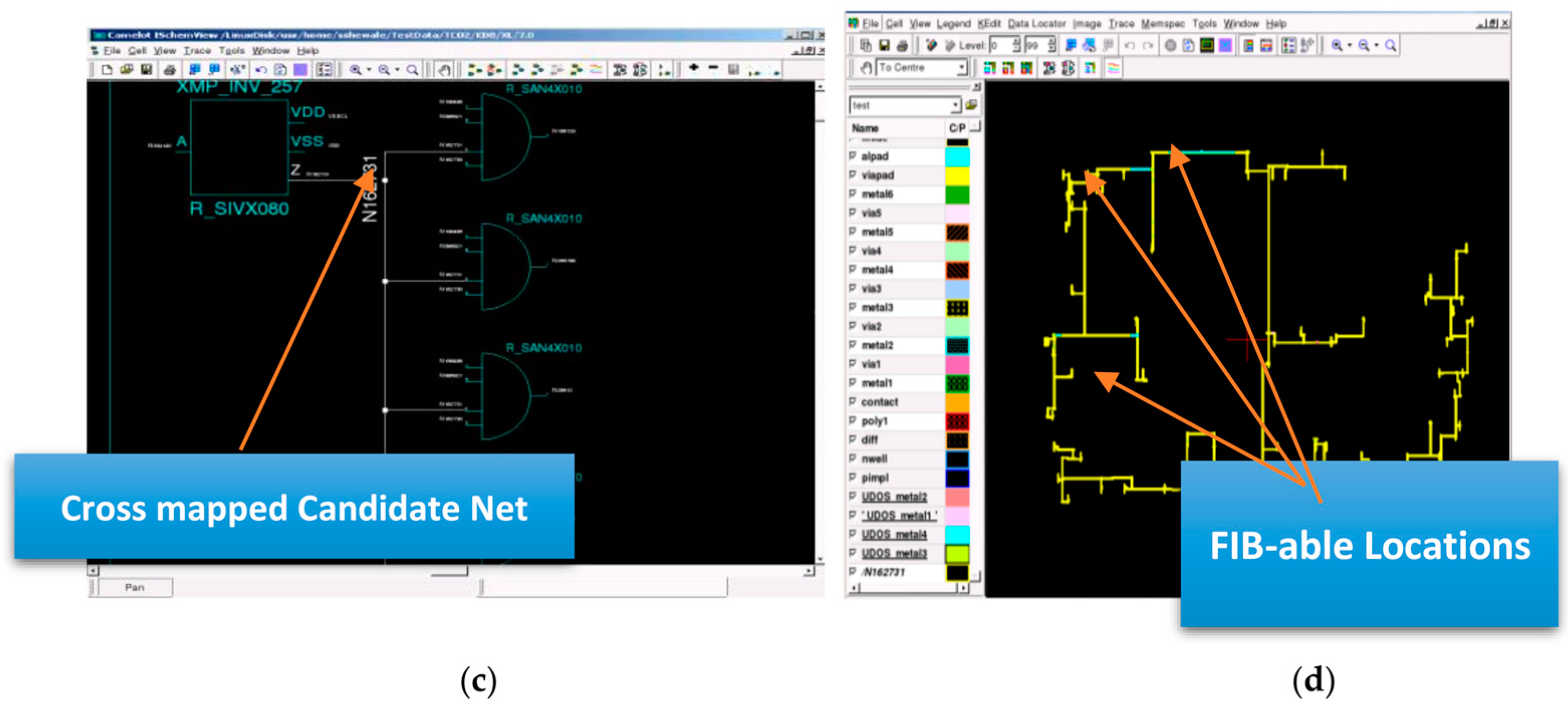

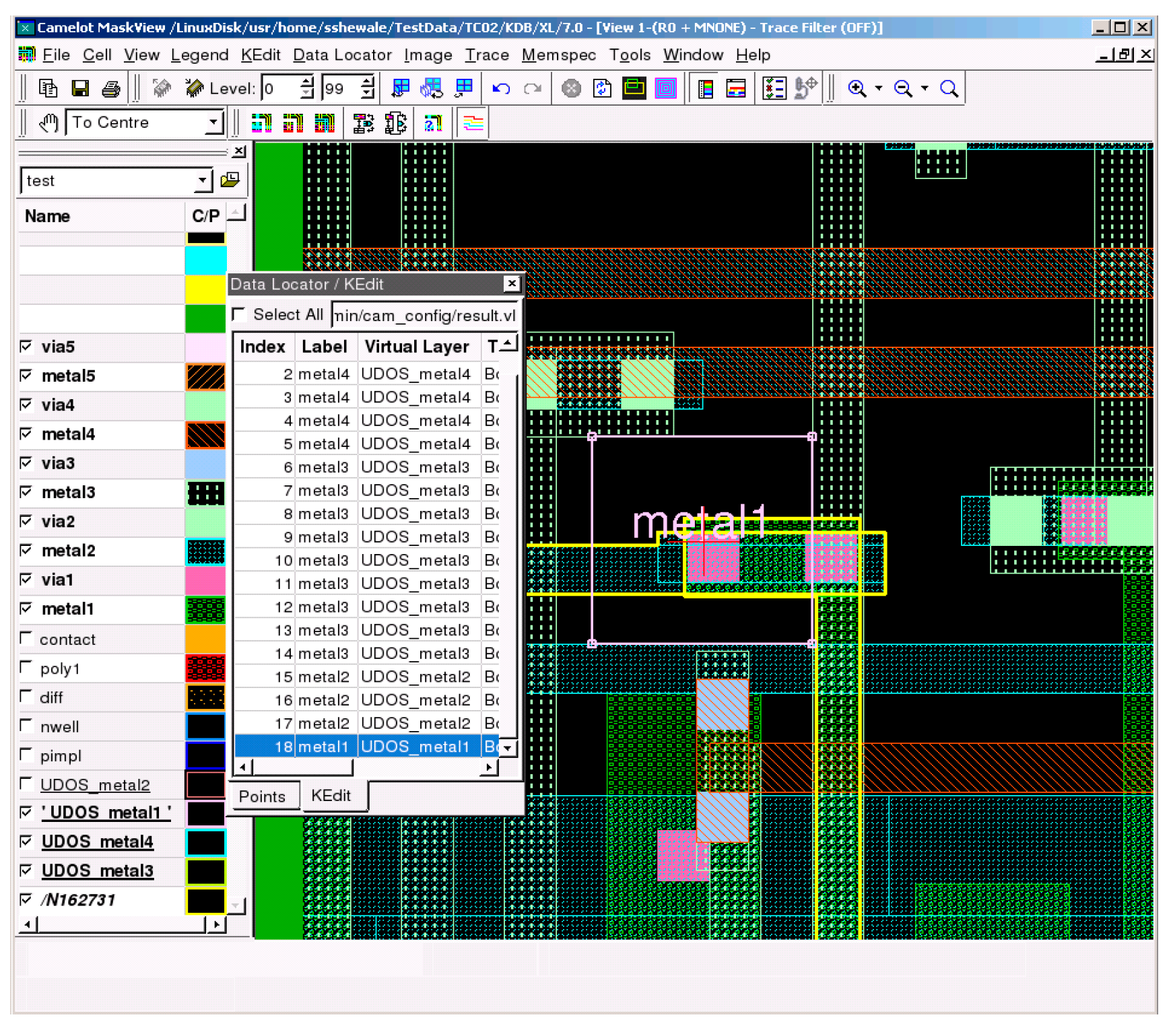

- MaskView—The Avalon MaskView tool can import CAD design data from all the key layout versus schematic (LVS) packages and several user-proprietary formats. It provides visual representations of circuits that can be manipulated, rotated, exploded, searched and linked with ease. It allows the tracing and cross-mapping of signals from the chip layout to netlist and schematic design data.

- NetView—Avalon NetView provides a visual representation of the net information of a chip design in the form of a hierarchical cell tree. The cell tree contains the top cell of the chip design and cell instances. The cell instances contain information on their signals and sub cells. The tool allows you to search and locate nets, cell instances and devices, cross-mapped from other Avalon tools. You can also trace and cross-map signals and cell instances from the netlist to the chip layout and schematic design data.

- SchemView—Avalon SchemView provides a pictorial representation of the chip schematic design data. The tool allows tracing and cross-mapping of signals, cell instances and devices from the schematic design to the chip layout and the netlist data.

- ISchemView—Avalon ISchemView provides a visual representation of the chip schematic design data. The tool allows tracing and cross-mapping of signals and cell instances from the schematic design to the chip layout and the netlist data. It helps in interactively viewing the desired instances/net.

- BitMap—Avalon BitMap allows you to analyze the memory layout of a chip. You can load the chip’s memory specification (memspec) files, created using Avalon MaskView, in Avalon. The tool then accepts a logical or a topological memory address and converts it to a physical address, or vice versa, using the expressions in the specification file. You can also cross-map the computed physical addresses to view them on the chip layout opened in MaskView.

- WaferMap—Avalon WaferMap provides a visual representation of the wafer under inspection, the dies present in the wafer and the defects present in the dies. The tool allows cross-mapping of defects in the wafer to their die layout opened in Avalon MaskView.

- The HotSpot Analyzer in MaskView: allows user to draw regions on the layout that correspond to hot-spot regions (emission spots) to detect the crucial nets. It finds the nets in each hot-spot region and plots a pareto graph of nets crossing one or more hotspots which helps easily locate the killer net. Figure 6 shows how CAD navigation is possible through Avalon and how Avalon HotSpot Analyzer helps in fault localization.

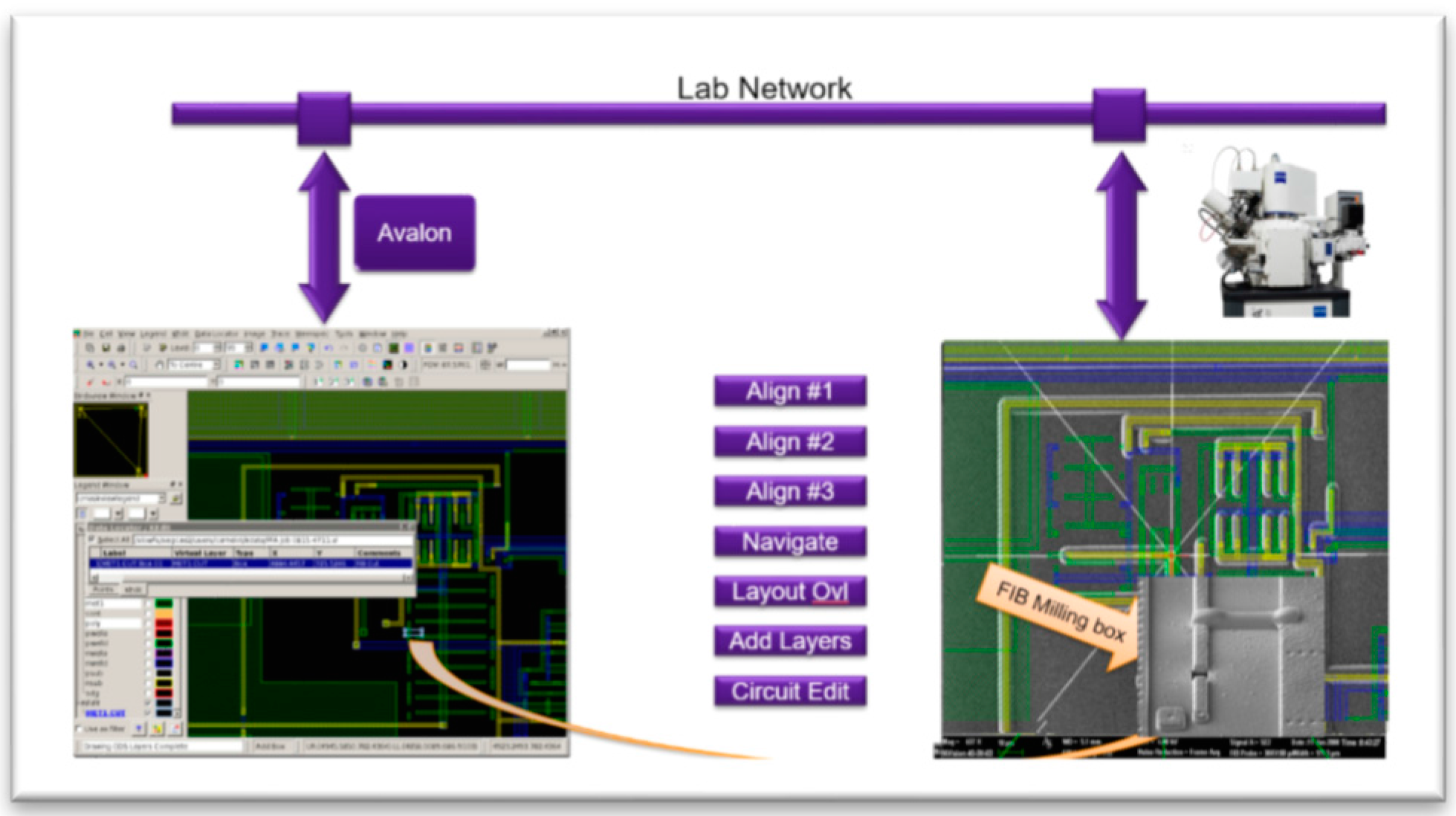

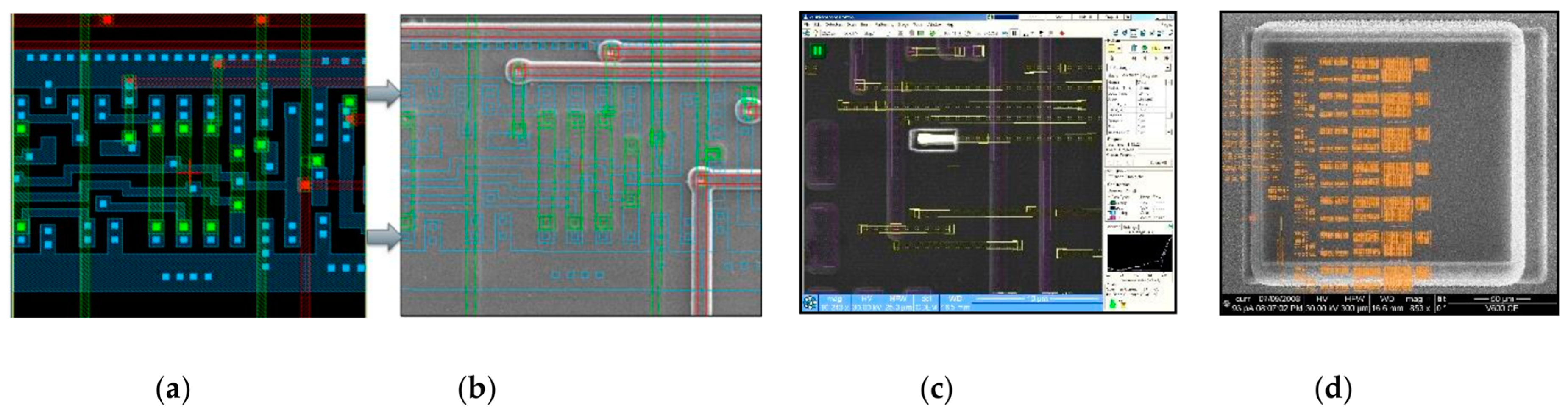

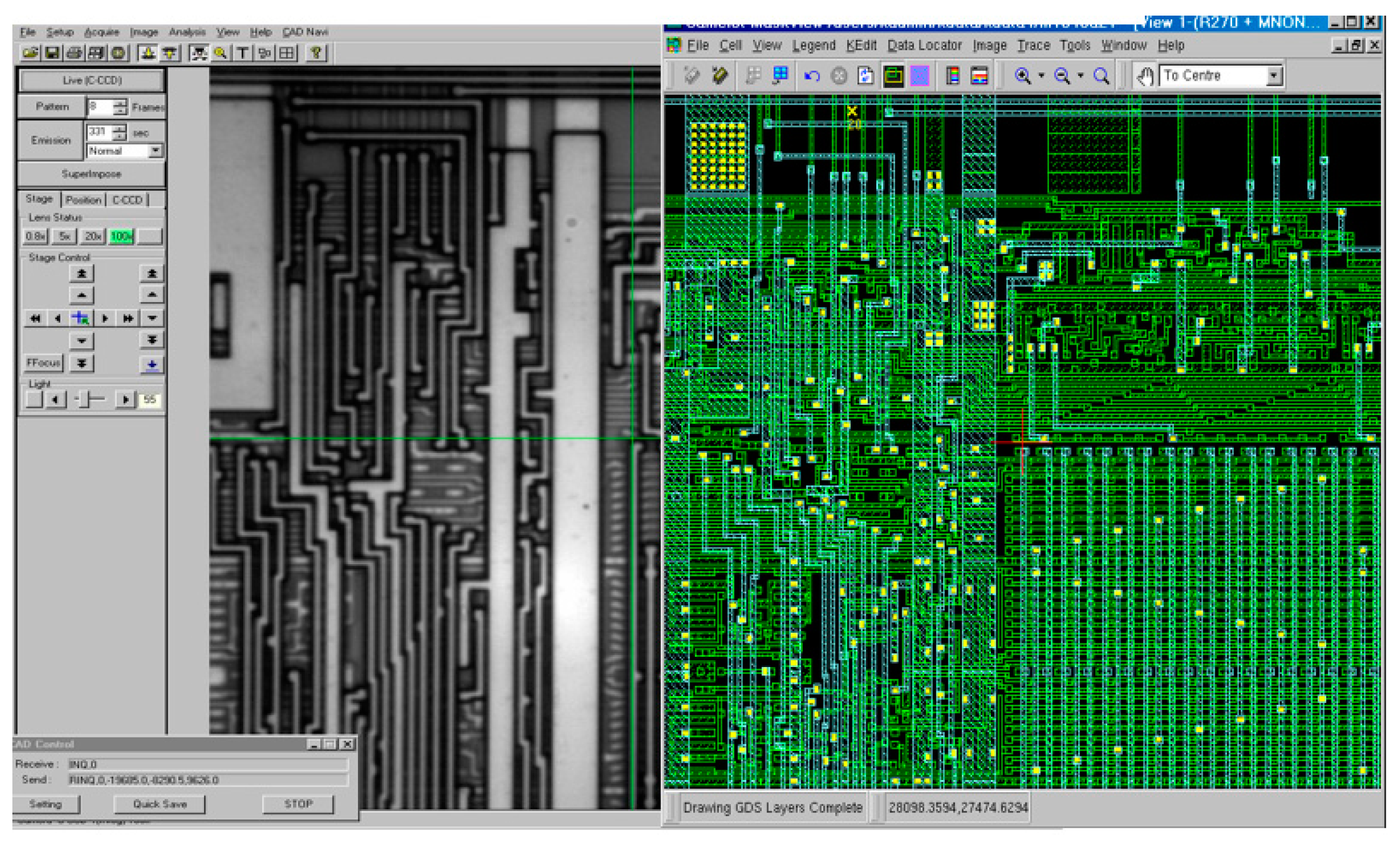

- Avalon’s capability to communicate with the equipment. Figure 7 shows the role of Avalon in PFA using its 3-point alignment and communication with manufacturing equipment.

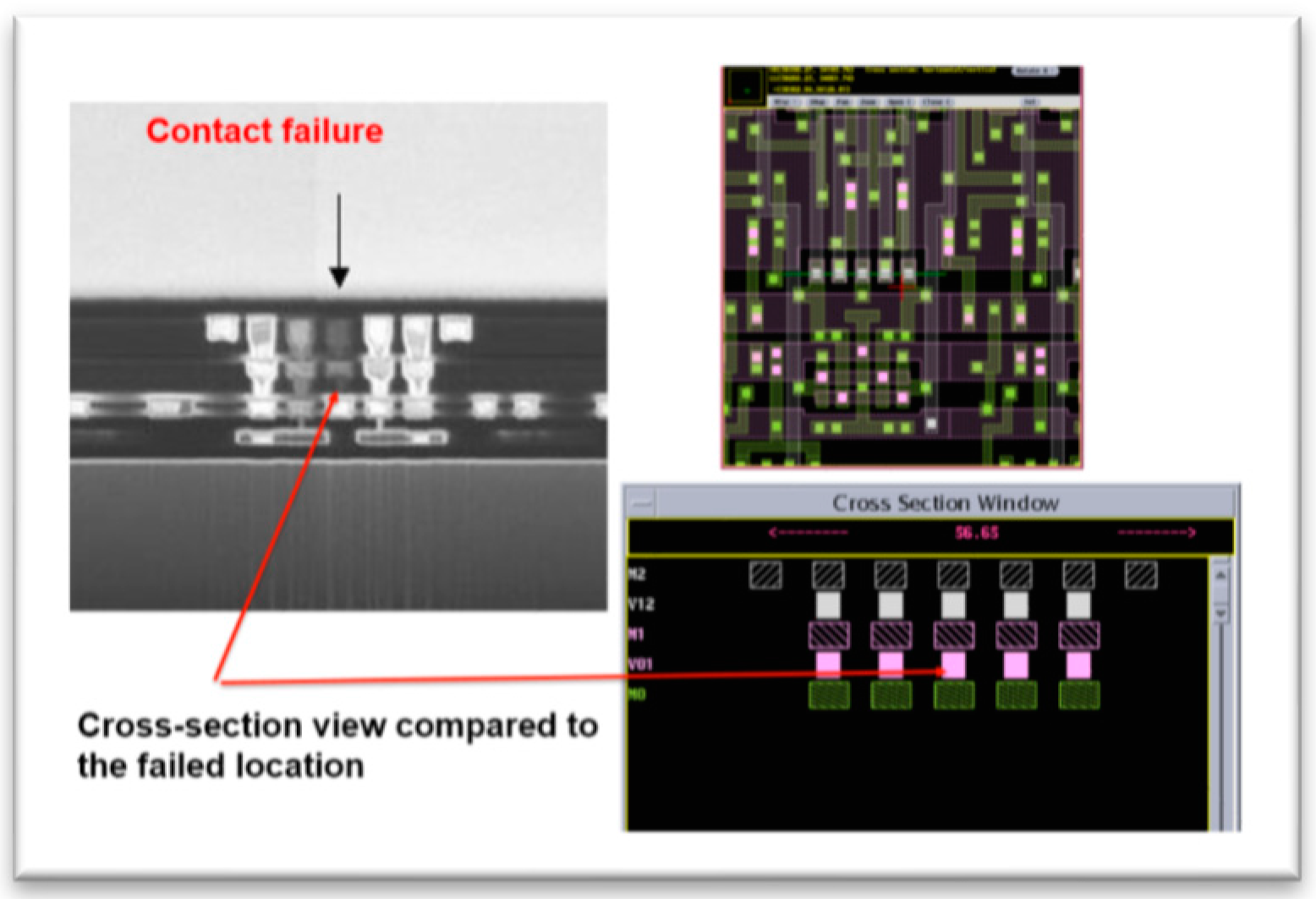

- The cross-section as viewed with the scanning emission microscope (SEM) analysis compared with the cross-sectional view of MaskView (see Figure 8).

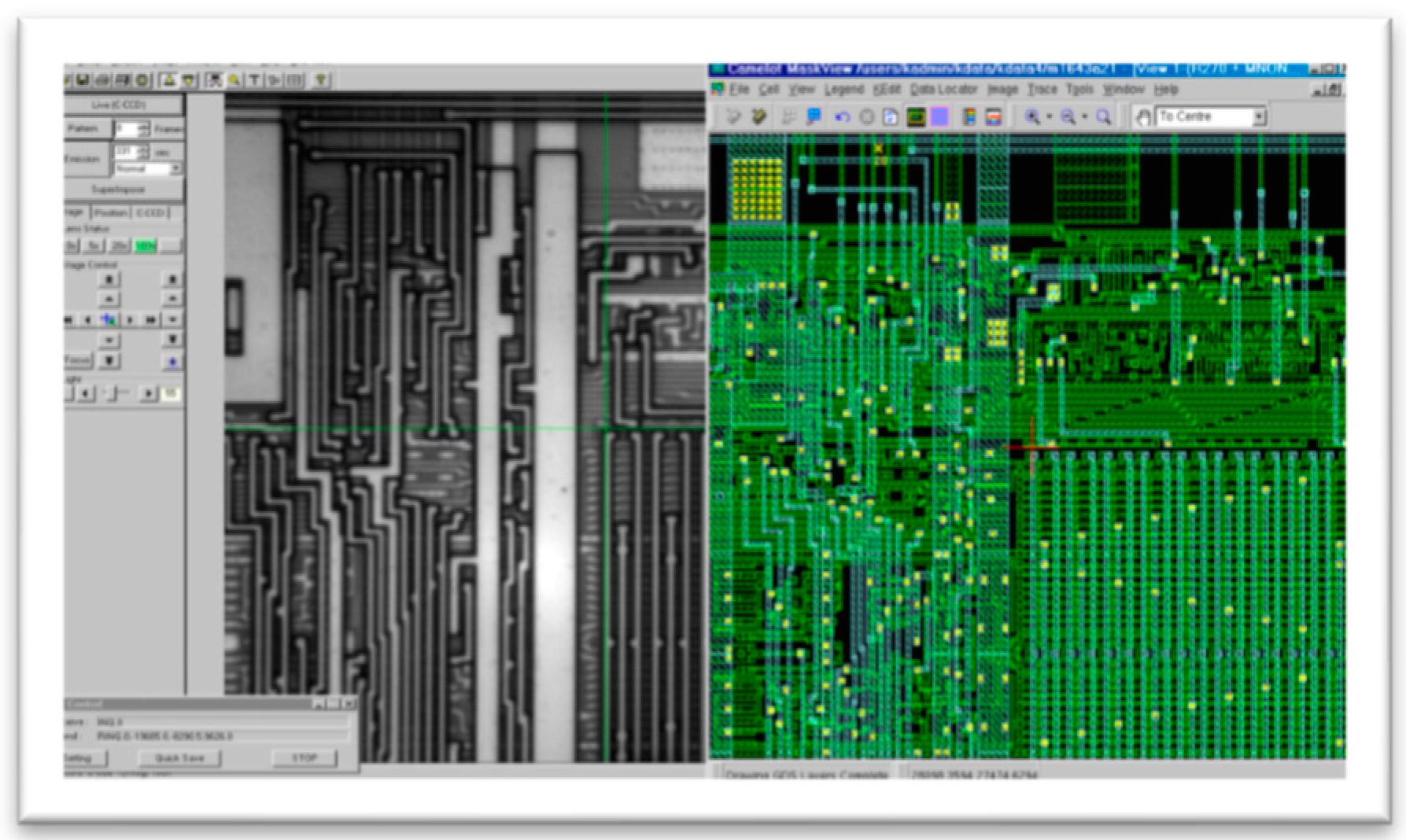

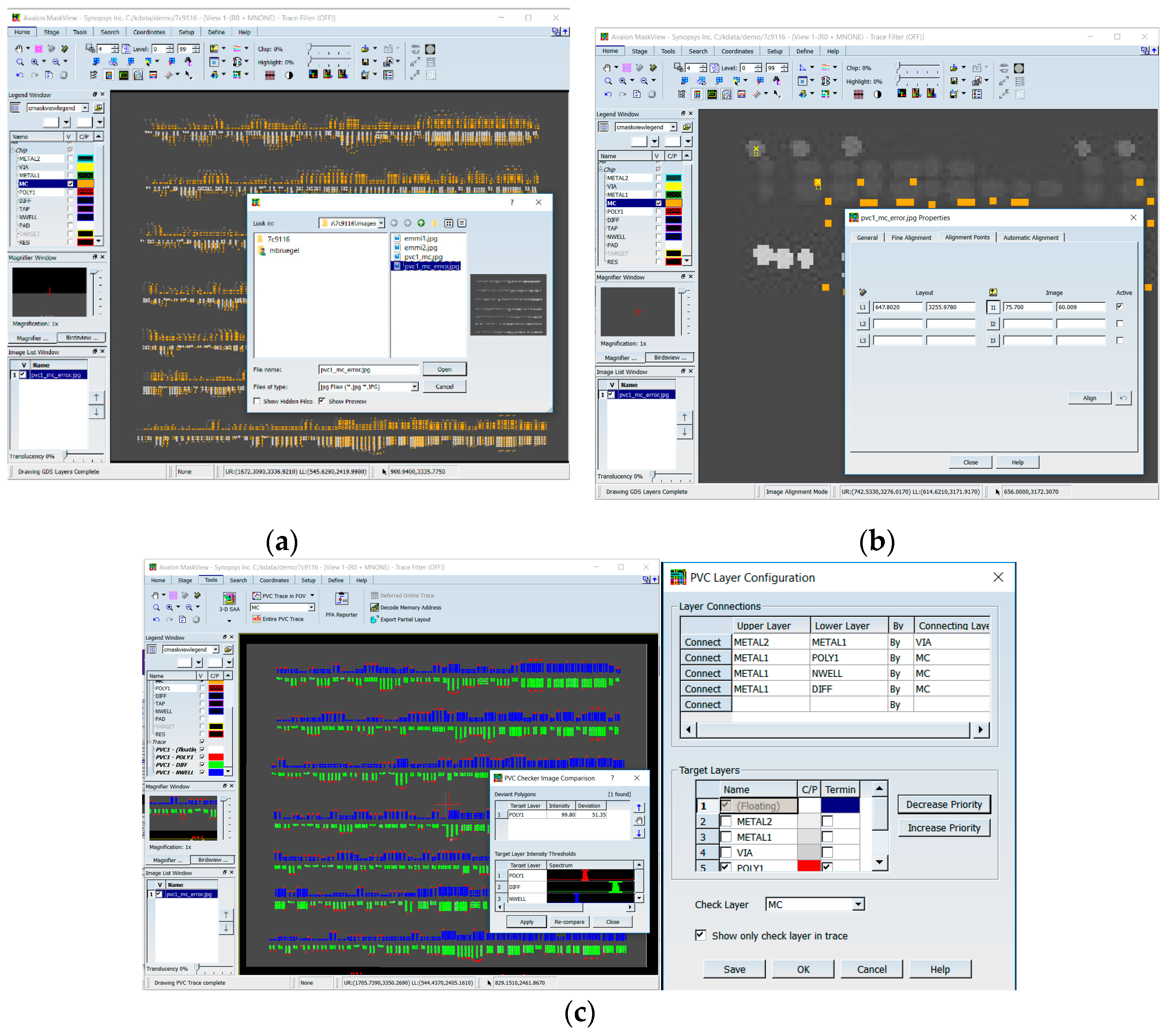

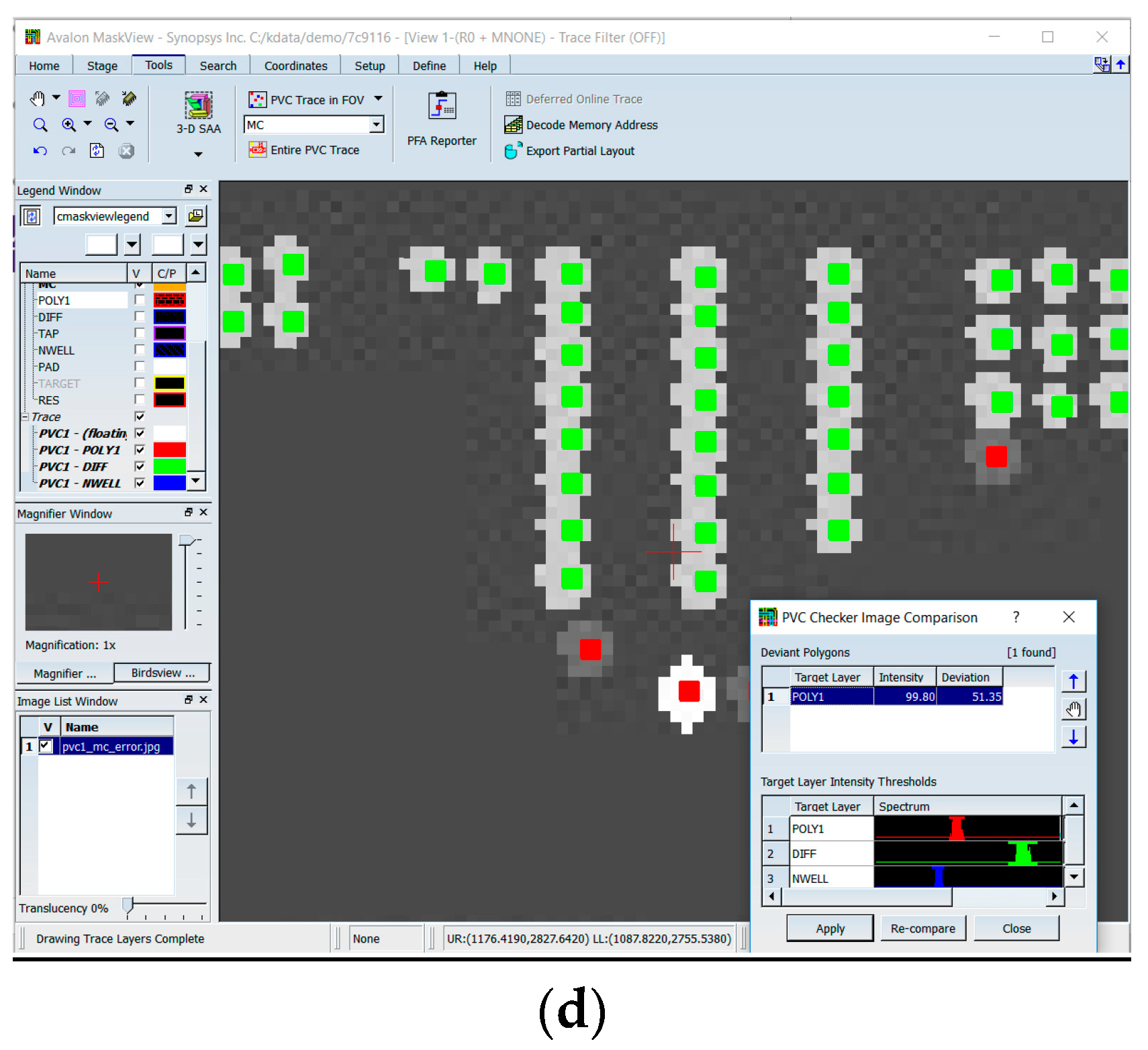

- Image Mapper: Avalon’s capability to communicate with the FA tools for synchronization and alignment. It automates the image alignment process in Avalon MaskView and saves time and effort spent in manual alignment. The image loading feature in MaskView enhances the process of overlaying the defect candidates in the layout viewer. Figure 9 shows an image overlay in Avalon.

- Export Partial Layout: Enables the customer to share partial layout data with service labs without compromising the intellectual property (IP) of the product.

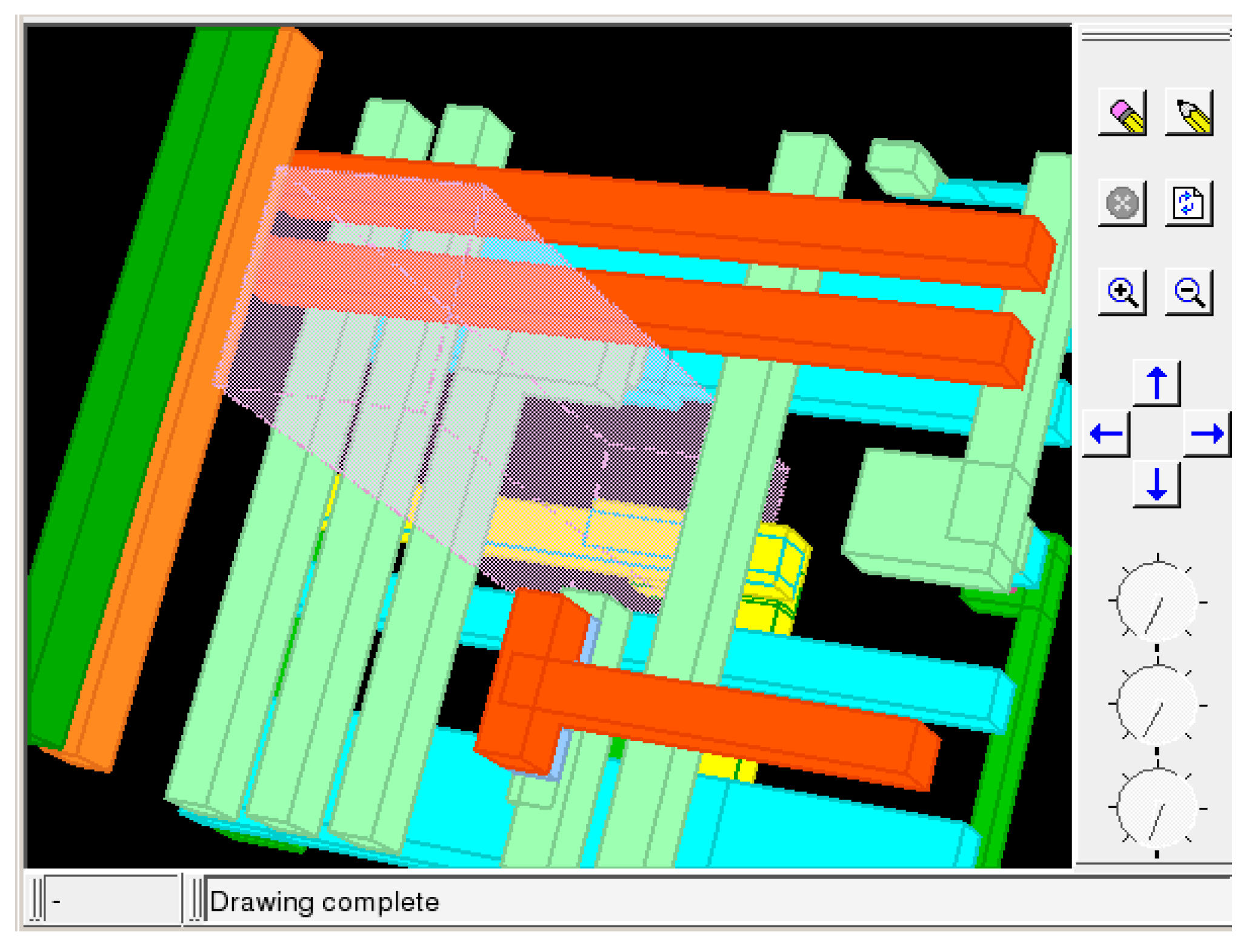

- Advanced three-dimension (3D) Viewer: Displays real time 3D view of the selected layout area. It shows each process step in the 3D view for which it uses the process data along with design data. It zooms into smaller details and helps minimize unintended consequences during focused ion beam (FIB) cuts, due to the underneath high-density structure.

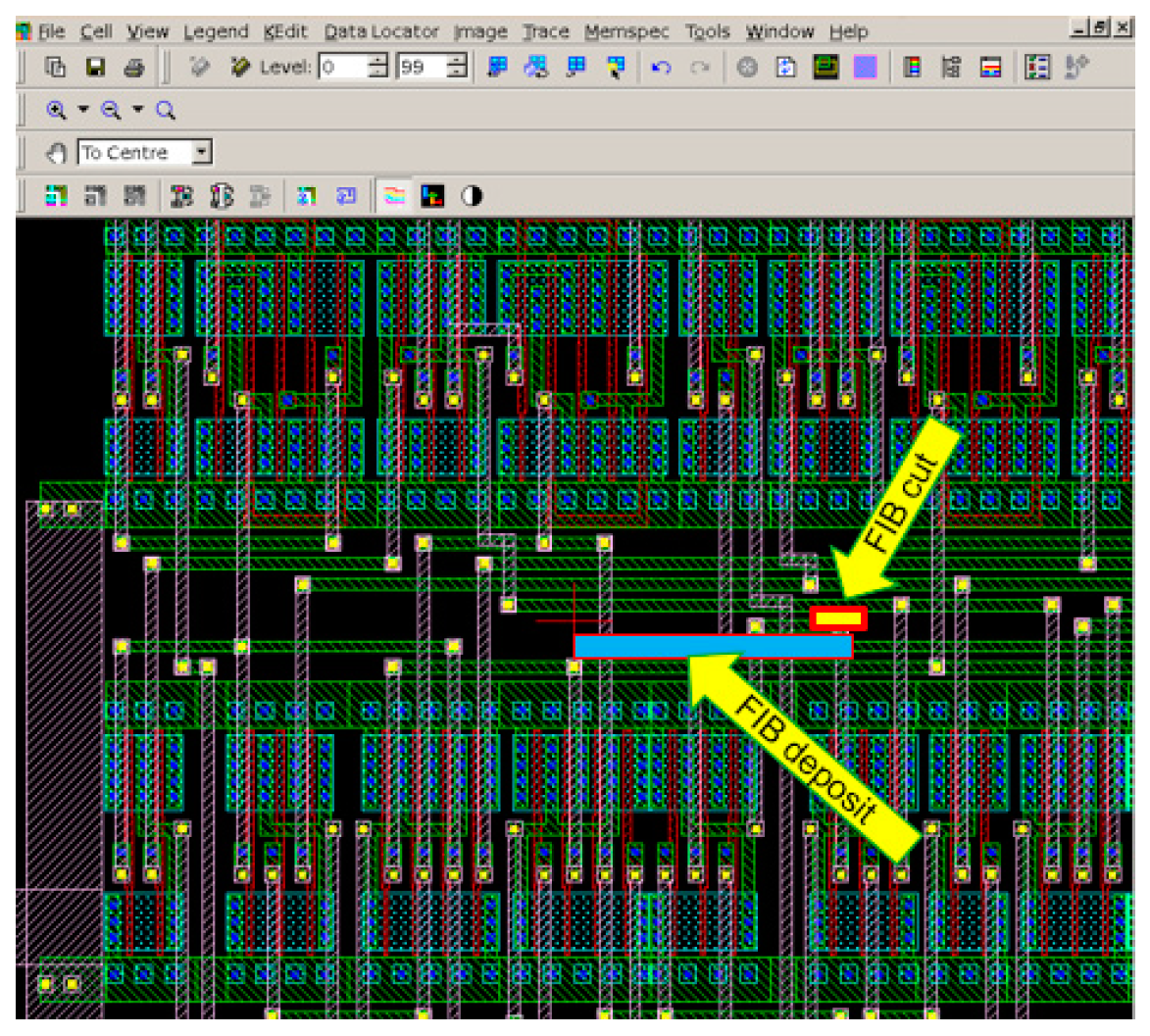

- Electronic Virtual Layer marks objects to represent net connectivity during FIB deposit or cut using KEdit (see Figure 10). The online trace will simulate the new connectivity to the virtual layer.

- 3D view of the layout for better visibility of the FIB simulation: provides a three-dimensional cross-section capability to FA engineers, enabling faster localization of circuit failures to accelerate IC manufacturing yield improvement. Figure 11 shows a 3D analysis that enables faster localization of circuit failures.

3. Methods of Fault Identification and Localization for Yield Improvement

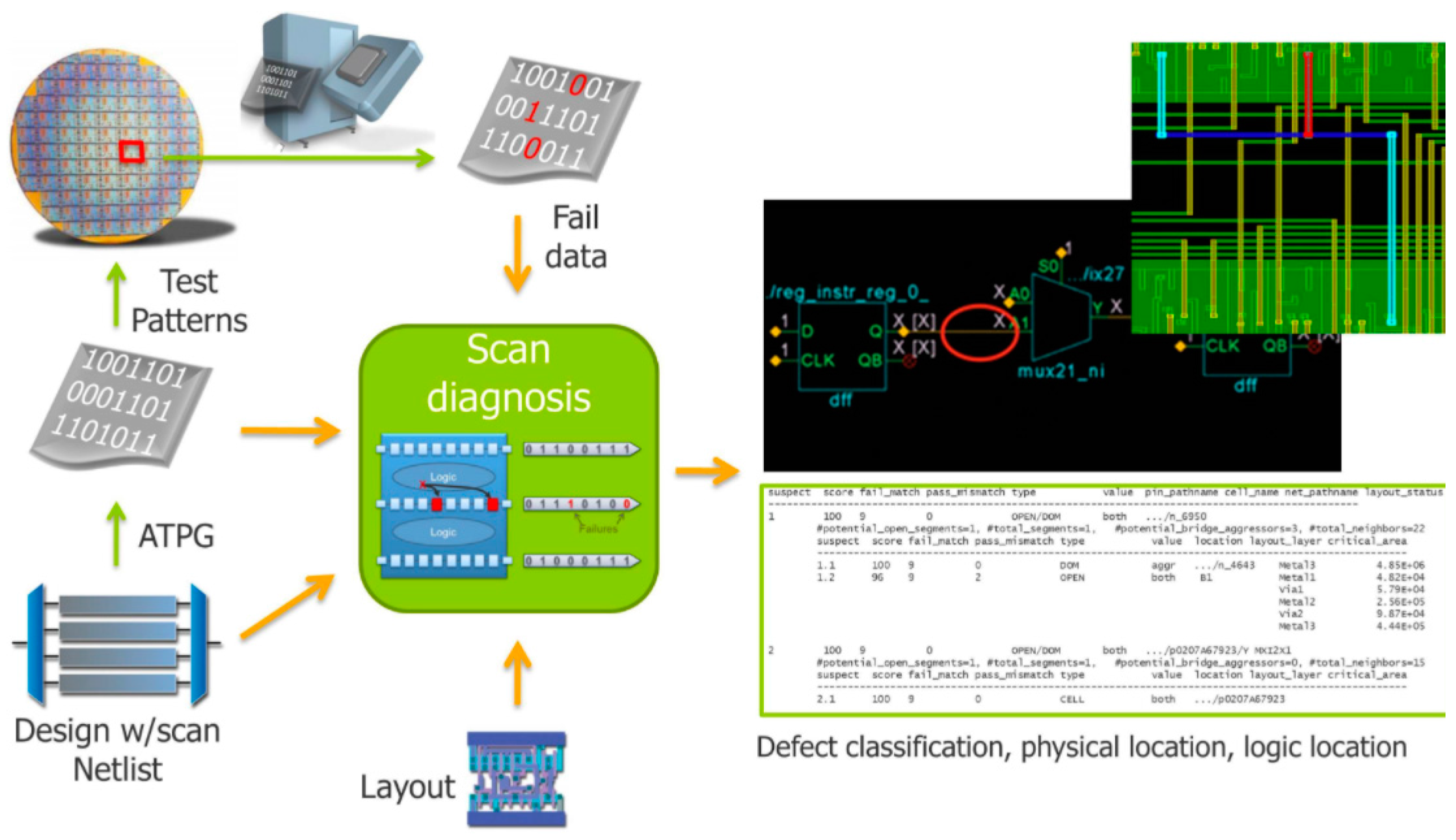

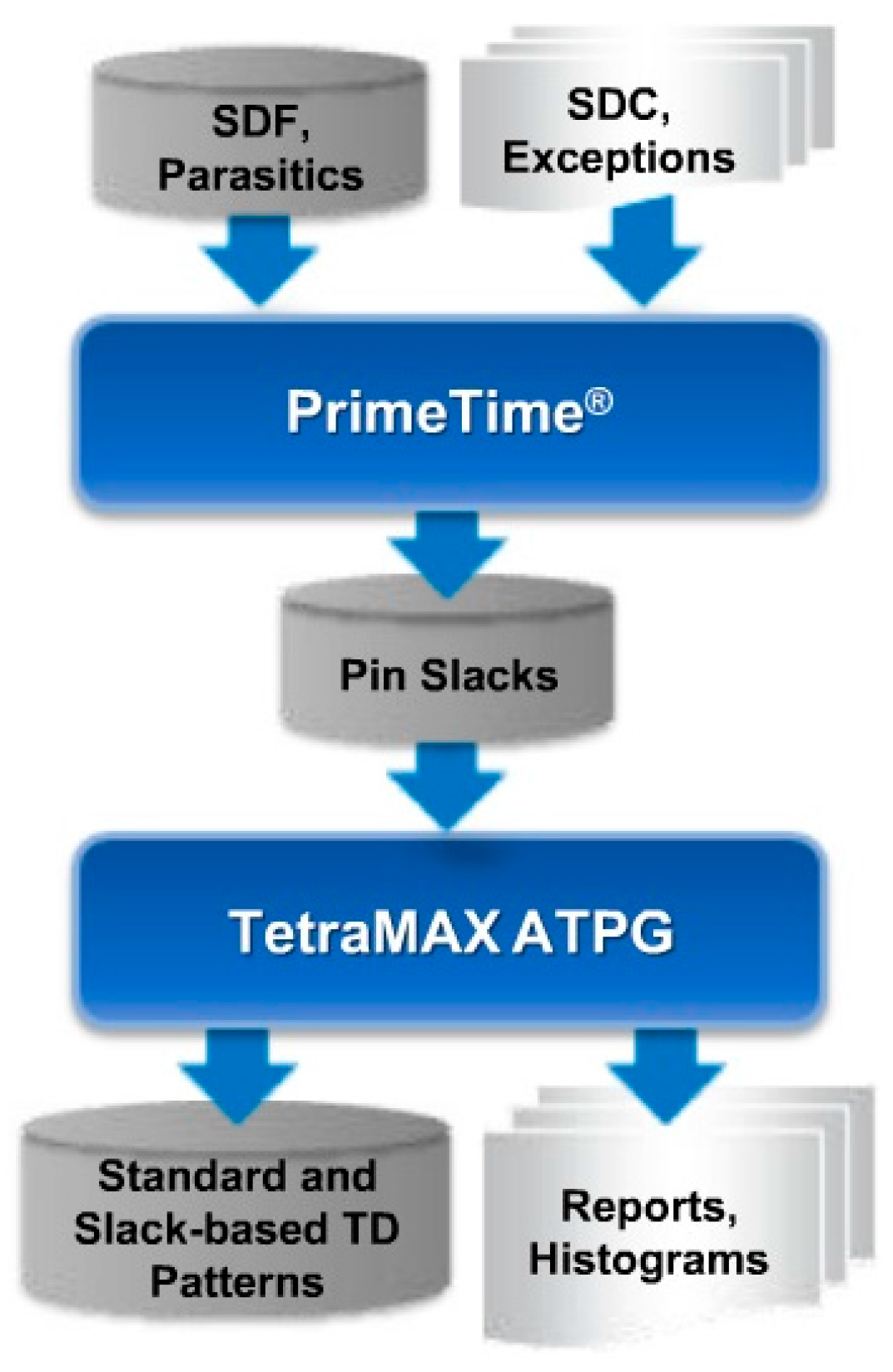

3.1. Software-Based Scan Chain Approach

3.2. Hardware-Based Scan Chain Approach

3.3. Layout Aware Diagnosis

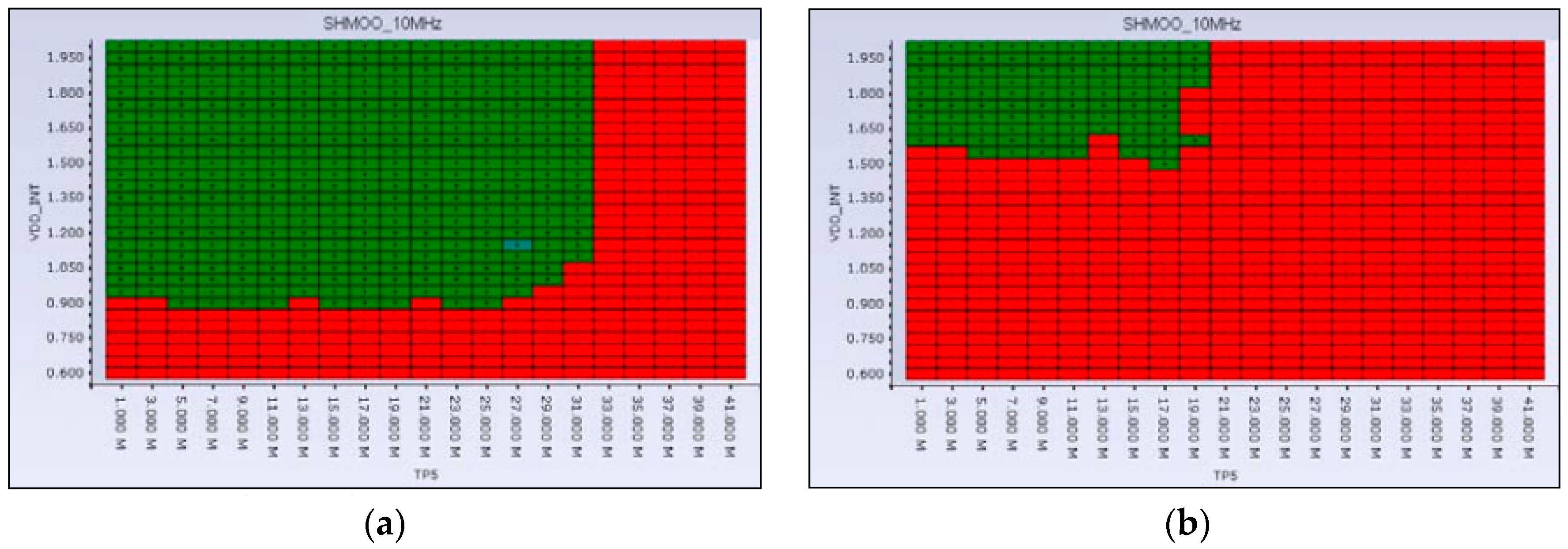

3.4. Case Study 1: Digital Circuit Failure

3.5. Case Study 2: Scan Chain Failure

- Stuck at Fault models: In this model, one of the signal lines in a circuit is assumed to be stuck at a fixed logic value either 0 or 1. If a node, regardless of what inputs are supplied to the circuit always remains at logic 1 or 0, it is referred to as stuck at 1 or stuck at 0 fault regardless of what inputs are supplied to the circuit.

- Transistor Faults: This model is used to describe faults for CMOS logic gates. At the transistor level, a transistor maybe stuck-short or stuck-open. In stuck-short, a transistor behaves as it is always conducting (i.e., stuck at the ON state) and stuck-open is when a transistor never conducts current (or stuck-off). Stuck-short will produce a short between VDD and VSS.

- Bridging Faults: A short circuit between two signal lines is called bridging faults. Bridging to VDD or VSS is equivalent to stuck at fault model.

- Open Faults: In an open fault a wire is assumed broken and one or more inputs are disconnected from the output that should drive them. As with bridging faults, the resulting behavior depends on the circuit implementation.

- Delay Faults: Delay faults can be of different types like the Gate delay fault, Transition fault, Hold Time fault, Slow/Small delay fault, Path delay fault.

- Passive voltage contrast (PVC)

- Biased voltage contrast

- Capacitive-coupled voltage contrast

- Electron beam probing.

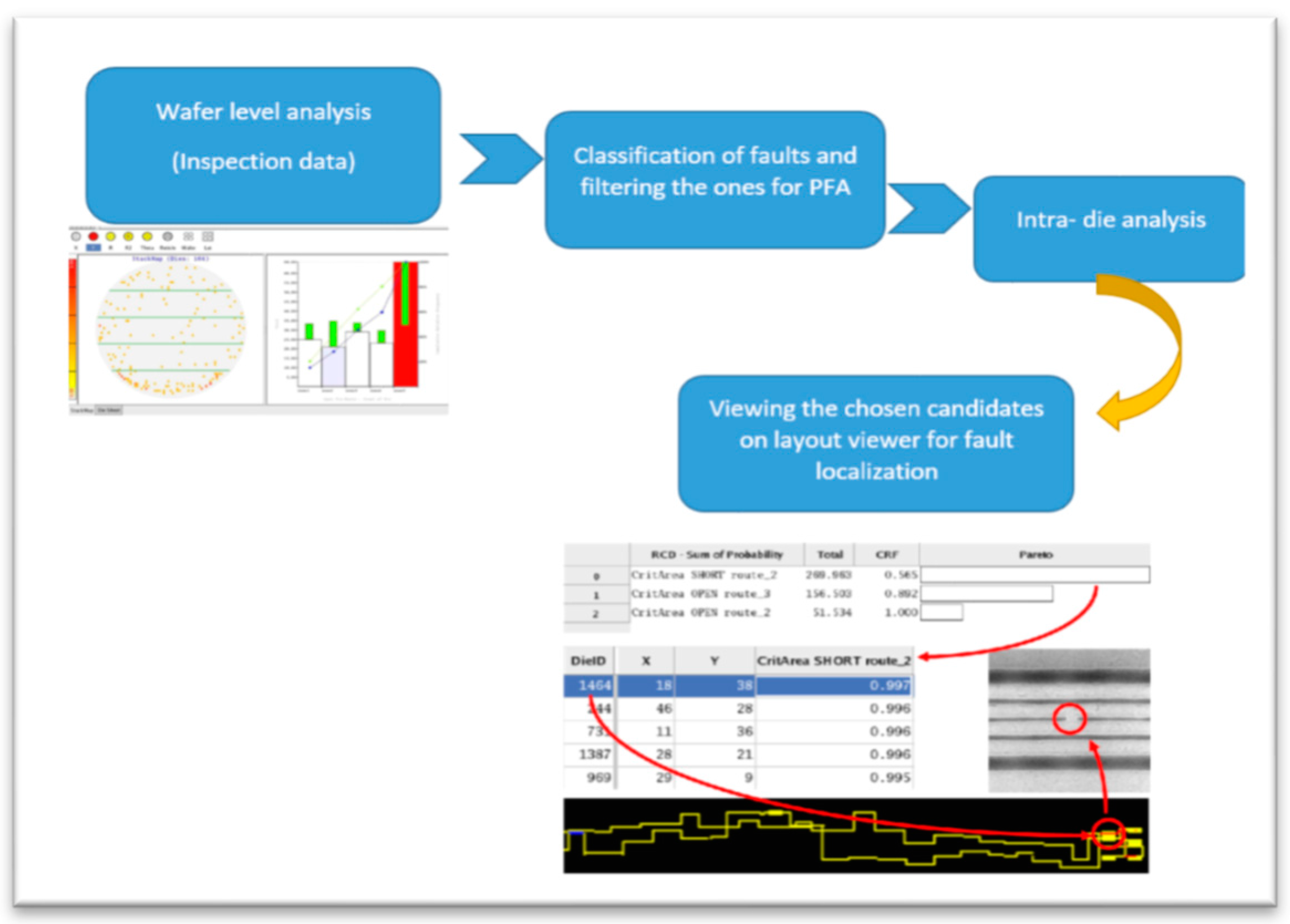

3.6. Wafer Navigation

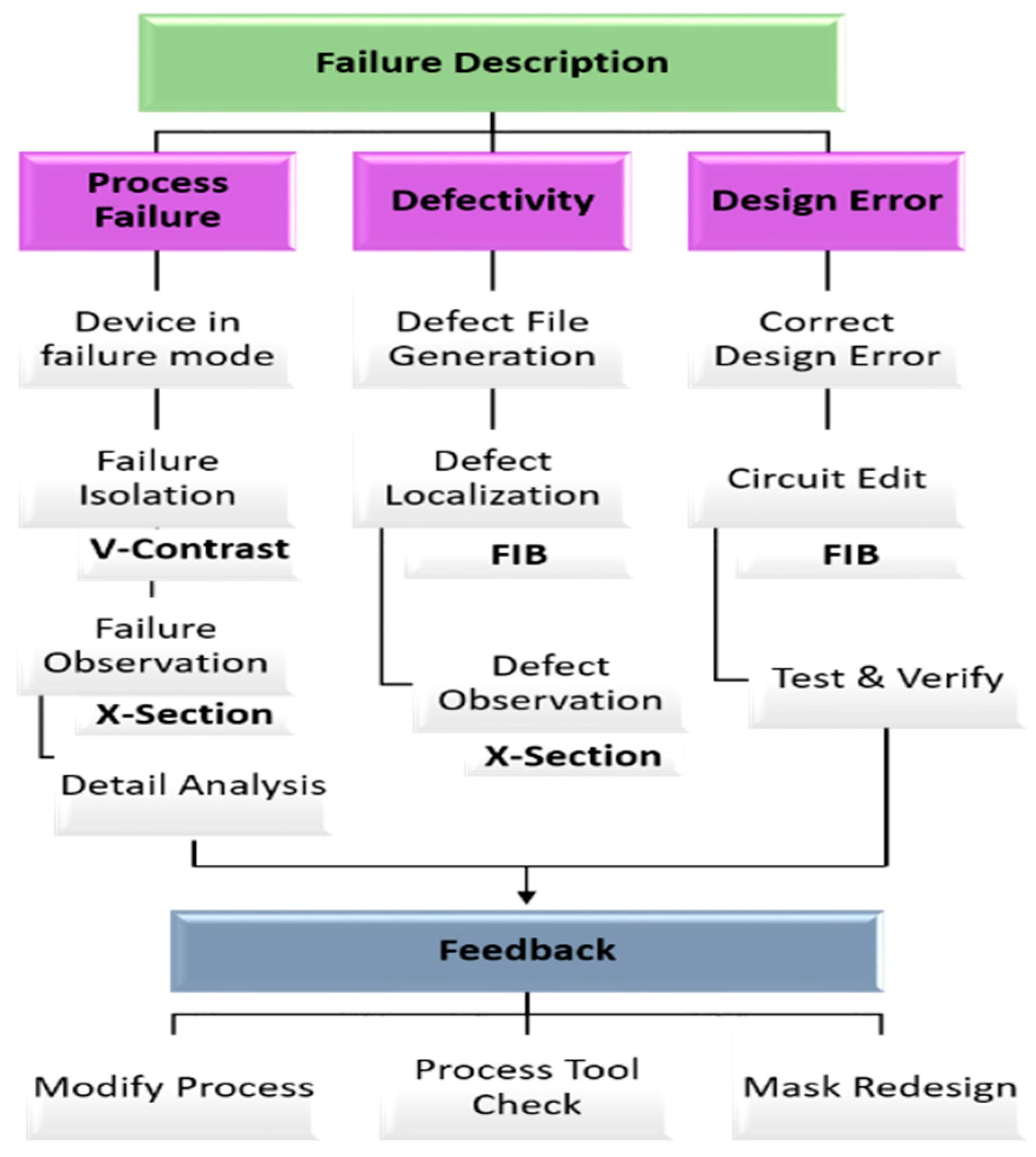

- Process integration issues

- Process induced defects (PID)

- Random particle from equipment and environment

- Device design problems.

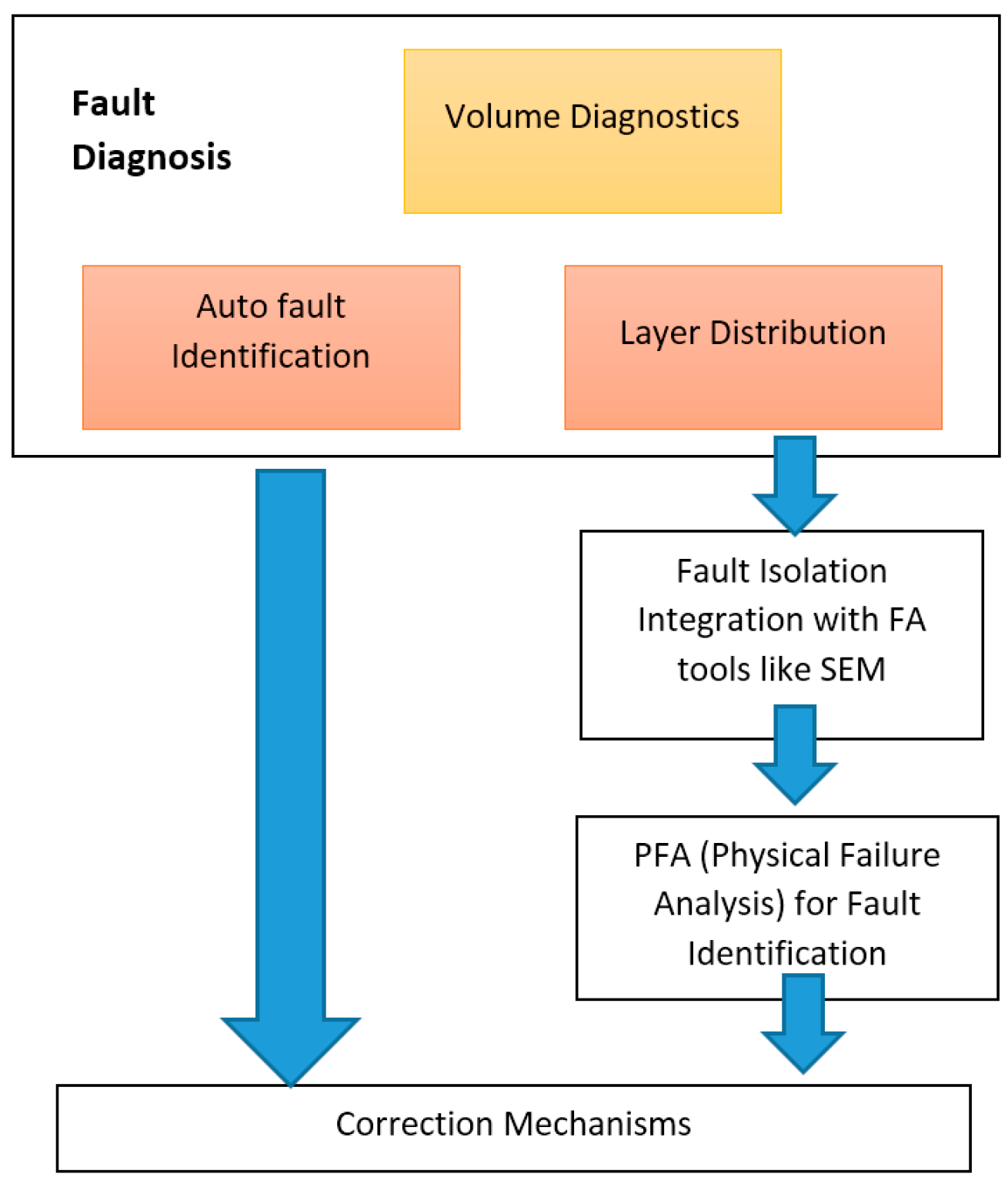

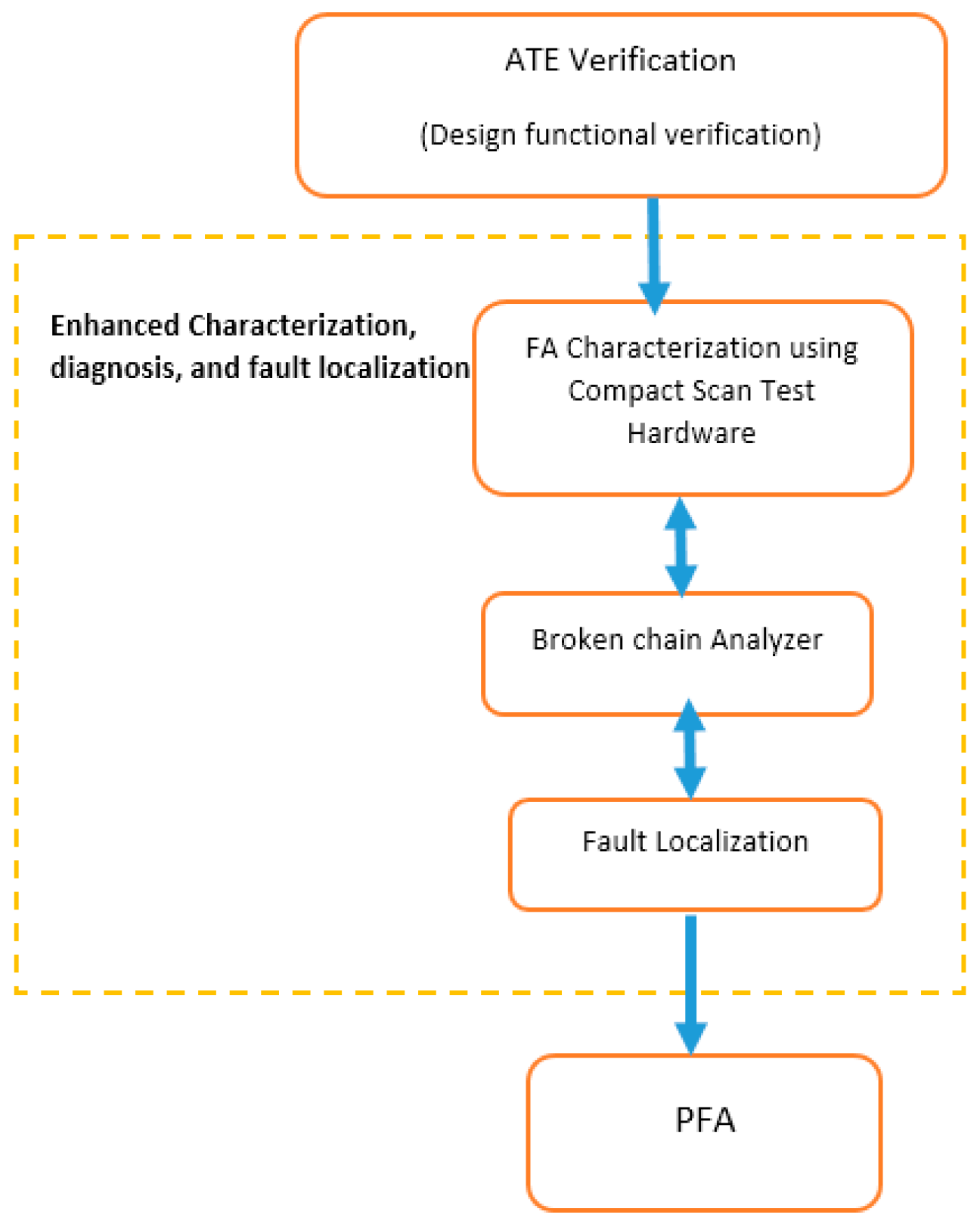

4. Use Flows of Physical Failure Analysis

- Volume diagnosis using tools like Yield Explorer to get potential candidates.

- Confirmation of potential candidates

- Loading and analyzing candidates in Avalon

- Using the Avalon cross-mapping feature to find failing devices/nets.

- Use the Kedit/Data locator feature to mark the desired area for correction/PFA which along with the extracted KDB for that region is sent to the FAB for the PFA.

- SEM cross-section at area of interest.

- Comparison of results: The cross-sectional view in Avalon and the actual SEM image helps view the changes/defects in the chip.

- Aligning layout and equipment

- Correction process/circuit edit (cut/deposit).

- Detection of avalanche luminescence from junction breakdowns, junction defects, currents due to saturated MOS transistors and transistor hot electron effects

- Detection of dielectric electroluminescence from current flow through SiO2 and SiN.

5. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Wang, J.; Hao, Y. Yield modeling of arbitrary defect outline. In Proceedings of the 8th International Conference on Solid-State and Integrated Circuit Technology, Shanghai, China, 23–26 October 2006. [Google Scholar]

- Rencher, M. Physical DFY Technique Improve Yields. EE Times, March 2004. [Google Scholar]

- Asami, T.; Nasu, H.; Takase, H. Oyamatsu. In Proceedings of the IEEE/SEMI Advanced Semiconductor Manufacturing Conference and Workshop, Boston, MA, USA, 4–6 May 2004; pp. 448–452. [Google Scholar]

- Ferris-Prabhu, V. Modeling the critical area in yield forecasts. IEEE J. Solid-State Circ. 1985, 20, 874–878. [Google Scholar] [CrossRef]

- Ferris-Prabhu, V. Defect size variation and their effect on the critical area. IEEE J. Solid-State Circ. 1985, 20, 878–880. [Google Scholar] [CrossRef]

- De Vries, D.K.; Simon, P.L.C. Calibration of open interconnect yield models. In Proceedings of the 18th IEEE International Symposium on Defect and Fault Tolerance in VLSI Systems, Boston, MA, USA, 5 November 2003. [Google Scholar]

- Allan, G.; Walton, A. Efficient extra material critical area algorithms. IEEE Trans. Comput. Aided Des. Integr. Circ. Syst. 1999, 18, 1480–1486. [Google Scholar] [CrossRef]

- Allan, G.; Walton, A. Critical area extraction of VLSI devices for soft fault estimation. IEEE Trans. Semicond. Manuf. 1998, 1, 146–154. [Google Scholar] [CrossRef]

- Wang, J.; Hao, Y.; Liu, H.; Jing, M. Yield modeling based on circular defect size and a real defect rectangular degree. In Proceedings of the International Conference on Solid-State and Integrated Circuit Technology, Beijing, China, 18–21 October 2004; pp. 1104–1107. [Google Scholar]

- Hess, C.; Weiland, L. Issues on the size and outline of killer defects and their influence on yield modeling. In Proceedings of the IEEE/SEMI Advanced Semiconductor Manufacturing Conference and Workshop, Cambridge, MA, USA, 12–14 November 1996; pp. 423–428. [Google Scholar]

- Auvray, E.; Armagnat, P.; Cason, M.; Villab, E.; Jothi, M.; Brugel, M. Evolution of navigation and simulation tools in failure analysis. In Proceedings of the 27th European Symposium on Reliability of Electron Devices, Failure Physics and Analysis, Handel-Halle, Halle (Saale), 19–22 September 2016; pp. 1–8. [Google Scholar]

- Auvray, E.; Armagnat, P.; Saury, L.; Jothi, M.; Brugel, M. Effective scan chain failure analysis method. Microelectron. Reliab. 2017, 201–213. [Google Scholar] [CrossRef]

- Wang, J.; Hao, Y. Segmentation of IC real defect color images based on an LS space. Acta Electron. Sin. 2005, 5, 954–956. [Google Scholar]

- Burmer, C.; Görlich, S. Failure analyses for debug and ramp-up of modern IC’s. Microelectron. Reliab. 2016, 46, 1486–1497. [Google Scholar] [CrossRef]

- Masafumi, N. Logic LSI yield improvement analysis by means of fault diagnosis. NEC Tech. J. 2009, 4, 63–66. [Google Scholar]

- Kim, B.; Hong, J.; Han, Y. Improving yield learning by rapid electrical fault inspection and localization. In Proceedings of the International Symposium on Physical and Failure Analysis of Integrated Circuits, Singapore, 2–6 July 2012; pp. 1–5. [Google Scholar]

- Kuo, F.; Chen, Y. Yield ramp up by scan chain diagnosis. In Proceedings of the Asian Test Symposium, Taichung, Taiwan, 23–26 November 2009. [Google Scholar]

- Chen, H.; Qi, Z.; Wang, L.; Xu, C. A scan chain optimization method for diagnosis. In Proceedings of the IEEE International Conference on Computer Design, New York, NY, USA, 18–21 October 2015; pp. 613–620. [Google Scholar]

- Goh, S.; You, G.; Yeoh, B.; Chan, Y.; Chua Tey, C.; Yap, C.; Lim, T.; Fei, T.; Herrmann, T.; Ho, H.; et al. An effective broken scan chain diagnosis flow combining software and hardware solutions for systematic failures. In Proceedings of the IEEE International Symposium on Physical and Failure Analysis of Integrated Circuits, Singapore, 2–6 July 2012; pp. 1–5. [Google Scholar]

- Estores, R.; Vercruysse, P.; Villareal, K. Failure analysis enhancement by incorporating a compact scan chain diagnosis System. In Proceedings of the International Symposium on Testing and Failure Analysis, Houston, TX, USA, 9–13 November 2014; pp. 436–444. [Google Scholar]

- Pearson, S.; Campos, J.; Just, R.; Fraser, G.; Abreu, R.; Ernst, M.; Pang, D.; Keller, B. Evaluating and improving fault localization. In Proceedings of the IEEE/ACM International Conference on Software Engineering, Alamitos, CA, USA, 20–28 May 2017; pp. 609–620. [Google Scholar]

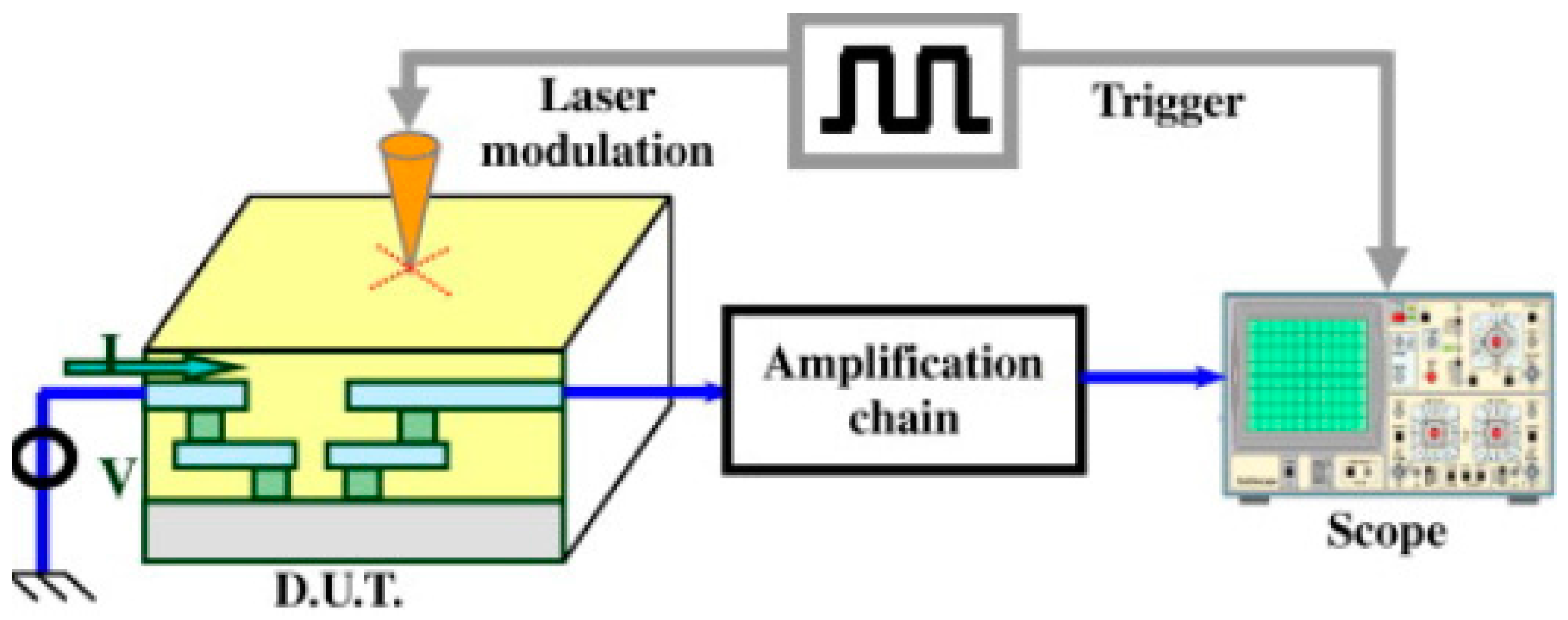

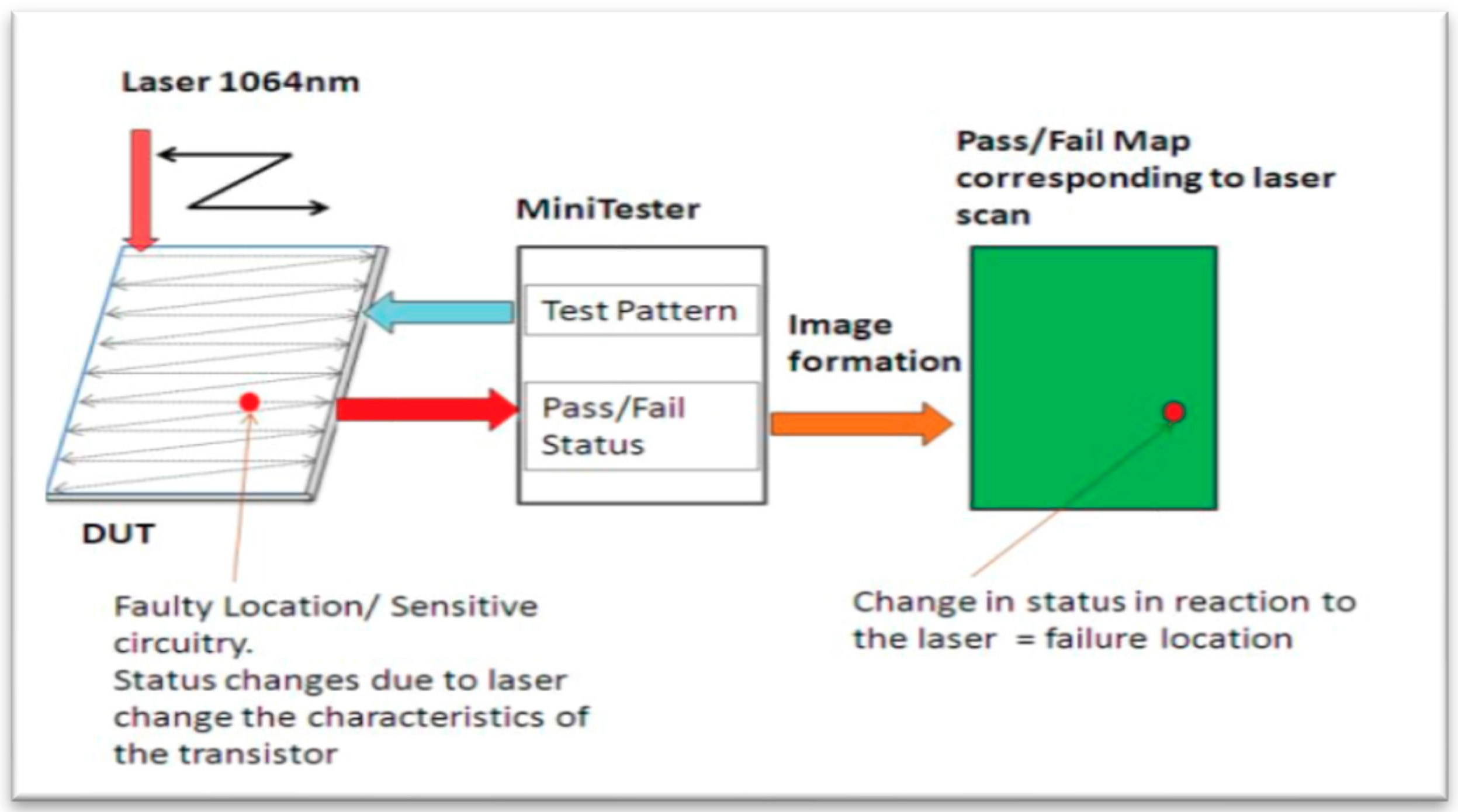

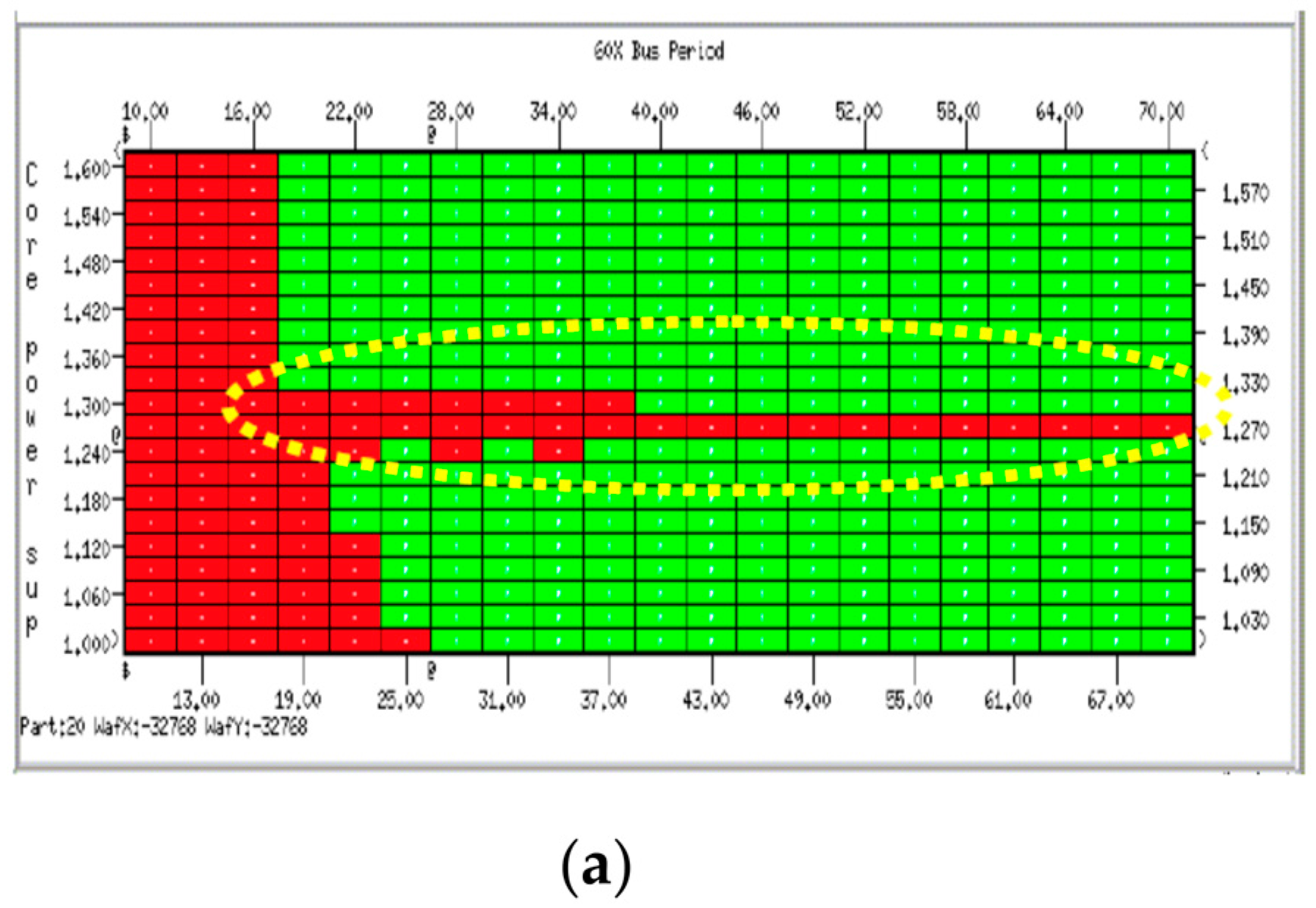

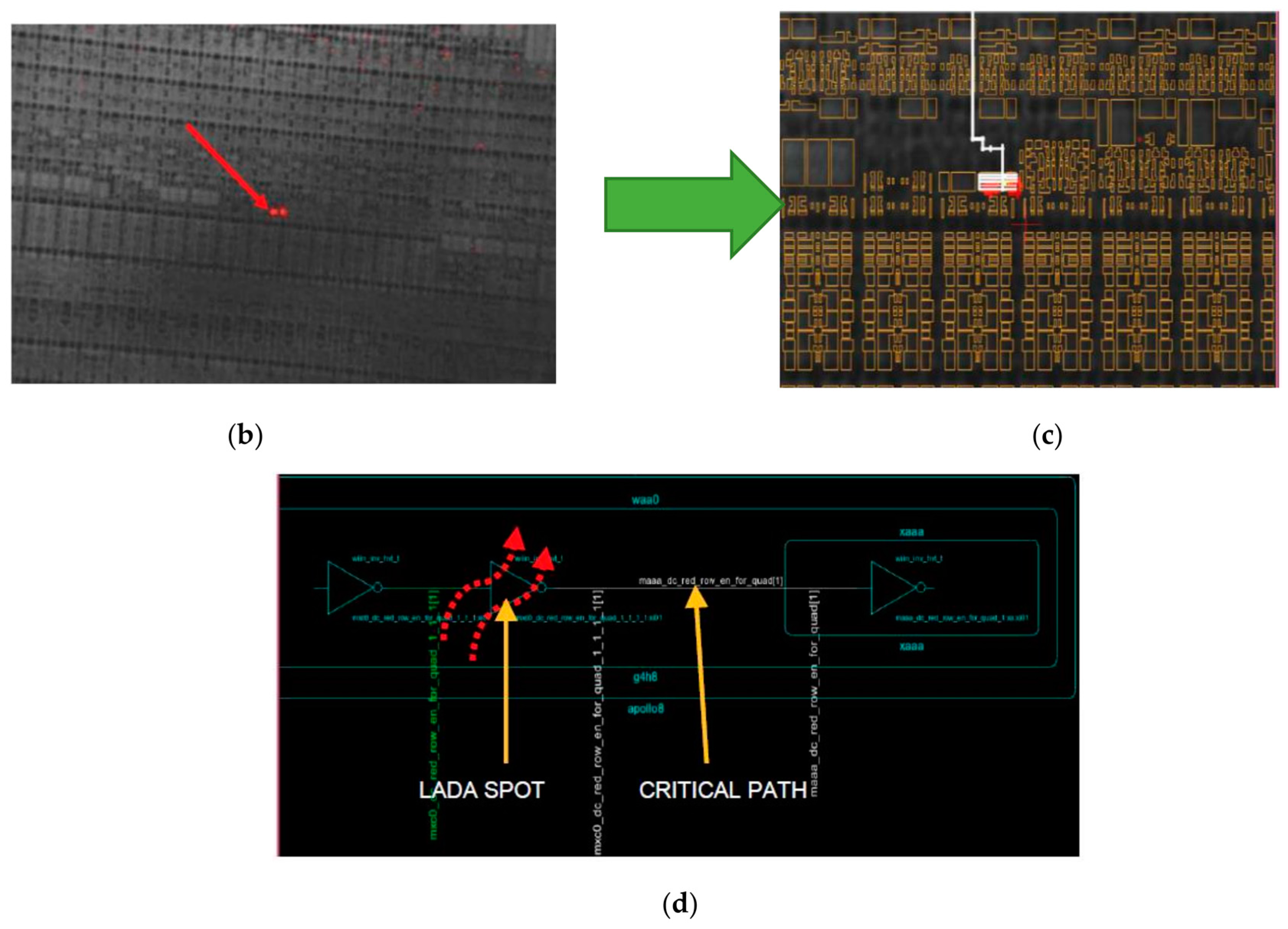

- Rowlette, J.; Eiles, T. Critical timing analysis in microprocessors using near-IR laser assisted device alteration (LADA). In Proceedings of the International Test Conference, Charlotte, NC, USA, 30 September–2 October 2003; pp. 264–273. [Google Scholar]

- Bruce, M. Laser induced techniques for microelectronic failure analysis: SDL and LADA. In Proceedings of the International Symposium for Testing and Failure Analysis, San Jose, CA, USA, 3–7 November 2013; pp. 56–63. [Google Scholar]

- Sheng, F.; Siew, R.; Mun, S.; Ting, D.; Teck, K. Laser assisted device alteration (LADA) for fault isolation and quick design in marginality failure. In Proceedings of the IEEE Symposium on Physical Failure Analysis and Integrated Circuits, Hsinchu, Taiwan, 29 June–2 July 2015; pp. 9–12. [Google Scholar]

- Rosenkranz, R. Failure localization with active and passive voltage contrast in FIB and SEM. J. Mater. Sci. 2011, 22, 1523. [Google Scholar] [CrossRef]

- Henderson, C. Passive Voltage Contrast. InfoTracks—SemiTracks Monthly Newsletter. Issue 115. November 2016. Available online: https://www.semitracks.com/newsletters/november/2016-november-newsletter.php (accessed on 10 November 2017).

- Lim, Y. Wafer Testing (1D). 3/20/13. Available online: https://uploadwikimedia.org/wikeversity/en/e/ef/SOC.1.D.Test.2013.3.20.pdf (accessed on 1 November 2017).

- Hsiung, S.; Tan, K.; Luo, J. New applications of the infrared emission microscopy to wafer-level backside and flip-chip package analyses. In Proceedings of the IEEE International Integrated Reliability Workshop, Lake Tahoe, CA, USA, 21–24 October 2012; pp. 147–150. [Google Scholar]

- Carleson, P.; Donnet, D.; Sidorov, O.; Rue, C. Delayering on advanced process technologies using FIB. In Proceedings of the IEEE International Symposium on Physical and Failure Analysis of Integrated Circuits, Singapore, 30 June–4 July 2014. [Google Scholar]

- Chen, Y.; Zhang, X. Focused ion beam technology and application in failure analysis. In Proceedings of the International Conference on Electronic Packaging Technology & High Density Packaging, Xi’an, China, 16–19 August 2010; pp. 957–960. [Google Scholar]

- Yee, P.; Sing, L. Application of atomic force microscopy in IC/discrete failure analysis. In Proceedings of the International Symposium on Physical and Failure Analysis of Integrated Circuits, Suzhou, China, 15–19 July 2013; pp. 449–454. [Google Scholar]

- Leong, H.W.; Zhang, O.; Lee, W.; Hoe, C.; Lin, R. C-AFM analysis of advanced IC on SRAM high resistance failure. In Proceedings of the International Symposium on Physical and Failure Analysis of Integrated Circuits, Singapore, 2–6 July 2012; pp. 1–3. [Google Scholar]

- Chapter 1: Introduction to Photon Emission Microscopy and Spectroscopy. Available online: scholarbank.nus.edu.sg (accessed on 10 November 2017).

- Shearer, J.; Le, L.; Yang, X.; Cleeves, M.; Meeks, A. Identification of an IDDQ failure mechanism using a variety of front and backside analytical techniques. In Proceedings of the International Symposium for Testing and Failure Analysis, Santa Clara, CA, USA, 1 October 2003. [Google Scholar]

- Lee, N.; Yong, F.; Nordin, N. TEM and chemical preferential etching analysis of protected FET leakage failure. In Proceedings of the International Symposium on Physical and Failure Analysis of Integrated Circuits, Hsinchu, Taiwan, 29 June–2 July 2015. [Google Scholar]

- Zhu, J.; Wang, Q.; Chen, C.; Neo, S.; Du, A.; Hua, Y. FIB sample preparation for TEM failure analysis of advanced devices. In Proceedings of the International Symposium on Physical and Failure Analysis of Integrated Circuits, Singapore, 5–9 July 2010; pp. 1–5. [Google Scholar]

- Stark, T.; Russell, P.; Nevers, C. 3-D defect characterization using plan view and cross-sectional TEM/STEM analysis. In Proceedings of the 31st International Symposium for Testing and Failure Analysis, San Jose, CA, USA, 6–10 November 2005; pp. 344–349. [Google Scholar]

- Soo, C.; Liu, B.; Er, E.; Zhao, S.; Lam, J.; Liu, W.; Mun, J. Study on the poly bump defect by TEM failure analysis. In Proceedings of the International Symposium on Physical and Failure Analysis of Integrated Circuits, Hsinchu, Taiwan, 29 June–2 July 2015; pp. 299–301. [Google Scholar]

- Hua, Y.; Liu, B.; Mo, Z.; Teong, J. Studies and applications of standardless EDX quantification method in failure analysis of wafer fabrication. In Proceedings of the International Symposium on Physical and Failure Analysis of Integrated Circuits, Singapore, 7–11 July 2008; pp. 1–6. [Google Scholar]

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Oberai, A.; Yuan, J.-S. Efficient Fault Localization and Failure Analysis Techniques for Improving IC Yield. Electronics 2018, 7, 28. https://doi.org/10.3390/electronics7030028

Oberai A, Yuan J-S. Efficient Fault Localization and Failure Analysis Techniques for Improving IC Yield. Electronics. 2018; 7(3):28. https://doi.org/10.3390/electronics7030028

Chicago/Turabian StyleOberai, Ankush, and Jiann-Shiun Yuan. 2018. "Efficient Fault Localization and Failure Analysis Techniques for Improving IC Yield" Electronics 7, no. 3: 28. https://doi.org/10.3390/electronics7030028