Optimal Cascade Non-Integer Controller for Shunt Active Power Filter: Real-Time Implementation

Abstract

:1. Introduction

- Fractional controller is applied due to its having more tunable parameters, which allow for more flexibility to achieve a high accuracy.

- The cascade controller is able to rapidly reject disturbance before it leaks to the other parts of the system.

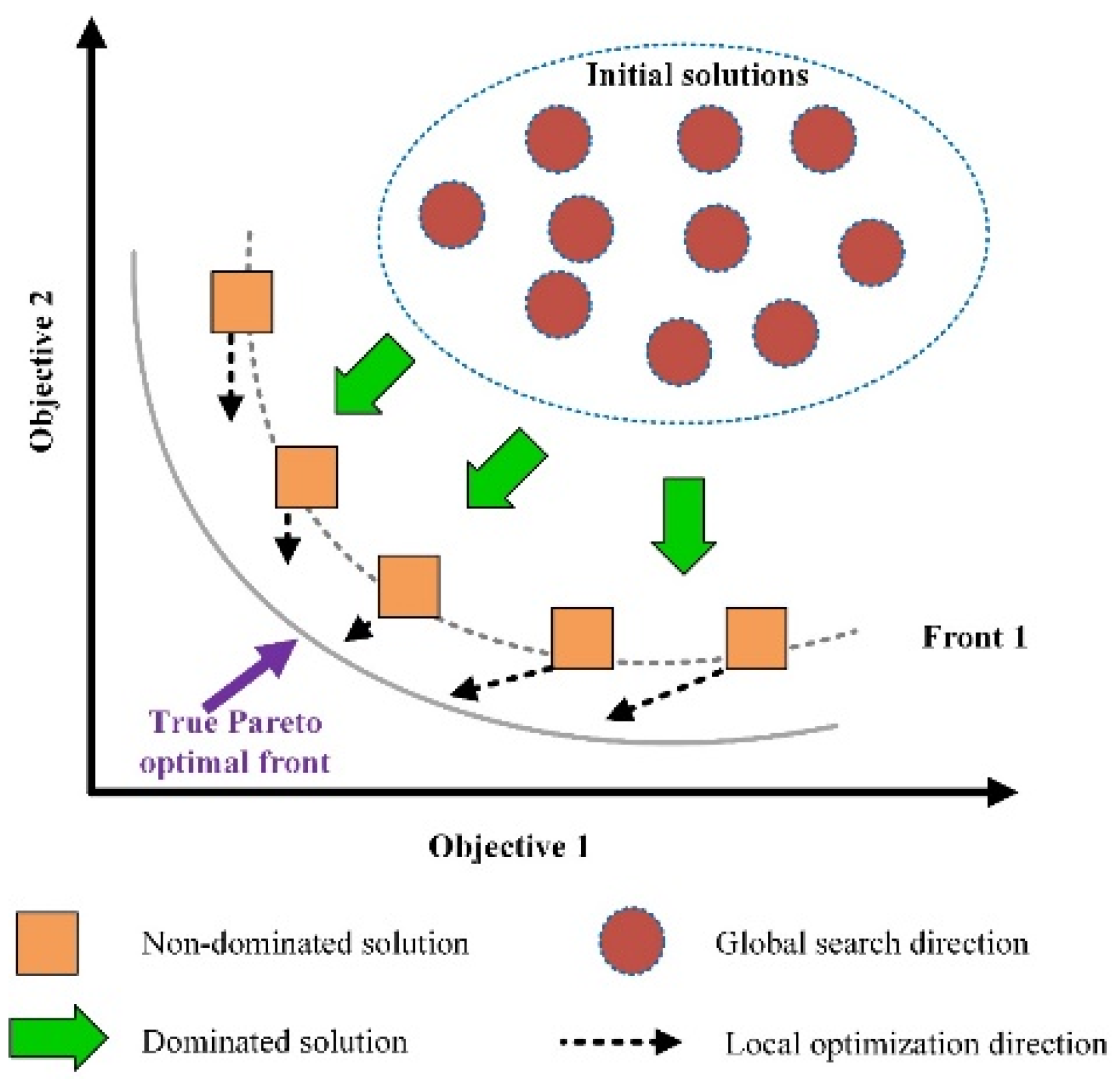

- Multi-objective NSGA-II algorithm offers optimal solutions to multidimensional objective functions, which minimize the THD.

2. Shunt Active Power Filter and Repetitive Controller

3. Fractional Controllers

3.1. Fractional-Order PID Controller (FOPID Controller)

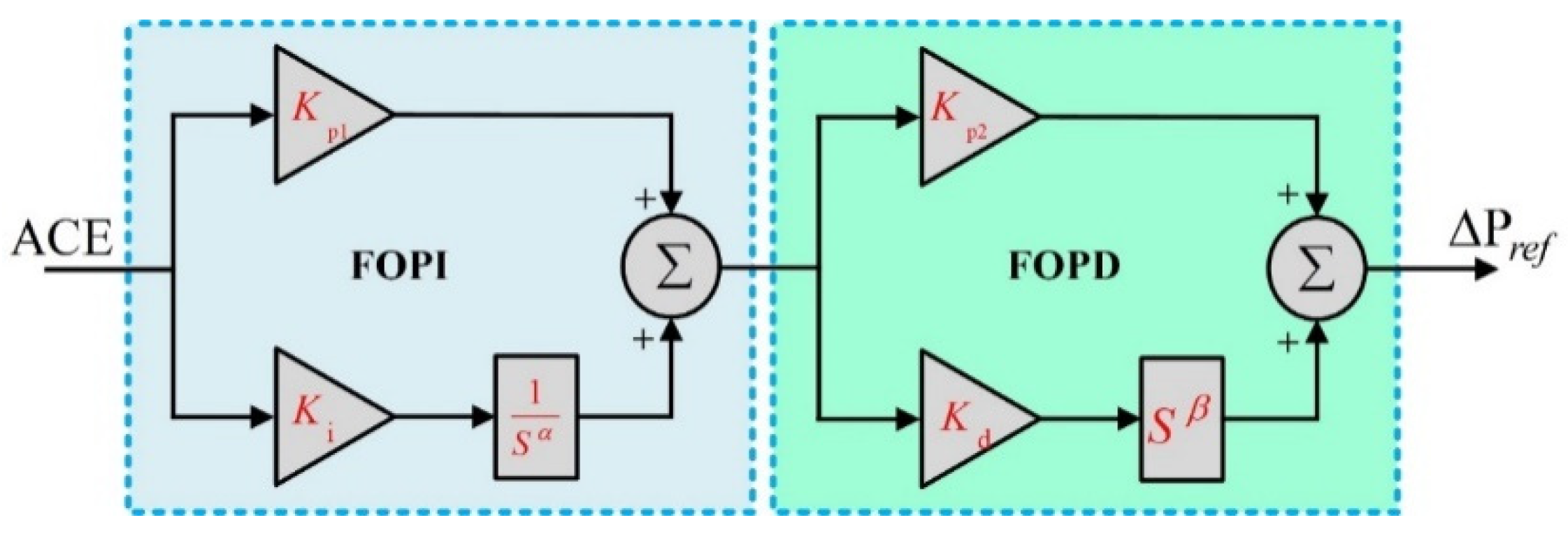

3.2. Fractional-Order (PI + PD) Cascade Controller

3.3. Multistage Fractional-Order PID Controller

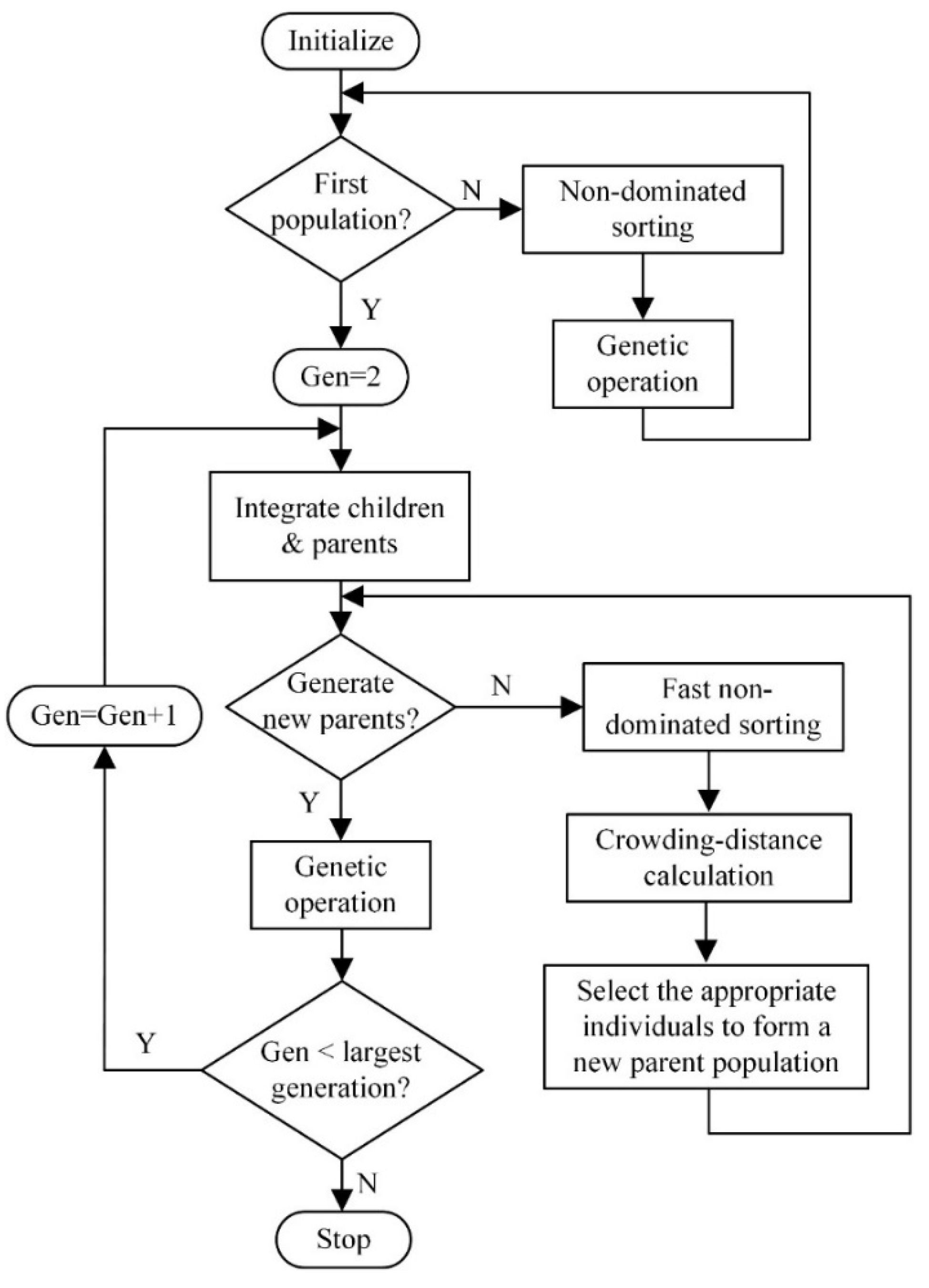

4. NSGA-II Optimization Method and Objective Functions

4.1. NSGA-II: An Overview

- Population initialization:

- 2.

- Non-dominated sorting process based upon non-domination criteria of the population that was initialized.

- 3.

- Crowding distance:

- 4.

- Selection:

- 5.

- Genetic Operators:

- 6.

- Recombination and selection:

4.2. Objective Functions

- Steady-State Response (THD (up to the 50th harmonic) of the source current)

- 2.

- Transient Response (Transient/Settling Time): In electrical engineering, transient response is the response of a system to changes from the equilibrium. The impulse response and step response are transient responses to a specific input (an impulse and a step, respectively).

4.3. Design Parameters

5. Real-Time Simulation Results

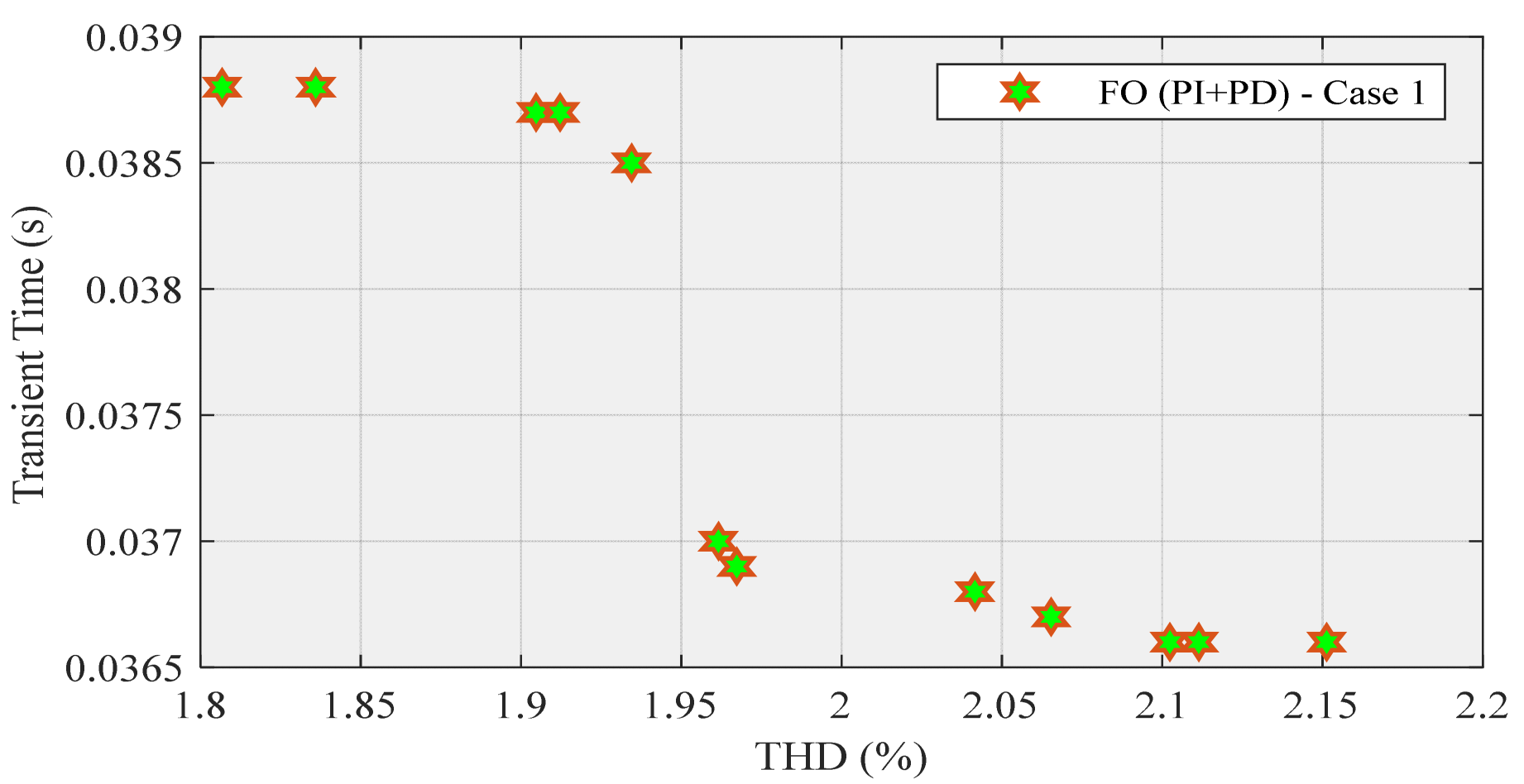

5.1. Case Study 1: THD (up to the 50th Harmonic) and Transient (Rise) Time Must Synchronously Be Minimized

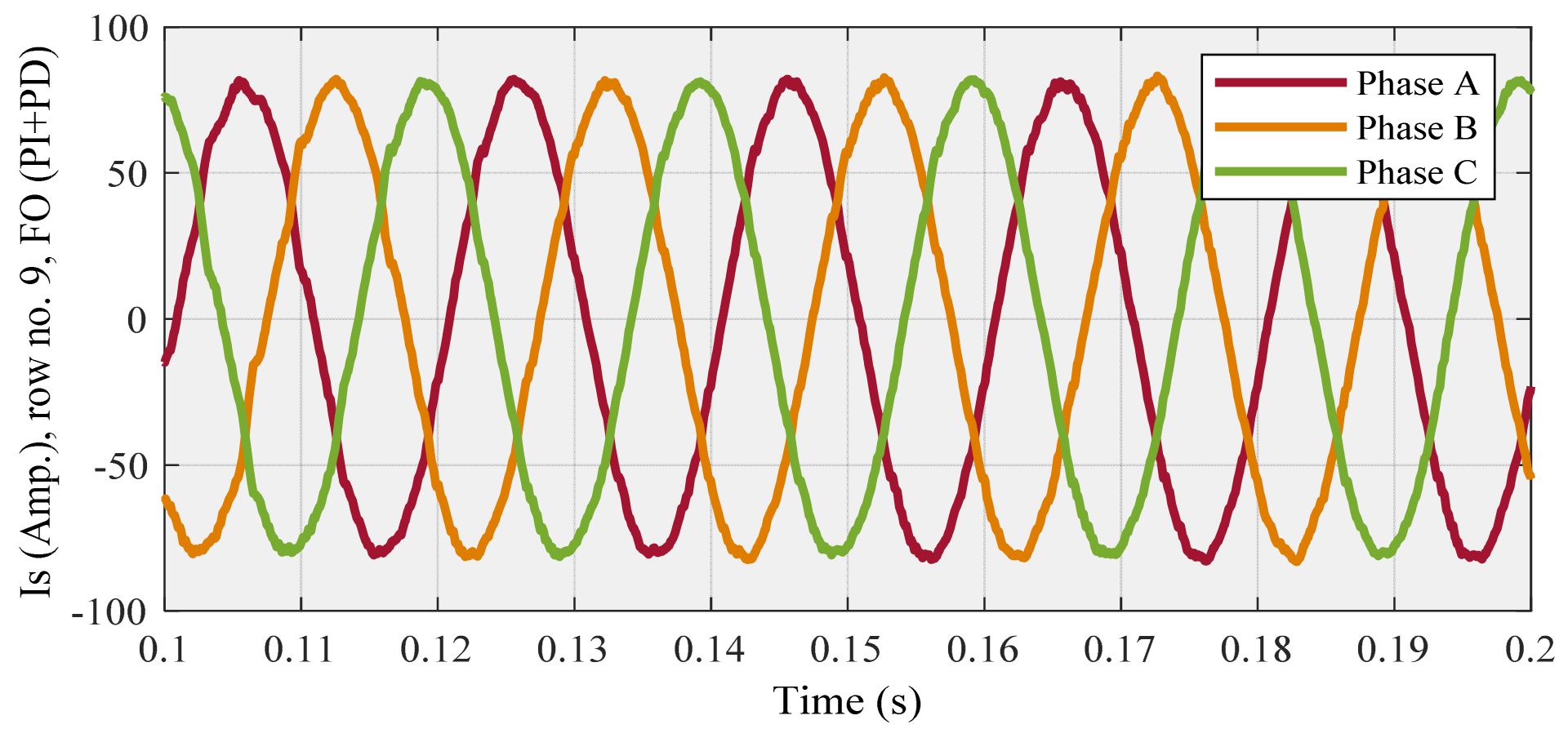

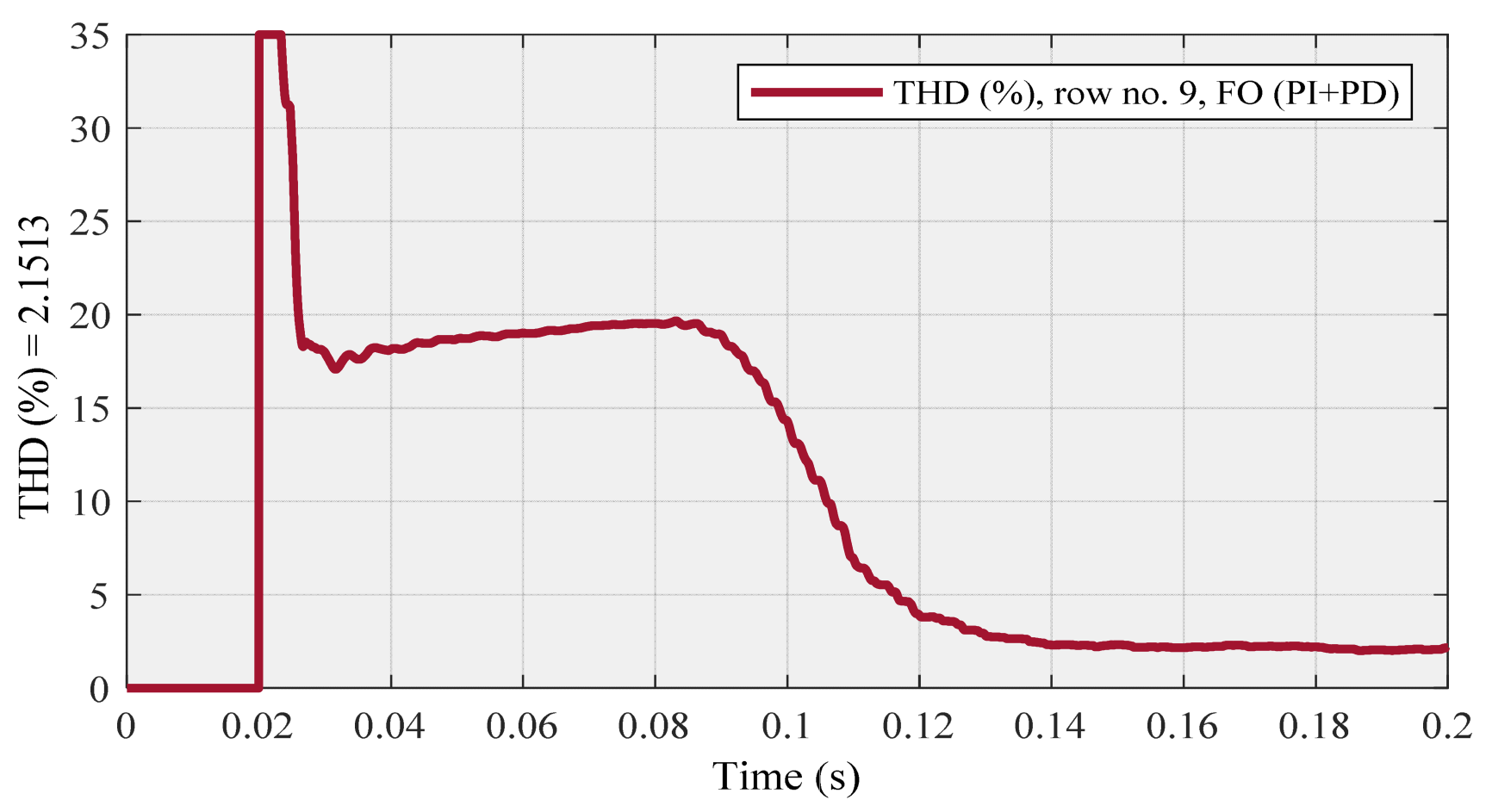

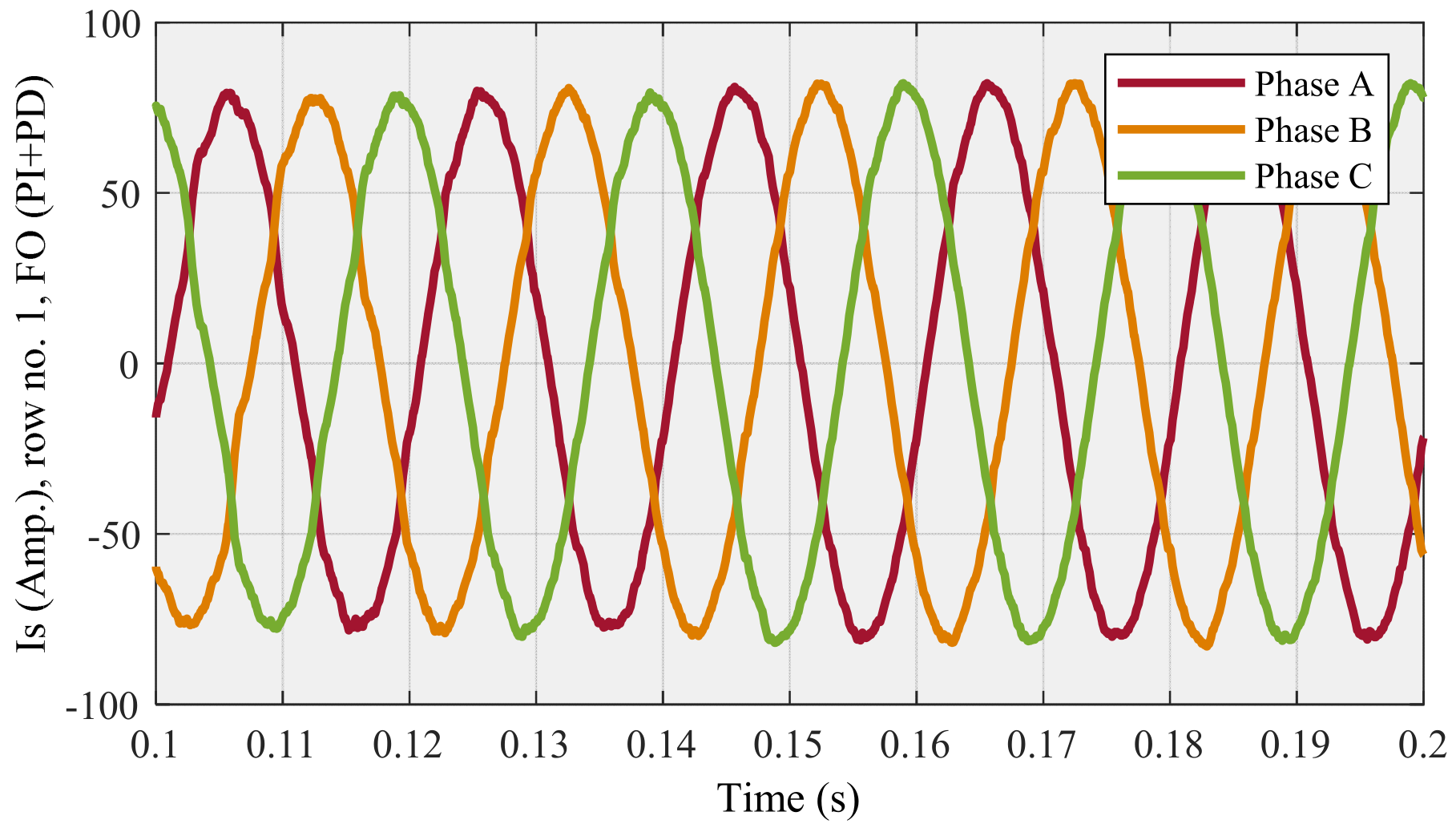

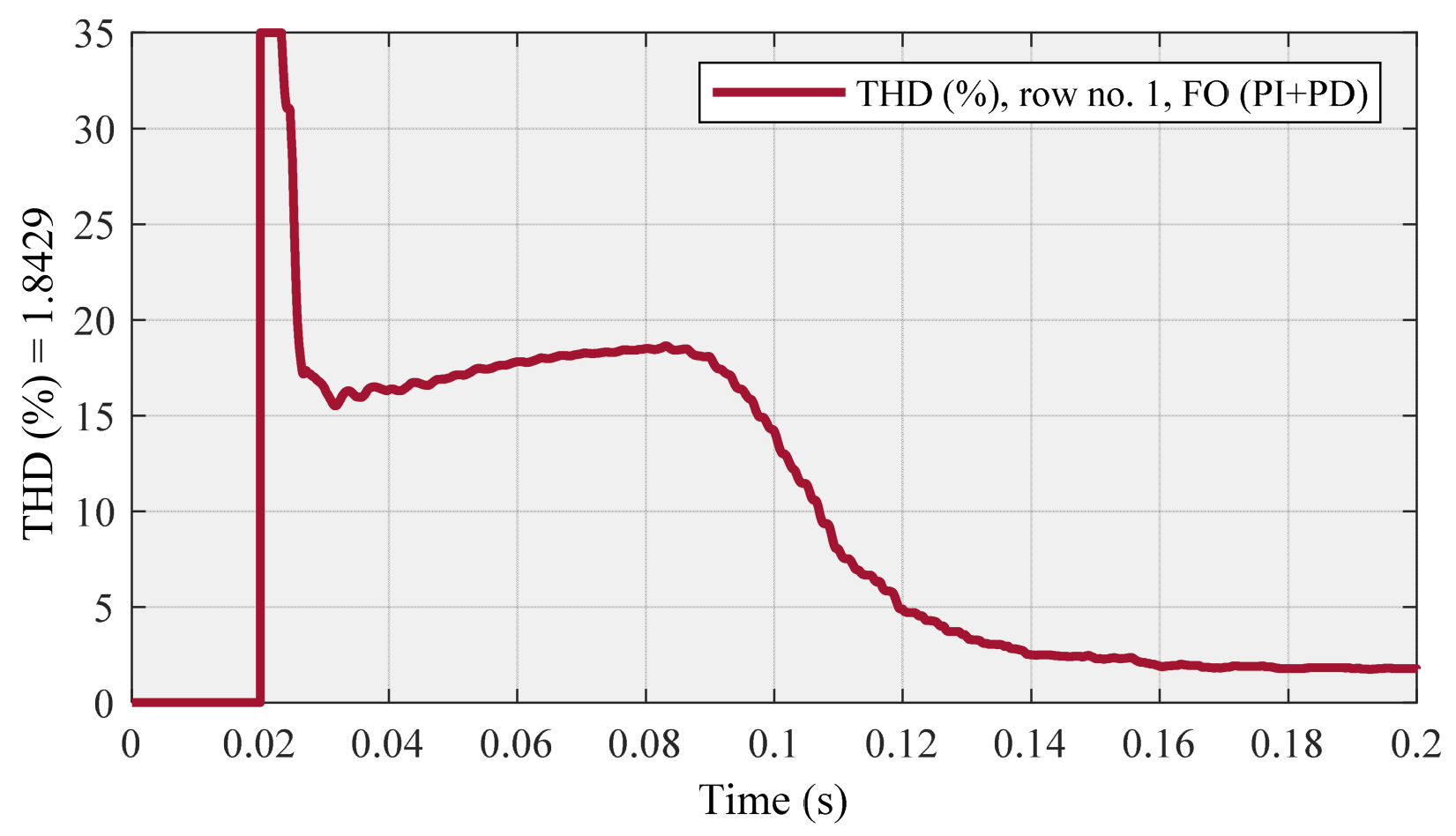

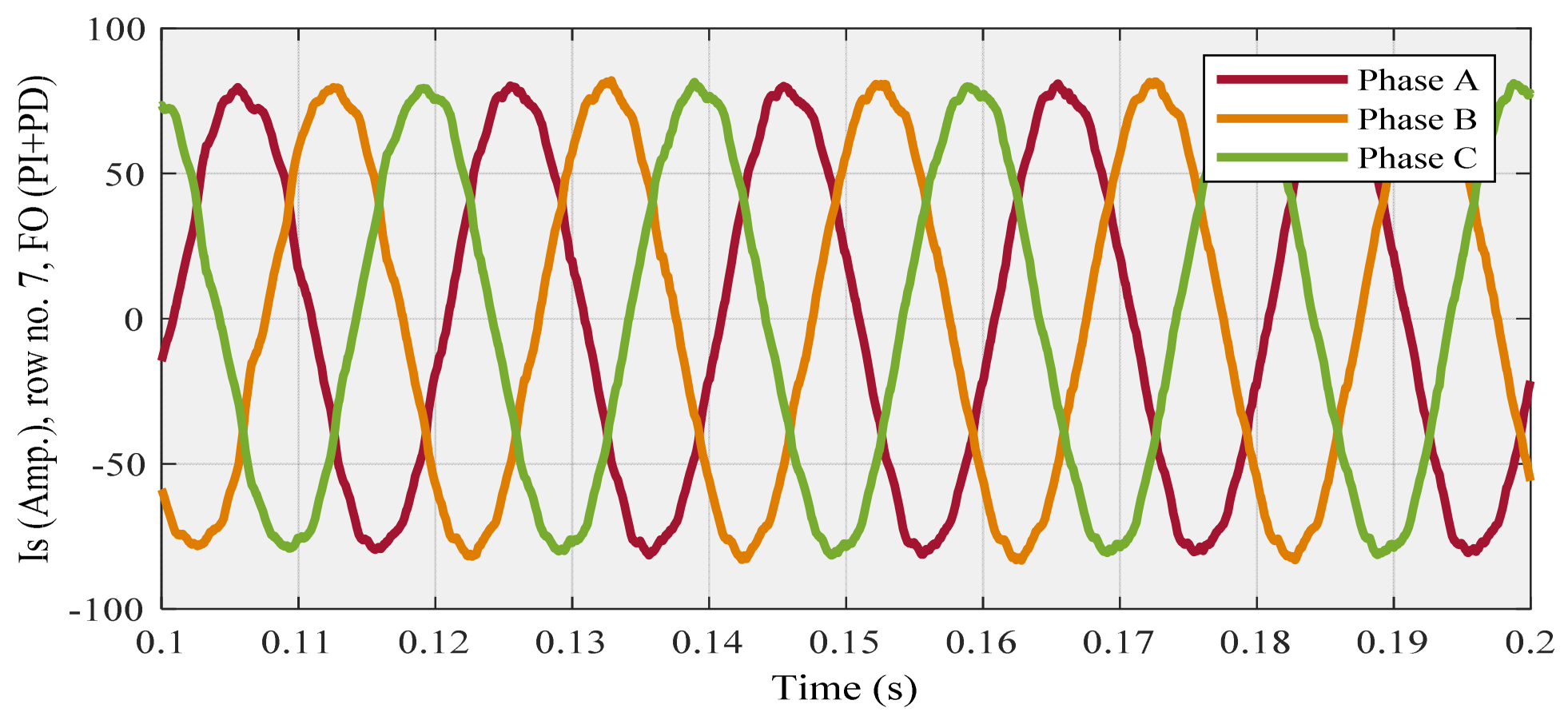

5.1.1. First Section of the First Case Study: Applying FO (PI + PD) Cascade Controller

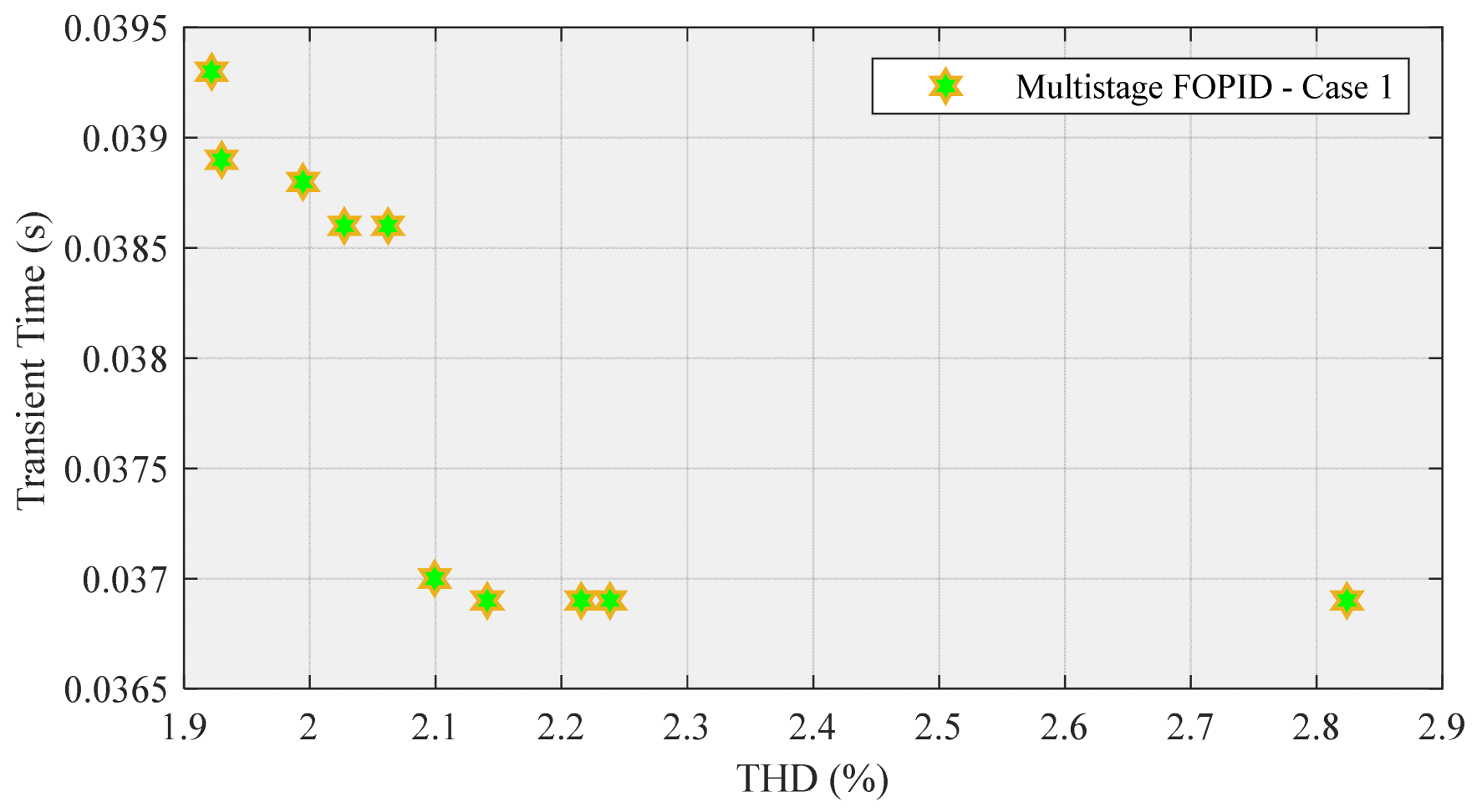

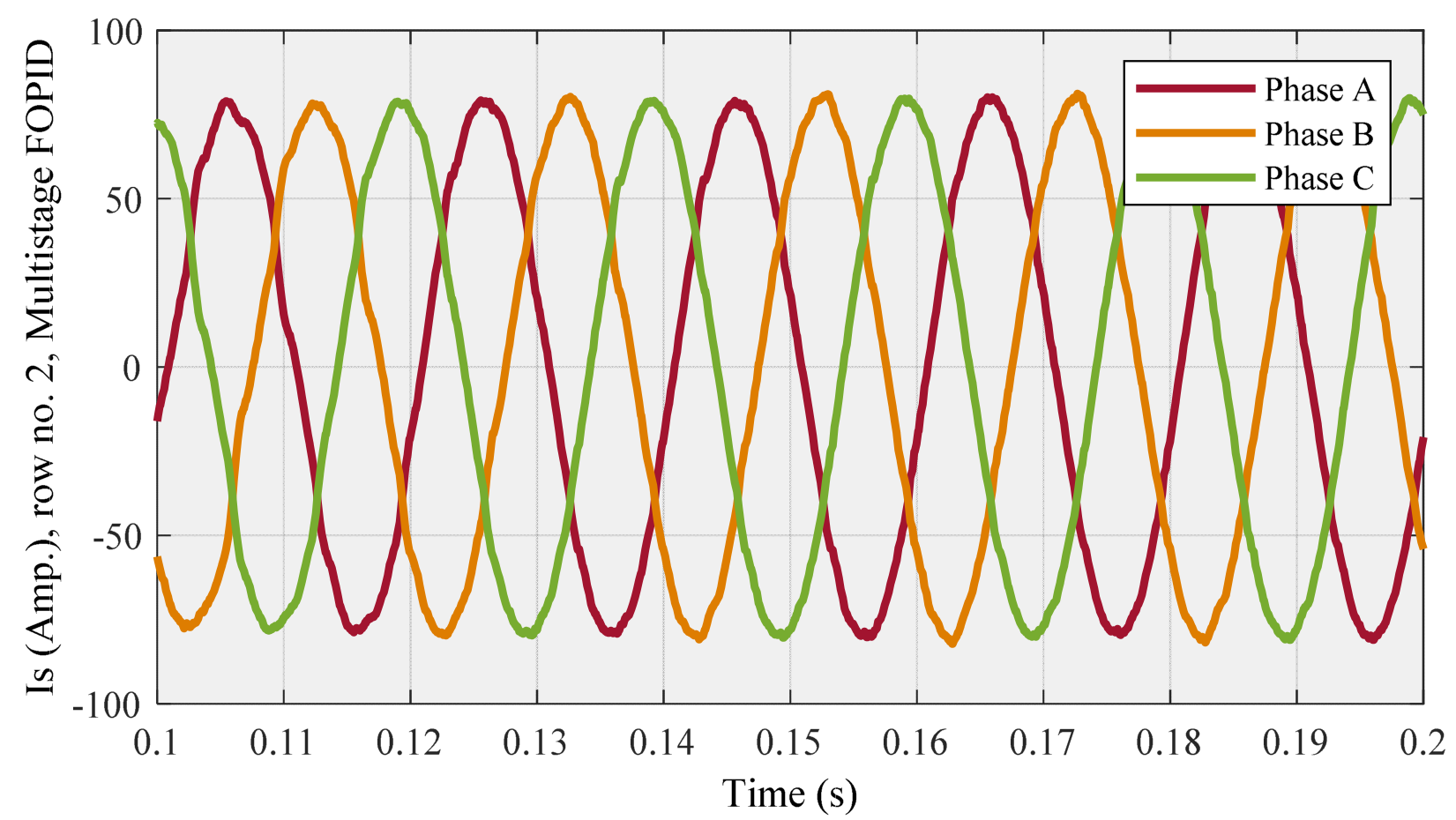

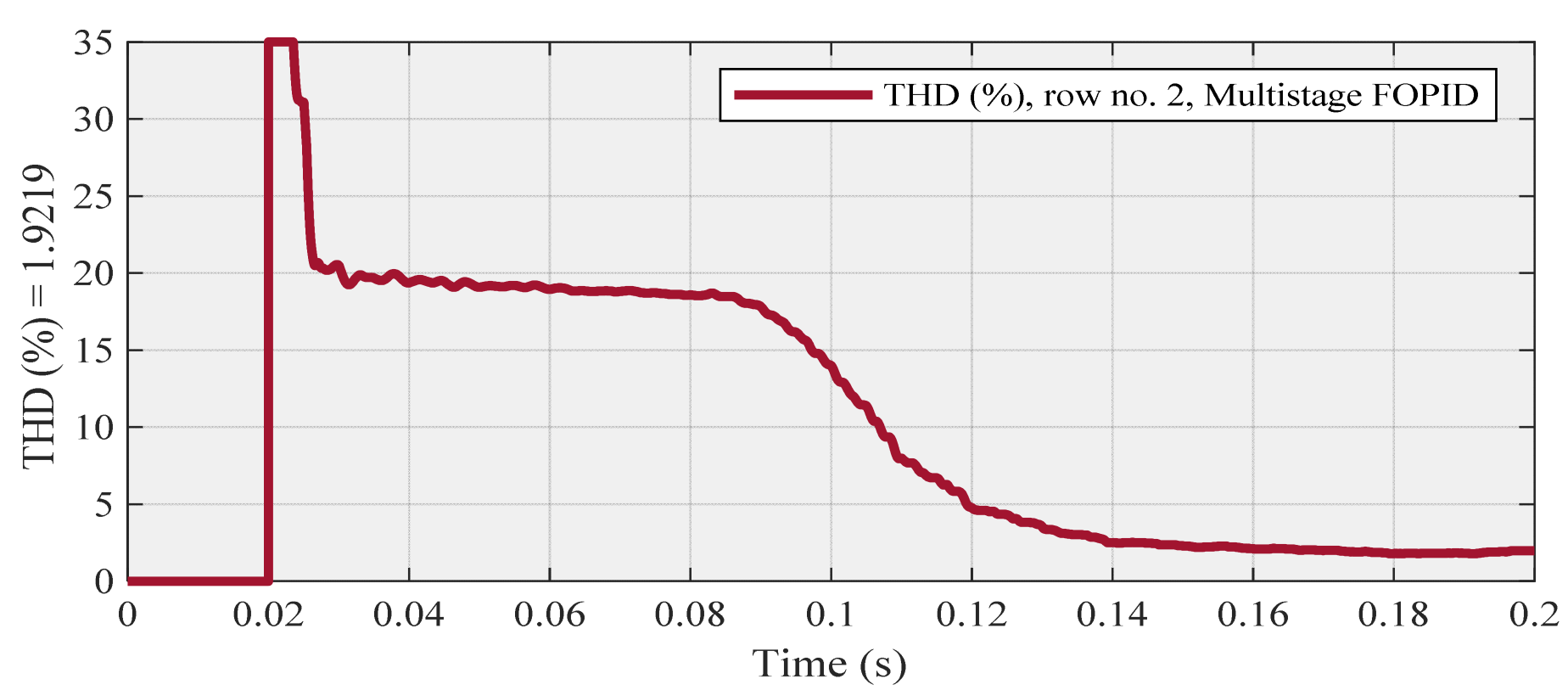

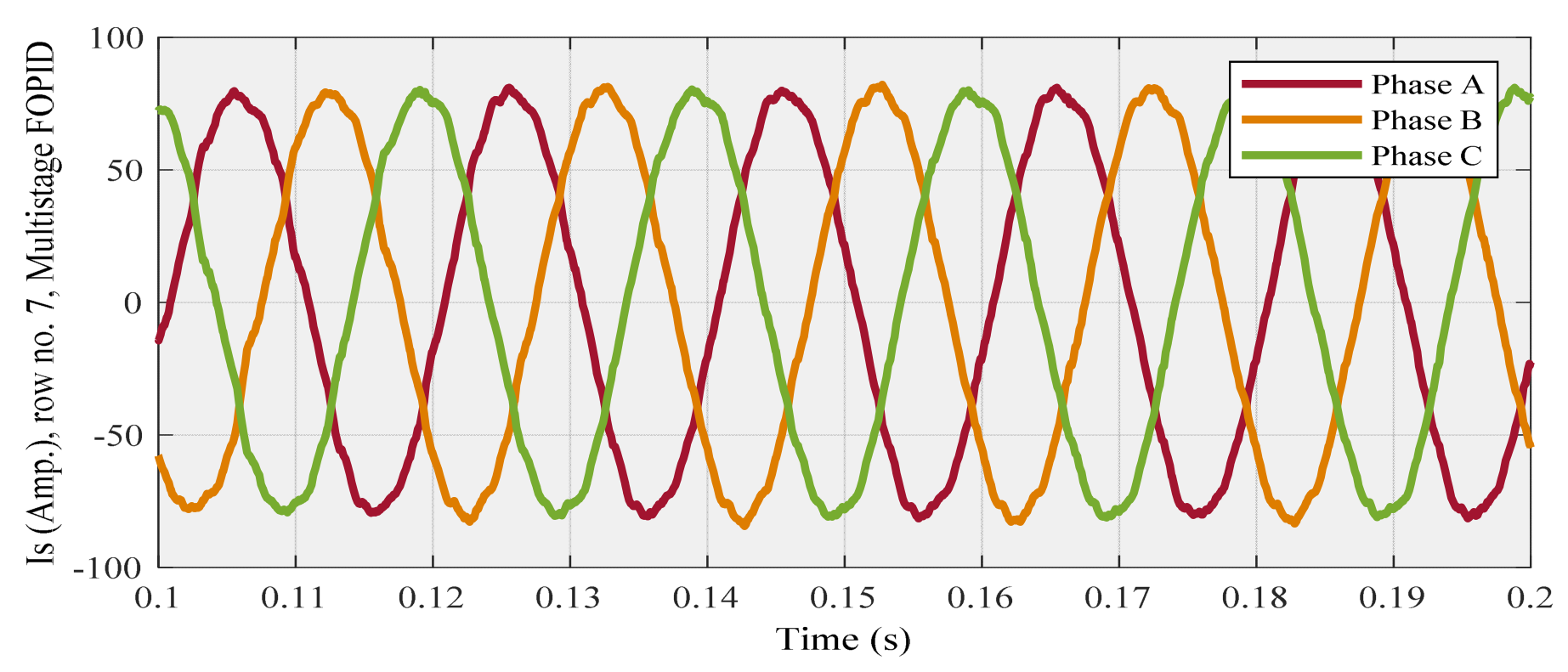

5.1.2. Second Section of the First Case Study: Applying Multistage FOPID Controller

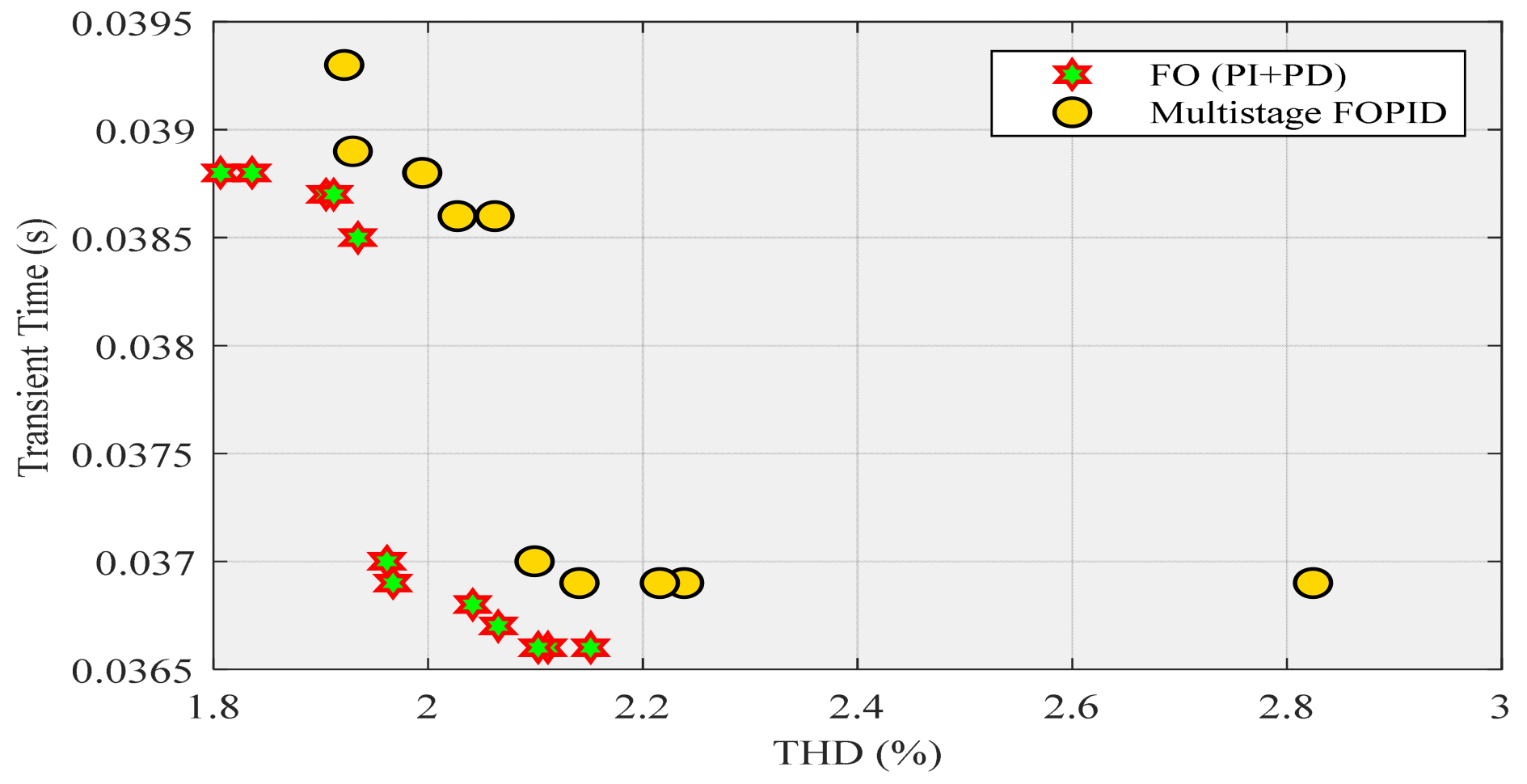

5.1.3. Third Section of the First Case Study: Comparison between FO (PI + PD) Cascade Controller and Multistage FOPID Controller

5.2. Case Study 2: THD (up to the 50th Harmonic) and Settling Time Must Synchronously Be Minimized

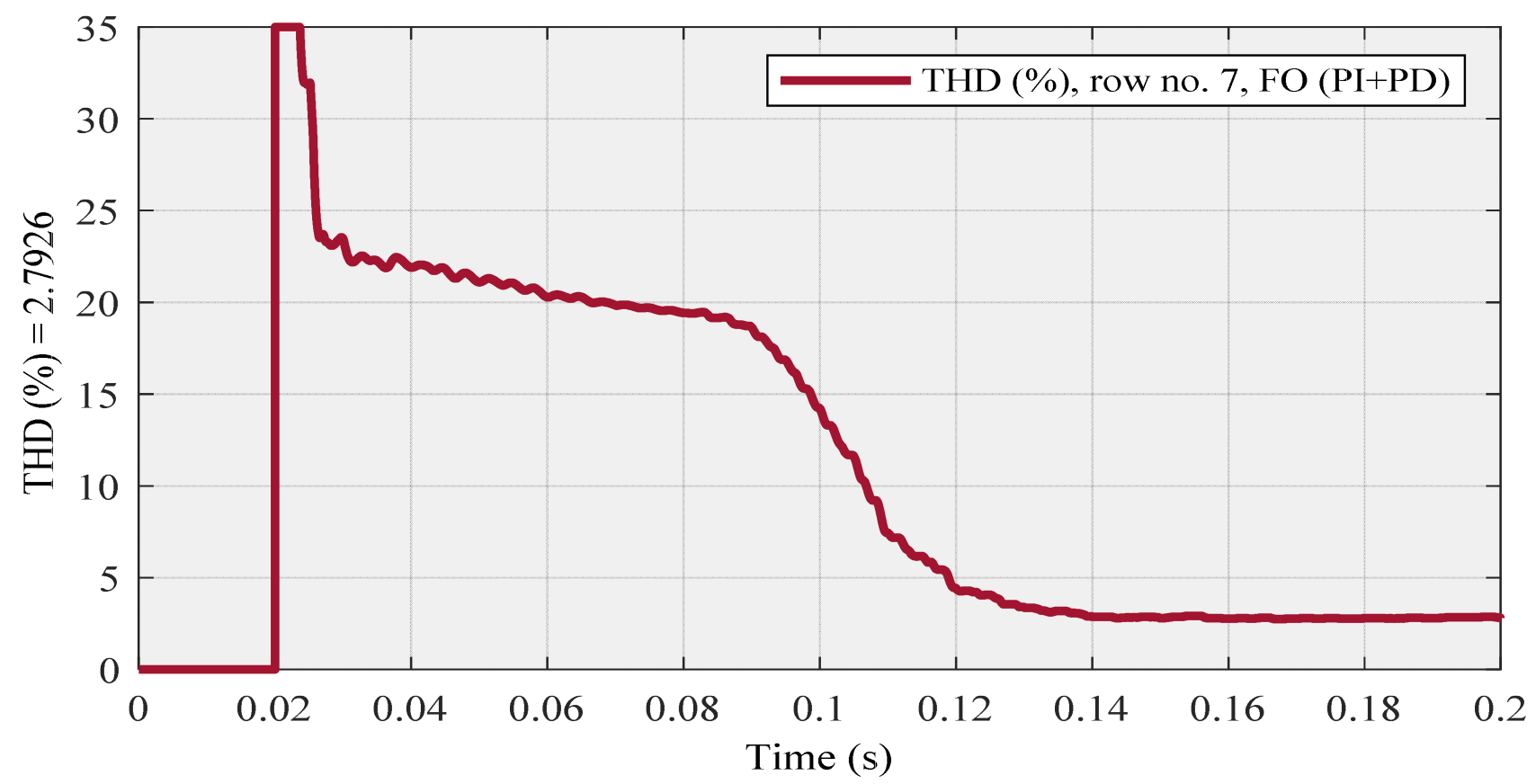

5.2.1. First Section of the Second Case Study: Applying FO (PI + PD) Cascade Controller

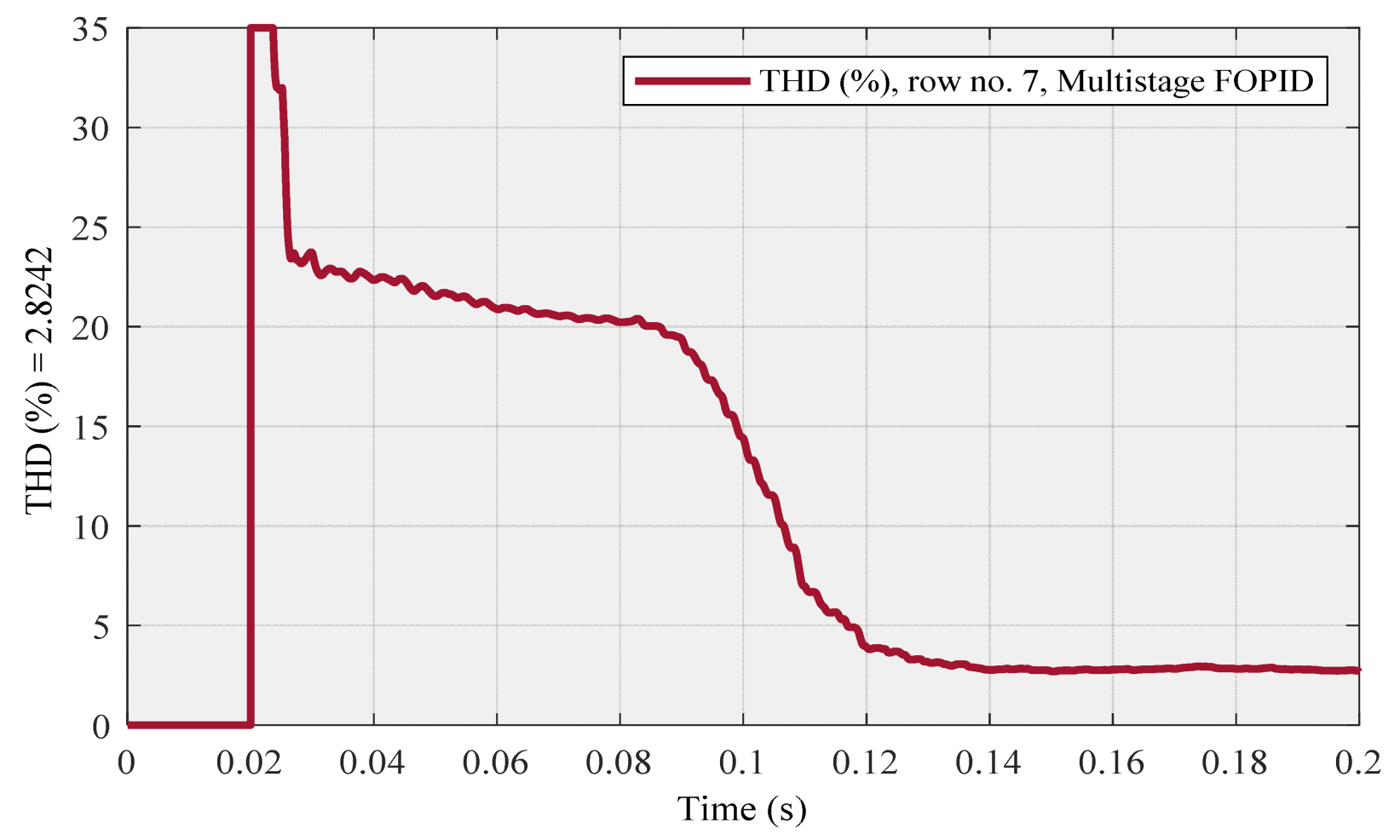

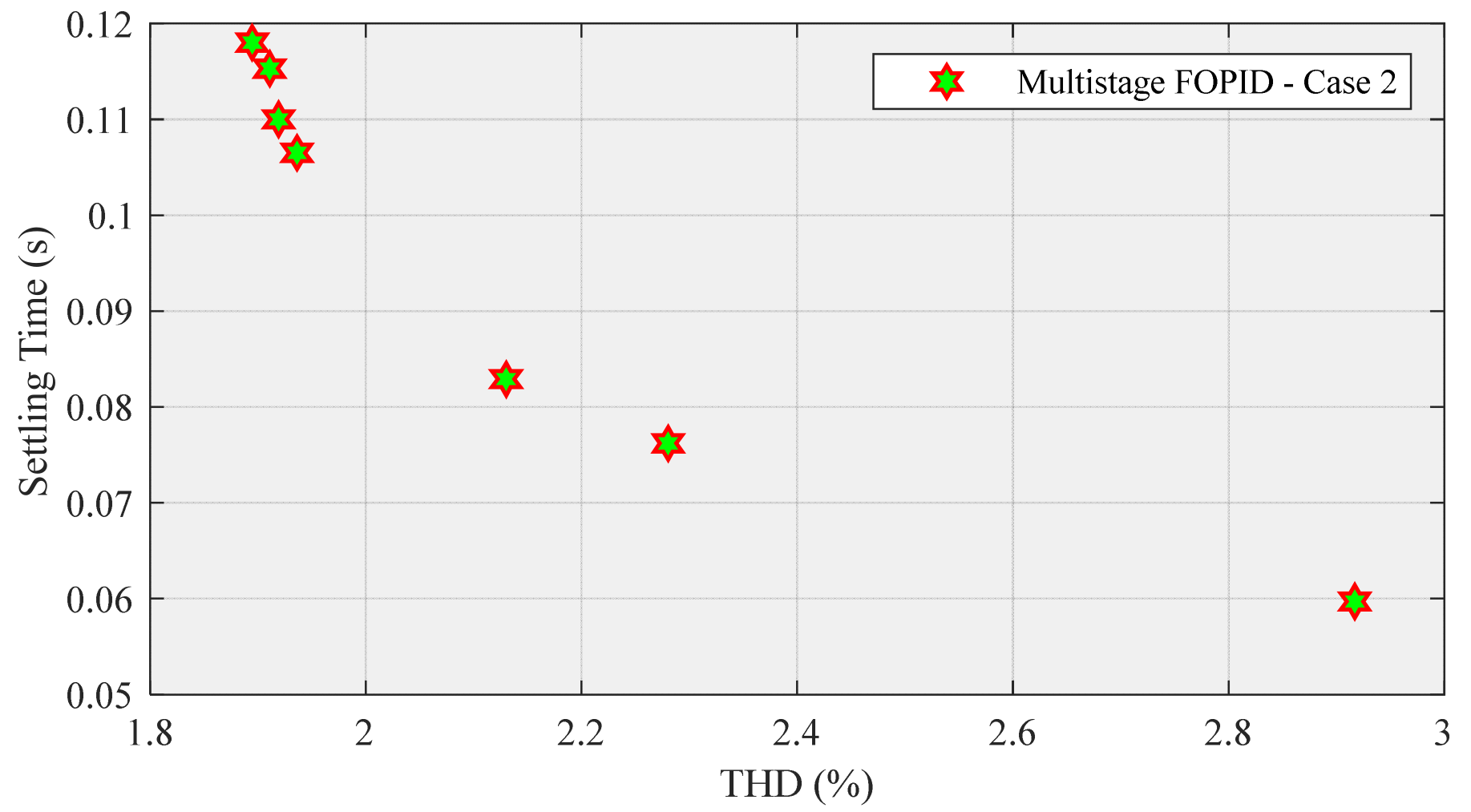

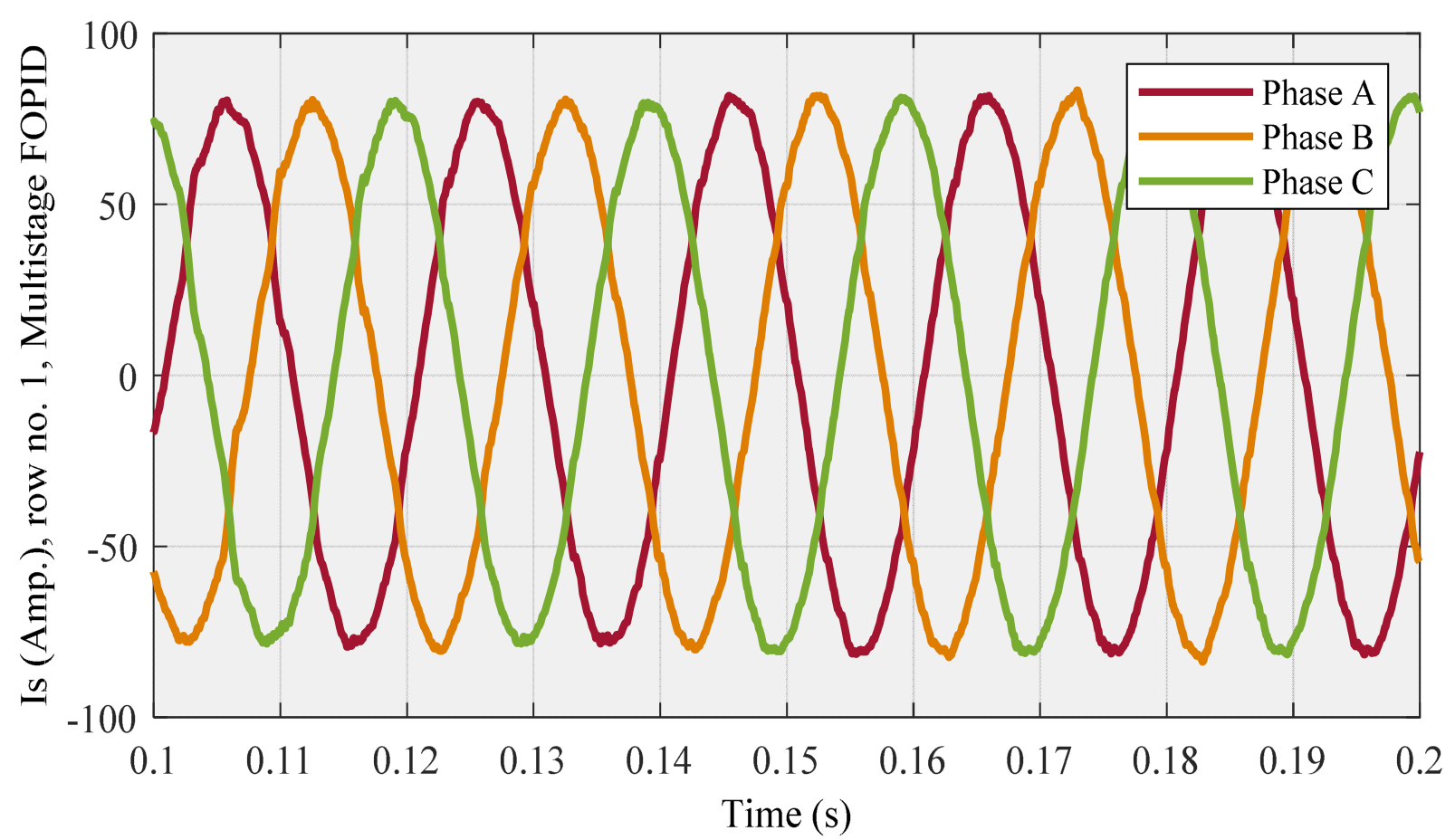

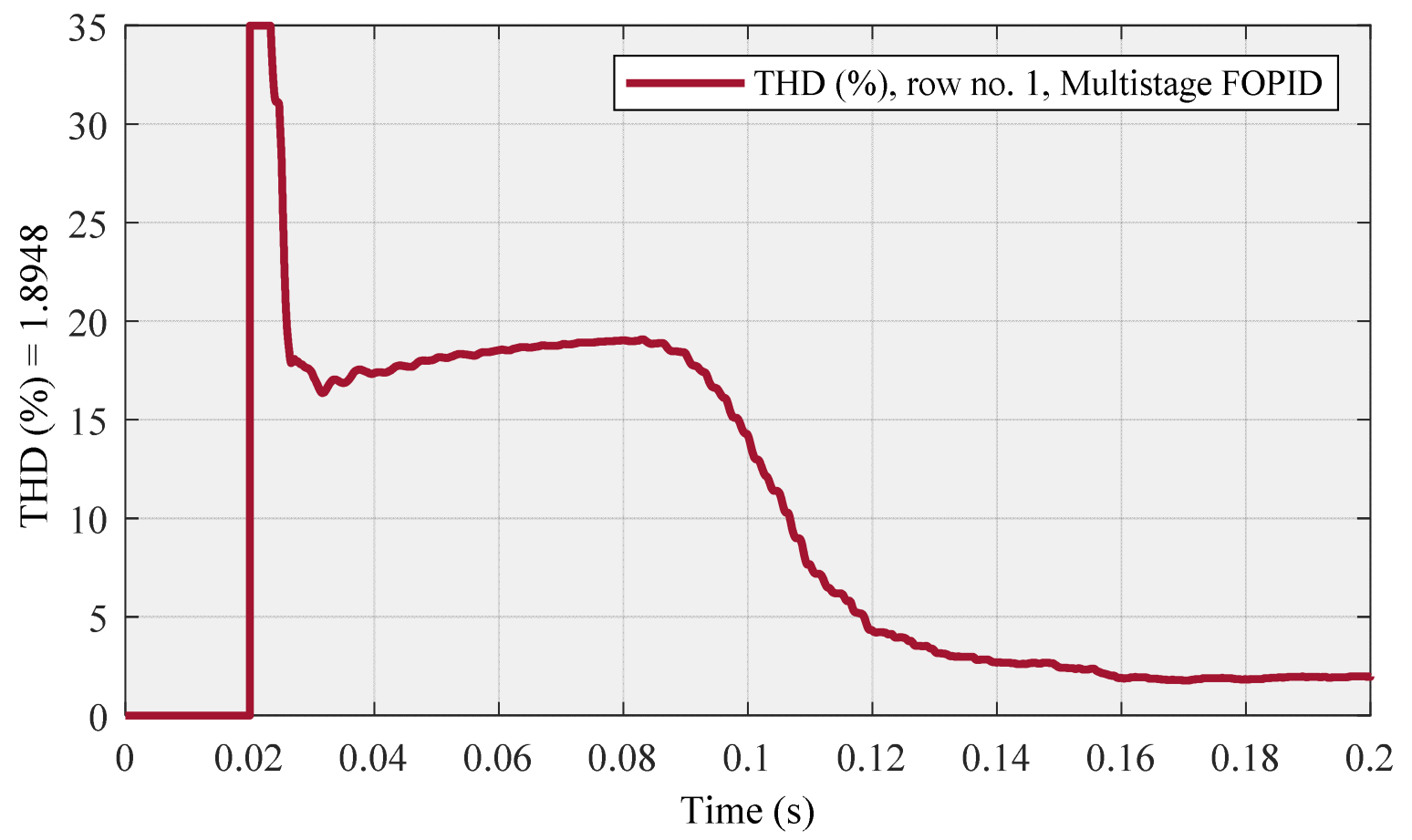

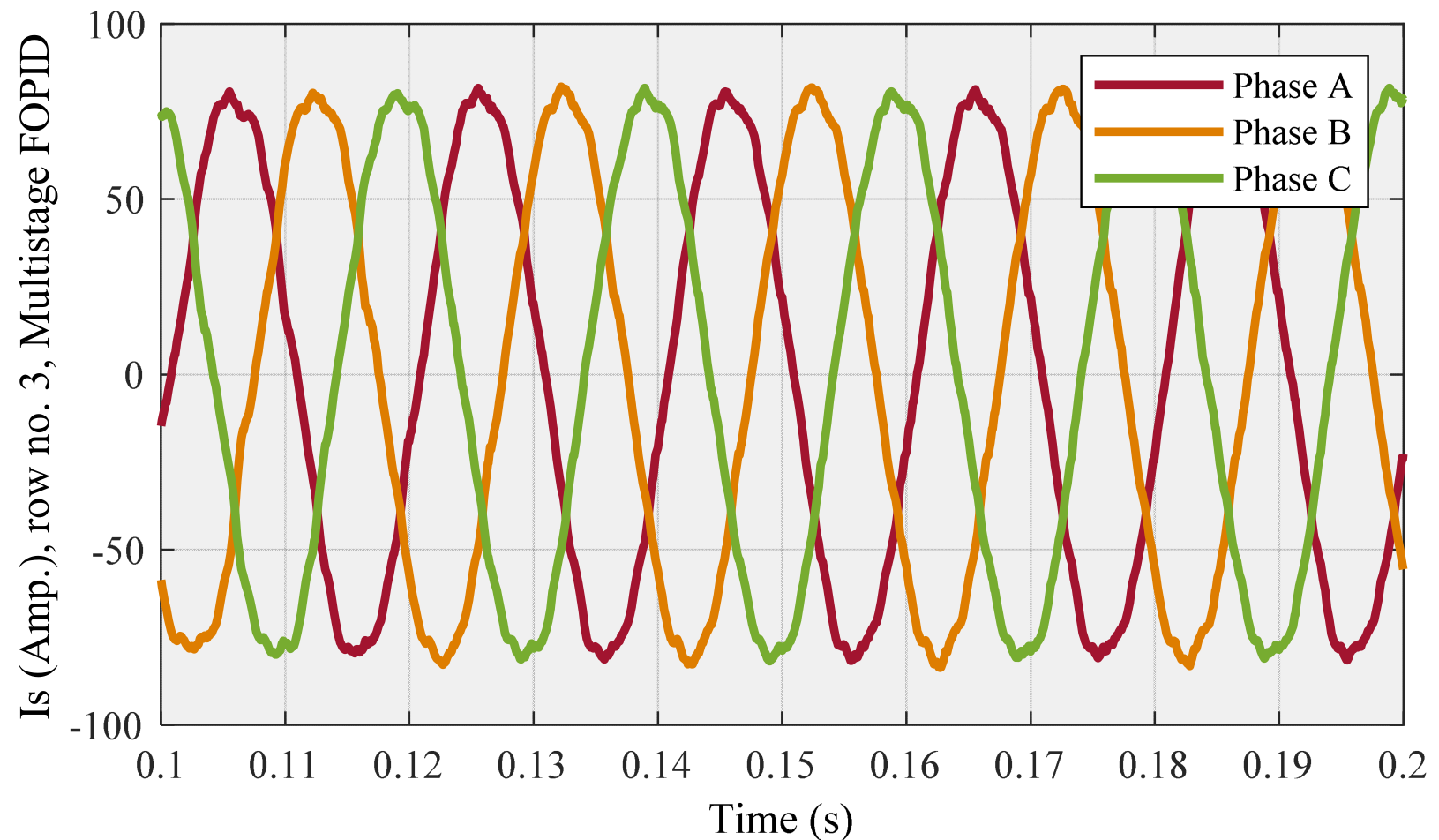

5.2.2. Second Section of the Second Case Study: Applying Multistage FOPID Controller

5.2.3. Third Section of the Second Case Study: Comparison between FO (PI + PD) Cascade Controller and Multistage FOPID Controller

5.3. Summary

- We designed two different controllers to improve the performance of a shunt active power filter based on the NSGA-II optimization approach.

- The mentioned controllers were the FO (PI + PD) cascade controller and multistage FOPID controller.

- For the first time, we devised a multistage FOPID controller using the inspired multistage PID.

- FO (PI + PD) cascade controller was our proposed controller, which was compared with the other controller.

- The obtained results demonstrate that the first controller is superior to the other one. Table 5 shows the compared THDs with their corresponding and .

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Conflicts of Interest

References

- Chen, D.; Xiao, L.; Yan, W.; Li, Y.; Guo, Y. A harmonics detection method based on triangle orthogonal principle for shunt active power filter. Energy Rep. 2021, 7, 98–104. [Google Scholar] [CrossRef]

- Xie, C.; Zhao, X.; Savaghebi, M.; Meng, L.; Guerrero, J.M.; Vasquez, J.C. Multirate fractional-order repetitive control of shunt active power filter suitable for microgrid applications. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 5, 809–819. [Google Scholar] [CrossRef] [Green Version]

- Buła, D.; Grabowski, D.; Maciążek, M. A Review on Optimization of Active Power Filter Placement and Sizing Methods. Energies 2022, 15, 1175. [Google Scholar] [CrossRef]

- Karuppanan, P.; Mahapatra, K.K. PI and fuzzy logic controllers for shunt active power filter—A report. ISA Trans. 2012, 51, 163–169. [Google Scholar] [CrossRef]

- Chebabhi, A.; Fellah, M.K.; Kessal, A.; Benkhoris, M.F. A new balancing three level three dimensional space vector modulation strategy for three level neutral point clamped four leg inverter based shunt active power filter controlling by nonlinear back stepping controllers. ISA Trans. 2016, 63, 328–342. [Google Scholar] [CrossRef]

- Toumi, T.; Allali, A.; Meftouhi, A.; Abdelkhalek, O.; Benabdelkader, A.; Denai, M. Robust control of series active power filters for power quality enhancement in distribution grids: Simulation and experimental validation. ISA Trans. 2020, 107, 350–359. [Google Scholar] [CrossRef]

- Pandove, G.; Singh, M. Robust repetitive control design for a three-phase four wire shunt active power filter. IEEE Trans. Ind. Inform. 2018, 15, 2810–2818. [Google Scholar] [CrossRef]

- Sugavanam, K.R.; Sundaram, K.M.; Jeyabharath, R.; Veena, P. Convolutional Neural Network-based harmonic mitigation technique for an adaptive shunt active power filter. Automatika 2021, 62, 471–485. [Google Scholar] [CrossRef]

- Li, D.; Wang, T.; Pan, W.; Ding, X.; Gong, J. A comprehensive review of improving power quality using active power filters. Electr. Power Syst. Res. 2021, 199, 107389. [Google Scholar] [CrossRef]

- Zhang, H.; Liu, Y. Adaptive RBF neural network based on sliding mode controller for active power filter. Int. J. Power Electron. 2020, 11, 460–481. [Google Scholar] [CrossRef]

- Sanjan, P.S.; Gowtham, N.; Bhaskar, M.S.; Subramaniam, U.; Almakhles, D.J.; Padmanaban, S.; Yamini, N.G. Enhancement of Power Quality in Domestic Loads Using Harmonic Filters. IEEE Access 2020, 8, 197730–197744. [Google Scholar] [CrossRef]

- Morales-Caporal, R. Optimal indirect model predictive control for single-phase two-level shunt active power filters. J. Power Electron. 2022, 22, 84–93. [Google Scholar] [CrossRef]

- França, B.W.; Aredes, M.; Da Silva, L.F.; Gontijo, G.F.; Tricarico, T.C.; Posada, J. An enhanced Shunt Active Filter based on Synchronverter concept. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 10, 494–505. [Google Scholar] [CrossRef]

- Hoon, Y.; Radzi, M.A.M.; Zainuri, M.A.A.M.; Zawawi, M.A.M. Shunt active power filter: A review on phase synchronization control techniques. Electronics 2019, 8, 791. [Google Scholar] [CrossRef] [Green Version]

- Jauhari, M.; Widarsono, K.; Kurdianto, A.A. Shunt active power filter for harmonic mitigation based on PQ theory. In Proceedings of the International Conference on Electrical, Electronics and Information Engineering (ICEEIE), Denpasar, Indonesia, 3–4 October 2019; pp. 11–14. [Google Scholar]

- Balasubramaniam, P.M.; Sudhakar, S.; Krishnamoorthy, S.; Sriram, V.P.; Dhanaraj, S.; Subramaniyaswamy, V.; Rajesh, T. An efficient control strategy of shunt active power filter for asymmetrical load condition using time domain approach. J. Discret. Math. Sci. Cryptogr. 2021, 24, 19–34. [Google Scholar] [CrossRef]

- Upadhyay, S.; Singh, S. Shunt Active Power Filter (SAPF) Design and Analysis of Harmonics Mitigation in Three-Phase Three-Wire Distribution System. In Computing Algorithms with Applications in Engineering; Springer: Singapore, 2020; pp. 201–217. [Google Scholar]

- Imam, A.A.; Kumar, R.S.; Al-Turki, Y.A. Modeling and Simulation of a PI Controlled Shunt Active Power Filter for Power Quality Enhancement Based on P-Q Theory. Electronics 2020, 9, 637. [Google Scholar] [CrossRef]

- Frifita, K.; Boussak, M. A novel strategy for high performance fault tolerant control of shunt active power filter. Electr. Eng. 2022, preview. [Google Scholar] [CrossRef]

- Çelik, D. Lyapunov based harmonic compensation and charging with three phase shunt active power filter in electrical vehicle applications. Int. J. Electr. Power Energy Syst. 2022, 136, 107564. [Google Scholar] [CrossRef]

- Bessa, R.J.; Trindade, A.; Miranda, V. Spatial-temporal solar power forecasting for smart grids. IEEE Trans. Ind. Inf. 2015, 11, 232–241. [Google Scholar] [CrossRef]

- Rafiei, S.M.R.; Limongi, L.; Griva, G.; Bojoi, R. Optimal Design of High Performance Repetitive Controller for Shunt Active Filters Using Strength Pareto Multi-Objective Optimization Approach. In Proceedings of the 13th European Conference on Power Electronics and Applications, Barcelona, Spain, 8–10 September 2009. [Google Scholar]

- Kashani, H.N.; Rafiei SM, R. Optimal control of active power filters using fractional order controllers based on NSGA-II optimization method. Int. J. Electr. Power Energy Syst. 2014, 63, 1008–1014. [Google Scholar] [CrossRef]

- Tehrani, K.; Amirahmadi, A.; Rafiei, S.M.R.; Griva, G.; Barrandon, L.; Hamzaoui, M.; Rasoanarivo, I.; Sargos, F.M. Design of fractional order PID controller for boost converter based on Multi-Objective optimization. In Proceedings of the 14th International Power Electronics and Motion Control Conference, EPE-PEMC, Ohrid, Macedonia, 6–8 September 2010; pp. T3-179–T3-185. [Google Scholar] [CrossRef]

- Sivalingam, R.; Chinnamuthu, S.; Dash, S.S. A hybrid stochastic fractal search and local unimodal sampling based multistage PDF plus (1+ PI) controller for automatic generation control of power systems. J. Frankl. Inst. 2017, 354, 4762–4783. [Google Scholar] [CrossRef]

- Çelik, E. Design of new fractional order PI–fractional order PD cascade controller through dragonfly search algorithm for advanced load frequency control of power systems. Soft Comput. 2021, 25, 1193–1217. [Google Scholar] [CrossRef]

- Zhou, X.; Shi, Y.; Zhu, J.; Zhao, L.; Zhu, Z. Structural multi-objective optimization on a MUAV-based pan–tilt for aerial remote sensing applications. ISA Trans. 2020, 100, 405–421. [Google Scholar] [CrossRef] [PubMed]

- Ghogare, M.G.; Patil, S.L.; Patil, C.Y. Experimental validation of optimized fast terminal sliding mode control for level system. ISA Trans. 2021, in press. [CrossRef]

- Xu, T.; Ren, Y.; Guo, L.; Wang, X.; Liang, L.; Wu, Y. Multi-objective robust optimization of active distribution networks considering uncertainties of photovoltaic. Int. J. Electr. Power Energy Syst. 2021, 133, 10719. [Google Scholar] [CrossRef]

- Sadeghi, A.; Daneshvar, A.; Zaj, M.M. Combined ensemble multi-class SVM and fuzzy NSGA-II for trend forecasting and trading in Forex markets. Expert Syst. Appl. 2021, 185, 115566. [Google Scholar] [CrossRef]

- Ghaderian, M.; Veysi, F. Multi-objective optimization of energy efficiency and thermal comfort in an existing office building using NSGA-II with fitness approximation: A case study. J. Build. Eng. 2021, 41, 102440. [Google Scholar] [CrossRef]

- Jain, K.; Gupta, S.; Kumar, D. Multi-objective power distribution optimization using NSGA-II. Int. J. Comput. Methods Eng. Sci. Mech. 2021, 22, 235–243. [Google Scholar] [CrossRef]

- Hu, H.X.; Shao, L.H.; Hu, Q.; Zhang, Y.; Hu, Z.Y. Multi-objective Reservoir Optimal Operation Based on GCN and NSGA-II Algorithm. In Proceedings of the 4th International Conference on Advanced Electronic Materials, Computers and Software Engineering (AEMCSE), Changsha, China, 26–28 March 2021; pp. 546–551. [Google Scholar]

- Rego, M.F.; Pinto, J.C.E.; Cota, L.P.; Souza, M.J. A mathematical formulation and an NSGA-II algorithm for minimizing the makespan and energy cost under time-of-use electricity price in an unrelated parallel machine scheduling. PeerJ Comput. Sci. 2022, 8, e844. [Google Scholar] [CrossRef]

- Ahmed, F.; Zhu, S.; Yu, G.; Luo, E. A potent numerical model coupled with multi-objective NSGA-II algorithm for the optimal design of Stirling engine. Energy 2022, 247, 123468. [Google Scholar] [CrossRef]

- Suman, G.K.; Guerrero, J.M.; Roy, O.P. Stability of microgrid cluster with Diverse Energy Sources: A multi-objective solution using NSGA-II based controller. Sustain. Energy Technol. Assess. 2022, 50, 101834. [Google Scholar] [CrossRef]

- Bagheri-Esfeh, H.; Dehghan, M.R. Multi-objective optimization of setpoint temperature of thermostats in residential buildings. Energy Build. 2022, 261, 111955. [Google Scholar] [CrossRef]

- Bao, L.; Zheng, M.; Zhou, Q.; Gao, P.; Xu, Y.; Jiang, H. Multi-objective optimization of partition temperature of steel sheet by NSGA-II using response surface methodology. Case Stud. Therm. Eng. 2022, 31, 101818. [Google Scholar] [CrossRef]

- Zhang, X.; Fan, X.; Yu, S.; Shan, A.; Fan, S.; Xiao, Y.; Dang, F. Intersection Signal Timing Optimization: A Multi-Objective Evolutionary Algorithm. Sustainability 2022, 14, 1506. [Google Scholar] [CrossRef]

- Ghosh, A.; Ledwich, G. A unified power quality conditioner (UPQC) for simultaneous voltage and current compensation. Electr. Power Syst. Res. 2001, 59, 55–63. [Google Scholar] [CrossRef]

- Rafiei, M.R.; Toliyat, H.A.; Ghazi, R.; Gopalarathanam, T. An optimal and flexible control strategy for active filtering and power factor correction under nonsinusoidal line voltages. IEEE Trans. Power Delivery 2001, 16, 297–305. [Google Scholar] [CrossRef]

- Milanés, M.I.; Romero, E.; Barrero, F. Comparison of control strategies for shunt active power filters in three-phase four-wire systems. IEEE Trans. Power Electron. 2007, 2, 229–236. [Google Scholar]

- da Silva, C.H.; Pereira, R.R.; da Silva LE, B.; Torres, G.L.; Pinto, J.O.P. Unified hybrid power quality conditioner (UHPQC). In Proceedings of the 2010 IEEE International Symposium on Industrial Electronics, Bari, Italy, 4–7 July 2010; pp. 1149–1153. [Google Scholar]

- Buso, S.; Fasolo, S.; Malesani, L.; Mattavelli, P. A dead-beat adaptive hysteresis current control. IEEE Trans. Ind. Appl. 2000, 36, 1174–1180. [Google Scholar] [CrossRef]

- Garcia-Cerrada, A.; Pinzon-Ardila, O.; Feliu-Batlle, V.; Roncero-Sanchez, P.; Garcia-Gonzalez, P. Application of a Repetitive Controller for a Three-Phase Active Power Filter. IEEE Trans. Power Electron. 2007, 22, 237–246. [Google Scholar] [CrossRef]

- Limongi, L.R.; Bojoi, R.; Griva, G.; Tenconi, A. Performance comparison of DSP-based current controllers for three-phase active power filters. In Proceedings of the IEEE International Symposium on Industrial Electronics, Cambridge, UK, 30 June–2 July 2008; pp. 136–141. [Google Scholar]

- Cavallini, A.; Montanari, G. Compensation strategies for shunt active-filter control. IEEE Trans. Power Electron. 1994, 9, 587–593. [Google Scholar] [CrossRef]

- Inoue, T.; Nakano, M.; Kubo, T.; Matsumoto, S.; Baba, H. High Accuracy Control of a Proton Synchrotron Magnet Power Supply. IFAC Proc. Vol. 1981, 14, 3137–3142. [Google Scholar] [CrossRef]

- Inoue, T.; Nakano, M.; Iwai, S. High accuracy control of servomechanism for repeated contouring. In Proceedings of the 10th Annual Symposium on Incremental Motion Control Systems and Devices, Rosemont, IL, USA, 1–4 June 1981; pp. 258–292. [Google Scholar]

- Wang, Y.; Gao, F.; Doyle, F.J., III. Survey on iterative learning control, repetitive control, and run-to-run control. J. Process Control. 2009, 19, 1589–1600. [Google Scholar] [CrossRef]

- Mattavelli, P.; Marafão, F. Repetitive-Based Control for Selective Harmonic Compensation in Active Power Filters. IEEE Trans. Ind. Electron. 2004, 51, 1018–1024. [Google Scholar] [CrossRef]

- Khooban, M.H.; Gheisarnejad, M. Islanded microgrid frequency regulations concerning the integration of tidal power units: Real-time implementation. IEEE Trans. Circuits Syst. II: Express Briefs 2019, 67, 1099–1103. [Google Scholar] [CrossRef]

- Gheisarnejad, M.; Khooban, M.H. An intelligent non-integer PID controller-based deep reinforcement learning: Implementation and experimental results. IEEE Trans. Ind.Electron. 2020, 68, 3609–3618. [Google Scholar] [CrossRef]

- Deb, K.; Pratap, A.; Agarwal, S.; Meyarivan, T.A.M.T. A fast and elitist multiobjective genetic algorithm: NSGA-II. IEEE Trans. Evol. Comput. 2002, 6, 182–197. [Google Scholar] [CrossRef] [Green Version]

- Yusoff, Y.; Ngadiman, M.S.; Zain, A.M. Overview of NSGA-II for Optimizing Machining Process Parameters. Procedia Eng. 2011, 15, 3978–3983. [Google Scholar] [CrossRef] [Green Version]

- Liu, M.; Liu, R.; Zhu, Z.; Chu, C.; Man, X. A Bi-Objective Green Closed Loop Supply Chain Design Problem with Uncertain Demand. Sustainability 2018, 10, 967. [Google Scholar] [CrossRef] [Green Version]

- Esfahani, Z.; Roohi, M.; Gheisarnejad, M.; Dragičević, T.; Khooban, M.-H. Optimal non-integer sliding mode control for frequency regulation in stand-alone modern power grids. Appl. Sci. 2019, 9, 3411. [Google Scholar] [CrossRef] [Green Version]

| No | Kp1 | Ki | Vdc | Kp2 | Kd | α | β | THD (%) | |

|---|---|---|---|---|---|---|---|---|---|

| 1 | 2.4154 | 10.4602 | 815.0000 | 3.0000 | 0.4257 | 0.7481 | 0.3224 | 1.9673 | 0.0369 |

| 2 | 2.0321 | 10.4680 | 815.0000 | 2.5807 | 0.4287 | 0.7496 | 0.3224 | 1.9048 | 0.0387 |

| 3 | 1.9759 | 12.4680 | 815.0000 | 3.0000 | 0.4257 | 0.7481 | 0.3224 | 2.0416 | 0.0368 |

| 4 | 2.2689 | 12.4055 | 815.0000 | 3.0000 | 0.4287 | 0.7481 | 0.3224 | 2.0654 | 0.0367 |

| 5 | 1.9759 | 12.4680 | 815.0000 | 2.5807 | 0.4287 | 0.7481 | 0.3216 | 1.8360 | 0.0388 |

| 6 | 2.0321 | 12.4679 | 814.9904 | 2.5807 | 0.4287 | 0.7481 | 0.3224 | 1.8068 | 0.0388 |

| 7 | 2.2689 | 12.4055 | 814.9904 | 2.5807 | 0.4287 | 0.7481 | 0.3224 | 1.9122 | 0.0387 |

| 8 | 2.4154 | 10.4602 | 815.0000 | 2.9902 | 0.4703 | 0.7481 | 0.3302 | 2.1114 | 0.0366 |

| 9 | 2.2970 | 12.4680 | 814.6924 | 3.0000 | 0.4257 | 0.7481 | 0.3224 | 2.1513 | 0.0366 |

| 10 | 2.4154 | 10.4602 | 814.9994 | 2.9902 | 0.4257 | 0.7481 | 0.3224 | 2.1024 | 0.0366 |

| 11 | 2.4154 | 10.4602 | 815.0000 | 2.9207 | 0.4287 | 0.7481 | 0.3224 | 1.9616 | 0.0370 |

| 12 | 2.4154 | 10.4602 | 815.0000 | 2.5807 | 0.4287 | 0.7480 | 0.3212 | 1.9345 | 0.0385 |

| No | Kp | Ki | Vdc | Kpp | N | Kd | α | β | THD (%) | |

|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 2.5400 | 12.4261 | 719.0607 | 11.2424 | 1.7693 | 0.9098 | 0.9000 | 0.0287 | 2.0274 | 0.0386 |

| 2 | 1.8393 | 10.7355 | 573.2281 | 11.7506 | 1.6734 | 0.1000 | 0.9408 | 0.0904 | 1.9219 | 0.0393 |

| 3 | 2.6000 | 13.2472 | 601.7378 | 11.7506 | 1.6734 | 0.6063 | 0.9041 | 0.0287 | 2.0992 | 0.0370 |

| 4 | 2.6000 | 10.0000 | 812.8484 | 11.7428 | 1.0054 | 0.2728 | 0.9683 | 0.0760 | 2.0621 | 0.0386 |

| 5 | 2.5315 | 13.8570 | 812.8484 | 11.7424 | 1.7693 | 0.2728 | 0.9683 | 0.0535 | 1.9946 | 0.0388 |

| 6 | 2.4969 | 13.8570 | 812.8484 | 11.6879 | 1.7547 | 0.9098 | 0.9683 | 0.0287 | 1.9299 | 0.0389 |

| 7 | 2.5764 | 11.1837 | 529.0360 | 11.3453 | 1.6186 | 0.4805 | 0.9335 | 0.0801 | 2.8242 | 0.0369 |

| 8 | 2.5764 | 11.5726 | 686.4316 | 11.9324 | 1.5213 | 0.6709 | 0.9335 | 0.0960 | 2.2386 | 0.0369 |

| 9 | 2.5764 | 11.5745 | 686.4515 | 11.9324 | 1.5213 | 0.6709 | 0.9336 | 0.0967 | 2.1409 | 0.0369 |

| 10 | 2.5764 | 11.5764 | 686.4515 | 11.9324 | 1.5213 | 0.6709 | 0.9336 | 0.0967 | 2.2158 | 0.0369 |

| NO | Kp1 | Ki | Vdc | Kp2 | Kd | α | β | THD (%) | |

|---|---|---|---|---|---|---|---|---|---|

| 1 | 1.2000 | 13.9922 | 816.6667 | 2.1886 | 1.2999 | 0.8416 | 0.3667 | 1.8429 | 0.1130 |

| 2 | 1.2000 | 13.9922 | 816.6667 | 2.1618 | 0.0100 | 0.7333 | 0.6349 | 1.8836 | 0.1013 |

| 3 | 2.4667 | 13.4800 | 816.6667 | 2.2449 | 1.2999 | 0.8416 | 0.3667 | 1.7717 | 0.1197 |

| 4 | 3.0667 | 14.2904 | 552.2070 | 3.0000 | 1.3000 | 0.6000 | 0.3667 | 2.7445 | 0.0643 |

| 5 | 2.6000 | 10.0000 | 616.6667 | 2.1667 | 0.8700 | 0.6000 | 0.1000 | 2.0936 | 0.0720 |

| 6 | 2.6000 | 10.0000 | 616.6667 | 2.1618 | 0.8700 | 0.9999 | 0.1000 | 2.0609 | 0.0763 |

| 7 | 2.6000 | 10.0000 | 500.0000 | 2.1618 | 1.3000 | 0.6002 | 0.1000 | 2.7926 | 0.0590 |

| NO | Kp | Ki | Vdc | Kpp | N | Kd | α | β | THD (%) | |

|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 2.5434 | 11.0508 | 794.7464 | 11.6264 | 1.3662 | 0.8016 | 0.9822 | 0.0984 | 1.8948 | 0.1180 |

| 2 | 2.5432 | 11.8920 | 763.7147 | 11.9952 | 1.2958 | 0.8016 | 0.9399 | 0.0321 | 2.1301 | 0.0829 |

| 3 | 2.4183 | 11.7547 | 490.0000 | 11.9461 | 0.1583 | 1.0000 | 0.9169 | 0.0886 | 2.9171 | 0.0597 |

| 4 | 2.1557 | 11.8764 | 763.7147 | 11.2523 | 0.2918 | 0.4703 | 0.9822 | 0.0984 | 1.9191 | 0.1100 |

| 5 | 2.1426 | 11.8998 | 763.7147 | 11.2523 | 0.2754 | 0.4703 | 0.9688 | 0.0984 | 1.9363 | 0.1065 |

| 6 | 2.1426 | 11.8920 | 763.7147 | 11.2523 | 0.2918 | 0.8016 | 0.9688 | 0.0666 | 1.9108 | 0.1153 |

| 7 | 2.3213 | 10.6331 | 547.4531 | 11.0189 | 1.2924 | 0.2266 | 0.9267 | 0.0921 | 2.2803 | 0.0762 |

| NO | Controller | THD (%) | THD (%) | ||

|---|---|---|---|---|---|

| 1 | FO (PI + PD) cascade | 1.8068 | 0.0388 | 1.8429 | 0.1130 |

| 2 | Multistage FOPID | 1.9219 | 0.0393 | 1.8948 | 0.1180 |

| 3 | FO (PI + PD) cascade | 2.1513 | 0.0366 | 2.7926 | 0.0590 |

| 4 | Multistage FOPID | 2.8242 | 0.0369 | 2.9171 | 0.0597 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Nikkhah Kashani, H.; Rouhi Ardeshiri, R.; Gheisarnejad, M.; Khooban, M.-H. Optimal Cascade Non-Integer Controller for Shunt Active Power Filter: Real-Time Implementation. Designs 2022, 6, 32. https://doi.org/10.3390/designs6020032

Nikkhah Kashani H, Rouhi Ardeshiri R, Gheisarnejad M, Khooban M-H. Optimal Cascade Non-Integer Controller for Shunt Active Power Filter: Real-Time Implementation. Designs. 2022; 6(2):32. https://doi.org/10.3390/designs6020032

Chicago/Turabian StyleNikkhah Kashani, Hoda, Reza Rouhi Ardeshiri, Meysam Gheisarnejad, and Mohammad-Hassan Khooban. 2022. "Optimal Cascade Non-Integer Controller for Shunt Active Power Filter: Real-Time Implementation" Designs 6, no. 2: 32. https://doi.org/10.3390/designs6020032