Compact SPAD-Based Pixel Architectures for Time-Resolved Image Sensors

Abstract

:1. Introduction

2. SPADs in CMOS Technologies

2.1. SPAD Structure

2.2. Figures of Merit

2.3. Uniformity

2.4. Layout

3. Compact Pixels for Time-Resolved Imaging

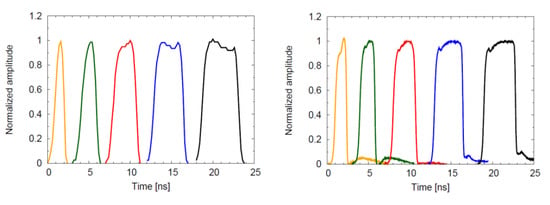

3.1. Pixel Architectures

3.2. Analysis and Comparison

4. Discussion and Conclusions

Author Contributions

Conflicts of Interest

References

- Aull, B.; Loomis, A.; Young, D. Geiger-mode avalanche photodiodes for three-dimensional imaging. Linc. Lab. J. 2002, 13, 335–350. [Google Scholar]

- Lakowicz, J.R. Principles of Fluorescence Spectroscopy, 3rd ed.; Springer US: Boston, MA, USA, 2006. [Google Scholar]

- Kostamovaara, J.; Tenhunen, J.; Kögler, M.; Nissinen, I.; Nissinen, J.; Keränen, P. Fluorescence suppression in Raman spectroscopy using a time-gated CMOS SPAD. Opt. Express 2013, 21, 31632–31645. [Google Scholar] [CrossRef] [PubMed]

- Remondino, F.; Stoppa, D. TOF Range-Imaging Cameras; Springer: Heidelberg, Germany, 2013; Volume 68121. [Google Scholar]

- Niclass, C.; Rochas, A.; Besse, P.-A.; Charbon, E. Design and characterization of a CMOS 3-D image sensor based on single photon avalanche diodes. IEEE J. Solid State Circuits 2005, 40, 1847–1854. [Google Scholar] [CrossRef]

- Stoppa, D.; Pancheri, L.; Scandiuzzo, M.; Gonzo, L.; Betta, G.-F.D.; Simoni, A. A CMOS 3-D Imager Based on Single Photon Avalanche Diode. IEEE Trans. Circuits Syst. I Regul. Pap. 2007, 54, 4–12. [Google Scholar] [CrossRef]

- Niclass, C.; Favi, C.; Kluter, T.; Gersbach, M.; Charbon, E. A 128 × 128 single-photon image sensor with column-level 10-bit time-to-digital converter array. IEEE J. Solid State Circuits 2008, 43, 2977–2989. [Google Scholar] [CrossRef]

- Guerrieri, F.; Tisa, S.; Tosi, A.; Zappa, F. Two-Dimensional SPAD Imaging Camera for Photon Counting. IEEE Photonics J. 2010, 2, 759–774. [Google Scholar] [CrossRef]

- Mori, M.; Sakata, Y.; Usuda, M.; Yamahira, S.; Kasuga, S.; Hirose, Y.; Kato, Y.; Tanaka, T. A 1280 × 720 single-photon-detecting image sensor with 100 dB dynamic range using a sensitivity-boosting technique. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016; pp. 120–121.

- Rochas, A.; Gani, M.; Furrer, B.; Besse, P.A.; Popovic, R.S.; Ribordy, G.; Gisin, N. Single photon detector fabricated in a complementary metal-oxide-semiconductor high-voltage technology. Rev. Sci. Instrum. 2003, 74, 3263–3270. [Google Scholar] [CrossRef]

- Pancheri, L.; Stoppa, D. Low-Noise CMOS single-photon avalanche diodes with 32 ns dead time. In Proceedings of the 37th European Solid State Device Research Conference, Munich, Germany, 11–13 September 2007; pp. 362–365.

- Pancheri, L.; Stoppa, D. Low-noise single photon avalanche diodes in 0.15 μm CMOS technology. In Proceedings of the 41th European Solid State Device Research Conference, Helsinki, Swedish, 12–16 September 2011; pp. 179–182.

- Dalla Betta, G.-F.; Pancheri, L.; Stoppa, D.; Henderson, R.; Richardson, J. Avalanche Photodiodes in Submicron CMOS Technologies for High-Sensitivity Imaging. In Advances in Photodiodes; Dalla Betta, G.-F., Ed.; InTech: Vienna, Austria, 2011; pp. 225–248. [Google Scholar]

- Richardson, J.A.; Webster, E.A.G.; Grant, L.A.; Henderson, R.K. Scaleable Single-Photon Avalanche Diode Structures in Nanometer CMOS Technology. IEEE Trans. Electron. Devices 2011, 58, 2028–2035. [Google Scholar] [CrossRef]

- Karami, M.A.; Yoon, H.J.; Charbon, E. Single-photon avalanche diodes in sub-100 nm standard CMOS technologies. In Proceedings of the International Image Sensor Workshop, Hokkaido, Japan, 8–11 June 2011.

- Webster, E.A.G.; Grant, L.A.; Henderson, R.K. A High-Performance Single-Photon Avalanche Diode in 130-nm CMOS Imaging Technology. IEEE Electron. Device Lett. 2012, 33, 1589–1591. [Google Scholar] [CrossRef]

- Tisa, S.; Guerrieri, F.; Zappa, F. Variable-load quenching circuit for single-photon avalanche diodes. Opt. Express 2008, 16, 2232–2244. [Google Scholar] [CrossRef] [PubMed]

- Pancheri, L.; Stoppa, D.; Dalla Betta, G.-F. Characterization and Modeling of Breakdown Probability in Sub-Micrometer CMOS SPADs. IEEE J. Sel. Top. Quantum Electron. 2014, 20, 328–335. [Google Scholar] [CrossRef]

- Pancheri, L.; Massari, N.; Stoppa, D. SPAD image sensor with analog counting pixel for time-resolved fluorescence detection. IEEE Trans. Electron. Devices 2013, 60, 3442–3449. [Google Scholar] [CrossRef]

- Ghioni, M.; Gulinatti, A.; Rech, I.; Zappa, F.; Cova, S. Progress in Silicon Single-Photon Avalanche Diodes. IEEE J. Sel. Top. Quantum Electron. 2007, 13, 852–862. [Google Scholar] [CrossRef]

- Villa, F.; Bronzi, D.; Zou, Y.; Scarcella, C.; Boso, G.; Tisa, S.; Tosi, A.; Zappa, F.; Durini, D.; Weyers, S.; et al. CMOS SPADs with up to 500 μm diameter and 55% detection efficiency at 420 nm. J. Mod. Opt. 2014, 61, 102–115. [Google Scholar] [CrossRef]

- Niclass, C.; Soga, M. A miniature actively recharged single-photon detector free of afterpulsing effects with 6 ns dead time in a 0.18 μm CMOS technology. In Proceedings of the 2010 International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010; pp. 14.3.1–14.3.4.

- Stoppa, D.; Mosconi, D.; Pancheri, L.; Gonzo, L. Single-Photon Avalanche Diode CMOS Sensor for Time-Resolved Fluorescence Measurements. IEEE Sens. J. 2009, 9, 1084–1090. [Google Scholar] [CrossRef]

- Rech, I.; Ingargiola, A.; Spinelli, R.; Labanca, I.; Marangoni, S.; Ghioni, M.; Cova, S. Optical crosstalk in single photon avalanche diode arrays: A new complete model. Opt. Express 2008, 16, 8381–8394. [Google Scholar] [CrossRef] [PubMed]

- Xu, H.; Pancheri, L.; Braga, L.H.C.; Dalla Betta, G.-F.; Stoppa, D. Crosstalk Characterization of Single-photon Avalanche Diode (SPAD) Arrays in CMOS 150 nm Technology. Procedia Eng. 2014, 87, 1270–1273. [Google Scholar] [CrossRef]

- Piemonte, C.; Acerbi, F.; Ferri, A.; Gola, A.; Paternoster, G.; Regazzoni, V.; Zappala, G.; Zorzi, N. Performance of NUV-HD Silicon Photomultiplier Technology. IEEE Trans. Electron. Devices 2016, 63, 1–6. [Google Scholar] [CrossRef]

- Pancheri, L.; Dalla Betta, G.-F.; Campos Braga, L.H.; Xu, H.; Stoppa, D. A single-photon avalanche diode test chip in 150 nm CMOS technology. In Proceedings of the 2014 International Conference on Microelectronic Test Structures (ICMTS), Udine, Italy, 24–27 March 2014; pp. 161–164.

- Henderson, R.K.; Webster, E.A.G.; Walker, R.; Richardson, J.A.; Grant, L.A. A 3 × 3, 5 μm pitch, 3-transistor single photon avalanche diode array with integrated 11 V bias generation in 90 nm CMOS technology. In Proceedings of the 2010 International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010; pp. 14.2.1–14.2.4.

- Veerappan, C.; Richardson, J.; Walker, R.; Li, D.-U.; Fishburn, M.W.; Maruyama, Y.; Stoppa, D.; Borghetti, F.; Gersbach, M.; Henderson, R.K.; et al. A 16 0 × 128 single-photon image sensor with on-pixel 55 ps 10 b time-to-digital converter. In Proceedings of the 2011 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 20–24 February 2011; pp. 312–314.

- Pancheri, L.; Stoppa, D. A SPAD-based pixel linear array for high-speed time-gated Fluorescence Lifetime Imaging. In Proceedings of the ESSCIRC 2009—35th European Solid-State Circuits Conference, Athens, Greece, 14–18 September 2009; pp. 428–431.

- Niclass, C.; Ito, K.; Soga, M.; Matsubara, H.; Aoyagi, I.; Kato, S.; Kagami, M. Design and characterization of a 256 × 64-pixel single-photon imager in CMOS for a MEMS-based laser scanning time-of-flight sensor. Opt. Express 2012, 20, 11863–11881. [Google Scholar] [CrossRef] [PubMed]

- Braga, L.H.C.; Gasparini, L.; Grant, L.; Henderson, R.K.; Massari, N.; Perenzoni, M.; Stoppa, D.; Walker, R. A Fully Digital 8 × 16 SiPM Array for PET Applications With Per-Pixel TDCs and Real-Time Energy Output. IEEE J. Solid State Circuits 2014, 49, 301–314. [Google Scholar] [CrossRef]

- Perenzoni, M.; Perenzoni, D.; Stoppa, D. A 64 × 64-pixel digital silicon photomultiplier direct ToF sensor with 100 M photons/s/pixel background rejection and imaging/altimeter mode with 0.14% precision up to 6 km for spacecraft navigation and landing. In Proceedings of the 2016 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016; pp. 118–119.

- Burri, S.; Maruyama, Y.; Michalet, X.; Regazzoni, F.; Bruschini, C.; Charbon, E. Architecture and applications of a high resolution gated SPAD image sensor. Opt. Express 2014, 22, 17573–17589. [Google Scholar] [CrossRef] [PubMed]

- Dutton, N.A.W.; Gyongy, I.; Parmesan, L.; Gnecchi, S.; Calder, N.; Rae, B.R.; Pellegrini, S.; Grant, L.A.; Henderson, R.K. A SPAD-Based QVGA Image Sensor for Single-Photon Counting and Quanta Imaging. IEEE Trans. Electron. Devices 2015, 63, 189–196. [Google Scholar] [CrossRef]

- Perenzoni, M.; Massari, N.; Perenzoni, D.; Gasparini, L.; Stoppa, D. A 160 × 120 Pixel Analog-Counting Single-Photon Imager with Time-Gating and Self-Referenced Column-Parallel A/D Conversion for Fluorescence Lifetime Imaging. IEEE J. Solid State Circuits 2016, 51, 155–167. [Google Scholar]

- Parmesan, L.; Dutton, N.A.W.; Caldery, N.J.; Krstaji, N.; Holmes, A.J.; Grant, L.A.; Henderson, R.K. A 256 × 256 SPAD array with in-pixel Time to Amplitude Conversion for Fluorescence Lifetime Imaging Microscopy. In Proceedings of the International Image Sensors Workshop 2015, Vaals, The Netherlands, 8–11 June 2015.

- Stoppa, D.; Borghetti, F.; Richardson, J.; Walker, R.; Grant, L.; Henderson, R.K.; Gersbach, M.; Charbon, E. A 32 × 32-pixel array with in-pixel photon counting and arrival time measurement in the analog domain. In Proceedings of the ESSCIRC 2009, Athens, Greece, 14–18 September 2009; pp. 204–207.

- Bronzi, D.; Villa, F.; Tisa, S.; Tosi, A.; Zappa, F. SPAD Figures of Merit for Photon-Counting, Photon-Timing, and Imaging Applications: A Review. IEEE Sens. J. 2016, 16, 3–12. [Google Scholar] [CrossRef]

- Kondo, T.; Takemoto, Y.; Kobayashi, K.; Tsukimura, M.; Takazawa, N.; Kato, H.; Suzuki, S.; Aoki, J.; Saito, H.; Gomi, Y.; et al. A 3D stacked CMOS image sensor with 16Mpixel global-shutter mode and 2 M pixel 10000 fps mode using 4 million interconnections. In Proceedings of the 2015 Symposium on VLSI Circuits (VLSI Circuits), Kyoto, Japan, 17–19 June 2015; pp. C90–C91.

- Aull, B.F.; Schuette, D.R.; Young, D.J.; Craig, D.M.; Felton, B.J.; Warner, K. A Study of Crosstalk in a 256 × 256 Photon Counting Imager Based on Silicon Geiger-Mode Avalanche Photodiodes. IEEE Sens. J. 2015, 15, 2123–2132. [Google Scholar] [CrossRef]

| [19] | [35] | [36] | [37] | |

|---|---|---|---|---|

| Process | 0.35 μm HV | 0.13 μm CIS | 0.35 μm HV | 0.13 μm CIS |

| Supply | 3.3 V | 1.2 V | 3.3 V | 1.2 V |

| Array size | 32 × 32 | 320 × 240 | 160 × 120 | 256 × 256 |

| Pixel pitch | 25 μm | 8 μm | 15 μm | 8 μm |

| Fill-factor | 20.8% | 26.8% | 21% | 20% |

| NMOS per pixel | 12T + 2C | 8T + 1C | 7T+1C | 8T + 2C |

| Timing | Gating >1.1 ns | Gating > 10 ns | Gating > 0.75 ns | TAC > 0.37 ns |

| Interface | Analog | Analog/Digital 1 b | Analog/Digital 8 b | Analog/Digital 2 b |

| Consumption | 33 mW | 69.5 mW | 20.6 mW a | n.a. |

| 157 mW b |

© 2016 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC-BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Perenzoni, M.; Pancheri, L.; Stoppa, D. Compact SPAD-Based Pixel Architectures for Time-Resolved Image Sensors. Sensors 2016, 16, 745. https://doi.org/10.3390/s16050745

Perenzoni M, Pancheri L, Stoppa D. Compact SPAD-Based Pixel Architectures for Time-Resolved Image Sensors. Sensors. 2016; 16(5):745. https://doi.org/10.3390/s16050745

Chicago/Turabian StylePerenzoni, Matteo, Lucio Pancheri, and David Stoppa. 2016. "Compact SPAD-Based Pixel Architectures for Time-Resolved Image Sensors" Sensors 16, no. 5: 745. https://doi.org/10.3390/s16050745

APA StylePerenzoni, M., Pancheri, L., & Stoppa, D. (2016). Compact SPAD-Based Pixel Architectures for Time-Resolved Image Sensors. Sensors, 16(5), 745. https://doi.org/10.3390/s16050745