Current Measurement Transducer Based on Current-To-Voltage-To-Frequency Converting Ring Oscillator with Cascade Bias Circuit

Abstract

:1. Introduction

2. Previous I–F Converting Current Transducer

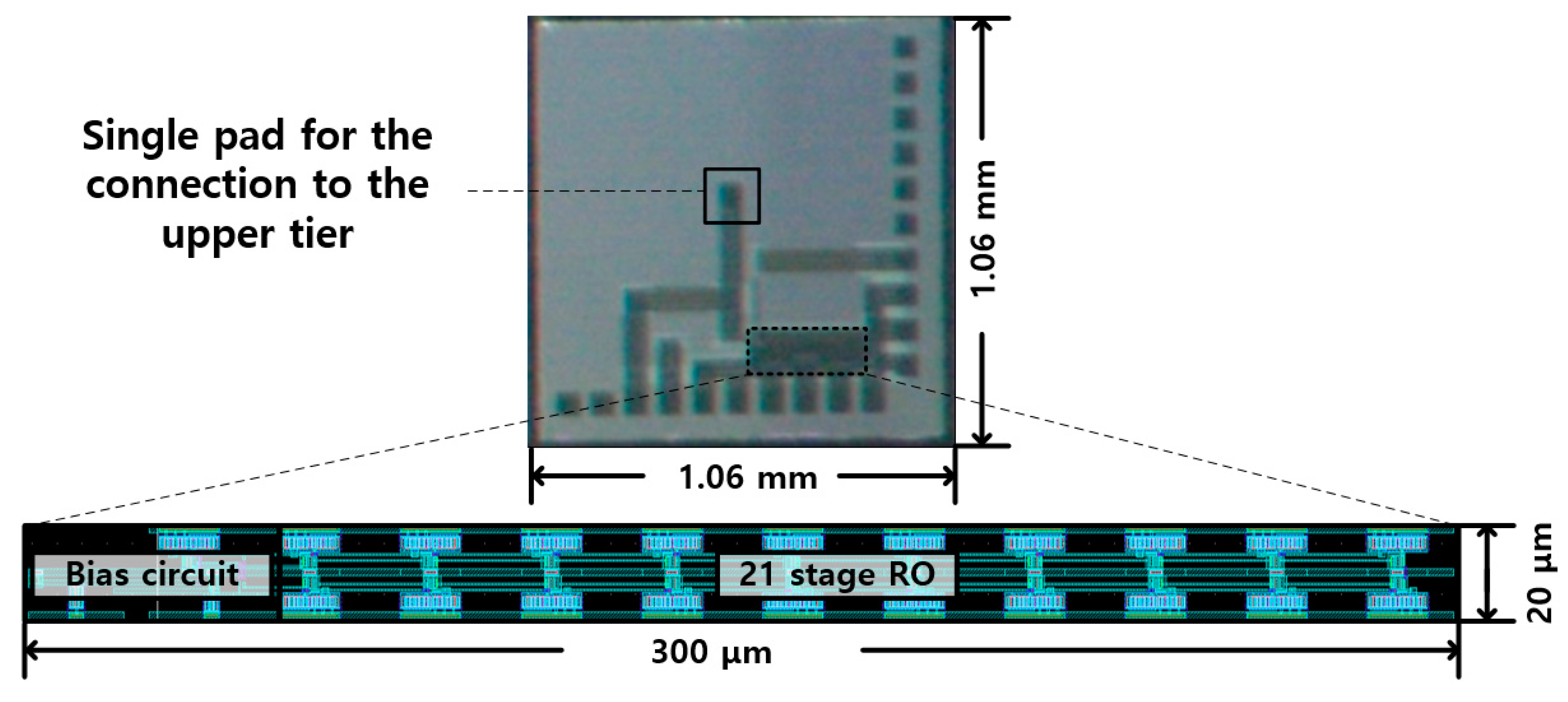

3. Proposed I–V–F Converting Current Transducer

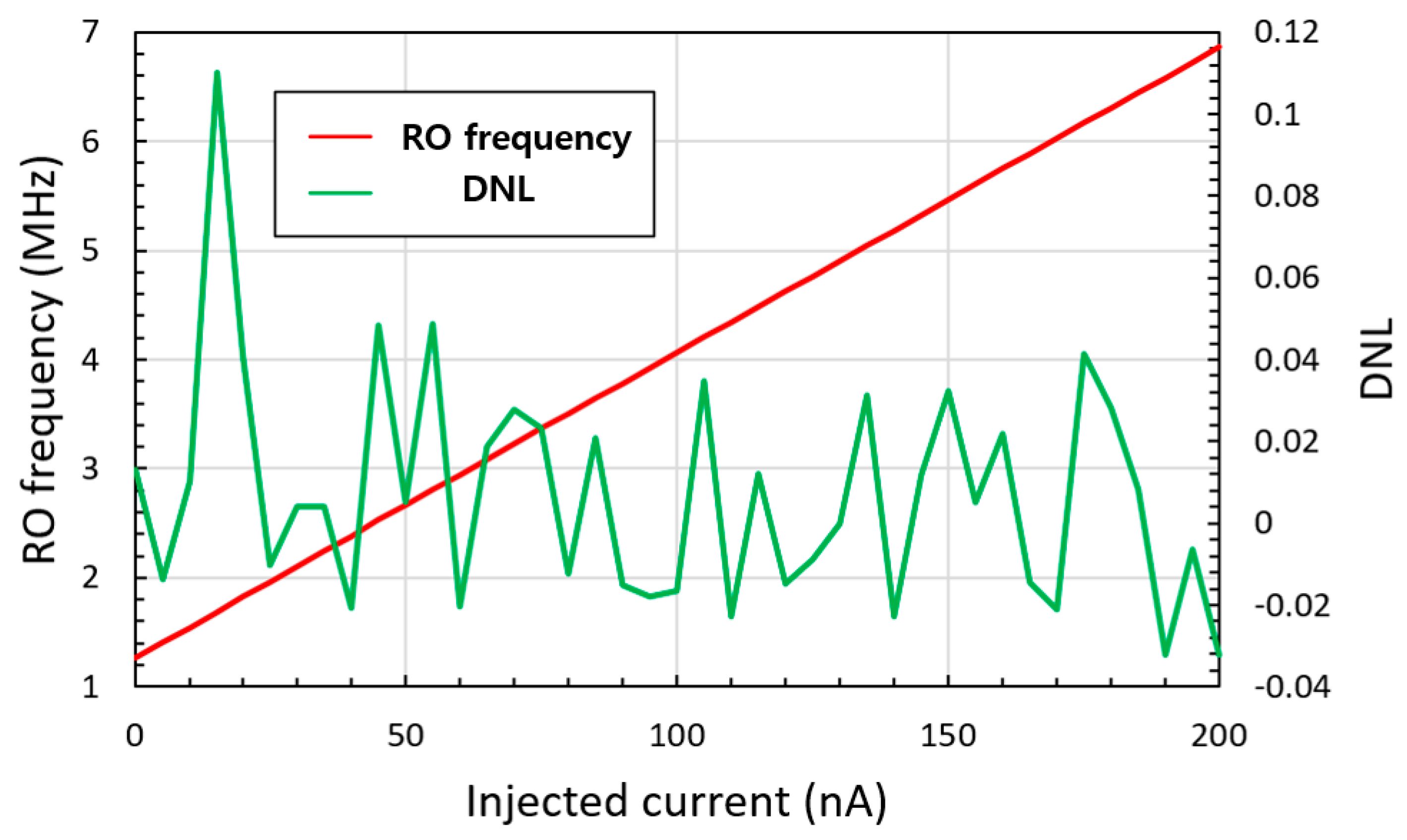

4. Results and Discussion

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Stanacevic, M.; Murari, K.; Murari, K.; Rege, A.; Cauwenberghs, G.; Thakor, N.V. VLSI Potentiostat Array with Oversampling Gain Modulation for Wide-Range Neurotransmitter Sensing. IEEE Trans. Biomed. Circuits Syst. 2007, 1, 63–72. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Jin, X.; Fisher, T.S.; Alam, M.A. Generalized Compact Modeling of Nanoparticle-Based Amperometric Glucose Biosensors. IEEE Trans. Electron Devices 2016, 63, 4924–4932. [Google Scholar] [CrossRef]

- Kim, S.K.; Shim, J.; Geum, D.; Kim, C.Z.; Kim, H.; Kim, Y.; Kang, H.; Song, J.D.; Choi, S.; Kim, D.H.; et al. Cost-effective Fabrication of In0.53Ga0.47As-on-Insulator on Si for Monolithic 3D via Novel Epitaxial Lift-Off (ELO) and Donor Wafer Re-use. In Proceedings of the IEEE International Electron Devices Meeting, San Francisco, CA, USA, 3–7 December 2016; pp. 25.4.1–25.4.4. [Google Scholar] [CrossRef]

- Prabha, P.; Kim, S.J.; Reddy, K.; Rao, S.; Griesert, N.; Rao, A.; Winter, G.; Hanumolu, P.K. A Highly Digital VCO-Based ADC Architecture for Current Sensing Applications. IEEE J. Solid-State Circuits 2015, 50, 1785–1795. [Google Scholar] [CrossRef]

- Xie, Y.; Liang, Y.; Liu, M.; Liu, S.; Zhu, Z. A 10-Bit 5 MS/s VCO-SAR ADC in 0.18-μm CMOS. IEEE Trans. Circuits Syst. II Express Br. 2019, 66, 26–30. [Google Scholar] [CrossRef]

- Liao, Y.; Yao, H.; Lingley, A.; Parviz, B.A.; Otis, B.P. A 3-μW CMOS Glucose Sensor for Wireless Contact-Lens Tear Glucose Monitoring. IEEE J. Solid-State Circuits 2012, 47, 335–344. [Google Scholar] [CrossRef]

- Pletea, I.; Wurman, Z.; Or-Bach, Z.; Şontea, V. Monolithic 3D layout using 2D EDA for embedded memory-rich designs. In Proceedings of the IEEE S3S, Rohnert Park, CA, USA, 5–8 October 2015. [Google Scholar] [CrossRef]

| Process Corner | SS | SF | TT | FS | FF |

| Frequency gain (kHz/nA) | 26.701 | 27.275 | 27.299 | 27.356 | 27.653 |

| Maximum DNL | 0.1237 | 0.1123 | 0.1145 | 0.1186 | 0.1423 |

| Temperature | 0 °C | 25 °C | 50 °C | 75 °C | 100 °C |

| Frequency gain (kHz/nA) | 27.267 | 27.299 | 27.334 | 27.384 | 27.447 |

| Maximum DNL | 0.1167 | 0.1145 | 0.1153 | 0.1186 | 0.183 |

| Supply Voltage | 1.62 V | 1.8 V | 1.98 V | ||

| Frequency gain (kHz/nA) | 27.132 | 27.299 | 27.532 | ||

| Maximum DNL | 0.1327 | 0.1145 | 0.1246 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Park, J.; Park, J.-H.; Jung, S.-O. Current Measurement Transducer Based on Current-To-Voltage-To-Frequency Converting Ring Oscillator with Cascade Bias Circuit. Sensors 2020, 20, 493. https://doi.org/10.3390/s20020493

Park J, Park J-H, Jung S-O. Current Measurement Transducer Based on Current-To-Voltage-To-Frequency Converting Ring Oscillator with Cascade Bias Circuit. Sensors. 2020; 20(2):493. https://doi.org/10.3390/s20020493

Chicago/Turabian StylePark, Jongha, Jung-Hyun Park, and Seong-Ook Jung. 2020. "Current Measurement Transducer Based on Current-To-Voltage-To-Frequency Converting Ring Oscillator with Cascade Bias Circuit" Sensors 20, no. 2: 493. https://doi.org/10.3390/s20020493

APA StylePark, J., Park, J. -H., & Jung, S. -O. (2020). Current Measurement Transducer Based on Current-To-Voltage-To-Frequency Converting Ring Oscillator with Cascade Bias Circuit. Sensors, 20(2), 493. https://doi.org/10.3390/s20020493