2.2. TMR Sensitive Element and Interface Circuit

The miniaturized solid-state magnetometers mainly include Hall-effect magnetometers, anisotropic magneto-resistance, giant magneto-resistance, and tunneling magneto-resistance [

8,

9]. The TMR element with multilayer film structure has created more and more applications in the magnetometer devices due to its high sensitivity and low-power consumption [

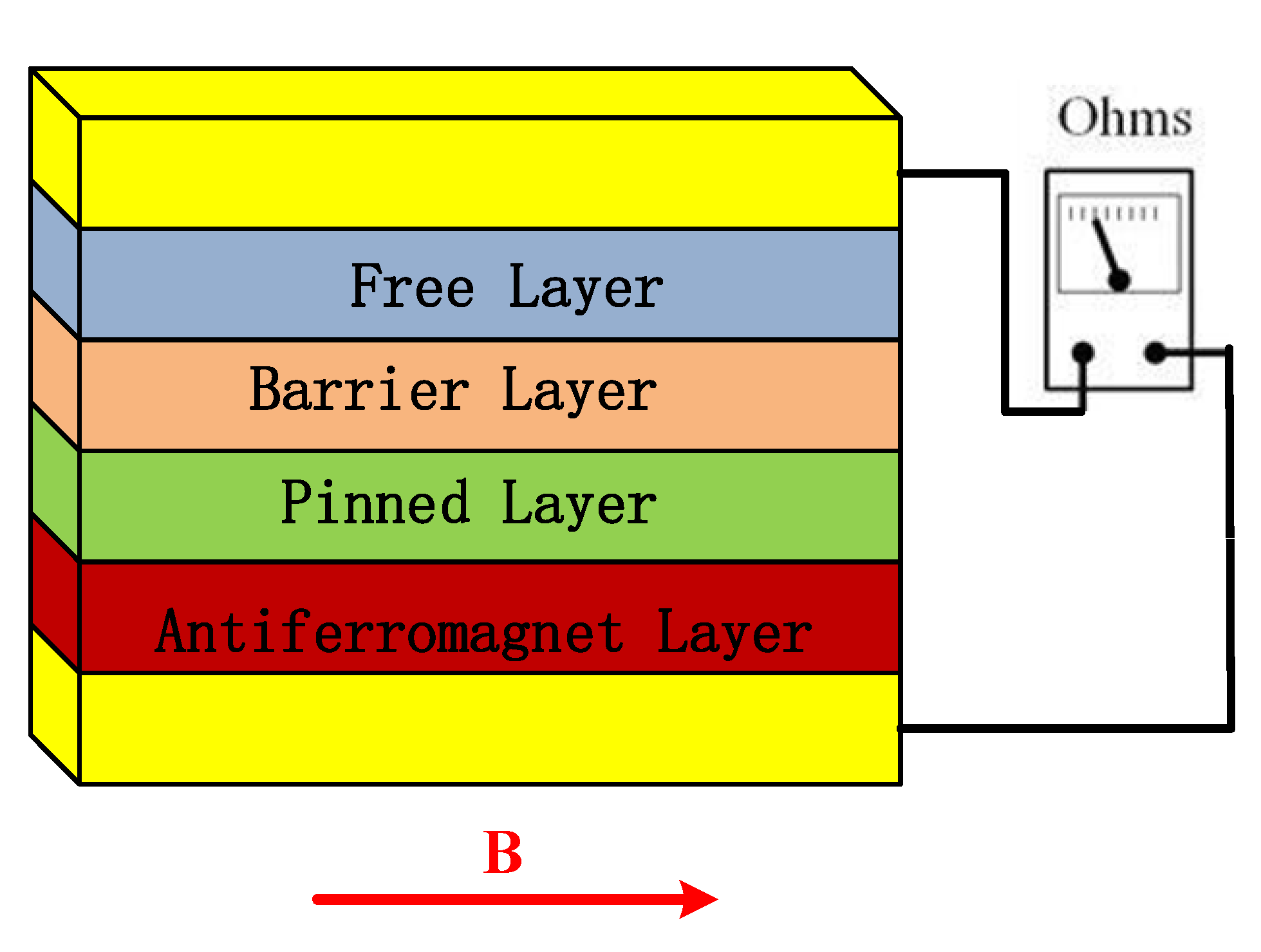

10]. The sensitive structure part of tunneling magneto-resistive sensor mainly consists of pinning layer, tunnel barrier, and free layer. The pinning layer composed of ferromagnetic layer and anti-ferromagnetic layer (AFM layer). The exchange coupling between ferromagnetic layer and anti-ferromagnetic layer determines the direction of the magnetic moment of a ferromagnetic layer; tunneling barrier layer is usually composed of MgO or Al

2O

3, located in the upper part of anti-ferromagnetic layer [

11]. As shown in

Figure 1 the arrows represent the direction of the magnetic moment of the pinning layer and the free layer. The magnetic moment of the pinning layer is relatively fixed under the action of a certain size of magnetic field. The magnetic moment of the free layer is relatively free and rotatable to the magnetic moment of the pinning layer, and it will turn over with the change of the magnetic field. The typical thickness of each film layer is between 0.1 nm and 10 nm [

12,

13,

14]. The sensitive element concludes 32 magnetic tunneling junctions (MTJ). The area of magnetic tunneling junctions is 50 μm

2. In this work, the thickness of free layer/barrier layer/pinning layer is 10/1/10 nm. The multilayer structure of MTJ is Ta/Ru/Ta/PtMn/CoFe/Ru/CoFeB/MgO/CoFeB/NiFe/Ru/Ta. Thin film is deposited by magnetron sputtering. MgO materials are used in the barrier layer so that TMR element is more sensitive and higher resolution. A Wheatstone bridge configuration composed of four active TMR arrays are applied by thin film process. The three-axis TMR sensitive element is built by stereoscopic orthogonal package. The sensitive element with flux modulation structure used for design, simulation and test in this work is from the Multidimension Technology Company. The sensitive element can achieve a background noise of 150 pT/Hz

1/2 by the vertical modulation film and a power consumption of 12.5 mW at 5 V power supply. Major parameter indicators are shown as in

Table 1.

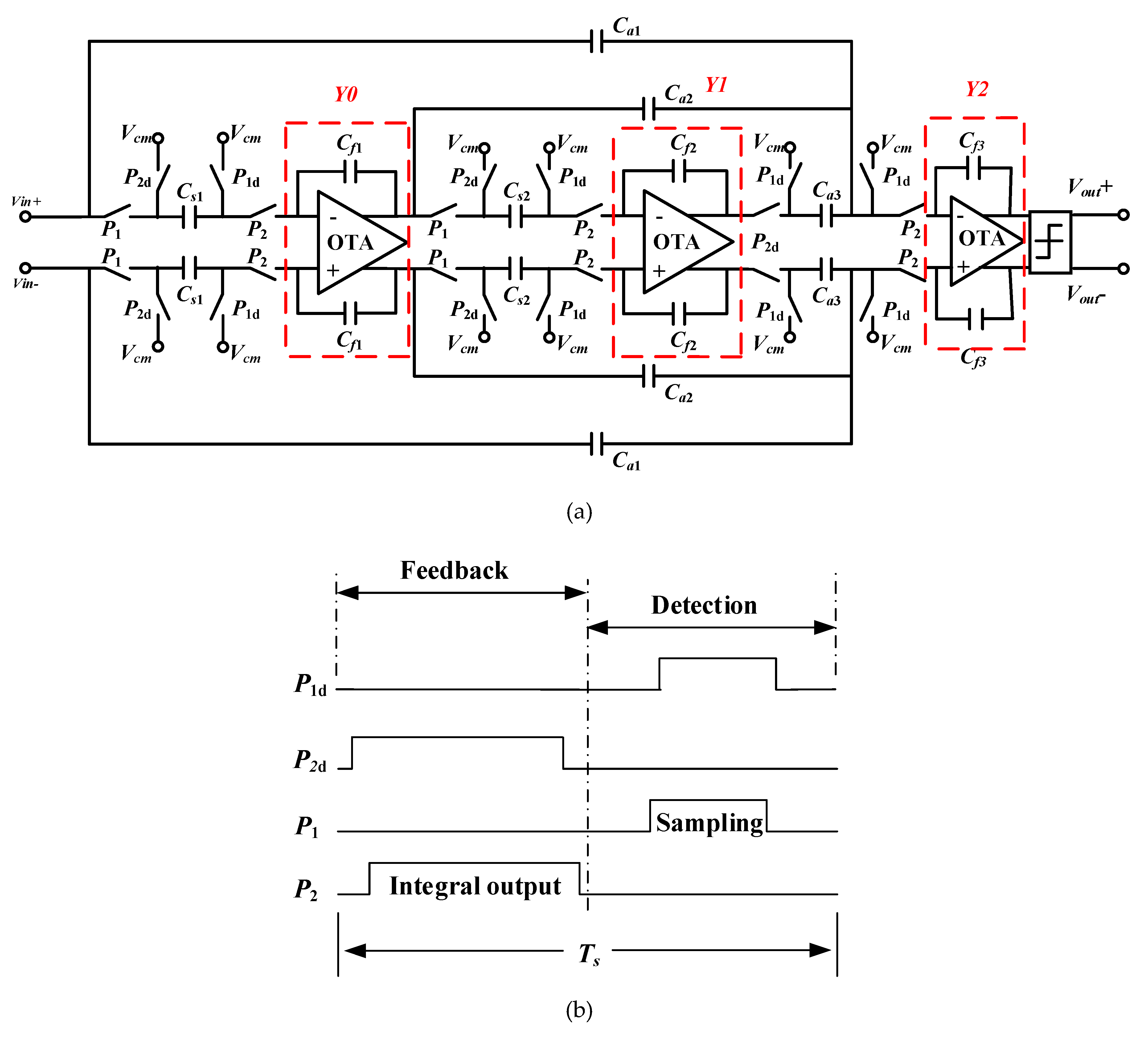

The read-out interface circuit of TMR sensors is consisted of a current feedback instrumentation amplifier circuit (CFIA), a sigma-delta modulator and desampling filters as shown in

Figure 2. For a tunneling magneto-resistance sensor element, a current feedback instrumentation amplifier circuit is used for the preceding stage weak signal detection. The main noise source of the system comes from low-frequency 1/

f noise. In order to eliminate low-frequency noise of sensors and improve the SNR of bandgap reference, the chopper stabilization technique is applied. The analog signals are converted into high-precision digital signals by sigma-delta ADC. We proposed the third-order CIFF (cascade-of-integrators feed-forward) sigma-delta interface circuit and the working sequence as shown in

Figure 3. The first stage switched capacitor integrator is the key unit of sigma-delta modulator system to realize loop filtering. Because the discrete signals are processed in switched capacitor circuit, the nonlinear analysis of the switched capacitor integrator is mainly in the discrete time domain. The timing diagram of the sigma-delta is as shown in

Figure 3b. There are four phases in operation of the circuit which is feedback phase, detection phase, sampling phase, and integral output phase. Wherein P1 and P2 are the two-phase non-overlapping clock, P1 is active-high, P2 is active-low. The shutdown time of P1d is later than P1, the shutdown time of P2d is later than P2, it can effectively suppress the influence of charge injection and clock-feedthrough in the switched-capacitor circuit. The feedback and detection phase operate at different times of a cycle to eliminate noise coupling. In the sampling phase, the input voltage signal is reset to ensure a correct bias point and the sampling capacitor is discharged to erase the memory from the previous cycle. The nonlinearity of switched capacitor integrators mainly originates from non-ideal factors of operational amplifier, such as non-linear DC gain, limited gain bandwidth, and limited voltage swing rate of op-amp which can lead to non-linearity during the transient establishment of integrators and generating high-order harmonic distortion in the system output. Considering the influence of the finite non-linear DC gain of the operational amplifier on the integrator nonlinearity, the DC gain of the operational amplifier is finite and varies with the output voltage [

15]. This can lead to harmonic distortion of the sigma-delta system.

2.3. Analysis and Optimization of Harmonic Distortion

The non-ideal factors of operational amplifier mainly lead to the non-linearity of integrator in the integration stage. The equivalent non-ideal model of integrator is as shown in

Figure 4 in the integration stage.

Cs, Cf, Cp, and

CL are sampling capacitors, integral feedback capacitors, parasitic capacitors, and load capacitors,

A is operational amplifier gain,

Vin and

Vo are input and output signal respectively,

Va is the potential at

a point,

gm and

go are the input and output transconductance of operational amplifier respectively.

According to the input-output relationship of the operational amplifier, where gain

A varies with the output voltage

For a fully differential structure, if

is an even function, its odd coefficients are all zero.

Among them, the parameters

a2 and

a4 can be determined by the gain non-linear model [

16].

In the mode, A0 is the DC gain of the operational amplifier and Vos is the output voltage swing.

According to integration stage model in the integrator, in the initial state, assuming that

CL value is very large, it can be obtained from the charge conservation.

Among them,

,

,

Ts is the sampling clock cycle. In the integral stage, the transient current equation is

According to the above results, the integral establishment is analyzed:

①If , , this is the transient establishment process of integral stage.

Among them, , , , operational amplifier voltage pendulum rate(SR) can be expressed as: , unit gain bandwidth product can be expressed as: , time constant can be expressed as .

We can obtain

Vn(t) at transient establishment phase of integrator

Among them,

,

,

. At the end of the integral,

t = Ts/2, the output of the sigma-delta system can be expressed as

The results of the equation show that when the swing rate is large enough, if the nonlinearity of DC gain is neglected, there is no nonlinearity in the integrator output, which indicates that the limited swing rate and bandwidth of the operational amplifier will not lead to nonlinearity at the integrator establishment process. According to the generation mechanism of harmonic distortion in discrete time domain, the nonlinearity of the integrator is only caused by the nonlinear gain of operational amplifier.

②When

,

, limited swing rate and bandwidth of operational amplifier may lead to the nonlinearity of integrator transient establishment

The equation at the transient establishment process of integral stage can be expressed as

When

, at the end of the integral, the output of the sigma-delta system can be expressed as

The final output of the sigma-delta system can be expressed as

In the Equation (13)

t0 is related to the input signal. Even if the nonlinearity of operational amplifier gain is neglected, the nonlinearity of integrator output can lead to system output harmonics. We summarize the above analysis results: for the given swing rate and bandwidth of operational amplifier, when the input signal amplitude is small, the final output of integrator is given by Equation (9). There is no nonlinearity in the integrator. When the amplitude of input signal increases to a certain value, the integrator output is determined by Equation (13). Obviously, the establishment process of integrator is non-linear at this time. According to Equation (9), Equation (12), Equation (13), gain nonlinearity in the Equation (2) and Equation (3), the nonlinear model of integrator can be established as shown in

Figure 5a.

In order to verify the analysis results and the established model, we add the model as shown in

Figure 5a to the ideal third-order electrical modulator model and then simulate. The dynamic simulation of the modulator is carried out by changing the DC gain of the operational amplifier, and the output results are analyzed. Because the typically output from TMR element is ac signal at the millivolt range. In simulation, we set the input sine wave signal as a frequency of 125 Hz, an amplitude of 1V. The PSD (power spectral density) output of the ideal model is compared with that of the model with nonlinear integrator as shown

Figure 5b,c. In the integrator, the DC gain of the operational amplifier gain is 68 dB, the voltage swing rate is 40 mV/s, and the unit gain bandwidth product is 40 MHz. It can be seen from the figure that the harmonic distortion of the system increases obviously after the integrator nonlinearity is added. In order to further analyze the influence of operational amplifier gain, we set a signal frequency of 250 Hz as the input signal and change the operational amplifier gain and input signal amplitude. The third harmonic distortion of the system changing with operational amplifier gain is shown in

Figure 5d. Due to the influence of operational amplifier nonlinear gain, as the operational amplifier gain decreases, the output harmonic distortion of the system will increase.

The switch is a key module in the switched-capacitor (S-C) sigma-delta modulator circuit. The nonlinearity will have a great influence on the linearity of the system [

17]. The nonlinearity of the switch mainly includes on resistance nonlinearity and channel charge injection nonlinearity [

18]. If only NMOS or PMOS is used as switch, the

Ron (conduction resistance) will change nonlinearly with the input signal, this will introduce harmonic distortion to the system. The CMOS complementary switch is commonly used in switched-capacitor circuit. We set the coefficient

KN and

KP as the Equation (14).

The

Ron (conduction resistance) of the switch can be expressed as

If we ignore the substrate bias effect, then design the suitable size

. The linearity of the switch will be optimized. If we consider the substrate bias effect, the threshold voltage

VTHN and

VTHP can be expressed as

So we can obain the Equation (17), in the Equation (17)

V1 and

V2 can be expressed as

In general,

, the Equation (17) can be simplified as

Due to the substrate bias effect, the conduction resistance of CMOS complementary switch still has some nonlinearity. In addition, the conduction resistance of the switch will also affect the integrator. In the sampling phase of integrator, the conduction resistance of switches

P1 and

P1d can be expressed as

At the end of sampling, the amount of charge on the capacitance C

S can be expressed as

In the Equation (21),

. In the integration stage, the actual amount of charge transfer stored on C

S can be expressed as

In the Equation (22),

. The signal transfer function and transfer function of integrator can be expressed as

In addition, the channel charge injection effect and clock feedthrough effect of MOS transistor are the main causes of switching nonlinearity. The channel charge injection model is shown in

Figure 6a. When the switch is on, the total charge

Qch in the inversion layer can be expressed as

When the switch is off, the charge will flow out through the source end and the drain end. The ratio of charge injection to capacitance

CH is related to the ratio of total capacitance, threshold voltage, input voltage and width-to-length ratio. The error voltage of the output in the CMOS complementary switch can be expressed as

In the design of switch, we set:

and

. The output

Vo can be expressed as

Considering the substrate bias effect and

. The output

Vo can be expressed as

The above Equation (28) shows that for CMOS complementary switches, the channel charge injection effect is still nonlinear and leads to harmonic generation. With the increase of switch size, the impact is intensified, so the switch size should be properly selected in the design. Obviously, the main reason why the channel charge injection effect brings nonlinearity to the system is the substrate bias effect. In order to effectively suppress the clock feedthrough effect and channel charge injection effect, we designed six-transistor CMOS complementary switch with virtual transistors as shown in

Figure 6b. The transistor

M1 and

M3 constitute complementary switch,

M2 and

M4 as virtual transistors can absorb the channel injected charge when the clock is turned off. We can reasonably design the width-to-length ratio of virtual transistors to minimize the clock feedthrough effect. We optimally designed the parameters in switches and the first-stage integrator as shown in

Table 2.

After analyzing the harmonic distortion of interface circuit, the circuit parameters of each module are calculated and optimized. In order to verify the rationality of calculation and analysis, we use the high-speed parallel simulator in Cadence to verify the function of the whole system. We use 0.35 μm CMOS standard technology and set a simulated power supply voltage of 5 V. Because the typically output from TMR element is ac signal at the millivolt range. We set an input signal amplitude of 300 mV and a signal frequency of 250 Hz in simulation. We designed a closed-loop gain of 26 dB in the CFIA. The transient simulation output waveform of integrators at all levels is as shown in

Figure 7. The waveforms in

Figure 7 are the first level integrator, the second level integrator and the third level integrator from top to bottom respectively. It can be seen from the

Figure 7 that the output of integrators at all levels is stable and the output swing is small.

Figure 8 shows the output waveforms of sigma-delta quantizer and sampling clock respectively. When the rising edge of the sampling clock is valid, the quantizer starts to output. When the sampling clock is off, the output of the quantizer keeps the output of the previous time. It can be seen from the output waveform in the

Figure 8 that using the sampling clock as a reference, the output of the quantizer does not have a continuous high or low level for a long time, which can show a good stability in the high-order sigma-delta system.

The sigma-delta TMR micro-sensors system (TMR sensitive element together with interface circuit) is simulated. We sample the output results of the quantizer at equal intervals and sample 65536 points for fast Fourier transform (FFT) analysis. The power spectral density (PSD) calculated and processed in MATLAB (R2016a, MathWorks, Natick, US) is shown in

Figure 9. It can be seen from the results shown that the system realizes the function of noise shaping and the quantization noise at the low-frequency is shaped to the high-frequency. The noise floor level is lower than −140 dBV/Hz

1/2. According to a reference voltage of ±2.5 V, the output noise voltage density in the signal band is lower than 250 nV/Hz

1/2. Since the sensitivity of the sigma-delta TMR micro-sensors system is 0.1 V/Oe (1 Oe=10

−4 T), the equivalent input noise of TMR sensors in the signal bandwidth is less than 0.25 nT/Hz

1/2.

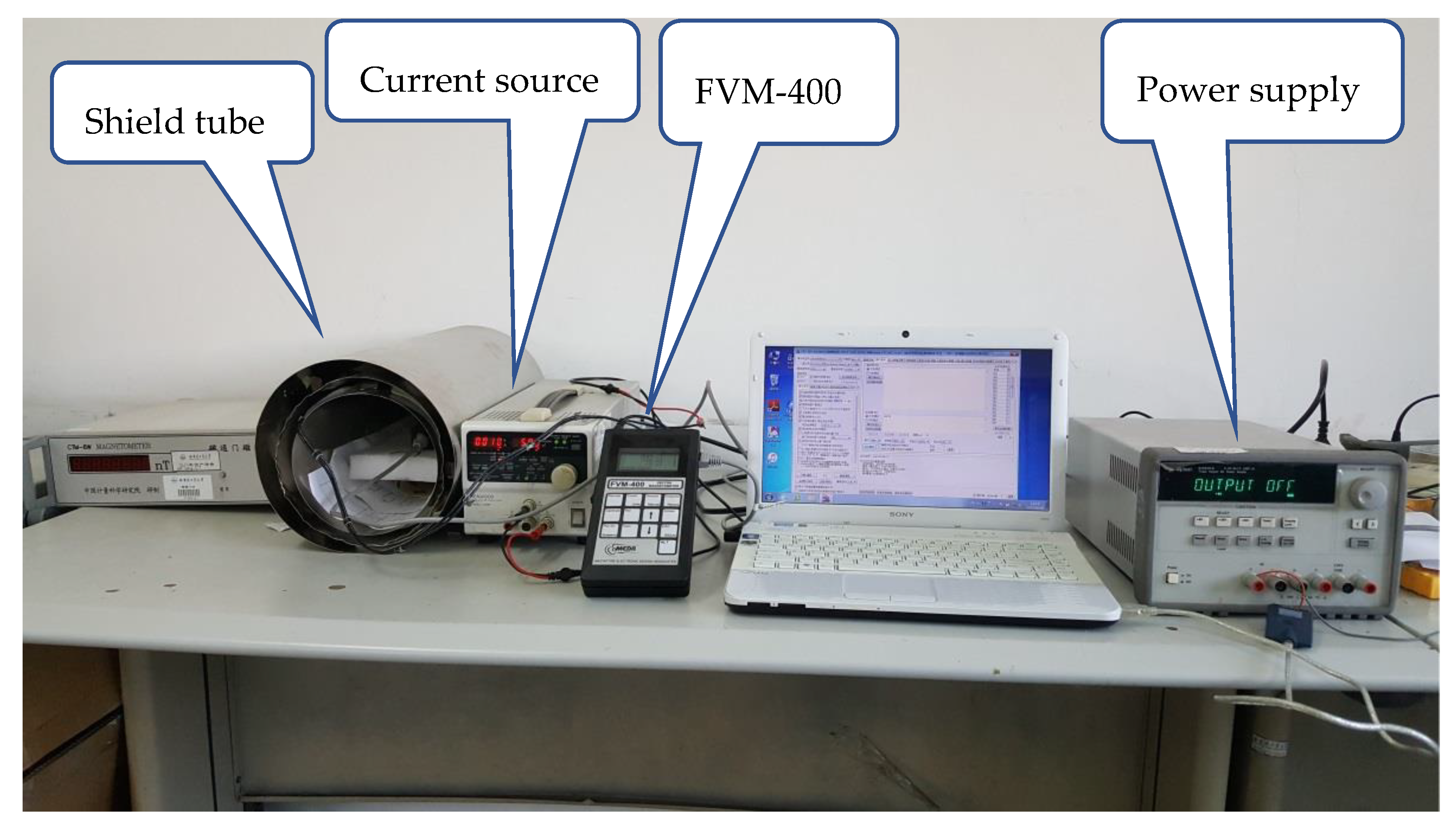

When the amplitude of input signal is large, the third harmonic distortion as shown in

Figure 9 is less than −110 dB. In order to verify the performance of TMR sensors interface circuit, the ideal sensitive structure is used in the simulation. The interface circuit adopts the full differential structure, so it can be seen from output FFT results that the second harmonic distortion is not obvious in the circuit simulation. The third harmonic distortion mainly comes from the nonlinearity of the first-stage integrator and the switch.