Time-Interleaved SAR ADC with Background Timing-Skew Calibration for UWB Wireless Communication in IoT Systems

Abstract

:1. Introduction

2. Timing-Skew Calibration Techniques: A Review

3. Proposed Timing-Skew Calibration Scheme

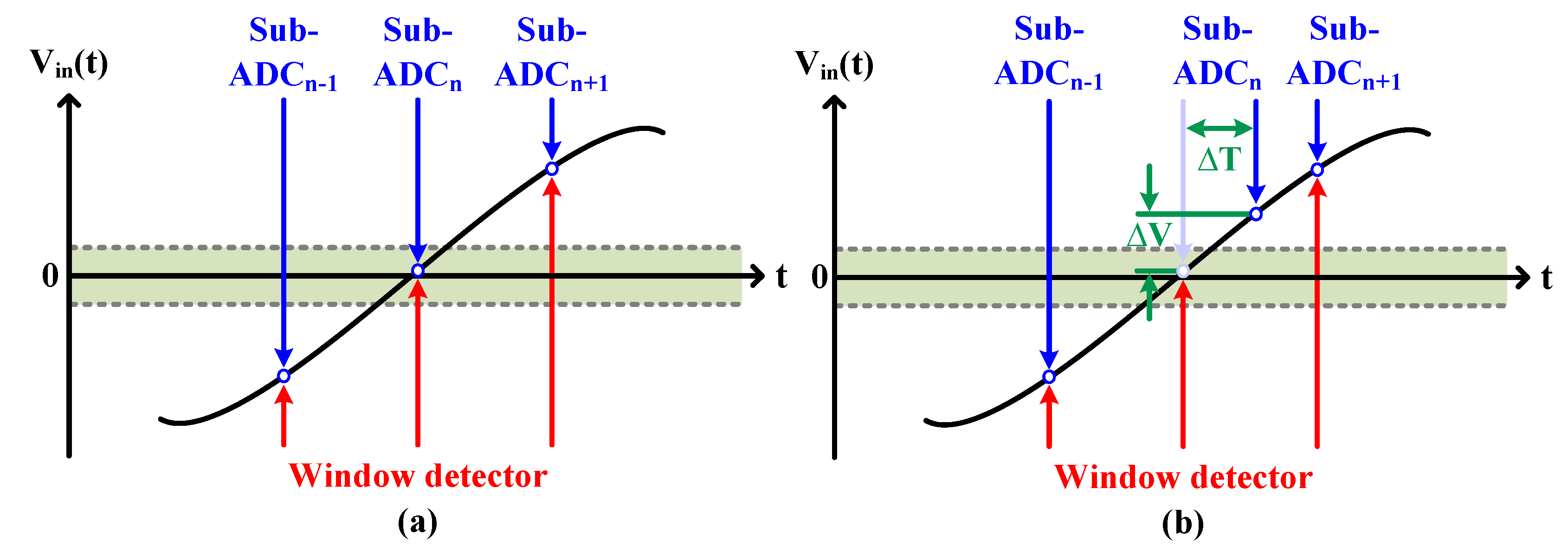

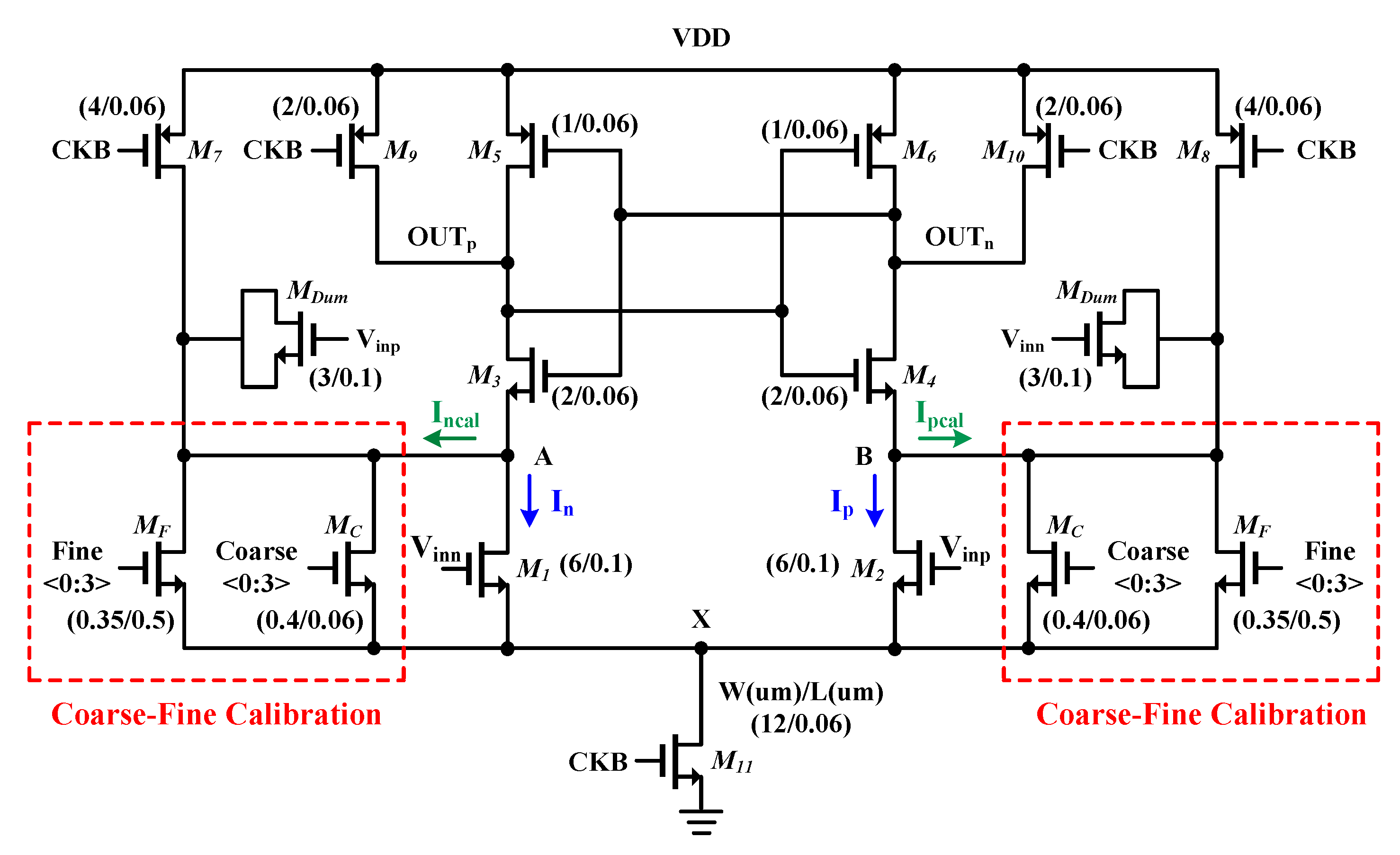

3.1. Comparator Offset-based Window Detector

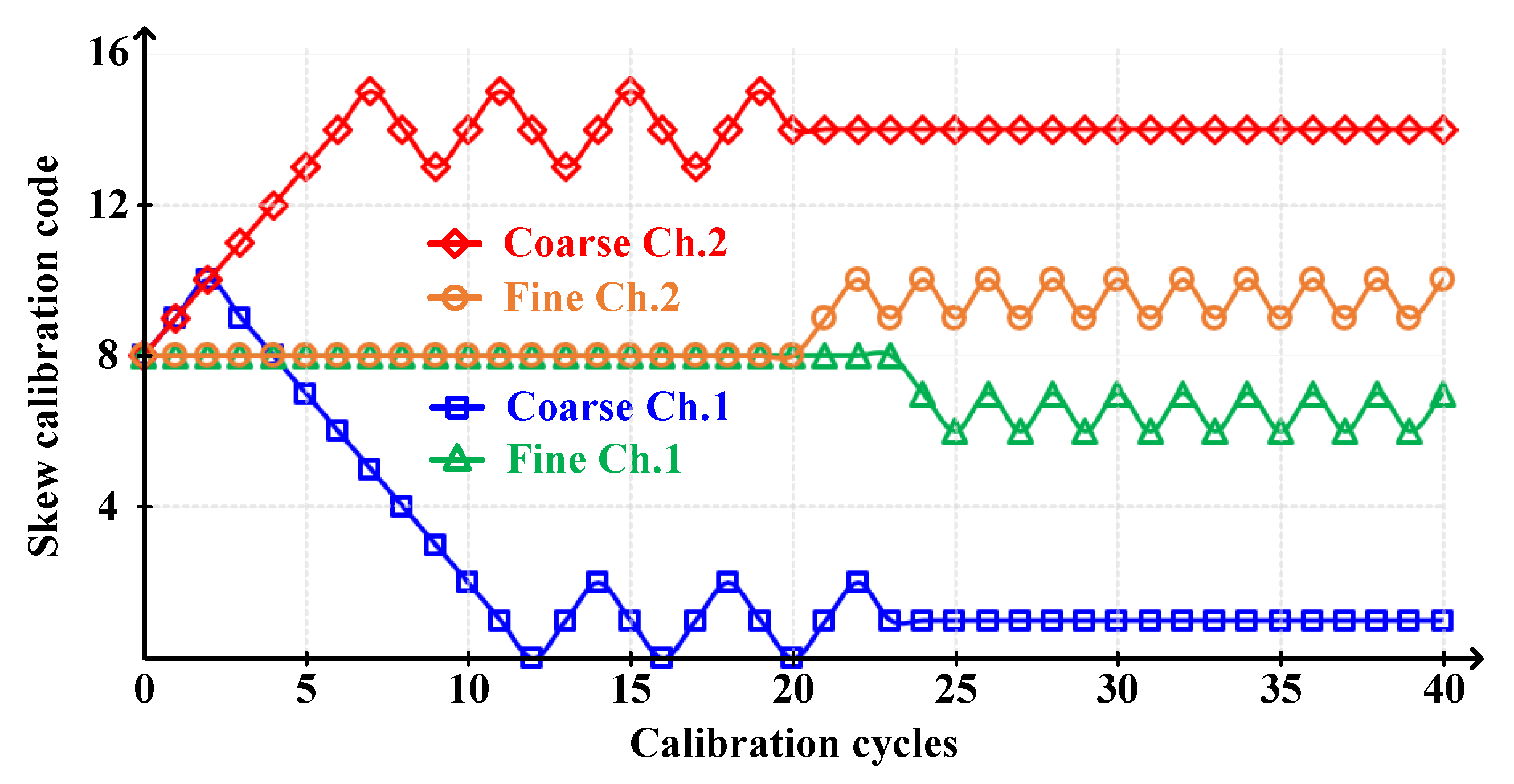

3.2. Timing-Skew Calibration Algorithm

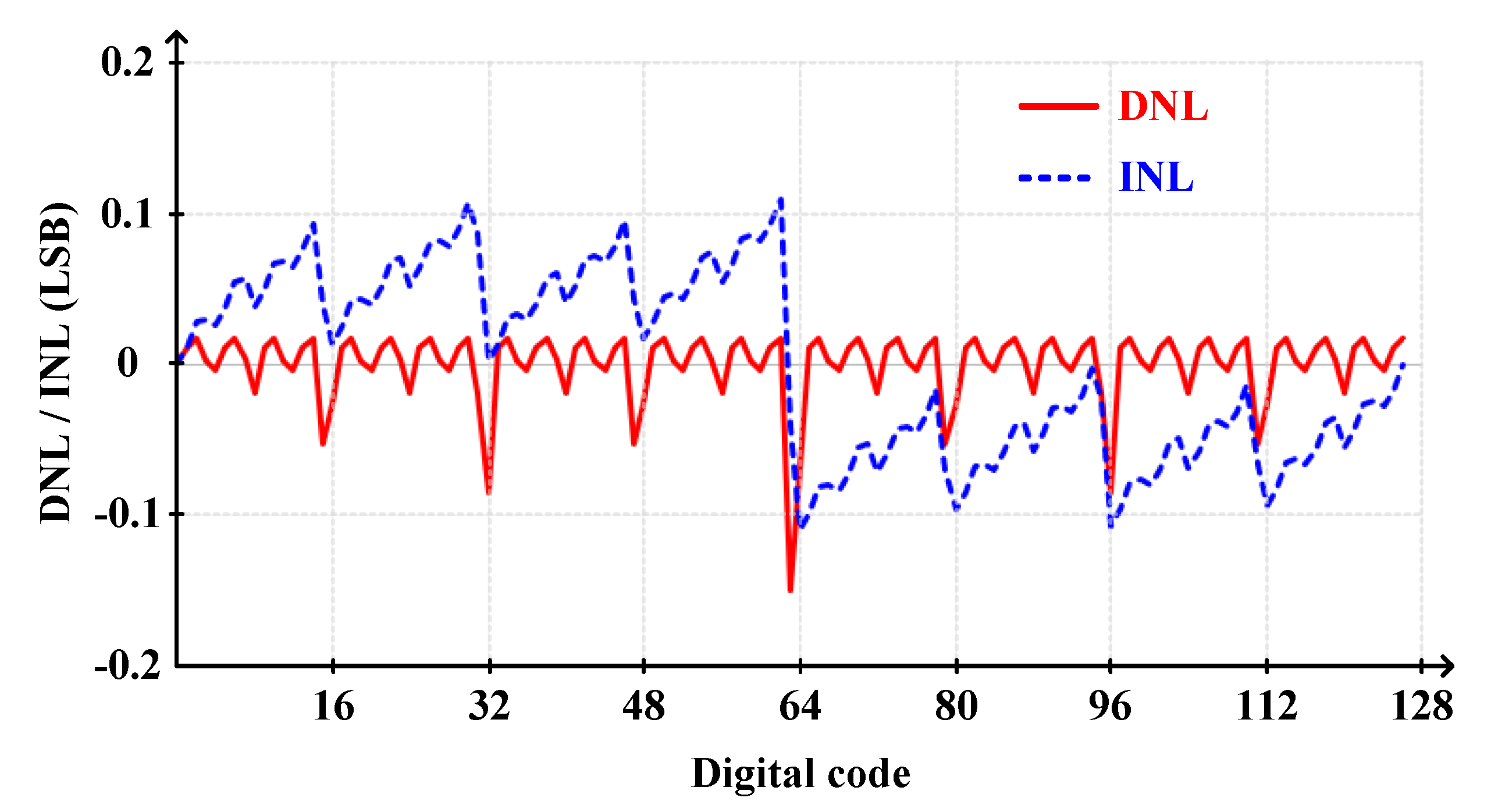

4. Results

5. Conclusions

Author Contributions

Acknowledgments

Conflicts of Interest

References

- Islam, S.M.R.; Kwak, D.; Kabir, M.H.; Hossain, M.; Kwak, K. The Internet of Things for Health Care: A Comprehensive Survey. IEEE Access 2015, 3, 678–708. [Google Scholar] [CrossRef]

- Marjani, M.; Nasaruddin, F.; Gani, A.; Karim, A.; Hashem, I.A.T.; Siddiqa, A.; Yaqoob, I. Big IoT Data Analytics: Architecture, Opportunities, and Open Research Challenges. IEEE Access 2017, 5, 5247–5261. [Google Scholar] [CrossRef]

- Lee, W.; Kang, T.; Lee, J.; Han, K.; Kim, J.; Pedram, M. TEI-ULP: Exploiting Body Biasing to Improve the TEI-Aware Ultralow Power Methods. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2019, 38, 1758–1770. [Google Scholar] [CrossRef]

- Yoon, D.; Jung, D.; Jung, B.; Choi, J.; Jo, Y.; Lee, S.; Lee, W.; Baek, K. LW-DEM: Designing a Low Power Digital-to-Analog Converter Using Lightweight Dynamic Element Matching Technique. IEEE Access 2019, 7, 112617–112628. [Google Scholar] [CrossRef]

- Alpman, E.; Lakdawala, H.; Carley, L.R.; Soumyanath, K. A 1.1 V 50 mW 2.5 GS/s 7b Time-Interleaved C-2C SAR ADC in 45 nm LP digital CMOS. In Proceedings of the 2009 IEEE International Solid-State Circuits Conference-Digest of Technical Papers, San Francisco, CA, USA, 8–12 February 2009; pp. 76–77. [Google Scholar]

- Nakajima, Y.; Sakaguchi, A.; Ohkido, T.; Kato, N.; Matsumoto, T.; Yotsuyanagi, M. A Background Self-Calibrated 6b 2.7 GS/s ADC With Cascade-Calibrated Folding-Interpolating Architecture. IEEE J. Solid-State Circuits 2010, 45, 707–718. [Google Scholar] [CrossRef]

- Ku, I.; Xu, Z.; Kuan, Y.; Wang, Y.; Chang, M.F. A 40-mW 7-bit 2.2-GS/s time-interleaved subranging ADC for low-power gigabit wireless communications in 65-nm CMOS. In Proceedings of the 2011 IEEE Custom Integrated Circuits Conference (CICC), San Jose, CA, USA, 19–21 September 2011; pp. 1–4. [Google Scholar]

- Sung, B.; Lee, C.; Kim, W.; Kim, J.; Hong, H.; Oh, G.; Lee, C.; Choi, M.; Park, H.; Ryu, S. A 6 bit 2 GS/s flash-assisted time-interleaved (FATI) SAR ADC with background offset calibration. In Proceedings of the 2013 IEEE Asian Solid-State Circuits Conference (A-SSCC), Singapore, 11–13 November 2013; pp. 281–284. [Google Scholar]

- Tai, H.; Tsai, C.; Tsai, P.; Chen, H.; Chen, H. A 6-bit 1-GS/s Two-Step SAR ADC in 40-nm CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2014, 61, 339–343. [Google Scholar] [CrossRef]

- Chung, Y.; Rih, W.; Chang, C. A 6-bit 1.3-GS/s Ping-Pong Domino-SAR ADC in 55-nm CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 999–1003. [Google Scholar] [CrossRef]

- Park, S.; Palaskas, Y.; Flynn, M.P. A 4GS/s 4b Flash ADC in 0.18/spl mu/m CMOS. In Proceedings of the 2006 IEEE International Solid State Circuits Conference-Digest of Technical Papers, San Francisco, CA, USA, 6–9 February 2006; pp. 2330–2339. [Google Scholar]

- Park, S.; Palaskas, Y.; Ravi, A.; Bishop, R.E.; Flynn, M.P. A 3.5 GS/s 5-b Flash ADC in 90 nm CMOS. In Proceedings of the IEEE Custom Integrated Circuits Conference 2006, San Jose, CA, USA, 10–13 September 2006; pp. 489–492. [Google Scholar]

- Deguchi, K.; Suwa, N.; Ito, M.; Kumamoto, T.; Miki, T. A 6-bit 3.5-GS/s 0.9-V 98-mW Flash ADC in 90-nm CMOS. IEEE J. Solid-State Circuits 2008, 43, 2303–2310. [Google Scholar] [CrossRef]

- El-Chammas, M.; Murmann, B. A 12-GS/s 81-mW 5-bit Time-Interleaved Flash ADC With Background Timing Skew Calibration. IEEE J. Solid-State Circuits 2011, 46, 838–847. [Google Scholar] [CrossRef]

- Dortz, N.L.; Blanc, J.; Simon, T.; Verhaeren, S.; Rouat, E.; Urard, P.; Tual, S.L.; Goguet, D.; Lelandais-Perrault, C.; Benabes, P. 22.5 A 1.62 GS/s time-interleaved SAR ADC with digital background mismatch calibration achieving interleaving spurs below 70dBFS. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 386–388. [Google Scholar]

- Lee, S.; Chandrakasan, A.P.; Lee, H. A 1 GS/s 10b 18.9 mW Time-Interleaved SAR ADC With Background Timing Skew Calibration. IEEE J. Solid-State Circuits 2014, 49, 2846–2856. [Google Scholar] [CrossRef]

- Kundu, S.; Alpman, E.; Lu, J.H.; Lakdawala, H.; Paramesh, J.; Jung, B.; Zur, S.; Gordon, E. A 1.2 V 2.64 GS/s 8 bit 39 mW Skew-Tolerant Time-interleaved SAR ADC in 40 nm Digital LP CMOS for 60 GHz WLAN. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 1929–1939. [Google Scholar] [CrossRef]

- Lin, C.; Wei, Y.; Lee, T. 27.7 A 10 b 2.6 GS/s time-interleaved SAR ADC with background timing-skew calibration. In Proceedings of the 2016 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016; pp. 468–469. [Google Scholar]

- Miki, T.; Ozeki, T.; Naka, J. A 2-GS/s 8-bit Time-Interleaved SAR ADC for Millimeter-Wave Pulsed Radar Baseband SoC. IEEE J. Solid-State Circuits 2017, 52, 2712–2720. [Google Scholar] [CrossRef]

- Song, J.; Ragab, K.; Tang, X.; Sun, N. A 10-b 800-MS/s Time-Interleaved SAR ADC With Fast Variance-Based Timing-Skew Calibration. IEEE J. Solid-State Circuits 2017, 52, 2563–2575. [Google Scholar] [CrossRef]

- Kang, H.; Hong, H.; Kim, W.; Ryu, S. A Time-Interleaved 12-b 270-MS/s SAR ADC With Virtual-Timing-Reference Timing-Skew Calibration Scheme. IEEE J. Solid-State Circuits 2018, 53, 2584–2594. [Google Scholar] [CrossRef]

- Liu, J.; Chan, C.; Sin, S.; Seng-Pan, U.; Martins, R.P. Accuracy-Enhanced Variance-Based Time-Skew Calibration Using SAR as Window Detector. IEEE Trans. Very Large Scale Integr. Syst. 2019, 27, 481–485. [Google Scholar] [CrossRef]

- Song, J.; Ragab, K.; Tang, X.; Sun, N. A 10-b 600-MS/s 2-Way Time-Interleaved SAR ADC With Mean Absolute Deviation-Based Background Timing-Skew Calibration. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 66, 2876–2887. [Google Scholar] [CrossRef]

- Kurosawa, N.; Kobayashi, H.; Maruyama, K.; Sugawara, H.; Kobayashi, K. Explicit analysis of channel mismatch effects in time-interleaved ADC systems. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 2001, 48, 261–271. [Google Scholar] [CrossRef]

- Razavi, B. Design Considerations for Interleaved ADCs. IEEE J. Solid-State Circuits 2013, 48, 1806–1817. [Google Scholar] [CrossRef] [Green Version]

- Stepanovic, D.; Nikolic, B. A 2.8 GS/s 44.6 mW Time-Interleaved ADC Achieving 50.9 dB SNDR and 3 dB Effective Resolution Bandwidth of 1.5 GHz in 65 nm CMOS. IEEE J. Solid-State Circuits 2013, 48, 971–982. [Google Scholar] [CrossRef]

- Wei, H.; Zhang, P.; Sahoo, B.D.; Razavi, B. An 8 Bit 4 GS/s 120 mW CMOS ADC. IEEE J. Solid-State Circuits 2014, 49, 1751–1761. [Google Scholar] [CrossRef]

- Sung, B.; Jo, D.; Jang, I.; Lee, D.; You, Y.; Lee, Y.; Park, H.; Ryu, S. 26.4 A 21fJ/conv-step 9 ENOB 1.6 GS/S 2× time-interleaved FATI SAR ADC with background offset and timing-skew calibration in 45 nm CMOS. In Proceedings of the 2015 IEEE International Solid-State Circuits Conference-(ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 22–26 February 2015; pp. 1–3. [Google Scholar]

- Wang, X.; Li, F.; Wang, Z. A novel autocorrelation-based timing mismatch C alibration strategy in Time-Interleaved ADCs. In Proceedings of the 2016 IEEE International Symposium on Circuits and Systems (ISCAS), Montreal, QC, Canada, 22–25 May 2016; pp. 1490–1493. [Google Scholar]

- Song, J.; Sun, N. A 10-b 600-MS/s 2-way time-interleaved SAR ADC with mean absolute deviation based background timing-skew calibration. In Proceedings of the 2018 IEEE Custom Integrated Circuits Conference (CICC), 8–11 April 2018; pp. 1–4. [Google Scholar]

- Hong, H.; Kim, W.; Kang, H.; Park, S.; Choi, M.; Park, H.; Ryu, S. A Decision-Error-Tolerant 45 nm CMOS 7b 1 GS/s Nonbinary 2b/Cycle SAR ADC. IEEE J. Solid-State Circuits 2015, 50, 543–555. [Google Scholar] [CrossRef]

- Cao, Z.; Yan, S.; Li, Y. A 32 mW 1.25 GS/s 6b 2b/Step SAR ADC in 0.13$\ \mu$m CMOS. IEEE J. Solid-State Circuits 2009, 44, 862–873. [Google Scholar] [CrossRef]

- Wei, H.; Chan, C.; Chio, U.; Sin, S.; Seng-Pan, U.; Martins, R.P.; Maloberti, F. An 8-b 400-MS/s 2-b-Per-Cycle SAR ADC With Resistive DAC. IEEE J. Solid-State Circuits 2012, 47, 2763–2772. [Google Scholar] [CrossRef] [Green Version]

- Sackinger, E.; Guggenbuhl, W. A versatile building block: The CMOS differential difference amplifier. IEEE J. Solid-State Circuits 1987, 22, 287–294. [Google Scholar] [CrossRef]

- Kuttner, F. A 1.2 V 10 b 20 MSample/s non-binary successive approximation ADC in 0.13/spl mu/m CMOS. In Proceedings of the 2002 IEEE International Solid-State Circuits Conference. Digest of Technical Papers (Cat. No.02CH37315), San Francisco, CA, USA, 7 February 2002; Volume 171, pp. 176–177. [Google Scholar]

- Razavi, B. The StrongARM Latch [A Circuit for All Seasons]. IEEE Solid-State Circuits Mag. 2015, 7, 12–17. [Google Scholar] [CrossRef]

- Harpe, P.; Cantatore, E.; Roermund, A.V. A 10b/12b 40 kS/s SAR ADC With Data-Driven Noise Reduction Achieving up to 10.1b ENOB at 2.2 fJ/Conversion-Step. IEEE J. Solid-State Circuits 2013, 48, 3011–3018. [Google Scholar] [CrossRef]

| This Work 1 | [20] | [22] 1 | [23] | |

|---|---|---|---|---|

| PVT sensitivity | robust | sensitive | robust | sensitive |

| Additional calibration | no | needed | no | needed |

| Area overhead | medium | low | high | low |

| Calibration method | MAD | variance | variance | MAD |

| Digital complexity | low | high | high | low |

| This Work 1 | [5] | [7] | [17] | [19] | |

|---|---|---|---|---|---|

| Architecture | TI SAR | TI SAR | TI Subranging | TI SAR | TI SAR |

| Technology (nm) | 65 | 45 | 65 | 40 | 40 |

| Supply voltage (V) | 1.2 | 1.1 | 1 | 1.2 | 1.1 |

| Sampling rate (GSPS) | 2.5 | 2.5 | 2.2 | 2.64 | 2 |

| Resolution (bit) | 7 | 7 | 7 | 8 | 8 |

| SFDR (dB) at Nyquist | 48.97 | 43 | 45.95 | - | 55 |

| SNDR (dB) at Nyquist | 40.79 | 34 | 37.96 | 38 | 39.4 |

| Power (mW) | 24 | 50 | 40 | 39 | 54.2 |

| FoMw 2 (fJ/conv.-step) | 108 | 480 | 280 | 230 | 355 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Seong, K.; Jung, D.-K.; Yoon, D.-H.; Han, J.-S.; Kim, J.-E.; Kim, T.T.-H.; Lee, W.; Baek, K.-H. Time-Interleaved SAR ADC with Background Timing-Skew Calibration for UWB Wireless Communication in IoT Systems. Sensors 2020, 20, 2430. https://doi.org/10.3390/s20082430

Seong K, Jung D-K, Yoon D-H, Han J-S, Kim J-E, Kim TT-H, Lee W, Baek K-H. Time-Interleaved SAR ADC with Background Timing-Skew Calibration for UWB Wireless Communication in IoT Systems. Sensors. 2020; 20(8):2430. https://doi.org/10.3390/s20082430

Chicago/Turabian StyleSeong, Kiho, Dong-Kyu Jung, Dong-Hyun Yoon, Jae-Soub Han, Ju-Eon Kim, Tony Tae-Hyoung Kim, Woojoo Lee, and Kwang-Hyun Baek. 2020. "Time-Interleaved SAR ADC with Background Timing-Skew Calibration for UWB Wireless Communication in IoT Systems" Sensors 20, no. 8: 2430. https://doi.org/10.3390/s20082430

APA StyleSeong, K., Jung, D.-K., Yoon, D.-H., Han, J.-S., Kim, J.-E., Kim, T. T.-H., Lee, W., & Baek, K.-H. (2020). Time-Interleaved SAR ADC with Background Timing-Skew Calibration for UWB Wireless Communication in IoT Systems. Sensors, 20(8), 2430. https://doi.org/10.3390/s20082430