FPGA Implementation of an Efficient FFT Processor for FMCW Radar Signal Processing

Abstract

:1. Introduction

2. FMCW Radar Algorithm

2.1. Measuring Range and Velocity in FMCW Radar

2.2. CFAR Algorithm

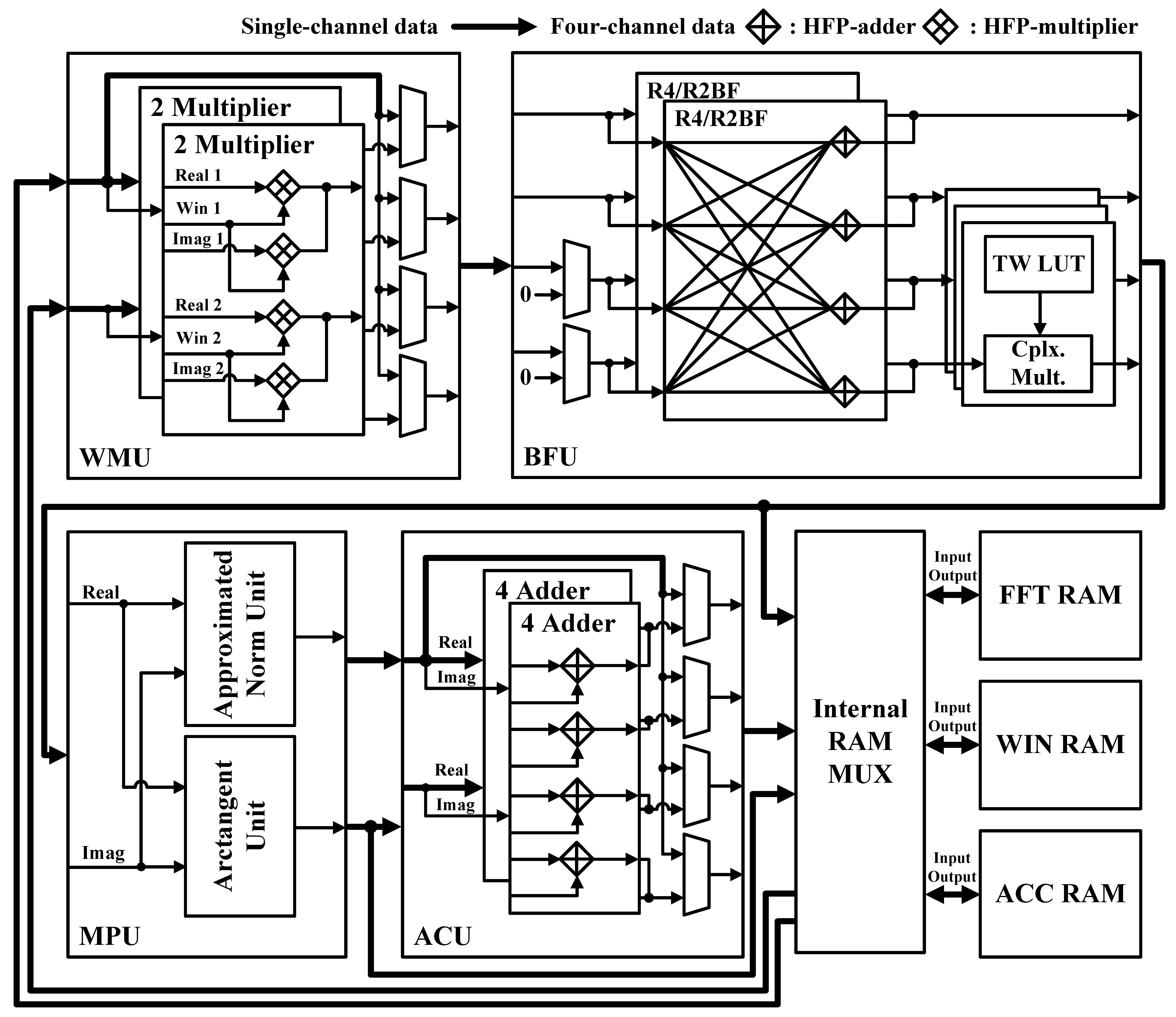

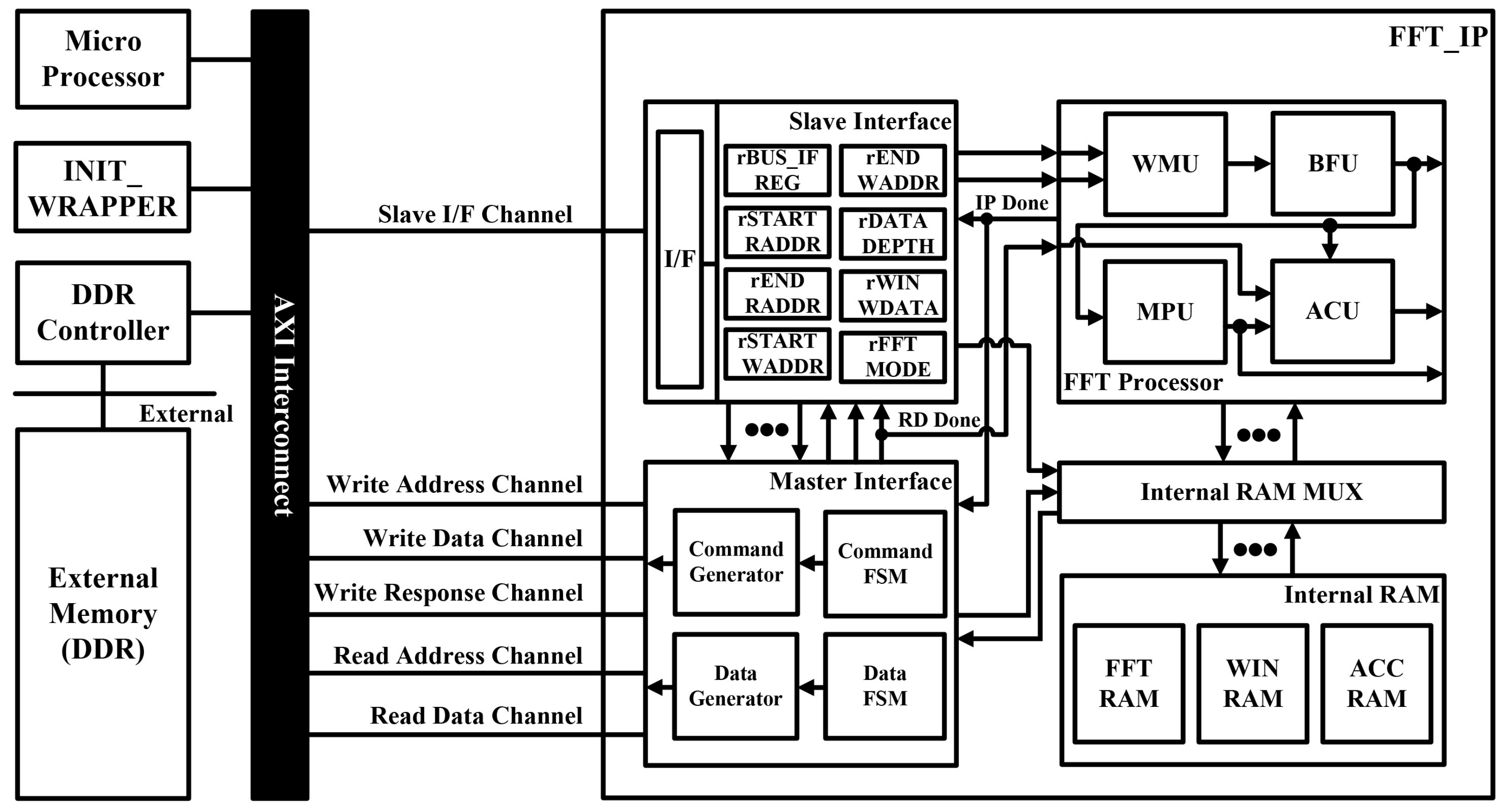

3. Hardware Architecture of the Proposed FFT Processor

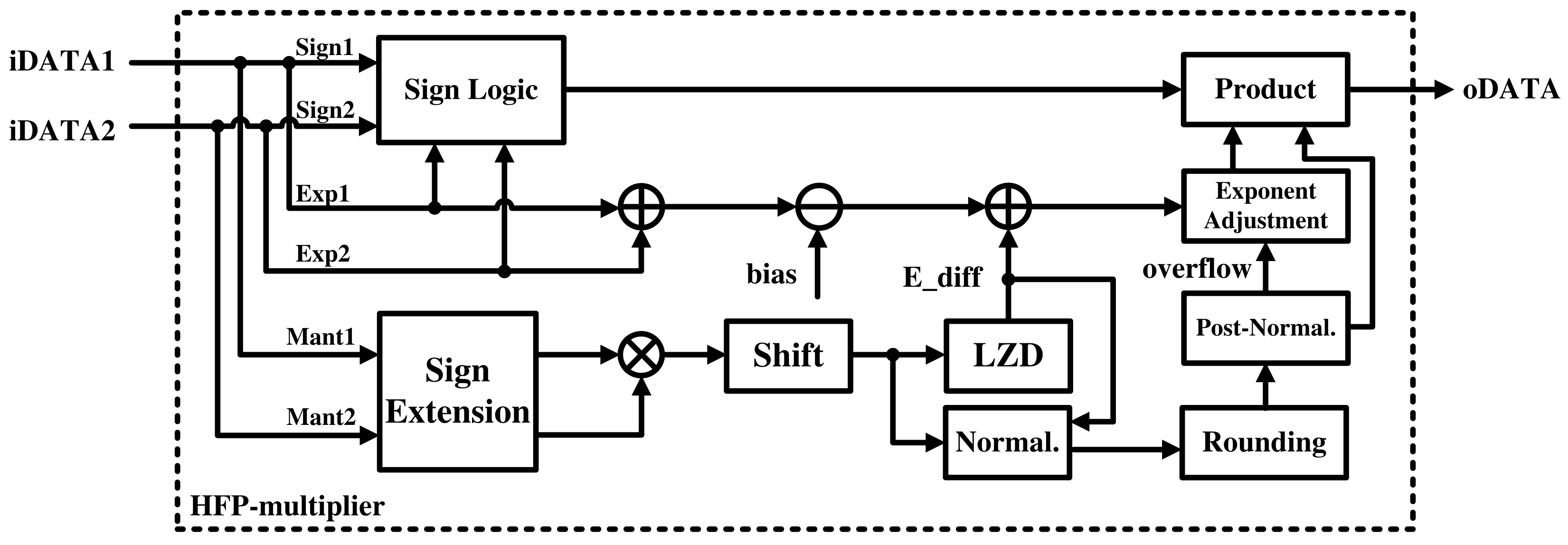

3.1. HFP Operation

3.2. Magnitude/Phase Calculation Unit

4. Implementation Results of the Proposed FFT Processor

5. Discussion and Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Cardillo, E.; Li, C.; Caddemi, A. Embedded heating, ventilation, and air-conditioning control systems: From traditional technologies toward radar advanced sensing. Rev. Sci. Instrum. 2021, 92, 061501. [Google Scholar] [CrossRef] [PubMed]

- Shao, Y.; Chen, P.; Cao, T. A grid projection method based on ultrasonic sensor for parking space detection. In Proceedings of the IGARSS 2018—2018 IEEE International Geoscience and Remote Sensing Symposium, Valencia, Spain, 22–27 July 2018; pp. 3378–3381. [Google Scholar]

- Son, Y.; Heo, S.W. A novel multi-target detection algorithm for automotive FMCW radar. In Proceedings of the 2018 International Conference on Electronics, Information, and Communication (ICEIC), Honolulu, HI, USA, 24–27 January 2018; pp. 1–3. [Google Scholar]

- Han, J.; Liao, Y.; Zhang, J.; Wang, S.; Li, S. Target fusion detection of LiDAR and camera based on the improved YOLO algorithm. Mathematics 2018, 6, 213. [Google Scholar] [CrossRef] [Green Version]

- Piotrowsky, L.; Jaeschke, T.; Kueppers, S.; Siska, J.; Pohl, N. Enabling high accuracy distance measurements with FMCW radar sensors. IEEE Trans. Microw. Theory Tech. 2019, 6, 5360–5371. [Google Scholar] [CrossRef]

- Park, J.; Park, S.; Kim, D.H.; Park, S.O. Leakage mitigation in heterodyne FMCW radar for small drone detection with stationary point concentration technique. IEEE Trans. Microw. Theory Tech. 2019, 67, 1221–1232. [Google Scholar] [CrossRef] [Green Version]

- Pérez, R.; Schubert, F.; Rasshofer, R.; Biebl, E. Single-frame vulnerable road users classification with a 77 GHz FMCW radar sensor and a convolutional neural network. In Proceedings of the 2018 19th International Radar Symposium (IRS), Bonn, Germany, 20–22 June 2018; pp. 1–10. [Google Scholar]

- Zhang, Z.; Tian, Z.; Zhou, M. Latern: Dynamic continuous hand gesture recognition using FMCW radar sensor. IEEE Sens. J. 2018, 18, 3278–3289. [Google Scholar] [CrossRef]

- Hyun, E.; Jin, Y.S.; Lee, J.H. Moving and stationary target detection scheme using coherent integration and subtraction for automotive FMCW radar systems. In Proceedings of the 2017 IEEE Radar Conference (RadarConf), Seattle, WA, USA, 8–12 May 2017; pp. 0476–0481. [Google Scholar]

- Kim, Y.; Ha, S.; Kwon, J. Human detection using Doppler radar based on physical characteristics of targets. IEEE Geosci. Remote Sens. Lett. 2014, 12, 289–293. [Google Scholar]

- Kim, J.C.; Jeong, H.G.; Lee, S. Simultaneous Target Classification and Moving Direction Estimation in Millimeter-Wave Radar System. Sensors 2021, 21, 5228. [Google Scholar] [CrossRef]

- Di Mattia, V.; Manfredi, G.; De Leo, A.; Russo, P.; Scalise, L.; Cerri, G.; Cardillo, E. A feasibility study of a compact radar system for autonomous walking of blind people. In Proceedings of the 2016 IEEE 2nd International Forum on Research and Technologies for Society and Industry Leveraging a Better Tomorrow (RTSI), Bologna, Italy, 7–9 September 2016; pp. 1–5. [Google Scholar]

- Hyun, E.; Jin, Y.S.; Lee, J.H. A pedestrian detection scheme using a coherent phase difference method based on 2D range-Doppler FMCW radar. Sensors 2016, 16, 124. [Google Scholar] [CrossRef] [Green Version]

- Ahmad, W.A.; Kucharski, M.; Ergintav, A.; Abouzaid, S.; Wessel, J.; Ng, H.J.; Kissinger, D. Multimode W-Band and D-Band MIMO Scalable Radar Platform. IEEE Trans. Microw. Theory Tech. 2020, 69, 1036–1047. [Google Scholar] [CrossRef]

- Swartzlander, E.E.; Saleh, H.H. FFT implementation with fused floating-point operations. IEEE Trans. Comput. 2010, 61, 284–288. [Google Scholar] [CrossRef]

- Chen, J.; Lei, Y.; Peng, Y.; He, T.; Deng, Z. Configurable floating-point FFT accelerator on FPGA based multiple-rotation CORDIC. Chin. J. Electron. 2016, 25, 1063–1070. [Google Scholar] [CrossRef]

- Chen, X.; Lei, Y.; Lu, Z.; Chen, S. A variable-size FFT hardware accelerator based on matrix transposition. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2018, 26, 1953–1966. [Google Scholar] [CrossRef]

- Li, Y.; Chen, H.; Xie, Y. An FPGA-Based Four-Channel 128k-Point FFT Processor Suitable for Spaceborne SAR. Electronics 2021, 10, 816. [Google Scholar] [CrossRef]

- Hou, J.; Zhu, Y.; Shen, Y.; Li, M.; Wu, Q.; Wu, H. Enhancing precision and bandwidth in cloud computing: Implementation of a novel floating-point format on fpga. In Proceedings of the 2017 IEEE 4th International Conference on Cyber Security and Cloud Computing (CSCloud), New York, NY, USA, 26–28 June 2017; pp. 310–315. [Google Scholar]

- Kronauge, M.; Rohling, H. Fast two-dimensional CFAR procedure. IEEE Trans. Aerosp. Electron. Syst. 2013, 49, 1817–1823. [Google Scholar] [CrossRef]

- Zhang, S.S.; Zeng, T.; Long, T.; Yuan, H.P. Dim target detection based on keystone transform. In Proceedings of the IEEE International Radar Conference, Arlington, VA, USA, 9–12 May 2005; pp. 889–894. [Google Scholar]

- Peng, W. Decision-making Optimization of Logistics Supply Chain Based on Small Target Echo Coherent Accumulation Algorithm Based on LTE Signal. Acoust. Speech Signal Process. 2019, 1, 1–6. [Google Scholar]

- Zheng, Q.; Yang, L.; Xie, Y.; Li, J.; Hu, T.; Zhu, J.; Xu, Z. A Target Detection Scheme with Decreased Complexity and Enhanced Performance for Range-Doppler FMCW Radar. IEEE Trans. Instrum. Meas. 2020, 70, 1–13. [Google Scholar] [CrossRef]

- Hyun, E.; Jin, Y.S.; Lee, J.H. Design and development of automotive blind spot detection radar system based on ROI pre-processing scheme. Int. J. Automot. Technol. 2017, 18, 165–177. [Google Scholar] [CrossRef]

- Alizadeh, M.; Shaker, G.; De Almeida, J.C.M.; Morita, P.P.; Safavi-Naeini, S. Remote monitoring of human vital signs using mm-Wave FMCW radar. IEEE Access 2019, 7, 54958–54968. [Google Scholar] [CrossRef]

- Wang, Y.; Wang, W.; Zhou, M.; Ren, A.; Tian, Z. Remote monitoring of human vital signs based on 77-GHz mm-wave FMCW radar. Sensors 2020, 20, 2999. [Google Scholar] [CrossRef]

- Garrido, M.; Qureshi, F.; Takala, J.; Gustafsson, O. Hardware architectures for the fast Fourier transform. In Handbook of Signal Processing Systems; Springer: Cham, Switzerland, 2019; pp. 613–647. [Google Scholar]

- Garrido, M.; Sánchez, M.Á.; López-Vallejo, M.L.; Grajal, J. A 4096-point radix-4 memory-based FFT using DSP slices. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2016, 25, 375–379. [Google Scholar] [CrossRef] [Green Version]

- Liu, S.; Liu, D. A high-flexible low-latency memory-based FFT processor for 4G, WLAN, and future 5G. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2018, 27, 511–523. [Google Scholar] [CrossRef]

- Hsiao, C.F.; Chen, Y.; Lee, C.Y. A generalized mixed-radix algorithm for memory-based FFT processors. IEEE Trans. Circuits Syst. II Express Briefs 2010, 57, 26–30. [Google Scholar] [CrossRef]

- Jung, Y.; Cho, J.; Lee, S.; Jung, Y. Area-efficient pipelined FFT processor for zero-padded signals. Electronics 2019, 8, 1397. [Google Scholar] [CrossRef] [Green Version]

- Jeon, H.; Jung, Y.; Lee, S.; Jung, Y. Area-Efficient Short-Time Fourier Transform Processor for Time–Frequency Analysis of Non-Stationary Signals. Appl. Sci. 2020, 10, 7208. [Google Scholar] [CrossRef]

- Hügler, P.; Geiger, M.; Waldschmidt, C. RCS measurements of a human hand for radar-based gesture recognition at E-band. In Proceedings of the 2016 German Microwave Conference (GeMiC), Bochum, Germany, 14–16 March 2016; pp. 259–262. [Google Scholar]

- Kärnfelt, C.; Péden, A.; Bazzi, A.; Shhadé, G.E.H.; Abbas, M.; Chonavel, T. 77 GHz ACC radar simulation platform. In Proceedings of the 2009 9th International Conference on Intelligent Transport Systems Telecommunications (ITST), Lille, France, 20–22 October 2009; pp. 209–214. [Google Scholar]

- Kahan, W. IEEE Standard 754 for Binary Floating-Point Arithmetic. Lect. Notes Status IEEE 1996, 754, 11. [Google Scholar]

- Adjoudani, A.; Beck, E.C.; Burg, A.P.; Djuknic, G.M.; Gvoth, T.G.; Haessig, D.; Wolniansky, P.W. Prototype experience for MIMO BLAST over third-generation wireless system. IEEE J. Sel. Areas Commun. 2003, 21, 440–451. [Google Scholar] [CrossRef]

- Muller, J.M. Discrete basis and computation of elementary functions. IEEE Trans. Comput. 1985, 34, 857–862. [Google Scholar] [CrossRef]

- Yu, J.Y.; Huang, D.; Li, X.; Xu, K.; Guo, L.M.; Gao, J.J. Four parallel channels radix-4 FFT with single floating-point butterfly. Appl. Mech. Mater. 2013, 427, 708–711. [Google Scholar] [CrossRef]

- Xilinx, Inc. Available online: https://www.xilinx.com/support/documentation/ip_documentation/xfft/v9_0/pg109-xfft.pdf (accessed on 24 August 2021).

- Gautam, V.; Ray, K.C.; Haddow, P. Hardware efficient design of variable length FFT processor. In Proceedings of the 14th IEEE International Symposium on Design and Diagnostics of Electronic Circuits and Systems, Cottbus, Germany, 13–15 April 2011; pp. 309–312. [Google Scholar]

- Wang, C.; Gan, W.S.; Jong, C.C.; Luo, J. A low-cost 256-point FFT processor for portable speech and audio applications. In Proceedings of the 2007 International Symposium on Integrated Circuits, Singapore, 26–28 September 2007; pp. 81–84. [Google Scholar]

| Format | 64 × 64 | 128 × 128 | 256 × 256 | 512 × 512 |

|---|---|---|---|---|

| Fixed-point (16 bits) | 34 | 26 | 22 | 14 |

| Fixed-point (20 bits) | 51 | 50 | 45 | 38 |

| Fixed-point (24 bits) | 52 | 51 | 51 | 50 |

| Fixed-point (28 bits) | 52 | 51 | 51 | 51 |

| HFP (16 bits) | 59 | 57 | 57 | 55 |

| Format | 1024 × 1024 | 2048 × 2048 | 4096 × 4096 | |

| Fixed-point (16 bits) | 10 | 2 | 0 | |

| Fixed-point (20 bits) | 34 | 26 | 22 | |

| Fixed-point (24 bits) | 45 | 41 | 35 | |

| Fixed-point (28 bits) | 51 | 50 | 50 | |

| HFP (16 bits) | 54 | 53 | 52 |

| Resource | Fixed-Point | HFP |

|---|---|---|

| Device | Zynq UltraScale+ | Zynq UltraScale+ |

| Bit width | 28 | 16 |

| Radix | 2, 4 | 2, 4 |

| LUT | 9846 | 10,891 |

| FF | 7377 | 6365 |

| BRAM | 20 | 10 |

| DSP | 76 | 20 |

| Block | LUT | FF | DSP |

|---|---|---|---|

| WMU | 637 | 393 | 8 |

| BFU | 6430 | 3570 | 12 |

| MPU | 2868 | 1811 | 0 |

| ACU | 956 | 591 | 0 |

| Total | 10,891 | 6365 | 0 |

| Data Size | Execution Time (ms) | ||

|---|---|---|---|

| Full SW | FFT Accel. | WMU/FFT/MPU/ACU (Full) Accel. | |

| 64 × 64 | 4.40 | 1.89 | 0.61 |

| 128 × 128 | 20.10 | 6.39 | 1.20 |

| 256 × 256 | 90.14 | 23.89 | 3.00 |

| 512 × 512 | 399.59 | 94.89 | 11.16 |

| 1024 × 1024 | 1761.42 | 373.39 | 38.22 |

| 2048 × 2048 | 7706.01 | 1331.16 | 168.06 |

| 4096 × 4096 | 32,973.46 | 4537.62 | 618.78 |

| [38] | [39] | Proposed | ||

|---|---|---|---|---|

| BFU | FFT | |||

| FPGA | Virtex-4 | Zynq UltraScale+ | Zynq UltraScale+ | Zynq UltraScale+ |

| Architecture | Memory-based | Memory-based | Memory-based | Memory-based |

| Transform length | 1024 | 4096 | 64–4096 | 64–4096 |

| Radix | 4 | 4 | 2, 4 | 2, 4 |

| Format | Floating-point | Floating-point | Floating-point | Floating-point |

| Windowing | - | - | - | O |

| Mag/Phase | - | - | - | O |

| Accumulation | - | - | - | O |

| LUT | 24,472 | 6237 | 6430 | 10,891 |

| FF | 13,834 | 3756 | 3570 | 6365 |

| Clock freq. (MHz) | 100 | 300 | 300 | 300 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Heo, J.; Jung, Y.; Lee, S.; Jung, Y. FPGA Implementation of an Efficient FFT Processor for FMCW Radar Signal Processing. Sensors 2021, 21, 6443. https://doi.org/10.3390/s21196443

Heo J, Jung Y, Lee S, Jung Y. FPGA Implementation of an Efficient FFT Processor for FMCW Radar Signal Processing. Sensors. 2021; 21(19):6443. https://doi.org/10.3390/s21196443

Chicago/Turabian StyleHeo, Jinmoo, Yongchul Jung, Seongjoo Lee, and Yunho Jung. 2021. "FPGA Implementation of an Efficient FFT Processor for FMCW Radar Signal Processing" Sensors 21, no. 19: 6443. https://doi.org/10.3390/s21196443

APA StyleHeo, J., Jung, Y., Lee, S., & Jung, Y. (2021). FPGA Implementation of an Efficient FFT Processor for FMCW Radar Signal Processing. Sensors, 21(19), 6443. https://doi.org/10.3390/s21196443