A Low-Power Opamp-Less Second-Order Delta-Sigma Modulator for Bioelectrical Signals in 0.18 µm CMOS

Abstract

:1. Introduction

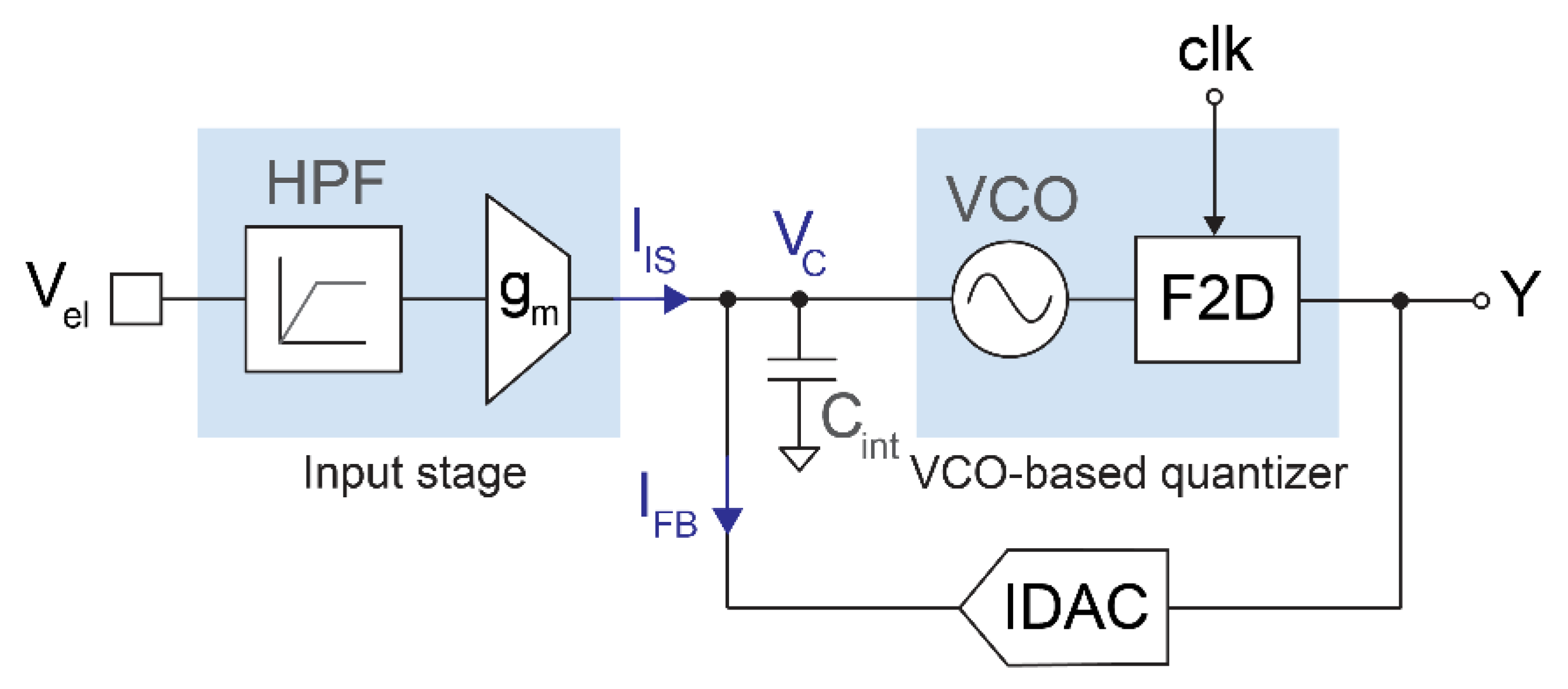

2. Readout Design

2.1. Input Stage

2.2. Feedback IDAC

2.3. Integrator

2.4. VCO-Based Quantizer

3. Electrical Characterization

4. In Vitro Validation

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Hierlemann, A.; Frey, U.; Hafizovic, S.; Heer, F. Growing cells atop microelectronic chips: Interfacing electrogenic cells in vitro with CMOS-based microelectrode arrays. Proc. IEEE 2011, 99, 252–284. [Google Scholar] [CrossRef]

- Musk, E.; Neuralink. An integrated brain-machine interface platform with thousands of channels. J. Med. Internet Res. 2019, 21, 1–14. [Google Scholar] [CrossRef]

- Dragas, J.; Viswam, V.; Shadmani, A.; Chen, Y.; Bounik, R.; Stettler, A.; Radivojevic, M.; Geissler, S.; Obien, M.E.J.; Müller, J.; et al. In Vitro Multi-Functional Microelectrode Array Featuring 59760 Electrodes, 2048 Electrophysiology Channels, Stimulation, Impedance Measurement, and Neurotransmitter Detection Channels. IEEE J. Solid-State Circuits 2017, 52, 1576–1590. [Google Scholar] [CrossRef] [Green Version]

- Kollo, M.; Racz, R.; Hanna, M.E.; Obaid, A.; Angle, M.R.; Wray, W.; Kong, Y.; Müller, J.; Hierlemann, A.; Melosh, N.A.; et al. CHIME: CMOS-Hosted in vivo Microelectrodes for Massively Scalable Neuronal Recordings. Front. Neurosci. 2020, 14, 834. [Google Scholar] [CrossRef]

- Park, S.Y.; Cho, J.; Na, K.; Yoon, E. Modular 128-Channel Δ—ΔΣ Analog Front-End Architecture Using Spectrum Equalization Scheme for 1024-Channel 3-D Neural Recording Microsystems. IEEE J. Solid-State Circuits 2018, 53, 501–514. [Google Scholar] [CrossRef]

- Najafi, K.; Wise, K.D. An Implantable Multielectrode Array with On-Chip Signal Processing. IEEE J. Solid-State Circuits 1986, 21, 1035–1044. [Google Scholar] [CrossRef]

- Mora Lopez, C.; Putzeys, J.; Raducanu, B.C.; Ballini, M.; Wang, S.; Andrei, A.; Rochus, V.; Vandebriel, R.; Severi, S.; Van Hoof, C.; et al. A Neural Probe with Up to 966 Electrodes and Up to 384 Configurable Channels in 0.13 μm SOI CMOS. IEEE Trans. Biomed. Circuits Syst. 2017, 11, 510–522. [Google Scholar] [CrossRef] [Green Version]

- Rey, H.G.; Pedreira, C.; Quian Quiroga, R. Past, present and future of spike sorting techniques. Brain Res. Bull. 2015, 119, 106–117. [Google Scholar] [CrossRef] [Green Version]

- Kato, Y.; Matoba, Y.; Honda, K.; Ogawa, K.; Shimizu, K.; Maehara, M.; Fujiwara, A.; Odawara, A.; Yamane, C.; Kimizuka, N.; et al. High-Density and Large-Scale MEA System Featuring 236, 880 Electrodes at 11.72 μm Pitch for Neuronal Network Analysis. In Proceedings of the 2020 IEEE Symposium on VLSI Circuits, Honolulu, HI, USA, 16–19 June 2020; Volume 1, pp. 31–32. [Google Scholar] [CrossRef]

- Chang, S., II; Park, S.Y.; Yoon, E. Minimally-invasive neural interface for distributed wireless electrocorticogram recording systems. Sensors 2018, 18, 263. [Google Scholar] [CrossRef] [Green Version]

- Lopez, C.M.; Chun, H.S.; Wang, S.; Berti, L.; Putzeys, J.; Van Den Bulcke, C.; Weijers, J.W.; Firrincieli, A.; Reumers, V.; Braeken, D.; et al. A multimodal CMOS MEA for high-throughput intracellular action potential measurements and impedance spectroscopy in drug-screening applications. IEEE J. Solid-State Circuits 2018, 53, 3076–3086. [Google Scholar] [CrossRef]

- Yuan, X.; Hierlemann, A.; Frey, U. Extracellular Recording of Entire Neural Networks Using a Dual-Mode Microelectrode Array with 19 584 Electrodes and High SNR. IEEE J. Solid-State Circuits 2021, 56, 2466–2475. [Google Scholar] [CrossRef] [PubMed]

- Leene, L.B.; Constandinou, T.G. A 0.006 mm2 1.2 μ W Analog-to-Time Converter for Asynchronous Bio-Sensors. IEEE J. Solid-State Circuits 2018, 53, 2604–2613. [Google Scholar] [CrossRef]

- Ballini, M.; Muller, J.; Livi, P.; Chen, Y.; Frey, U.; Stettler, A.; Shadmani, A.; Viswam, V.; Lloyd Jones, I.; Jackel, D.; et al. A 1024-Channel CMOS Microelectrode Array with 26,400 Electrodes for Recording and Stimulation of Electrogenic Cells In Vitro. IEEE J. Solid-State Circuits 2014, 49, 2705–2719. [Google Scholar] [CrossRef] [Green Version]

- Lee, C.; Jeon, T.; Jang, M.; Park, S.; Kim, J.; Lim, J.; Ahn, J.; Huh, Y.; Chae, Y. A 6.5-μW 10-kHz BW 80.4-dB SNDR Gm C-Based CT Modulator with a Feedback-Assisted Gm Linearization for Artifact-Tolerant. IEEE J. Solid-State Circuits 2020, 55, 2889–2901. [Google Scholar] [CrossRef]

- Pazhouhandeh, M.R.; Kassiri, H.; Shoukry, A.; Weisspapir, I.; Carlen, P.L.; Genov, R. Opamp-Less Sub-μW/Channel Delta-Modulated Neural-ADC with Super-G Input Impedance. IEEE J. Solid-State Circuits 2021, 56, 1565–1575. [Google Scholar] [CrossRef]

- Wendler, D.; De Dorigo, D.; Amayreh, M.; Bleitner, A.; Marx, M.; Manoli, Y. A 0.00378 mm2 Scalable Neural Recording Front-End for Fully Immersible Neural Probes Based on a Two-Step Incremental Delta-Sigma Converter with Extended Counting and Hardware Reuse. In Proceedings of the 2021 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 13–22 February 2021; Volume 64, pp. 398–400. [Google Scholar] [CrossRef]

- Schreier, R.; Temes, G.C. Understanding Delta-Sigma Data Converters; Wiley-IEEE Press: Hoboken, NJ, USA, 2005; ISBN 9780471465850. [Google Scholar]

- Park, M.; Perrott, M.H. A 78 dB SNDR 87 mW 20 MHz Bandwidth Continuous-Time DS ADC with VCO-Based Integrator and Quantizer Implemented in 0.13 μm CMOS. IEEE J. Solid-State Circuits 2009, 44, 3344–3358. [Google Scholar] [CrossRef]

- Straayer, M.Z.; Perrott, M.H. A 12-Bit, 10-MHz Bandwidth, Continuous-Time SD ADC with a 5-Bit, 950-MS/s VCO-Based Quantizer. IEEE J. Solid-State Circuits 2008, 43, 805–814. [Google Scholar] [CrossRef]

- Kim, J.; Jang, T.K.; Yoon, Y.G.; Cho, S.H. Analysis and design of voltage-controlled oscillator based analog-to-digital converter. IEEE Trans. Circuits Syst. I Regul. Pap. 2010, 57, 18–30. [Google Scholar] [CrossRef]

- Ardalan, S.H.; Paulos, J.J. An Analysis of Nonlinear Behavior in Delta-Sigma Modulators. IEEE Trans. Cir. Syst. 1987, 34, 593–603. [Google Scholar] [CrossRef]

- Gutierrez, E.; Hernandez, L.; Cardes, F.; Rombouts, P. A Pulse Frequency Modulation Interpretation of VCOs Enabling VCO-ADC Architectures with Extended Noise Shaping. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 444–457. [Google Scholar] [CrossRef]

- Cardes, F.; Quintero, A.; Gutierrez, E.; Buffa, C.; Wiesbauer, A.; Hernandez, L. SNDR limits of oscillator-based sensor readout circuits. Sensors 2018, 18, 445. [Google Scholar] [CrossRef] [PubMed] [Green Version]

| [3] | [13] | [10] | [5] | [11] | [9] | [15] | [16] | [17] | [12] | This Work | ||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| C0 = 4.25 pF | C0 = 350 fF | |||||||||||

| Year | 2017 | 2018 | 2018 | 2018 | 2018 | 2020 | 2020 | 2021 | 2021 | 2021 | 2021 | |

| Architecture | SAR | ATC | SAR | ∆-∆Σ | SAR | SS | ∆Σ (VCO-Q) | ∆Σ | I∆Σ | SAR | ∆Σ(VCO-Q) | |

| Technology (nm) | 180 | 65 | 250 | 180 | 130 | 90/65 | 110 | 130 | 180 | 180 | 180 | |

| Sampling frequency (Hz) | 20 k | -e | 31.25 k | 25 k | 30 k | 70 k | 1.28 M | 10 M | 20 k | 11.6 k | 1M | |

| Bandwidth (Hz) | 300–10 k | 11 k | 10–10 k | 0.5–12.7 k | 300–10 k | 300–10 k | 10 k | 1–500 | 300–10 k | 300–5 k | 1–10 k | 300–6 k |

| Area/channel (mm2/ch) | 0.024 a | 0.006 | 0.155 | 0.058 c | 0.043 a | 0.014 a | 0.078 | 0.011 c | 0.0046 c | 0.001 a | 0.006 b | 0.0045b |

| Power/channel (μW/ch) | 16 | 1.2 | 2.5 | 3.05 | 46 | 130 | 6.5 | 0.99 c | 8.59 c | 5.9 | 3.5b | |

| Input-referred noise (μVrms) | 2.4 | 3.8 | 5.62 | 3.32 | 7.5 | 5.5 | 9.5 | 2.6 | 4.37 | 10.4 | 8.7 | 5.0 |

| Input range (mVpp) | - | 4 | - | - | - | - | 300 | 10 d | 14 | 8 | 6 | |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cardes, F.; Baladari, N.; Lee, J.; Hierlemann, A. A Low-Power Opamp-Less Second-Order Delta-Sigma Modulator for Bioelectrical Signals in 0.18 µm CMOS. Sensors 2021, 21, 6456. https://doi.org/10.3390/s21196456

Cardes F, Baladari N, Lee J, Hierlemann A. A Low-Power Opamp-Less Second-Order Delta-Sigma Modulator for Bioelectrical Signals in 0.18 µm CMOS. Sensors. 2021; 21(19):6456. https://doi.org/10.3390/s21196456

Chicago/Turabian StyleCardes, Fernando, Nikhita Baladari, Jihyun Lee, and Andreas Hierlemann. 2021. "A Low-Power Opamp-Less Second-Order Delta-Sigma Modulator for Bioelectrical Signals in 0.18 µm CMOS" Sensors 21, no. 19: 6456. https://doi.org/10.3390/s21196456

APA StyleCardes, F., Baladari, N., Lee, J., & Hierlemann, A. (2021). A Low-Power Opamp-Less Second-Order Delta-Sigma Modulator for Bioelectrical Signals in 0.18 µm CMOS. Sensors, 21(19), 6456. https://doi.org/10.3390/s21196456