1. Introduction

Currently, we have high-capacity technology of analog and digital electronic devices due to the micro-components that are increasingly becoming smaller in scale. In fact, in 1965, Gordon E. Moore predicted (Moore’s law) that every 2 years the number of transistors in a microprocessor would double. This law worked for the first 10 years [

1]; then it became a joke between engineers who said that “now people predict that the end of Moore’s law doubles every 2 years.” Since then, transistor integration has been observed as illustrated in

Figure 1, where Moore’s law was in force for a long time. However, the limits towards a scale in nanotechnology have shown that although Moore’s law no longer applies, significant efforts are still being made to continue reducing the size of the micro and nano components. For example, recently design and process in semiconductors have been done with the development of the world’s first chip with 2 nanometers (nm) nanosheet technology [

2].

Therefore, with this context in which the microchip technology is reducing in size over time, college students with different science and engineering majors need to understand the “know-how” of designing circuits that integrate microchips. Unfortunately, often this knowledge is taught with specialized complex (and expensive) software, which is sometimes not readily available in many universities around the world.

Analog and digital integrated circuit design has emphasized a good understanding of analog and digital electronic circuits to model, simplify, analyze, and simulate microelectronic devices before developing layouts and sending devices to IC fabrication foundry consortiums. Design engineers find SPICE simulations useful to validate “thinking models” [

3,

4] to verify cause–effect relationships and to ensure that assumptions made are appropriate in the design process. Microelectronics courses and specialized workshops (and webinars) teach conceptual design where the following concepts are emphasized.

The importance of the integrated circuit (IC) design in microelectronics engineering is embedded into electronic engineering innovation and design flow.

Analog CMOS microelectronics focus on the electrical and physical design processes.

IC design is important in device development for microelectronics engineering innovation and is embedded into the design flow which may have continuous iterations to optimize designs by decision refinements. In the process of CMOS microelectronics conceptual design [

5,

6,

7], the electrical device specification requires active and passive models for creating, verifying, and determining the robustness of the design. This process involves the selection of a conceptual circuit, the analysis of the selected circuit, the possibility of a modification to the circuit, and the verification of the circuit solution. The physical electronics design process [

8,

9,

10] consists of representing the electrical device in a 2D layout consisting of many different geometrical rectangles at various levels (layers). This layout is then used to implement a 3D integrated circuit during the fabrication process. The device conceptual model follows a process to obtain a layout. This process includes [

3,

4]:

The W/L (width/length of transistors) values and schematic (usually from SPICE simulations).

A computer-aided tool (CAD) system is used to enter geometries.

The engineer must obey a set of rules called design rules. These rules establish the fabrication limitations and ensure that the device is robust and reliable.

Once the layout is complete, a process called layout versus schematic (LVS) is applied to determine if the physical layout represents the electrical schematic.

Parasitic elements are extracted, once the physical dimensions of the designs are known. They include capacitances from conductor to ground or between conductors and bulk resistances.

The parasitic elements are entered into the simulation database and the design is re-stimulated to ensure they will not cause a device failure.

This process is depicted in the flow diagram shown below in

Figure 2.

Once the first approach to design is terminated, the process continues with design testing which consists of coordinating, planning, and implementing the measurement of the integrated circuit performance. The objective is to compare the experimental performance with the specifications and/or simulation results. Several tests are available, e.g., functional: verification of the nominal specifications; parametric: verification of the characteristics to within a specified tolerance, verification of the static (AC and DC) characteristics of the circuit or system, and verification of the dynamic (transient) characteristics of a circuit or system. Additional testing could include device testing performed at the wafer level or package level and detailed testing that removes the influence of measurement system in the device performance.

The conceptual design of analog integrated circuits in new devices is now shaped by rules such as: consumers generate a need for new integrated circuits, design engineers have an open possibility of participating in designs, time to develop a product is reduced, profit in products and prototypes are not readily necessary, and the new concept of “crowd designing” [

3] plays an important role in device development. This article discusses Excel methods to perform “paper and pencil” calculations (“thinking model”) in the conceptual design of CMOS analog integrated circuits which are validated using ELECTRIC-LTSpice to provide the initial characteristics of the device. Several methodologies have been developed for CMOS device design and testing but most of them are very specific to the final prototype or experimental application [

11,

12,

13,

14,

15,

16,

17]. The Excel methods analyzed in this study focus on providing didactic instruction in microelectronics for undergraduate and graduate students. Therefore, it seeks to focus learning by referring to world trends in conducting open science, providing the social appropriation of knowledge. The forefront is didactic management whose central axis is the catalyst of open innovation processes that have proven to be very successful disruptive models in open laboratories, universities, research centers, industry, and government for the development of emerging economies and public policies [

18,

19,

20,

21,

22,

23,

24,

25,

26].

As a result, this study describes a method that uses an Excel spreadsheet to start the conceptual design from the point of view of the “thinking model” or the first cut evaluation of the design with “paper and pencil”. In addition, several contributions stand out:

The Excel methods discussed here focus on microelectronics education for undergraduate and graduate students. The article describes a simple method using an Excel spreadsheet to initiate conceptual design from the standpoint of “thinking model” or “paper and pencil” first cut evaluation of the design. Furthermore, several contributions are emphasized:

- (a)

This work describes both the conceptual design evaluations using the traditional equations and prepares the way for the layout implementation by setting up the schematic of the design.

- (b)

In addition, this study describes that once the schematic simulation agrees with the scheduled specifications and the “thinking model” provides a possible design solution, the layout is developed and a comparison between the output results with the thinking model specs validates the third phase of the process.

- (c)

Moreover, the methodology applied in this study can be developed for more complicated CMOS analog integrated circuits (IC) conceptual designs, specifically for teaching purposes.

- (d)

Complex conceptual designs can also be addressed using simple and readily available software (freeware) to teach with an open science view.

- (e)

Furthermore, this article illustrates an exhaustive example of a low voltage operational transconductance amplifier (OTA) design for portable biomedical applications. The test is performed using this instrumentation amplifier to implement a front-end signal conditioning device for CMOS-MEMS biomedical applications.

This manuscript is organized as follows.

Section 2 briefly describes device modeling to represent transistors using first principle equations that predict their behavior in different regimes and operating conditions.

Section 3 provides the basic MOSFET modeling equations, starting with the threshold voltage calculations, the transconductance equations for the ohmic (sub-saturation), active (saturation), and subthreshold conditions, both for long channel and short channel devices.

Section 3 also gives the typical MOSFET parameters for 0.5 mm CMOS technology, the small-signal model parameter equations, and useful resistance and capacitance calculations using the foundry process parameters for the technology.

Section 4 describes the Excel methods that students use to develop their first cut approximations in conceptual designs of CMOS devices and before testing schematic simulations and layouts. This section explains three Excel methodologies: single straight, tabular straight, and two-dimensional processing methods to perform the evaluation of the device’s conceptual design. This section also discusses resistance, capacitance, and differential amplifier conceptual designs as specific examples to apply the Excel methods.

Section 5 discusses the Excel methods applied for complete amplifier design. Here the cascode amplifier and the OTA (Operational Transconductance Amplifier) are used as examples of how students use the basic two-dimensional Excel methodology to solve CMOS microelectronic conceptual design devices.

Section 6 illustrates a complete case study, developed by students and wrapped up by their instructor, of a low-power high-gain operational amplifier for biomedical applications. In this section, comparison of the design is performed with respect to a particular device appearing in the technical literature and an application of a CMOS-MEMS signal conditioning is developed considering the requirement of conditioning a differential mode temperature sensor´s output to obtain a readily available low voltage representation of the temperature of a micro hotplate multisensor platform. Finally,

Section 7 wraps up the paper with illustrative conclusions about how these Excel methods have provided extraordinary insights to undergraduate students in their effort to consolidate a good understanding of microelectronics conceptual integrated circuit (IC) design.

2. Materials and Methods—Device Modeling

The process of device modeling consists of representing the electrical properties of devices using mathematical equations, circuits, graphs, correlations, and energy conservation laws. Models allow predictions and validation of circuit performance with uncertainties coming from no-idealities and non-linear behaviors in electronic components. Typical equations and conservation laws are Ohm´s law, large- and small-signal models of MOSFET transistors, VTC curves, and I-V curves of diodes. The final goals are to simplify the cause–effect relationships allowing the engineer to understand and consider decisions that increase performance in the circuit.

Analog integrated circuits in microelectronic conceptual design are developed using a non-hierarchical structure where the use of repeated blocks is only possible in few devices, and therefore the design process is complex and challenging. To handle this, design engineers use hierarchy whenever possible, use good organization techniques, efficiently document the design, provide reasonable and reliable assumptions and simplifications, and eventually validate the conceptual designs using simulation experiments. Assumptions and simplifications are used to emphasize the essential characteristics by neglecting the non-dominant effects in the design. The challenge of teaching microelectronics is to develop an insight into the design process without requiring specialized professional software which is not readily available in many universities around the world.

Figure 3 shows the microelectronics design process, on the left side, with the insight given on the right side, using Excel methods and other simulation techniques which are readily available to universities.

Analog integrated circuit design and device evaluation have reached a level of maturity in established applications such as digital to analog and analog to digital conversion systems, front end signal conditioning devices, instrumentation channel devices, bandgap reference sources, DC to DC power conversion drives, and other important microelectronic circuits [

3]. Finally, analog circuit conceptual designs have significant applications in devices where speed and power have an overwhelming advantage over digital devices. This paper reviews the long and short channel models for CMOS devices and further application of long channel equations using Excel methods for first cut approximations before computer simulations and layout development. Those approximation models can be found in many CMOS microelectronics specialized textbooks [

3,

4,

7,

27,

28,

29] and they are summarized here for completeness in this discussion.

6. Analysis of Results

To further increase the potential of using Excel methods in developing instrumentation amplifiers for biomedical applications, we examined a project case study using the methodology to design a 3-stage amplifier having a low voltage and low power operation in the strong inversion zone. Undergraduate students during the spring semester of 2021 in the microelectronics course at Tecnológico de Monterrey developed a project where they used the methods learned in class [

34]. This design was going to be used as a subsystem of a bioinstrumentation amplifier required in sensor signal conditioning applications.

The project consisted of the development of a three-element instrumentation amplifier for biomedical applications.

Figure 22 illustrates the basic scheme where two op-amps receive the differential mode input signals, and a third op-amp changes the signal from differential mode to single-ended mode referenced to ground.

In

Figure 22, each op-amp (OA1, OA2, and OA3) must be selected from possible topologies seen in class to achieve certain performance characteristics. Those op-amps have the following components:

First stage differential amplifier;

Second stage common source amplifier;

Third stage push-pull output stage;

Power source to provide the required bias currents and voltages.

Figure 23 shows a block diagram of each op-amp with all the functional parts of the system. For the power source, the students have the option of developing a high-performance bandgap reference source that is stable with respect to variations in supply voltage, temperature, and noise.

The requirements and specifications provided in

Table 9 are to be met for each of the op-amp blocks.

The students began with a literature survey before selecting the device to develop from the conceptual requirements, theoretical development, schematic development, and layout implementation using Electric_VLSI [

35,

36,

37,

38]. Instead of adding a third stage at the output of the two-stage OTA device, they added a second stage differential-amplifier with compensation between the first differential stage and the output stage. This results in improving the frequency response and sacrificing some gain and having a better phase margin for even robust design. Even with this modification, the simulations show an increase in the overall gain compared to the last three stage designs (

Section 5). The compensation capacitor

Cc and

Rz are kept for both differential stages, and the output terminals of both compensation elements are connected all the way to the output of the circuit. The methodology generates the transistor dimensions and capacitor values illustrated in

Table 10 and

Table 11.

Considering the transistor dimensions for this new three stage amplifier design, the first cut expected parameters are calculated as follows, assuming long channel models.

- 2.

Estimated amplifier gain.

- 3.

Power dissipation.

- 4.

Output swing.

- 5.

Input common mode range, ICMR.

- 6.

Output resistance.

Afterward, the circuit schematic and layout are developed in Electric VLSI to perform simulations tests. The compensation capacitor is designed as a poly-poly2 capacitor. The area for the capacitor is 78 by 78 lambda, with a 47 fF parasitic capacitance.

Figure 24 shows the Excel first cut approximation used for the first part of the conceptual design.

The Excel design spreadsheet shown in

Figure 24 replicates the strategy which has been proposed in this article. The CMOS technology characteristics and specifications flow horizontally to the right and the CMOS design equations, from (5) to (10),

Table 1 and

Table 2, flow downwards illustrating the step-by-by step procedure.

Figure 25 and

Figure 26 illustrate the schematic and layout diagrams for the three-stage amplifier designed using the methodology shown and initiating with the conceptual design equations coming from the long channel model.

The output simulation runs show results that comply with the major specifications required by the design.

Figure 27 illustrates the layout frequency sweep where the dB gain, gain bandwidth, and the phase margin are displayed. The DC gain obtained is 91.7 dB, the gain bandwidth GB is 46 MH and the phase margin is now close to 94°, which makes a very robust device.

Figure 28 shows the time domain simulation to verify the slew rate response. The graph shows

and

which is much more than the required response.

To summarize the complete results for all the theoretical and expected parameters,

Table 12 compares:

Desired requirements for the conceptual design;

Theoretical calculations using the Excel method;

Simulation results of the schematic circuit;

Simulation results of the layout circuit.

The results compare well to the specified requirements except for the maximum positive swing of the output signal which does not reach the specified value of 1.4 V. Furthermore, the power dissipation is slightly higher than anticipated by the theoretical calculations of 0.403 mW. However, very good results are obtained in gain bandwidth (GB), CMRR, PSRR, phase margin PM, and noise. The requirements for slew rate (SR) and DC gain () are barely achieved. Some of those specifications could have been obtained with additional calibration and refinements in the final conceptual design.

The student team [

34] decided to compare the conceptual design of this low-power operational amplifier with one that appears in the literature with similar characteristics and is used in similar biomedical applications [

35].

Table 13 shows this comparison where the supply voltage and the power consumption appear higher in our design. The load capacitance was a specification given by the instructor. Slew rate and bandwidth show a significantly higher performance in our design; however, those were parameters also required by the instructor. The chip area is twice in our design, however, in this case, the instructor did not have any restrictions here and no optimization was performed to reduce the layout artwork whatsoever.

Table 13 results, however, illustrate comparisons under different specifications such as the load capacitance and voltage supply. Reference [

35] used

and

, whereas our example used

and

, respectively. Some of those conditions were imposed by the course instructor. These changes produced large differences in closed-loop bandwidth and slew rate (SR) as seen by

Table 11 results. Furthermore, the power dissipation and chip area obtained here are twice the values obtained by reference [

35]. Another way to reduce the power dissipation and voltage supply could have been if they have designed the amplifier to operate in the subthreshold zone. However, the model equations in the Excel method would need to be changed to include the subthreshold model whatsoever. This comparison is an excellent way to encourage confidence in students about the design of integrated circuits at the nanoscale level [

36].

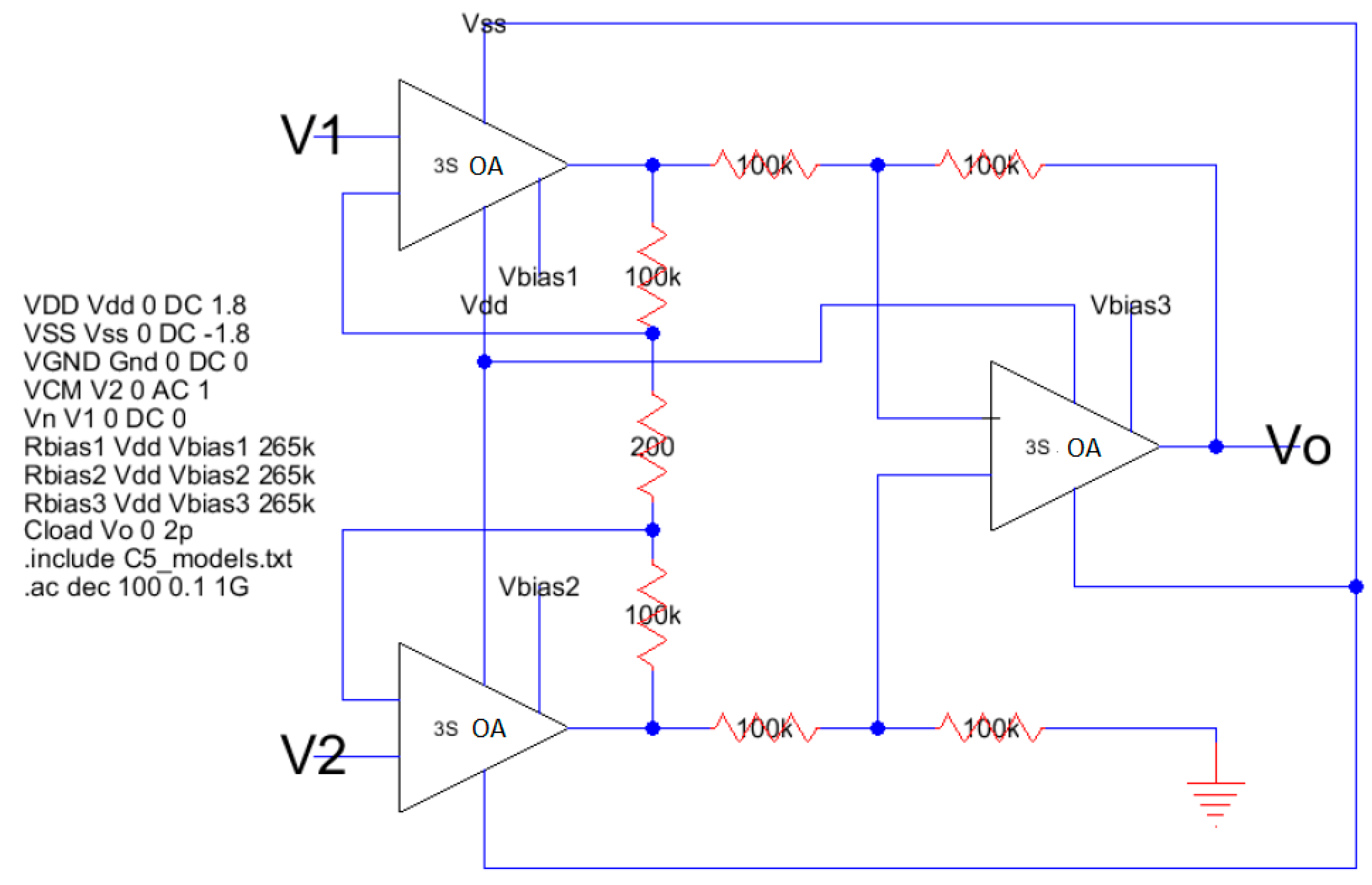

A system simulation test was performed by students with an instrumentation amplifier working with a gain of 60 dB or 1000

v/v using the traditional three op-amp topology.

Figure 29 shows the Icon-View of the simulation experiment having three op-amps (3S_OA) and the required resistors to provide the gain factor and the bias of the device. The figure shows on the left-hand side the SPICE code to run the frequency domain test (.ac dec 100 0.1 1 G). Furthermore, the MOSFET models command < include C5_models.txt> describes the 500 nm technology used in this case.

The frequency-domain tests show a DC gain very close to the required for this instrumentation amplifier.

Figure 30 shows the output voltage graph with a measured gain of 59.7 dB, approximately 966 V/V, which shows less than 5 % error with respect to the required 1000 V/V gain. This gain goes along to up to 10 KH in bandwidth.

Finally, a time-domain system test for the instrumentation amplifier was developed to find the maximum output symmetrical swing for the device when amplifying the biomedical sensor signal. This transient test was performed with a 1.8 mV amplitude at 1000 H differential mode signal (V2-V1) at the input.

Figure 31 shows the output signal with a+1.7323 V to −1.735 V swing which also shows the gain of 966

v/v for the instrumentation amplifier configuration.

The designed operational amplifier and the instrumentational amplifier have good features for biomedical portable sensor conditioning applications. ECG and EEG biopotentials can be processed, and a good front device can be implemented using the conceptual design generated using these methods. The design of micro-power-operational amplifiers to fulfill biomedical instrumentation characteristics has become a huge yet complicated research task with great opportunity areas for improvement and innovation. The design proposed by the students offers further improvement opportunities (like reducing output resistance) yet possesses interesting features that would hopefully serve for its application in sensor signal conditioning in biomedical instrumentation.

Another application of the low power operational amplifier is to perform signal conditioning in signals coming from CMOS-MEMS sensors [

39,

40,

41,

42] where the CMOS amplifiers are used as the standard electronic system maneuvering platform. For instance, in [

42] the low power operational amplifier is used as a high input impedance instrumentation amplifier to condition signals coming from a micro-hotplate in either Pirani, Temperature, or Gas CMOS-compatible MEMS sensors. Three operational amplifiers, designed in this paper, are set up as instrumentation amplifiers like the one shown in

Figure 29. This configuration is ideal for this multifunctional sensor platform application, particularly for the results obtained by the temperature sensor as shown in

Figure 32.

Figure 33 shows the new instrumentation amplifier configuration used to condition the signal coming from the multiplatform temperature sensor [

42] to obtain the results shown in

Table 14.

Figure 34 illustrates the linear conditioning performed by the instrumentation amplifier designed using the low power OTA developed by the students.

The results obtained in this CMOS-MEMS sensor application confirm the possibility of using the EXCEL methods to perform first cut front end device design and testing. In teaching microelectronics, sometimes the use of high-performance software tools deviates attention toward the final objective and competence development for electronics engineers. The analysis of results from the previous two examples shows that the use of EXCEL methods provides a fertile background to start conceptual design processes without requiring complex or expensive software which is not readily available in many universities around the globe. Finally, to account for parasitic capacitances and temperature effects over the operating point of the amplifiers,

Appendix A provides additional equations that can be added to the Excel method to find those fluctuations when using Spice simulations of the device.

Appendix A.1 shows the parasitic capacitance modeling and

Appendix A.2 illustrates the temperature model of this technology.