Evidence of Negative Capacitance and Capacitance Modulation by Light and Mechanical Stimuli in Pt/ZnO/Pt Schottky Junctions

Abstract

:1. Introduction

2. Materials and Methods

2.1. ZnO Thin Films and Pt Metal Electrodes Deposition

2.2. Structural and Electrical Characterization of ZnO Thin Films

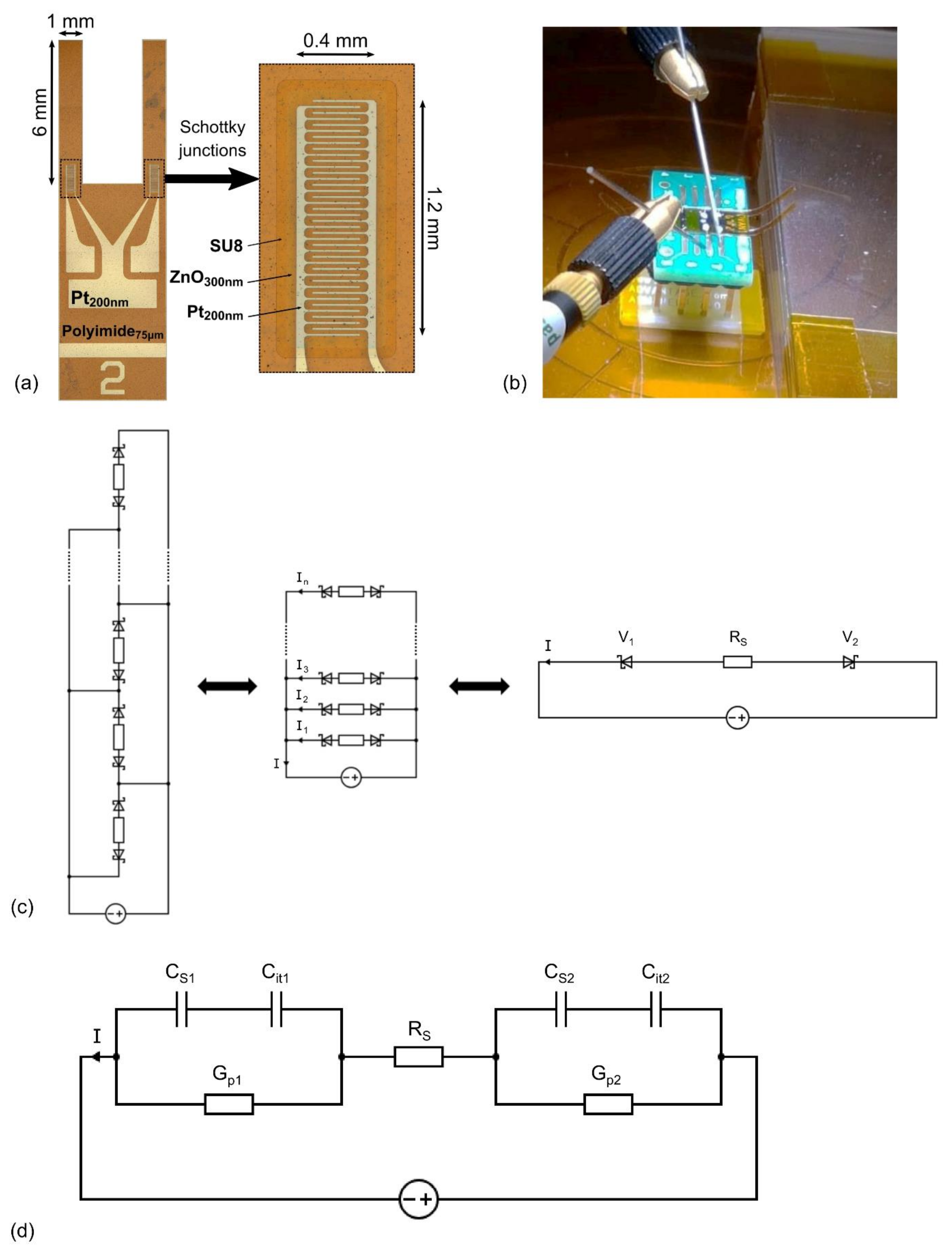

2.3. Strain Sensor and Equivalent Circuit Model

2.4. Electrical Characterization of the Pt/ZnO/Pt Schottky Junctions

3. Results and Discussion

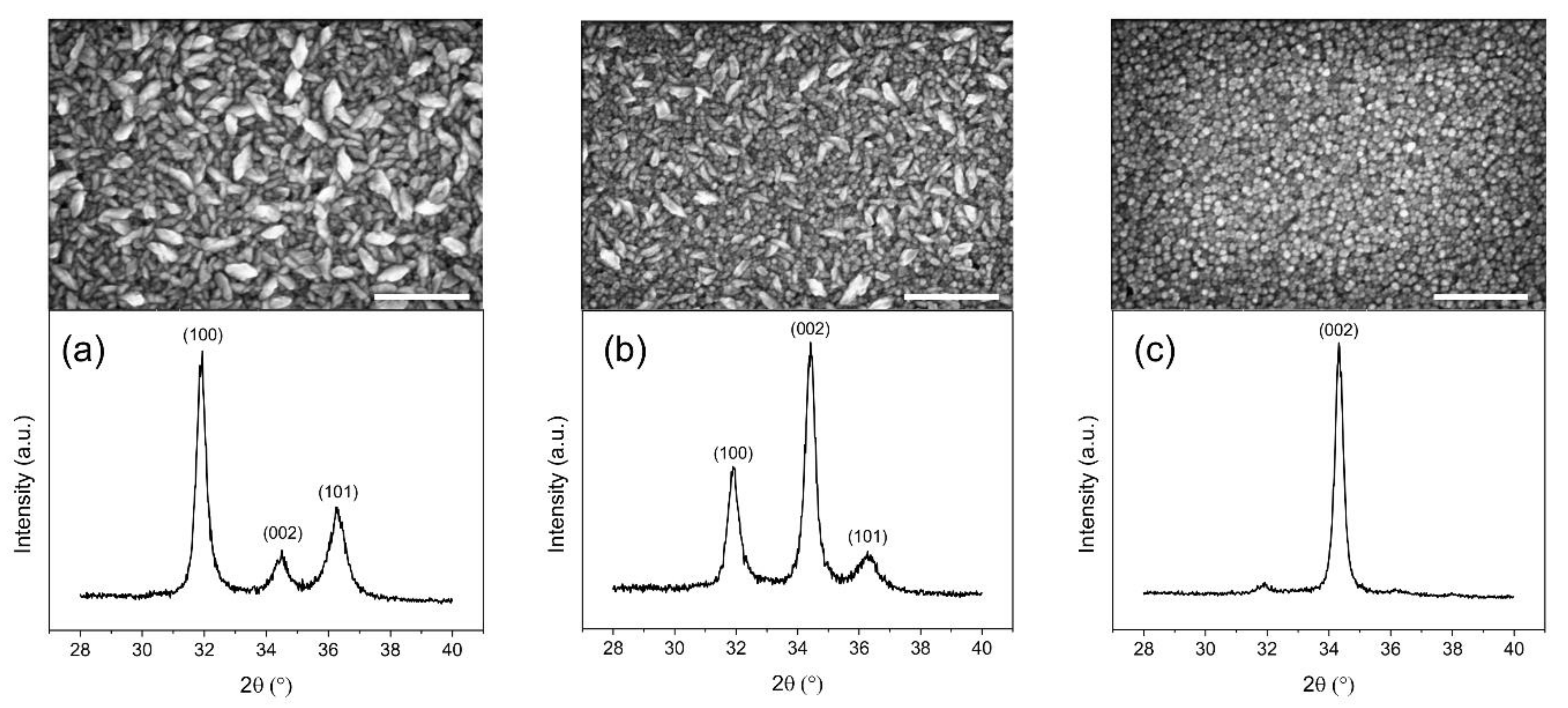

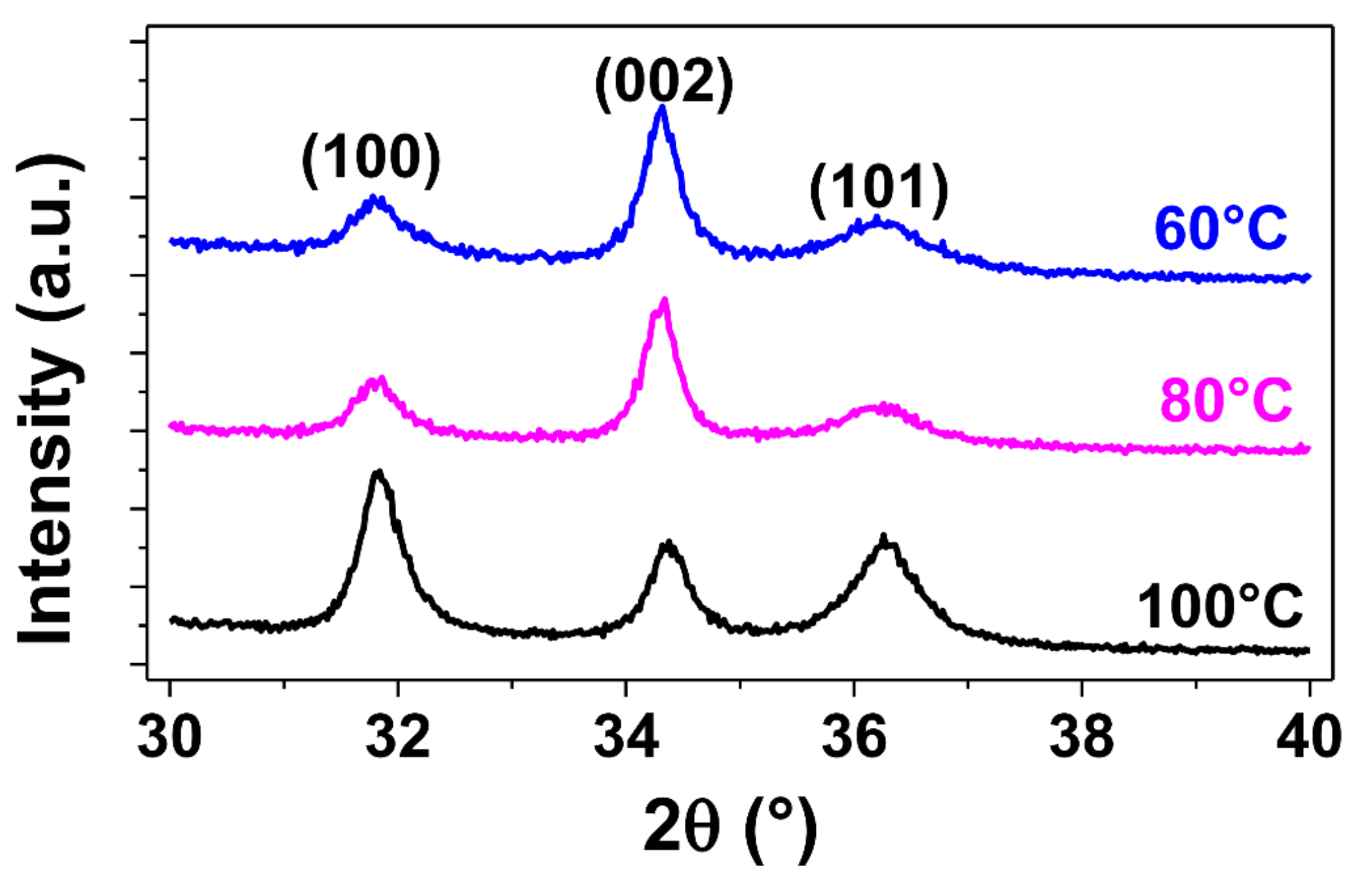

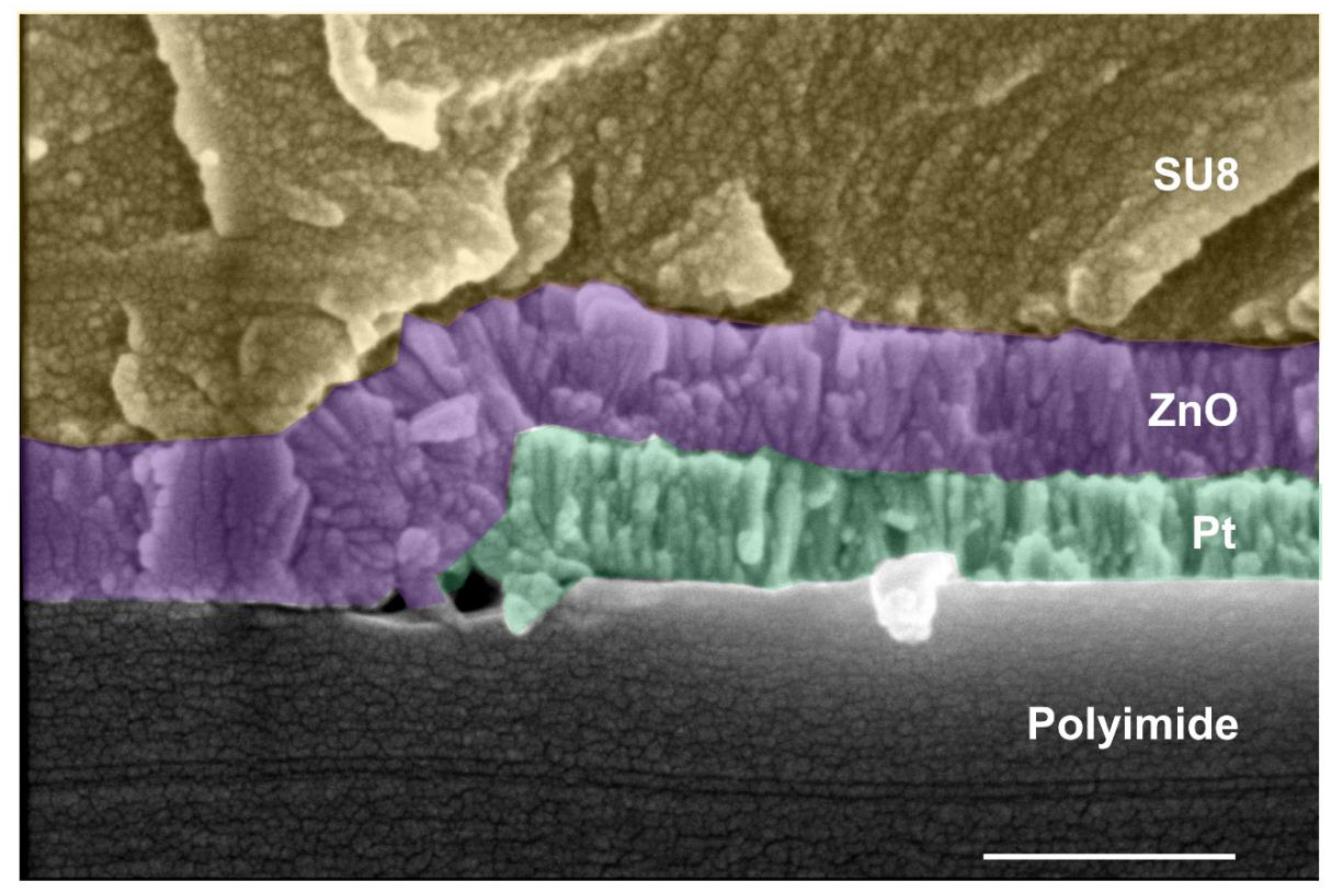

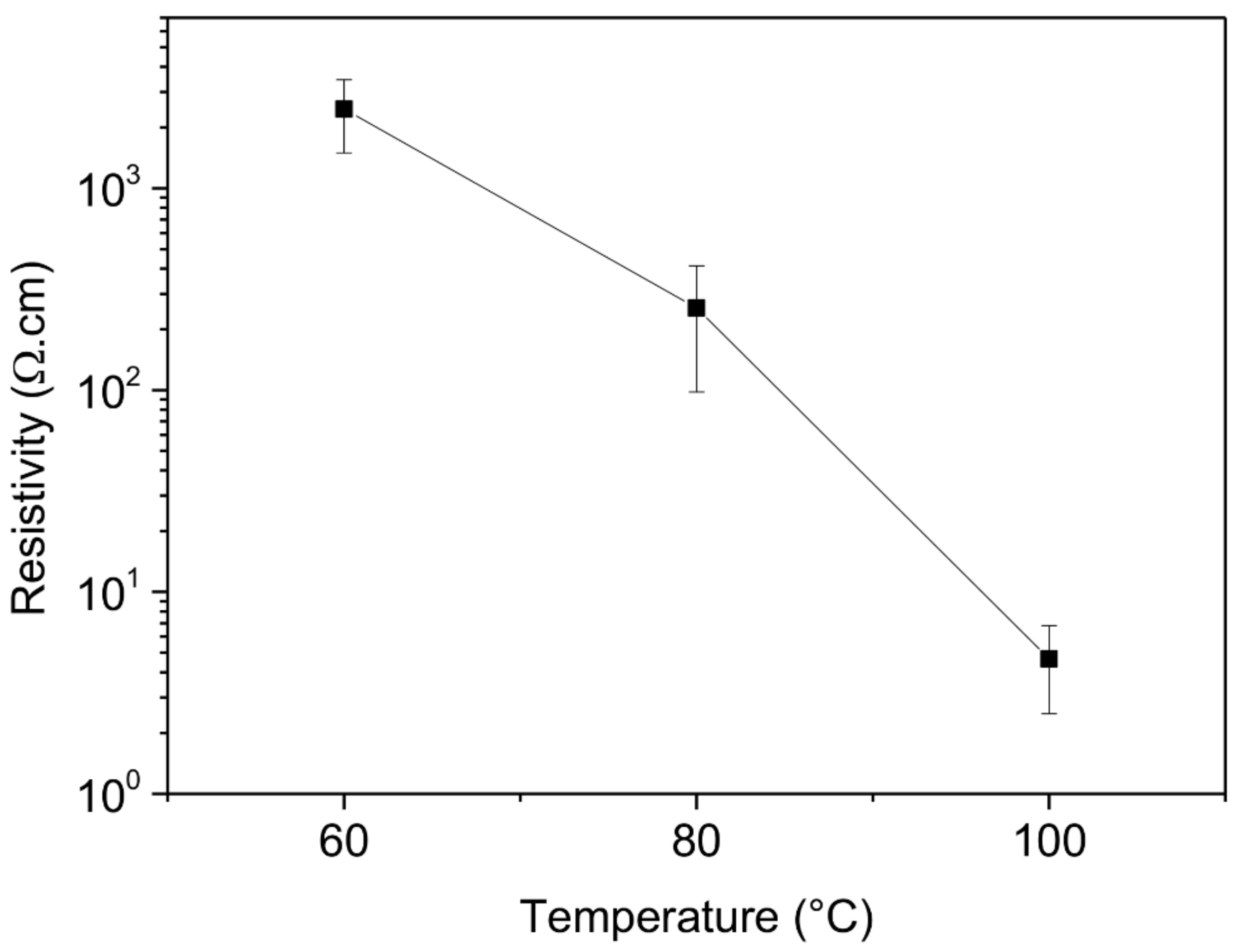

3.1. Structural and Electrical Properties of ZnO Thin Films

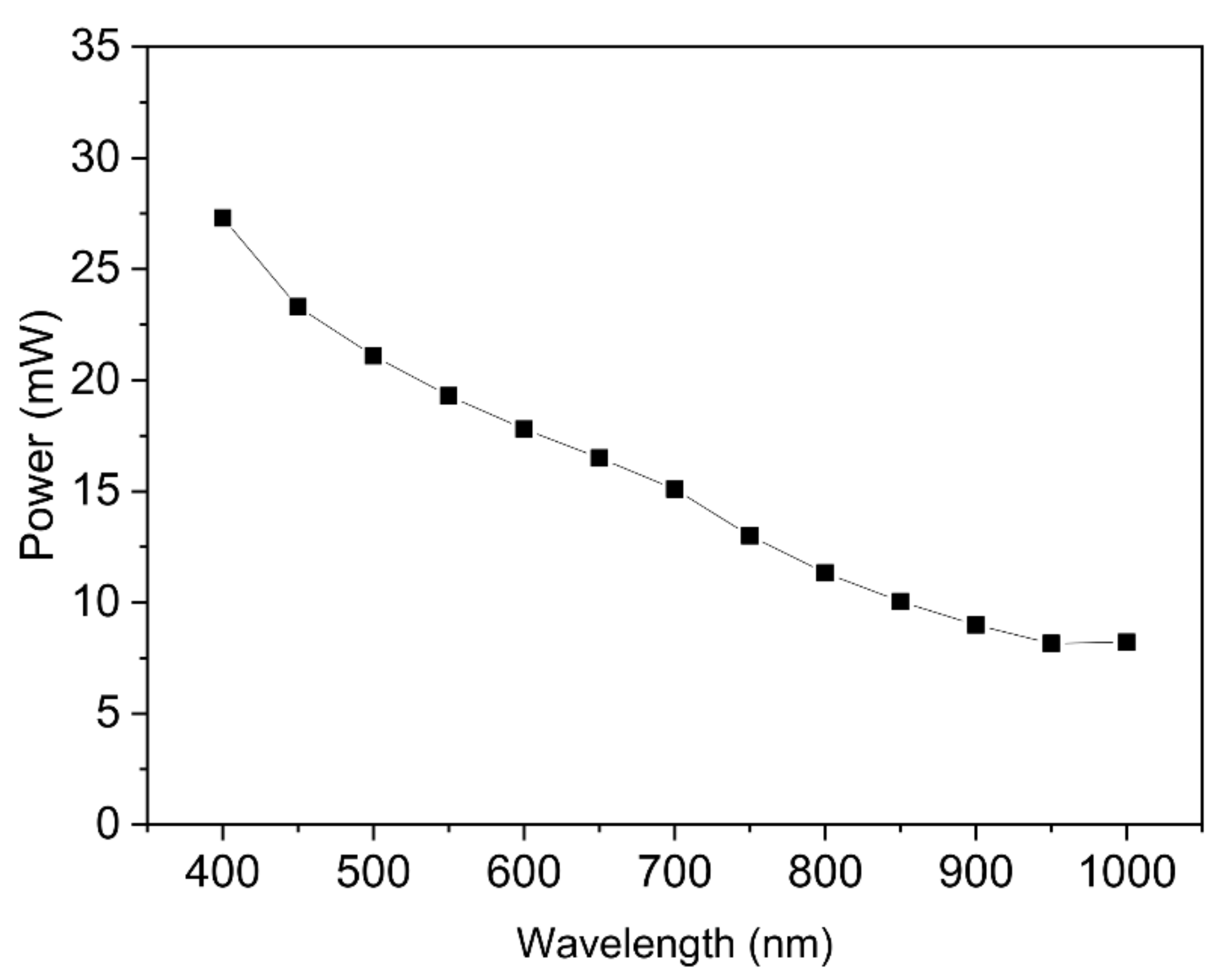

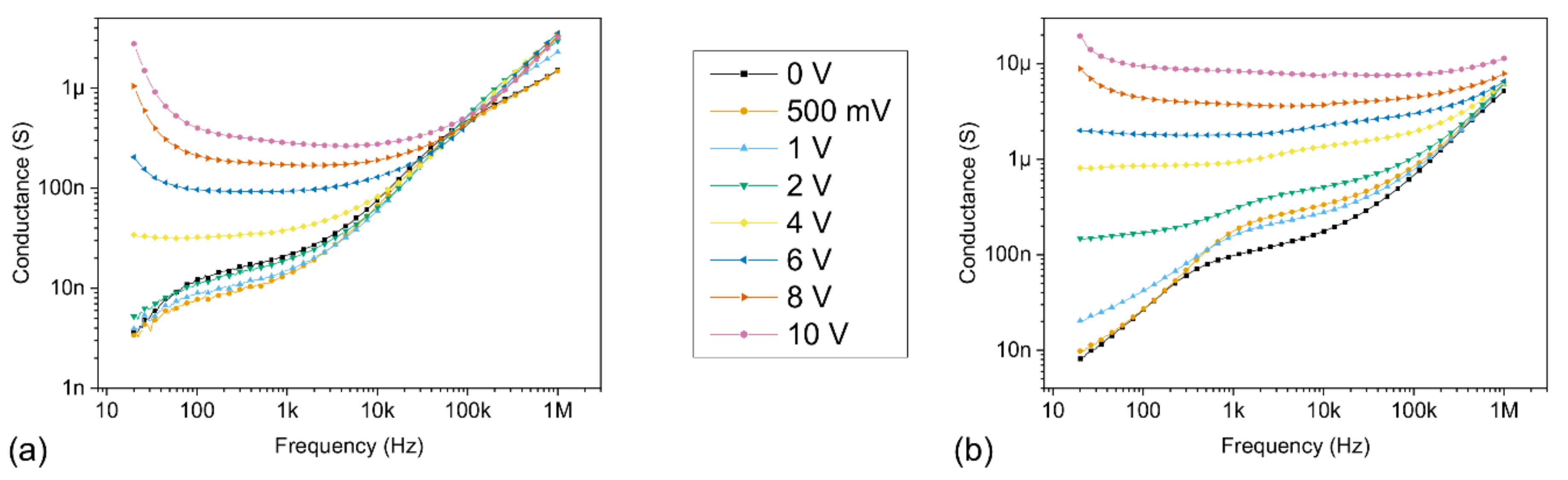

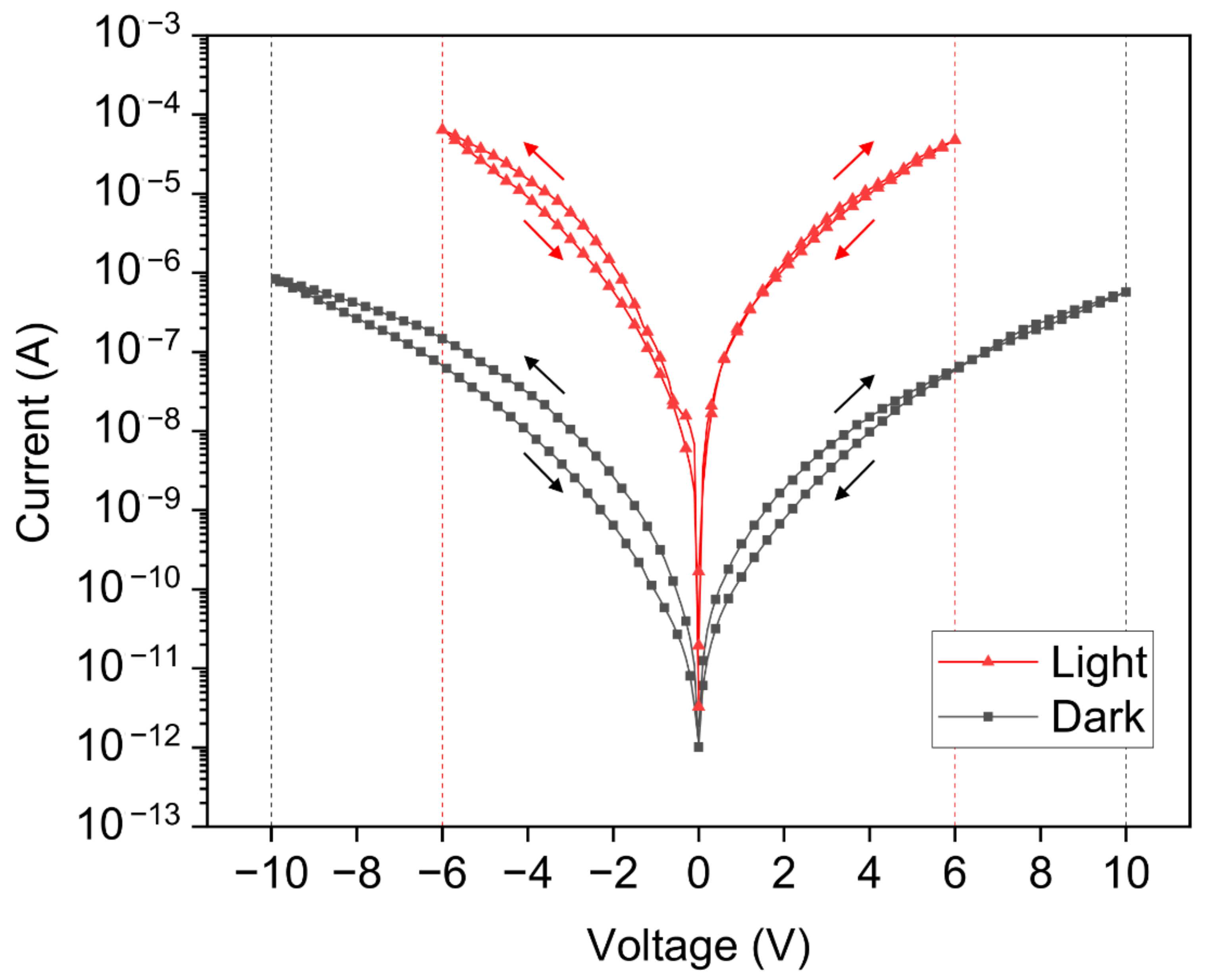

3.2. Capacitance Modulation by Light

3.3. Capacitance Modulation by Light and Mechanical Strain

4. Conclusions

Supplementary Materials

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Wu, X.; Yang, E.S.; Evans, H.L. Negative capacitance at metal-semiconductor interfaces. J. Appl. Phys. 1990, 68, 2845–2848. [Google Scholar] [CrossRef]

- Jones, B.; Santana, J.; McPherson, M. Negative capacitance effects in semiconductor diodes. Solid State Commun. 1998, 107, 47–50. [Google Scholar] [CrossRef]

- Jonscher, A.K. The physical origin of negative capacitance. J. Chem. Soc. Faraday Trans. 1986, 82, 75–81. [Google Scholar] [CrossRef]

- Íñiguez, J.; Zubko, P.; Luk’Yanchuk, I.; Cano, A. Ferroelectric negative capacitance. Nat. Rev. Mater. 2019, 4, 243–256. [Google Scholar] [CrossRef] [Green Version]

- Yadav, A.K.; Nguyen, K.X.; Hong, Z.; García-Fernández, P.; Aguado-Puente, P.; Nelson, C.T.; Das, S.; Prasad, B.; Kwon, D.; Cheema, S.; et al. Spatially resolved steady-state negative capacitance. Nature 2019, 565, 468–471. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Cheng, P.-H.; Yin, Y.-T.; Tsai, I.-N.; Lu, C.-H.; Li, L.-J.; Pan, S.C.; Shieh, J.; Shiojiri, M.; Chen, M.-J. Negative capacitance from the inductance of ferroelectric switching. Commun. Phys. 2019, 2, 32. [Google Scholar] [CrossRef] [Green Version]

- Khan, A.I.; Bhowmik, D.; Yu, P.; Kim, S.J.; Pan, X.; Ramesh, R.; Salahuddin, S. Experimental evidence of ferroelectric negative capacitance in nanoscale heterostructures. Appl. Phys. Lett. 2011, 99, 113501. [Google Scholar] [CrossRef] [Green Version]

- Wong, J.C.; Salahuddin, S. Negative Capacitance Transistors. Proc. IEEE 2018, 107, 49–62. [Google Scholar] [CrossRef]

- Salahuddin, S.; Datta, S. Use of Negative Capacitance to Provide Voltage Amplification for Low Power Nanoscale Devices. Nano Lett. 2008, 8, 405–410. [Google Scholar] [CrossRef] [PubMed]

- Tade, O.; Gardner, P.; Hall, P. Negative impedance converters for broadband antenna matching. In Proceedings of the 2012 42nd European Microwave Conference, Amsterdam, The Netherlands, 29 October–1 November 2012; pp. 613–616. [Google Scholar] [CrossRef]

- Khan, A.I.; Chatterjee, K.; Wang, B.; Drapcho, S.; You, L.; Serrao, C.; Bakaul, S.R.; Ramesh, R.; Salahuddin, S. Negative capacitance in a ferroelectric capacitor. Nat. Mater. 2015, 14, 182–186. [Google Scholar] [CrossRef]

- Bilkan, Ç.; Gümüş, A.; Altindal, Ş. The source of negative capacitance and anomalous peak in the forward bias capacitance-voltage in Cr/p-si Schottky barrier diodes (SBDs). Mater. Sci. Semicond. Process. 2015, 39, 484–491. [Google Scholar] [CrossRef]

- Dianat, P.; Prusak, R.W.; Gallo, E.; Cola, A.; Persano, A.; Quaranta, F.; Nabet, B. A highly tunable heterostructure metal-semiconductor-metal capacitor utilizing embedded 2-dimensional charge. Appl. Phys. Lett. 2012, 100, 153505. [Google Scholar] [CrossRef]

- Zhu, M.; Huang, Y.; Pei, Z.; Xue, Q.; Li, H.; Geng, H.; Zhi, C. Capacitance Enhancement in a Semiconductor Nanostructure-Based Supercapacitor by Solar Light and a Self-Powered Supercapacitor-Photodetector System. Adv. Funct. Mater. 2016, 26, 4481–4490. [Google Scholar] [CrossRef]

- Tu, L.; Cao, R.; Wang, X.; Chen, Y.; Wu, S.; Wang, F.; Wang, Z.; Shen, H.; Lin, T.; Zhou, P.; et al. Ultrasensitive negative capacitance phototransistors. Nat. Commun. 2020, 11, 1–8. [Google Scholar] [CrossRef] [PubMed]

- Yoo, J.; Nam, Y.; Kim, T.-S.; Jung, G.; Song, J.-H.; Chang, S.-K. Light-induced capacitance enhancement and successive carrier escape in InGaN/GaN multiple quantum wells. J. Appl. Phys. 2020, 127, 024503. [Google Scholar] [CrossRef]

- Dianat, P. Unconventional Photo Capacitor with giant light induced capacitance enhancement. Photodetectors Mater. Devices Appl. 2016. [Google Scholar] [CrossRef]

- Korucu, D.; Turut, A.; Altindal, Ş. The origin of negative capacitance in Au/n-GaAs Schottky barrier diodes (SBDs) prepared by photolithography technique in the wide frequency range. Curr. Appl. Phys. 2013, 13, 1101–1108. [Google Scholar] [CrossRef]

- Trong, V.D.; Anh, C.T.; Cuong, N.D.; Binh, P.H.; Truong, C.T.; Pham, A.T. Frequency dependence of negative capacitance in light-emitting devices. In Proceedings of the 2012 Fourth International Conference on Communications and Electronics (ICCE), Hue, Vietnam, 1–3 August 2012; pp. 44–47. [Google Scholar]

- Byrum, E.L.; Ariyawansa, G.; Jayasinghe, R.C.; Dietz, N.L.; Perera, A.G.U.; Matsik, S.G.; Ferguson, I.T.; Bezinger, A.; Liu, H.C. Negative capacitance in GaN/AlGaN heterojunction dual-band detectors. J. Appl. Phys. 2009, 106, 053701. [Google Scholar] [CrossRef]

- Mikhelashvili, V.; Padmanabhan, R.; Meyler, B.; Yofis, S.; Eisenstein, G. Negative capacitance in optically sensitive metal-insulator-semiconductor-metal structures. J. Appl. Phys. 2016, 120, 224502. [Google Scholar] [CrossRef]

- Ershov, M.; Liu, H.C.; Li, L.; Buchanan, M.; Wasilewski, Z.R.; Jonscher, A.K. Negative capacitance effect in semiconductor devices. IEEE Trans. Electron Devices 1998, 45, 2196–2206. [Google Scholar] [CrossRef] [Green Version]

- Bobby, A.; Shiwakoti, N.; Verma, S.; Asokan, K.; Antony, B. Frequency dependent negative capacitance effect and dielectric properties of swift heavy ion irradiated Ni/oxide/n-GaAs Schottky diode. Phys. B Condens. Matter 2016, 489, 23–27. [Google Scholar] [CrossRef]

- Werner, J.; Levi, A.F.J.; Tung, R.T.; Anzlowar, M.; Pinto, M. Origin of the Excess Capacitance at Intimate Schottky Contacts. Phys. Rev. Lett. 1988, 60, 53–56. [Google Scholar] [CrossRef]

- Bouiadjra, W.B.; Saïdane, A.; Mostefa, A.; Henini, M.; Shafi, M. Effect of nitrogen incorporation on electrical properties of Ti/Au/GaAsN Schottky diodes. Superlattices Microstruct. 2014, 71, 225–237. [Google Scholar] [CrossRef]

- Janotti, A.; van de Walle, C.G. Fundamentals of zinc oxide as a semiconductor. Rep. Prog. Phys. 2009, 72. [Google Scholar] [CrossRef] [Green Version]

- Gomez, J.L.; Tigli, O. Zinc oxide nanostructures: From growth to application. J. Mater. Sci. 2012, 48, 612–624. [Google Scholar] [CrossRef]

- Liu, L.; Mei, Z.; Tang, A.; Azarov, A.; Kuznetsov, A.; Xue, Q.-K.; Du, X. Oxygen vacancies: The origin ofn-type conductivity in ZnO. Phys. Rev. B 2016, 93, 235305. [Google Scholar] [CrossRef] [Green Version]

- Brillson, L.J.; Lu, Y. ZnO Schottky barriers and Ohmic contacts. J. Appl. Phys. 2011, 109, 121301. [Google Scholar] [CrossRef]

- Allen, M.W.; Durbin, S.M. Influence of oxygen vacancies on Schottky contacts to ZnO. Appl. Phys. Lett. 2008, 92, 122110. [Google Scholar] [CrossRef]

- El Kamel, F.; Gonon, P.; Jomni, F.; Yangui, B. Observation of negative capacitances in metal-insulator-metal devices based on a-BaTiO3:H. Appl. Phys. Lett. 2008, 93, 042904. [Google Scholar] [CrossRef]

- Laurenti, M.; Verna, A.; Chiolerio, A. Evidence of Negative Capacitance in Piezoelectric ZnO Thin Films Sputtered on Interdigital Electrodes. ACS Appl. Mater. Interfaces 2015, 7, 24470–24479. [Google Scholar] [CrossRef]

- Hu, P.; Lu, J.Q.; Wu, S.X.; Lv, Q.B.; Li, S.W. Coexistence of Memristive Behaviors and Negative Capacitance Effects in Single-Crystal TiO2 Thin-Film-Based Devices. IEEE Electron Device Lett. 2012, 33, 890–892. [Google Scholar] [CrossRef]

- Ke, Q.; Lou, X.; Yang, H.; Kumar, A.; Zeng, K.; Wang, J. Negative capacitance induced by redistribution of oxygen vacancies in the fatigued BiFeO3-based thin film. Appl. Phys. Lett. 2012, 101, 22904. [Google Scholar] [CrossRef]

- Gul, F.; Efeoglu, H. ZnO and ZnO1−x based thin film memristors: The effects of oxygen deficiency and thickness in resistive switching behaviour. Ceram. Int. 2017, 43, 10770–10775. [Google Scholar] [CrossRef] [Green Version]

- Cho, K.; Jo, J.; Shin, C. Amorphous Indium Zinc Oxide Thin-Film Transistor with Steep Subthreshold Slope by Negative Capacitance. IEICE Trans. Electron. 2016, 99, 544–546. [Google Scholar] [CrossRef]

- Mazumder, N.; Roy, R.; Ghorai, U.K.; Saha, S.; Chattopadhyay, K.K.; Mandal, P. Negative capacitance in ZnO1−xChx (Ch = S, Se, Te): Role of localized charge recombination. J. Appl. Phys. 2017, 121, 135702. [Google Scholar] [CrossRef]

- Joly, R.; Girod, S.; Adjeroud, N.; Nguyen, T.; Grysan, P.; Klein, S.; Menguelti, K.; Vergne, C.; Polesel-Maris, J. Polymeric cantilevered piezotronic strain microsensors processed by Atomic Layer Deposition. Sens. Actuators Phys. 2020, 315, 112280. [Google Scholar] [CrossRef]

- Laurenti, M.; Porro, S.; Pirri, C.F.; Ricciardi, C.; Chiolerio, A. Zinc Oxide Thin Films for Memristive Devices: A Review. Crit. Rev. Solid State Mater. Sci. 2016, 42, 153–172. [Google Scholar] [CrossRef]

- Matienzo, L.J.; Unertl, W.N. Adhesion of metal films to polyimides. Polyim. Fundam. Appl. 1996. [Google Scholar] [CrossRef]

- Rhoderick, E.H.; Williams, R.H. Metal-Semiconductor Contacts; Clarendon Press: Oxford, UK, 1988; Available online: https://books.google.lu/books?id=0zcoAQAAMAAJ (accessed on 9 March 2021).

- Cai, J.; Ma, Z.; Wejinya, U.; Zou, M.; Liu, Y.; Zhou, H.; Meng, X. A revisit to atomic layer deposition of zinc oxide using diethylzinc and water as precursors. J. Mater. Sci. 2018, 54, 5236–5248. [Google Scholar] [CrossRef]

- Briscoe, J.; Dunn, S. Piezoelectric nanogenerators—A review of nanostructured piezoelectric energy harvesters. Nano Energy 2015, 14, 15–29. [Google Scholar] [CrossRef]

- Wang, Z.L. Piezoelectric Nanogenerators Based on Zinc Oxide Nanowire Arrays. Science 2006, 312, 242–246. [Google Scholar] [CrossRef]

- Wang, X.; Zhou, J.; Song, J.; Liu, J.; Xu, A.N.; Wang, Z.L. Piezoelectric Field Effect Transistor and Nanoforce Sensor Based on a Single ZnO Nanowire. Nano Lett. 2006, 6, 2768–2772. [Google Scholar] [CrossRef]

- Van der Pauw, L.J. A method of measuring the resistivity and Hall coefficient on lamellae of arbitrary shape. Philips Tech. Rev. 1958, 20, 220–224. [Google Scholar]

- Nguyen, T.; Adjeroud, N.; Guennou, M.; Guillot, J.; Fleming, Y.; Papon, A.-M.; Arl, D.; Menguelti, K.; Joly, R.; Gambacorti, N.; et al. Controlling electrical and optical properties of zinc oxide thin films grown by thermal atomic layer deposition with oxygen gas. Results Mater. 2020, 6, 100088. [Google Scholar] [CrossRef]

- Ellmer, K. Resistivity of polycrystalline zinc oxide films: Current status and physical limit. J. Phys. D Appl. Phys. 2001, 34, 3097–3108. [Google Scholar] [CrossRef]

- Kwon, S.; Bang, S.; Lee, S.; Jeon, S.; Jeong, W.; Kim, H.; Gong, S.C.; Chang, H.J.; Park, H.-H.; Jeon, H. Characteristics of the ZnO thin film transistor by atomic layer deposition at various temperatures. Semicond. Sci. Technol. 2009, 24. [Google Scholar] [CrossRef]

- Sze, S.; Coleman, D.; Loya, A. Current transport in metal-semiconductor-metal (MSM) structures. Solid-State Electron. 1971, 14, 1209–1218. [Google Scholar] [CrossRef]

- Sze, S.M.; Ng, K.K. Physics of Semiconductor Devices, 3rd ed.; Simon, M., Kwok, S., Ng, K., Eds.; John Wiley Sons, Inc.: Hoboken, NJ, USA, 2007. [Google Scholar] [CrossRef]

- Bardeen, J. Surface States and Rectification at a Metal Semi-Conductor Contact. Phys. Rev. 1947, 71, 717–727. [Google Scholar] [CrossRef]

- Zhang, Y.; Liu, Y.; Wang, Z.L. Fundamental Theory of Piezotronics. Adv. Mater. 2011, 23, 3004–3013. [Google Scholar] [CrossRef] [PubMed]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Joly, R.; Girod, S.; Adjeroud, N.; Grysan, P.; Polesel-Maris, J. Evidence of Negative Capacitance and Capacitance Modulation by Light and Mechanical Stimuli in Pt/ZnO/Pt Schottky Junctions. Sensors 2021, 21, 2253. https://doi.org/10.3390/s21062253

Joly R, Girod S, Adjeroud N, Grysan P, Polesel-Maris J. Evidence of Negative Capacitance and Capacitance Modulation by Light and Mechanical Stimuli in Pt/ZnO/Pt Schottky Junctions. Sensors. 2021; 21(6):2253. https://doi.org/10.3390/s21062253

Chicago/Turabian StyleJoly, Raoul, Stéphanie Girod, Noureddine Adjeroud, Patrick Grysan, and Jérôme Polesel-Maris. 2021. "Evidence of Negative Capacitance and Capacitance Modulation by Light and Mechanical Stimuli in Pt/ZnO/Pt Schottky Junctions" Sensors 21, no. 6: 2253. https://doi.org/10.3390/s21062253

APA StyleJoly, R., Girod, S., Adjeroud, N., Grysan, P., & Polesel-Maris, J. (2021). Evidence of Negative Capacitance and Capacitance Modulation by Light and Mechanical Stimuli in Pt/ZnO/Pt Schottky Junctions. Sensors, 21(6), 2253. https://doi.org/10.3390/s21062253