Abstract

A reconfigurable -boosted, image-rejected downconversion mixer is presented in this paper using the SiGe 8 HP technology. The proposed mixer operates within 0.9–13.5 GHz that is suitable for software-defined radio applications. The conversion mixer comprises of resistive biased radio frequency (RF) section, double balanced Gilbert cell mixer core sections divided as per I and Q stages for image-rejection purpose, inductively peaked -boosting section and tunable filter section, respectively. In comparison to previous works in the scientific literature, the design shows enhanced conversion gain (CG), noise figure (NF), and image-rejection ratio (IRR). For the entire band of operation, the mixer attains a good return loss of <−10 dB. Additionally, the design accomplishes an excellent CG of 22 dB, NF of 2.5 dB, and an image-rejection ratio of 30.2 dB at maximum frequency. Finally, a third-order intercept point (IP3) of −3.28 dBm and 1 dB compression point (CP1) of −13 dBm, respectively, shows moderate linearity performance.

1. Introduction

Wireless communications have become increasingly popular due to the wide range of potential applications. In recent years, this industry has experienced tremendous development leading to many wireless standards. Therefore, it is desired to have a radio front end that is capable of handling multiple standards and applications [1,2,3]. For developing such receiver circuits, especially within high-frequency bands, proper radio frequency (RF) and baseband blocks must be available to perform downconversion operation. Ideally, distinct radio front ends can be used for different standards and applications. However, this is not possible due to frequency sensitivity [4,5]. Hence, RF-front-ends are compatible with distinct standards operating at specific frequencies. In addition, one must develop advanced systems with modern blocks with the emergence of the latest wireless standards. Reconfigurable blocks can be reused to accommodate multiple wireless standards, and thus lower development time and cost [6]. Software-defined radios (SDRs) offer this flexibility by allowing multiple band operations inside a single circuitry [7,8], whereas cognitive radios (CRs) take care of spectrum crowding and congestion hurdles [9,10]. Although most of the research is based on single-band cognitive radio, multiband cognitive radio has greater potential in the efficient implementation of cognitive networks. It is expected that multiband cognitive radios improve the throughput and lower handoff frequency for better channel maintenance. However, wideband front end and access to multiband spectrum present several challenges [11]. Thus, the best is to have CR with SDR features, which can sense the electromagnetic spectrum environment, tracking and responding to the variations and findings in a smart way. Moreover, the cost and power consumption are significant while talking about reconfigurable receiver architectures [12]. Earlier receivers were using analog-to-digital converters. Signal processing is carried out in the digital domain that consumes high power and attains inaccurate RF signals, which limits the use of SDRs. Thus, to overcome that, mixers must be used [13].

Mixers are used for frequency conversion purposes. Upon mixing, the frequency of the output signal is in the form of a sum or difference of those of the input signals. Within the receiver, mixers can perform frequency downconversion to shift RF to IF [14]. For good performance with low NF, high linearity, polarity switching through local oscillator (LO) input is required. Such a mixer will have radio frequency (RF) signals divided into in-phase and out-of-phase parts; the conversion switch operated by LO signal can alternatively choose in-phase and out-of-phase signals. Ideally, mixers will introduce the minimum amount of noise and have good linearity [15]. Moreover, they should be independent of LO amplitude and intermodulation products. However, practical mixers have the following limitations: non-negligible NF, limited CG, and linearity [16]. Mixers are broadly classified as passive mixers and active mixers. Passive mixers introduce signal attenuation and mixing is achieved through passive switches. Therefore, the switches are turned on and off depending on the LO signal, which is compared to a reference voltage and mixing is achieved through the multiplication operation of RF and LO frequency signals (in terms of square wave or sinewave). These mixers are widely used because of their simplicity, zero power consumption, high IP3, and good NF at the expense of port isolation. However, its main drawback is the high LO power requirement [14]. In contrast to passive mixers, active mixers can provide high CG, good port isolation, low NF, and low LO power requirements. However, it is difficult for them to achieve good linearity. Thus, based on the advantages, active mixers are preferred over passive mixers. Among active mixers, Gilbert mixer is the most commonly used architecture that follows a double balanced structure. This configuration shows high isolation [17]. The mixer also attains high performance in terms of CG, NF at the expense of linearity [18]. The systematic approach can be used further to improve the overall performance that estimates the proper width-to length (W/L) ratio to attain the required design specifications. This approach shows a good trade-off among different performance parameters [19].

For SDR, a single mixer operating within a wideband would be able to convert multiple RF signals to a single IF signal, reducing the design complexity and overall cost [20]. In general, the overall performance of the receiver depends on various metrics such as dynamic range, IP3, NF, CG, IRR, filtering, signal-noise ratio, and spurious-free dynamic range, respectively. Nevertheless, there are no industrial standards defined for SDRs, but they should be able to attain at least high CG, high IRR, and low NF, respectively [21]. Additionally, SDR mixers should be able to provide linear operation while maintaining stability. However, there are a limited number of SDR mixers that provide good reconfiguration, cover a wide bandwidth, and attain high IP3 due to additional circuitry requirements [22,23]. The design complexity should also be low while consuming low power to prolong the battery lifespan [24].

Reconfigurable SDR mixers can be either switchable or tunable. In case of switchable SDR mixers, reconfiguration is possible using switches along with other components such as inductors, transformers. However, tunable mixers use tunable resonators for reconfiguration. With strict bandwidth requirements, analog or discrete tuning can be opted. Numerous techniques exist for possible tuning of operating frequency, among which typical techniques include transmission line-based designs with limited frequency of operation [25,26], transformer dependent inductors with variable frequency of operation [27], analog bias tuning with limited tuning range, array arranged filters, charge domain discrete-time filters [28], and polyphase networks [29], respectively. Tuning is important to lower the RF front-end section area for multifunctional, multiple frequency, and multistandard applications. Moreover, easy reconfiguration will be done as per the parameters’ necessity with respect to the standards, band of operation and overall performance. Thus, it is expected to have a single tunable filter that can replace the large and expensive filter banks, has a wide operating band, and can be easily optimized as per the standards, band or requirements. Moreover, it should cover a small chip area and consumes less power [30]. Hence, for proper reconfiguration to occur, it is important to have perfect tuning based on the above-mentioned approaches.

Gilbert mixer is quite common among SDR receiver architectures as they can provide high bandwidth and broadband performance without degradation in the performance parameters [31]. Several mixer designs have been discussed in [32,33,34,35,36,37]. As in [38], improved Gilbert mixer design is proposed that attains reasonable CG and high port isolation while operating within a wideband. Likewise, in [39] a reconfigurable Gilbert mixer is proposed that employs a passive switchable network (a combination of switched capacitor and inductors) for tuning purposes, resulting in a highly flexible design. The design attained high CG, moderate IP3 at the expense of NF. To overcome the issues within the above-mentioned designs, a joint LNA + mixer-based design can be used. The proposed design maintains a small chip size and consumes less power [40]. Noise-cancelling plays an important role for such a front-end topology. However, it depends on the proper metric matching based on I/Q mixer topology. Another common approach is to use partial noise-cancelling with a folding mixer architecture with no current reuse, specifically for wideband and low power operation. In this case, gm-boosting is the better option, which is independent of performance metrics matching as used in LNA section. Finally, in [5], a gm-boosted technique is employed in the RF stage of the mixer that helps in CG improvement with low power consumption.

Based on the above-mentioned approaches, a novel Gilbert mixer is proposed that employs gm-boosting technique with high image rejection. For tuning purposes, the ninth-order tunable resonator has been developed using varactors and inductors, where the varactors are responsible for providing tuning behavior within the mixer. In this paper, we discuss the design and analysis of the mixer achieving tunable input-output matching from 0.9 GHz to 13.5 GHz. The rest of the paper is organized as follows: Section 2 focuses on motivation. Section 3 presents the mixer design, followed by the analyses of the proposed mixer in Section 4. Section 5 discusses about the simulation results and the layout of the proposed mixer. The proposed mixer’s reliability performance is analyzed using Relxpert software as discussed in Section 6 and finally Section 7 concludes the paper.

2. Motivation

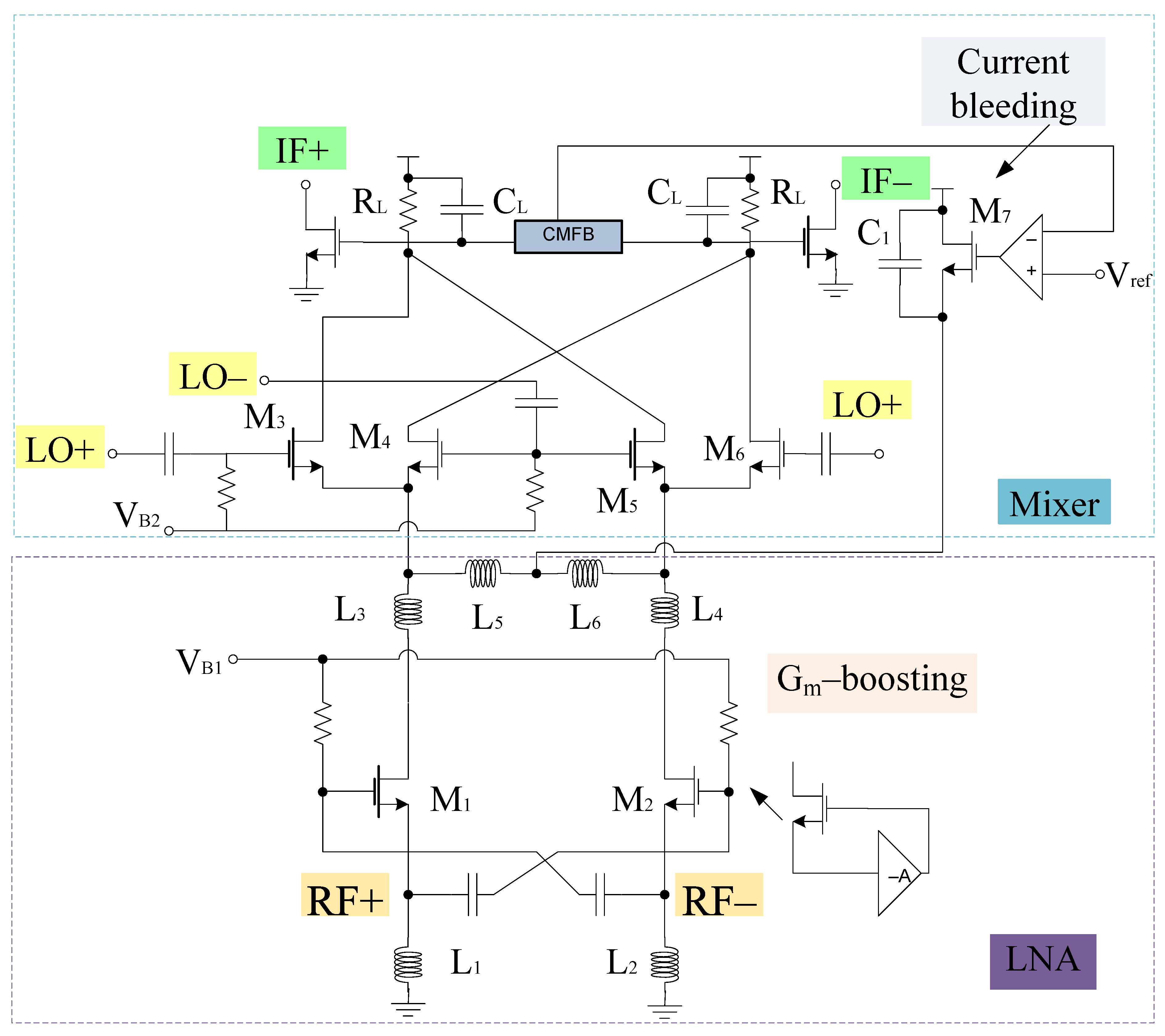

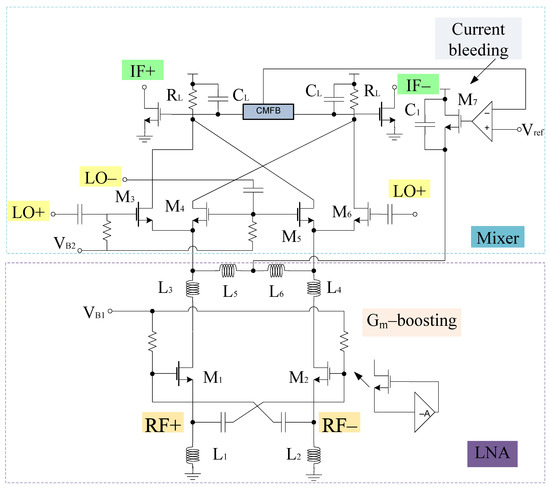

A merged LNA and mixer circuitry is shown in Figure 1. It consists of gm-boosting section, and a source inductor at the input end. At the output end capacitors and inductors (ignoring parasitic resistance) are connected to the LNA section. LNA and mixer employ gm-boosting and current bleeding techniques, which makes the design capable of attaining high CG, low NF, and low power consumption. The design also employs the current peaking approach for wideband operation [40]. Therefore, the input and output impedance can be expressed using a small signal model as shown in Figure 2.

Figure 1.

Merged LNA and mixer.

Figure 2.

Small signal model.

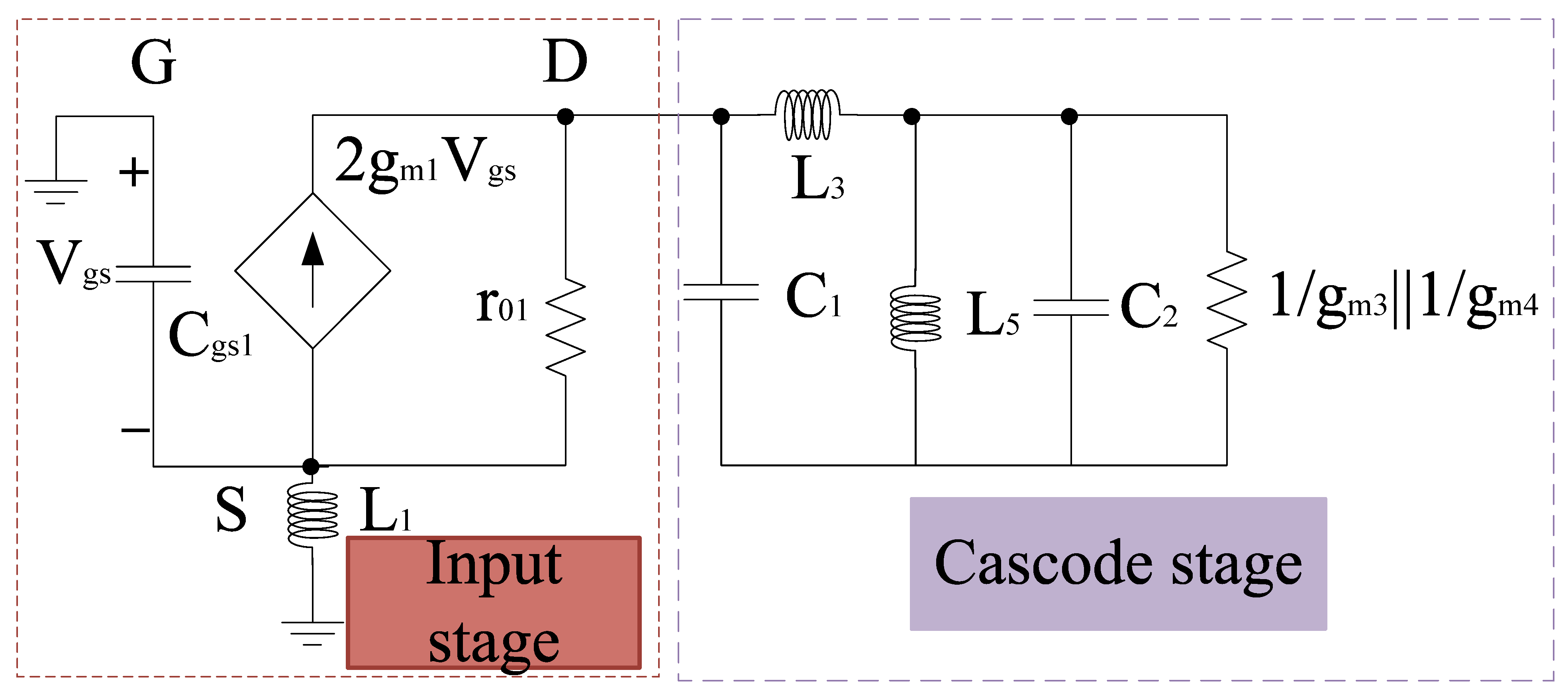

Input impedance, Zin can be expressed as:

where Cgs1 refers to the gate to source capacitance at the input end. Gm-boosting helps in overall gain improvement as it improves the overall transconductance in the stage to which it is connected by the factor () as shown in Figure 1. Upon analysis, it can be expressed as

where Gm1 refers to gm-boosting term; gm1, r01, and ZL refer to the transconductance, transistor impedance, and load impedance, respectively. Similarly, the output impedance, ZL can be expressed as:

where C1, C2 refers to the interstage parasitic capacitance. gm3 and gm4 refer to the transconductance of M3 and M4 transistors. As per the input network, the resonant frequency depends on Cgs1 and L1. The resonant frequency at which the input impedance, Zin will be real can be defined as

Therefore, to attain the tunable frequency, f0 and input impedance, it is desired for Zin to use the tunable filter components. This will enhance not only the overall chip area and power consumption but also the performance metrics such as noise figure. In this paper, we propose an active mixer with a tunable filter, comprising of variable capacitors and inductors. Therefore, in order to attain the minimum return loss, S11 at each centered frequency, the input impedance can be varied with the variation in the current. To improve the performance of the circuitry, the design also employs the gm-boosting technique.

3. Proposed Mixer Topology

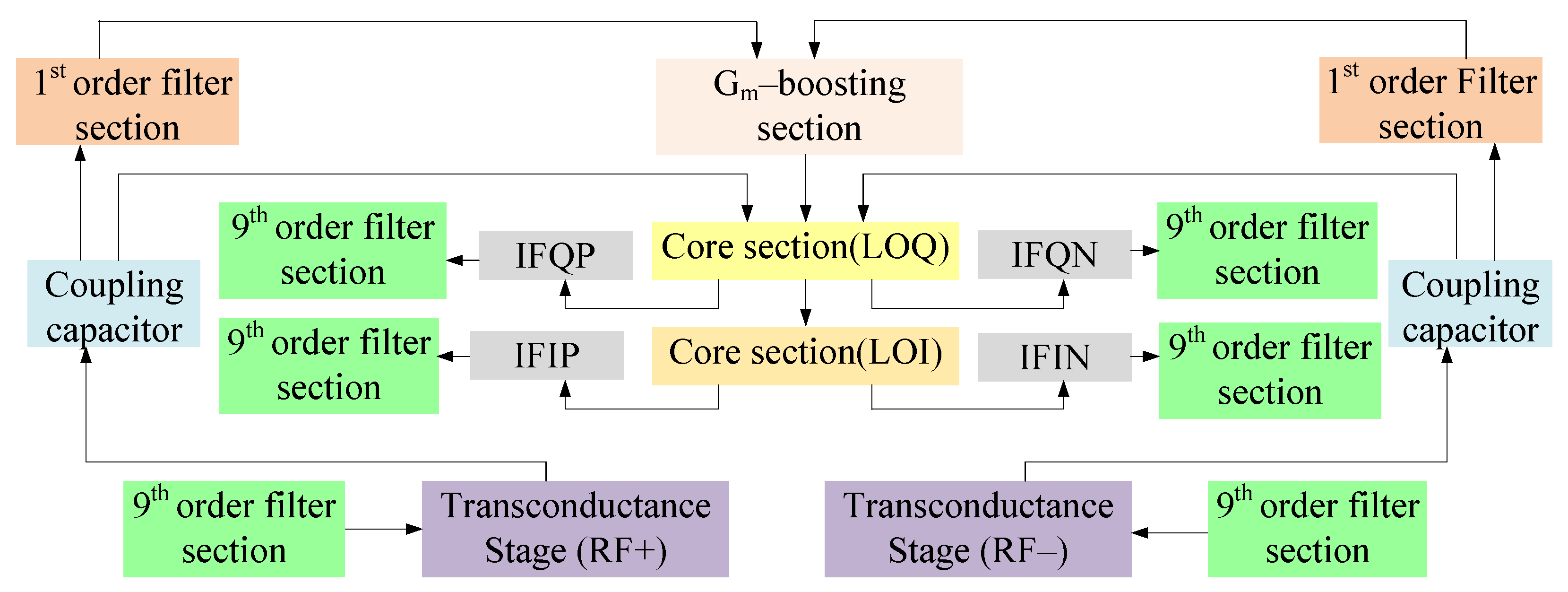

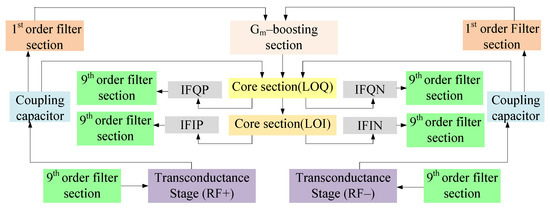

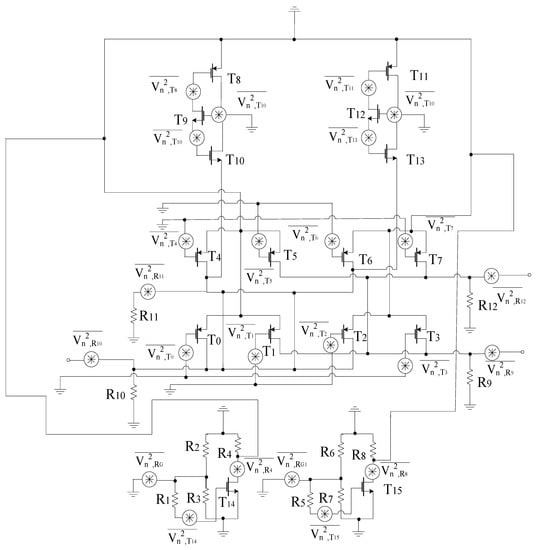

Figure 3 shows the block representation of the proposed mixer with different stages. Starting from the bottom, Stage I refers to the transconductance stage that follows a common source configuration. Stage II refers to the core section categorized into LOI (local oscillator in-phase) and LOQ (local oscillator out-of-phase) stages where input signals are in 90 degree phase shift with respect to each other. For coupling, transconductance and core stages, coupling capacitors have been used. The third stage refers to the gm-boosting stage and finally, stage IV discusses the filters, i.e., first-order filter for avoiding leakage from the power supply and the ninth-order tunable filter for impedance matching at RF and IF stages. For a better understanding of the proposed circuit topology, the design and analysis of all stages have been discussed as follows.

Figure 3.

Block diagram of the proposed mixer.

3.1. Tranconductance Stage

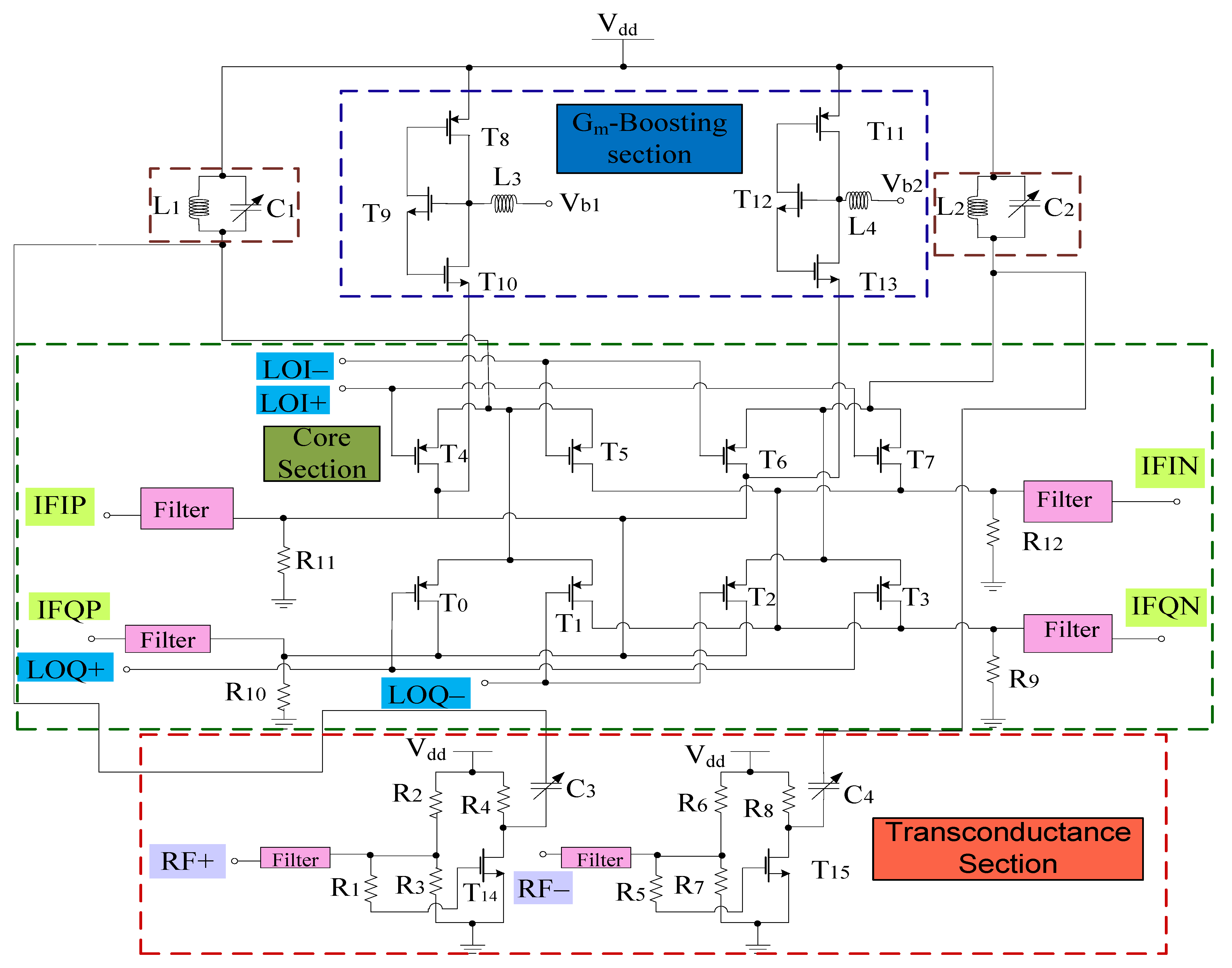

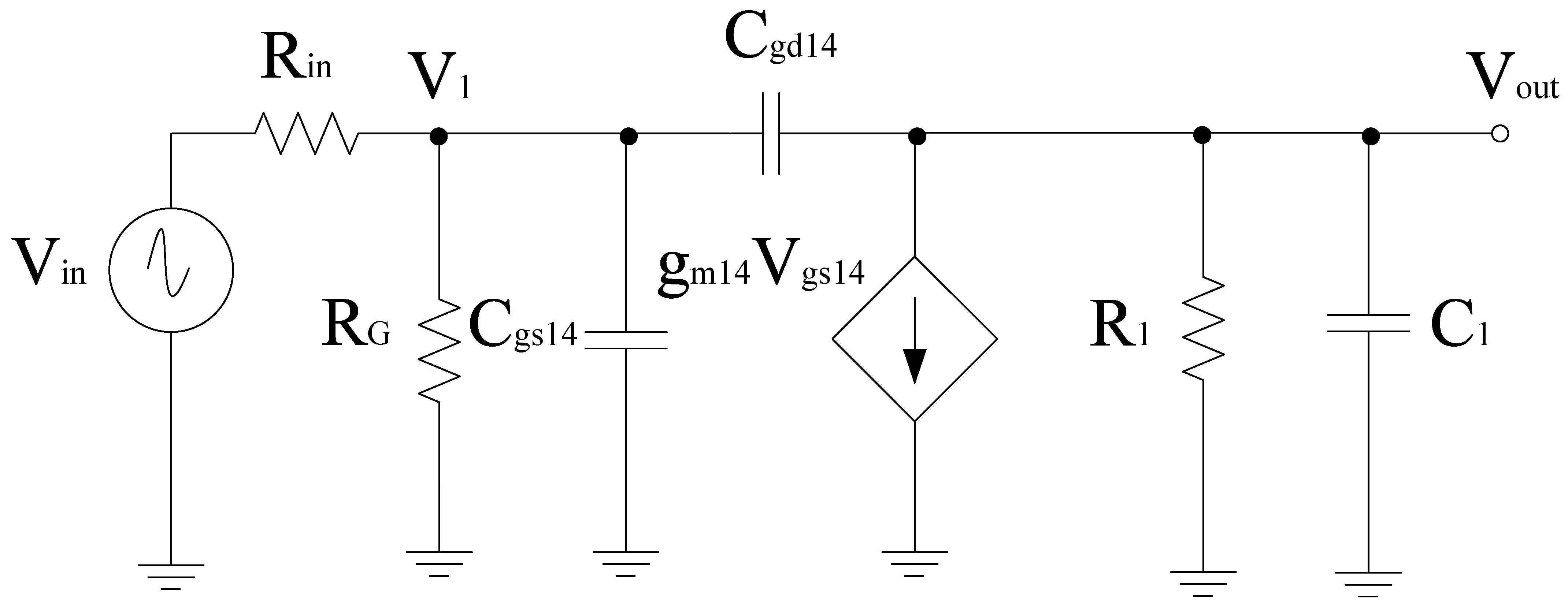

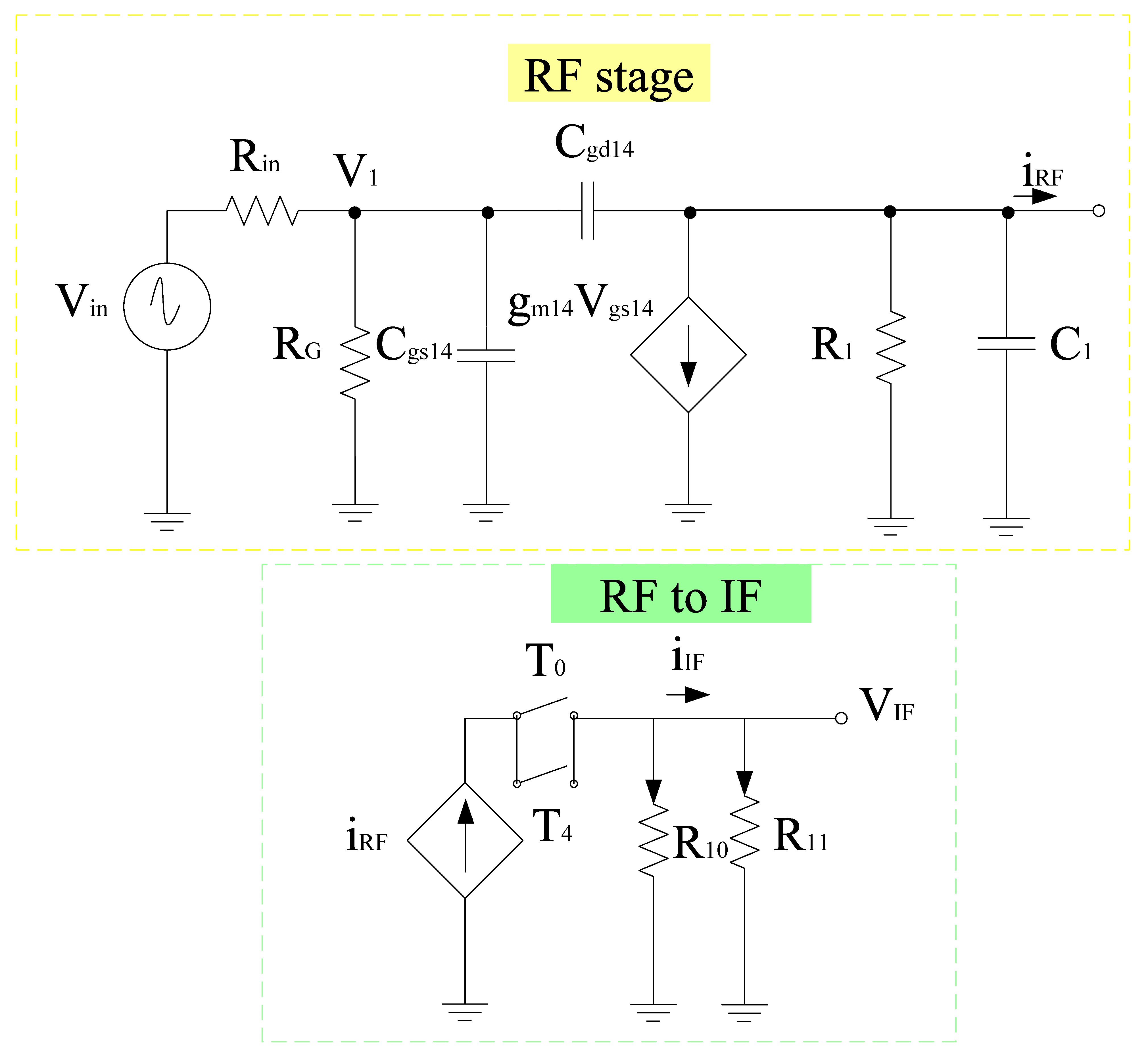

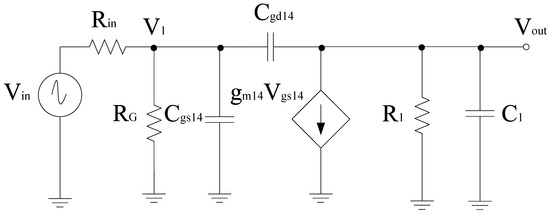

Figure 4 shows the complete circuit diagram of the proposed mixer. Based on the design, the transconductance stage follows the common source configuration and is categorized into different sections, i.e., RF+ and RF− stage, respectively. Both RF+ and RF− stages consist of resistors arranged in a shunt configuration with RF+ stage that consists of input resistors R1, R2, and R3. Similarly, RF− consists of input resistors R5, R6, and R7, respectively. R1 and R5 resistors are responsible for the overall input resistance of each stage and can alter the input voltage and hence the overall gain performance. R4 and R8 refer to the load resistors opted while keeping the desired drain current ID. Filters are also linked to the input end of these stages for impedance matching purposes. Transistor W/L ratio is in such a way that it satisfies the core stage transistor saturation region operating conditions. The input, output impedance, and gain expression of the RF stages can be obtained with the help of the equivalent small signal model. Figure 5 shows the small signal model while ignoring the filter whose analysis is discussed in the filter section. Therefore, for the RF+ stage Rin is the internal resistance, RG refers to the gate resistance, which is the parallel combination of R1, R2, and R3 respectively. Input impedance of RF+ stage

Figure 4.

Proposed mixer.

Figure 5.

Equivalent small signal model for the RF+ stage.

Output impedance of RF+ stage

where R1 = rds14= R4, sC1 = sCdb14+ sC3. Similarly, the input impedance of RF- stage can be represented as

Output impedance of RF− stage

where R2 = rds15= R8, sC2 = sCdb15+ sC4. Therefore, to obtain the frequency response of the small signal circuit, nodal analysis can be done. The first term should be the node at which the currents are added. If node voltages are multiplied, it refers to all admittances being connected to a node. Next terms will have negative signs which are actually neighboring node voltages and each of these terms uses a multiplication operation on the connecting admittance. The final terms refer to the current sources having a positive sign that is considered only if current sources are flowing out of that node [41]. Based on this, we have

By substituting (11) in (9), we get;

Rin is not used and upon simplification and converting GG, G1 to RG, R1, we get;

If s = 0, the low frequency gain is obtained as mentioned below:

When the poles are real and

The denominator of Equation (13) becomes

Similarly, for RF− stage, the simplified gain can be expressed as mentioned below:

3.2. Core Stages

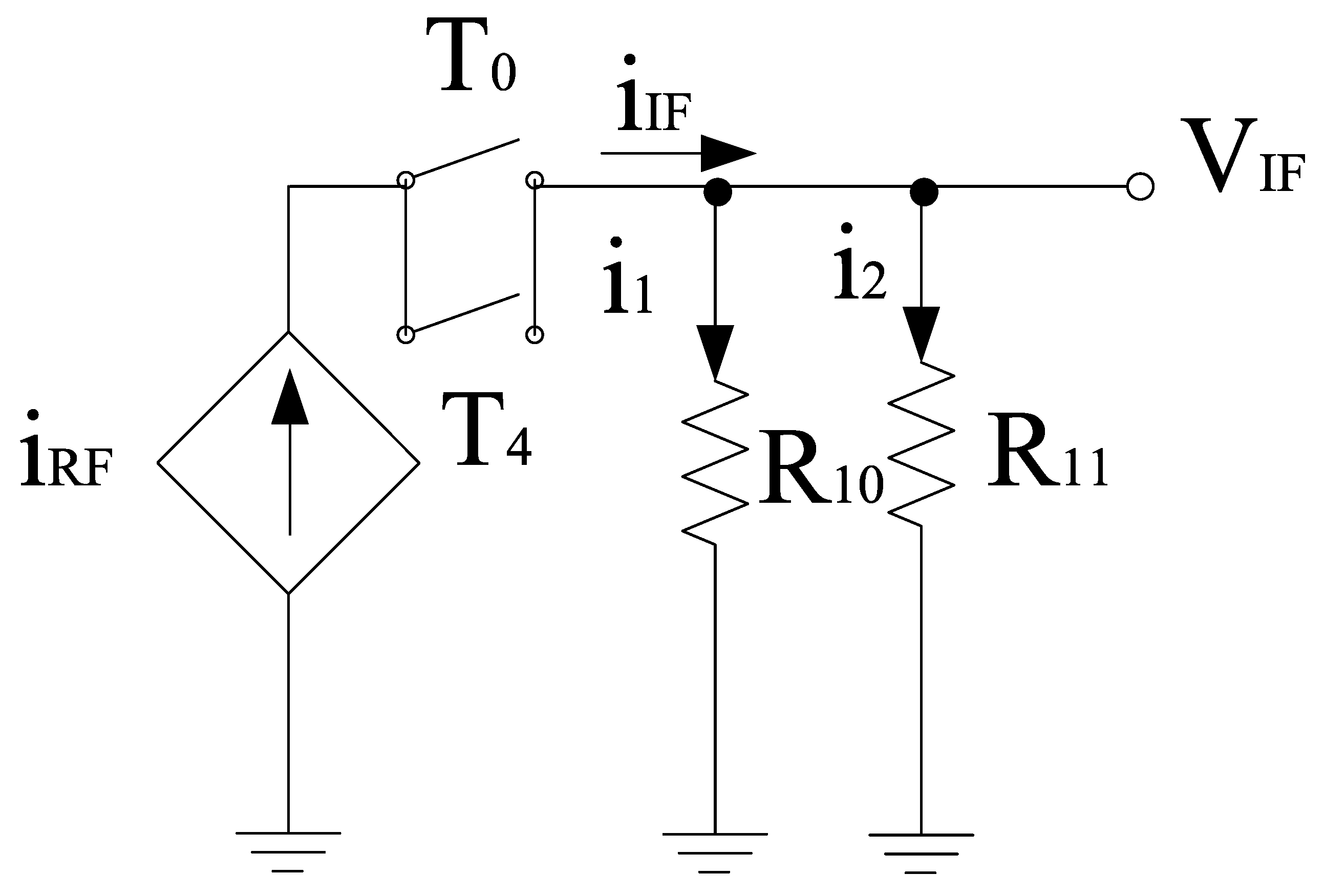

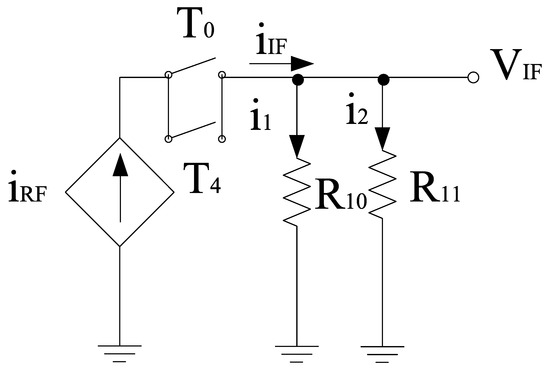

It is well known that the image signal is an unwanted input signal to the mixer. Its frequency will be above or below the local oscillator (LO) frequency by an amount which is equal to the IF frequency. Suppose if fR1 is the frequency of the desired input signal, then fR2 is for its image. Thus, both image and actual input signals mix with the LO and will downconvert to the same frequency. This is problematic for the mixer as both downconverted products interfere with each other as they exit at the IF port together. Thus, by using separate LO stages will overcome this problem and the outputs will be obtained at different IF stages. Based on this phenomenon, two core stages have been developed for the proposed mixer whose outputs will be obtained at different IF stages. The switching stages steered by LO inputs are classified as in-phase (I) and quadrature-phase (Q) stages for image-rejection purposes. Both LO stages contain p-type field effect transistors (FETs) for flicker noise reduction purpose, the transistors T0–T3,T4–T7 are the part of LOQ and LOI stages, respectively. Alternate transistors in each stage form a differential pair and operate alternatively when LO pulse is applied. Hence, differential outputs will be obtained and the current switch between outputs. The output current is directly proportional to the input current and the signal that is applied at the gate terminals. For determining the output voltage, the current flowing through load resistors is considered along with the load resistors itself. In the design, coupling capacitors are used to couple RF and LO stages. The small signal model for obtaining the output voltage with respect to the current obtained from the RF stage is shown in Figure 6. The model uses Kirchoff’s current law (KCL) for analysis. Therefore,

Figure 6.

Equivalent small signal model for LO stage.

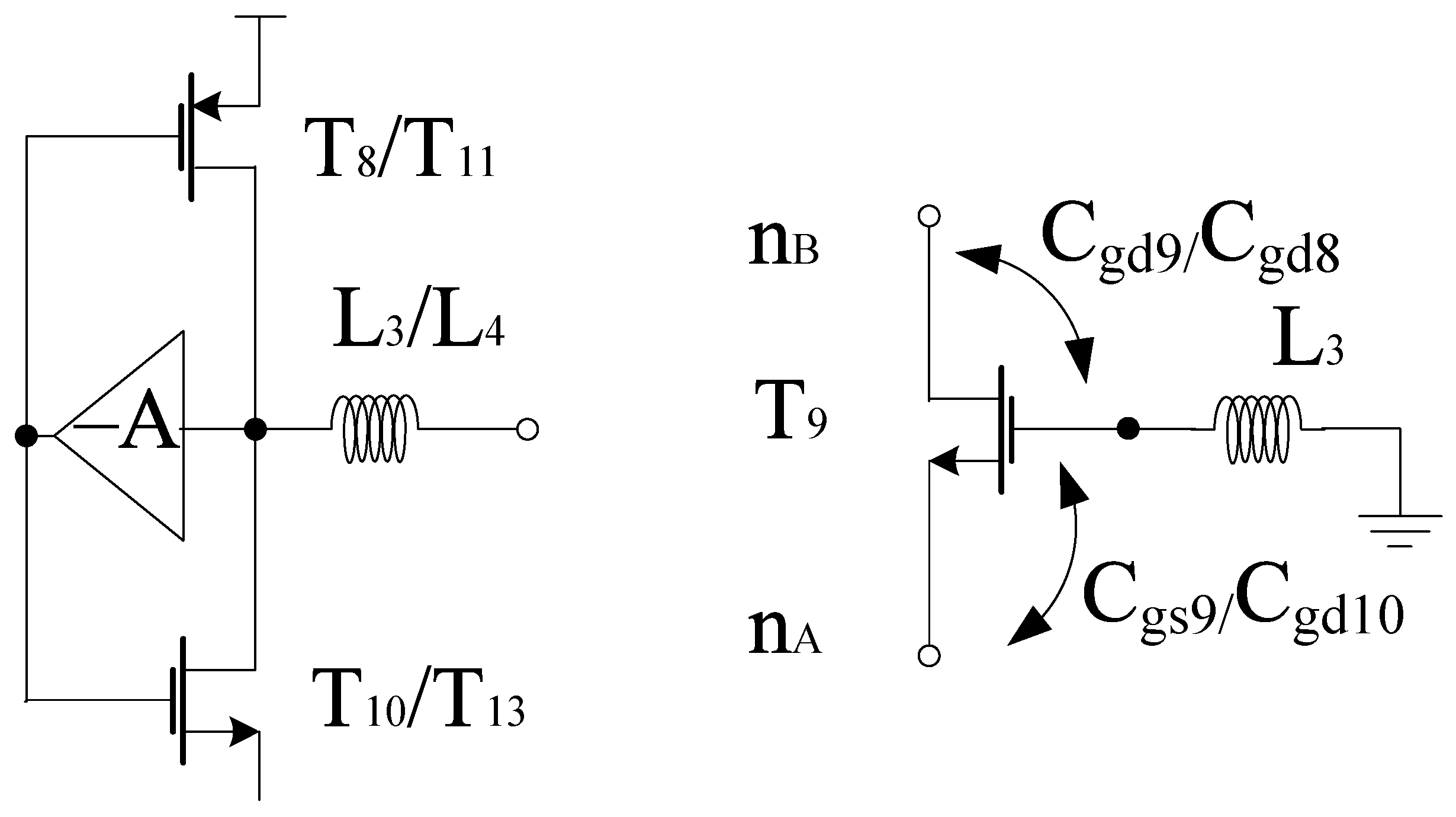

3.3. Gm-Boosting Section

Gm-boosting circuitry is connected to core stages, which is responsible for the transconductance improvement. Hence, the conversion gain will be enhanced while controlling the power consumption [5]. The proposed design employs peaking inductors at the gate of the transistors. These inductors resonate with the parasitic capacitances and are responsible for avoiding current leakage. The design also employs P-type FETs (T8 and T11) connected to Vdd. However, (T9–T12) are N-type FETs. The design follows the stacking structure, where transistors T9 and T12 act as an amplifier that improves gm and overall gain by a factor of (). Transistors T10 and T13 are responsible for delivering the current to the connecting stages. All transistors are operating in the saturation region. The drain current will start flowing in the core stages, the current obtained from this stage will bleed to transconductance stage. Hence, the current will be reused by the transistors T14 and T15, respectively. The equivalent circuit for the gm-boosting stage is shown in Figure 6.

When the transistors T8, T10, T11, and T13 are operating in the saturation region, the current flowing through that stage is given by:

Similarly, for the other section

The LO switches are considered ideal. Therefore, during the positive half of LO pulse, the output current will be positive; during the negative half cycle, the current obtained will be negative. The total current due to the half LOI stage is represented as:

This current is transferred to the LOQ stage, then the current within this stage will be due to LOI and the stage itself

As the coupling capacitors connect the LO stages to the RF stage, the overall boosting can be observed in terms of CG, where the gm stage is acting in parallel with the load at the IF end. Moreover, gm-boosting inductor L3 or L4 present within the design are responsible for gain improvement. The design analysis is explained as per the positive feedback theory whose model is shown in Figure 7 . For using this principle, the T9 signal paths are taken into consideration and output impedance has been ignored for simplicity. Thus, due to presence of L3 or L4 a non-zero impedance can be observed at the gate terminal of T9. The feedforward and feedback paths are considered using parasitic capacitances such as gate-source capacitance (Cgs) and the gate-drain capacitance (Cgd), respectively. Thus, gate-source voltage of T9 becomes Vg,T9 while considering new signal paths. The next step is to calculate the open-loop voltage gain as per voltage-voltage feedback configuration. Hence, the voltage at the drain terminal is expressed as

where Vgs9, gm9 and ZnB refers to the gate to source voltage of T9, transconductance of T9 and output impedance at node nB that includes the duplicate, respectively. where

where Z’nB, , Cgd9 and Cgd8 refer to the output impedance excluding the duplicate, voltage ratio from source to gate, parasitic capacitances for T8 and T9, respectively. Thus, the open-loop gain is represented as

where

Figure 7.

Gm stage model.

Finally, the voltage gain (AV0) without the feedback inductor and the closed-loop voltage gain (AVf) can be expressed as

where

where is the feedback factor from drain to gate Hence, it has been verified from the above equations that the gain has been boosted in the presence of the inductor.

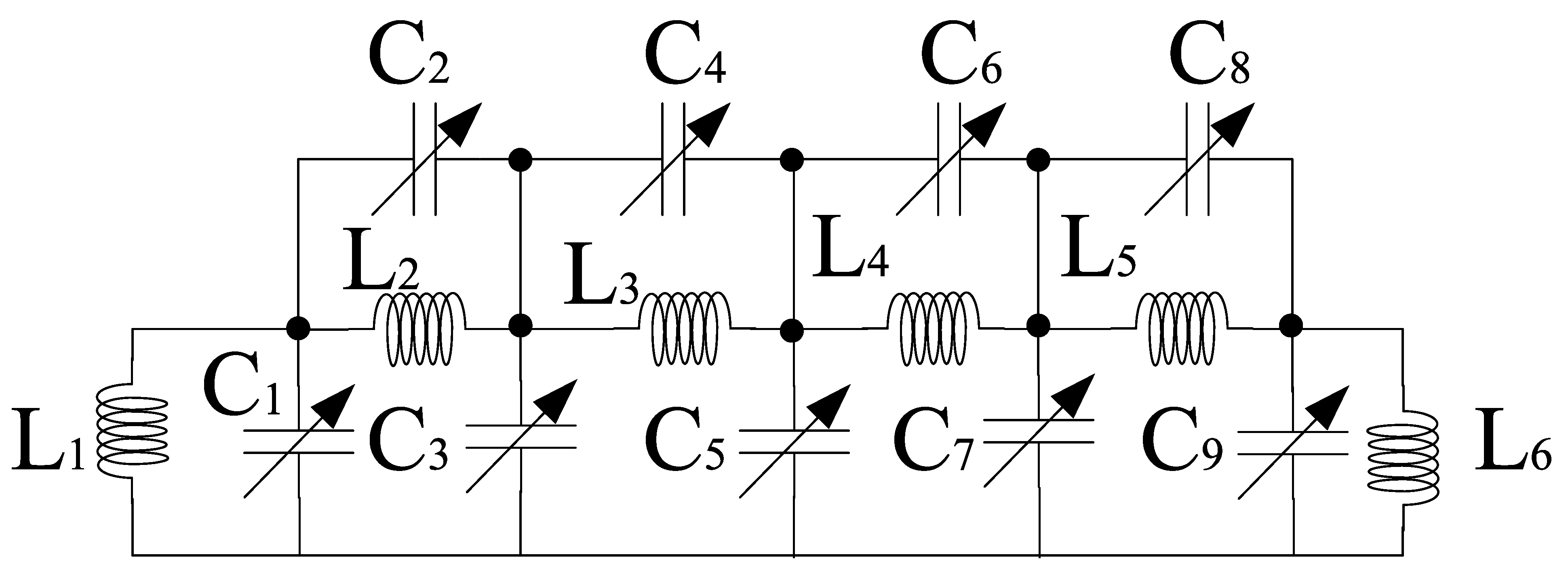

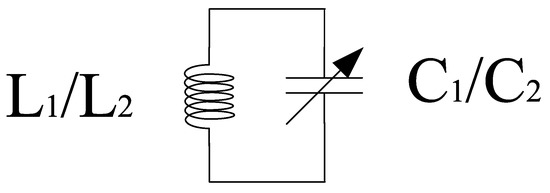

3.4. Filter Section

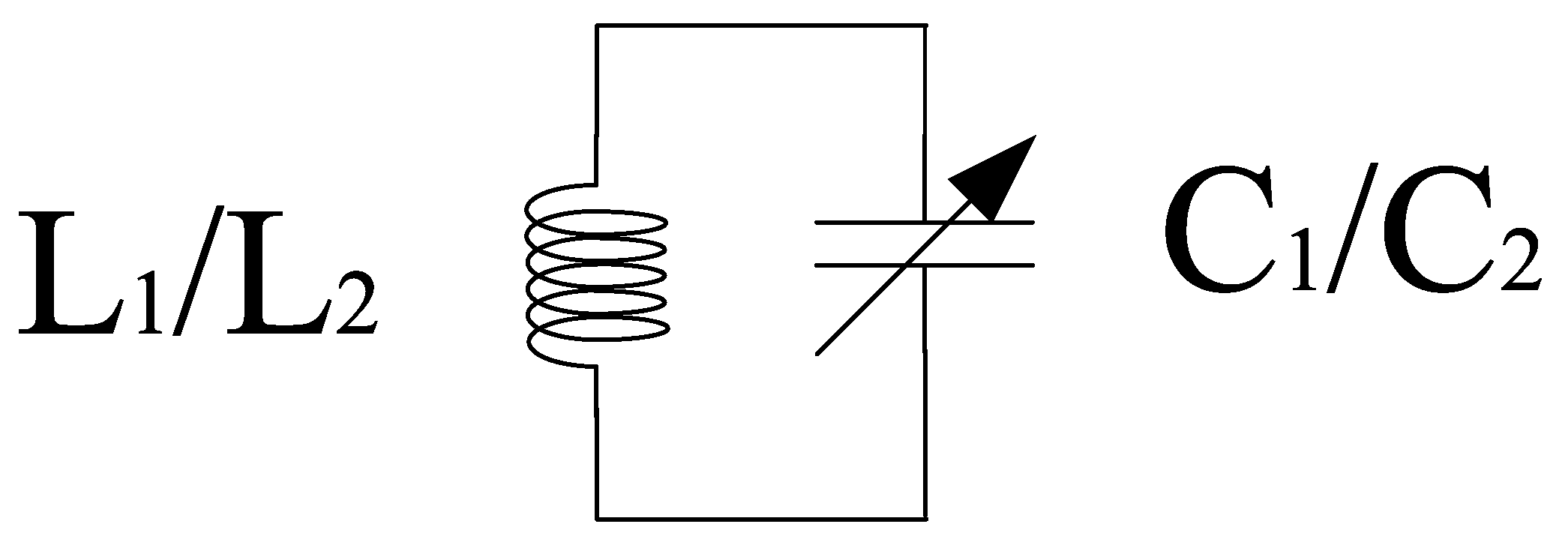

Filters present at the input and output stages are responsible for impedance matching at various frequencies within a band. However, the ones near the core stage prevents signal leakage from the power supply. Various filters have been proposed and the most common techniques are transmission lines, transformer dependent programmable or spiral inductors, and dual-behavior resonator topology [42,43,44,45]. However, these filters are limited to some extent and may cover a large area. Therefore, off-chip filters can be used but easy integration is not possible and they are expensive as well. Hence, the most convenient approach is to develop an image-rejected mixer that employs different filters. We propose ninth-order band pass tunable filters for impedance matching purpose which are present at the RF and IF stages of the mixer as shown in Figure 8. Moreover, Figure 9 shows the design of first-order bandpass filter present at the source terminals of the LOI stage transistors at one end and the power supply at the other end to avoid leakage from the power supply.

Figure 8.

Ninth-order filter.

Figure 9.

First-order filter.

The input and output impedance of the ninth-order filter section can be expressed as a combination of series and parallel LC sections within the design. The filter order depends on the number of LC pairs. The input impedance, Zin is expressed as:

For simplicity, different letters have been used to represent the LC combinations. The output impedance, Zout is expressed as:

Similarly, the first-order impedance depends on the parallel combination of L and C.

The resonant frequency at which the impedance, ZP will be real can be defined as

or

where ZP refers to the parallel circuit impedance. The resonant frequency varies depending on the selected filter circuit within the design.

4. Mixer Design Analysis

Figure 4 shows the complete structure of the designed mixer with gm-boosting, common source configured transconductance stage and Gilbert cell core stage. The first step is to determine the band of operation. The next step is choosing the design topology and filters for successful reconfiguration. The design uses Gilbert topology responsible for improving the overall CG, NF. To further enhance this performance, gm-boosting with inductive peaking is employed. The design is structured to provide good image rejection as well without affecting performance of the design.

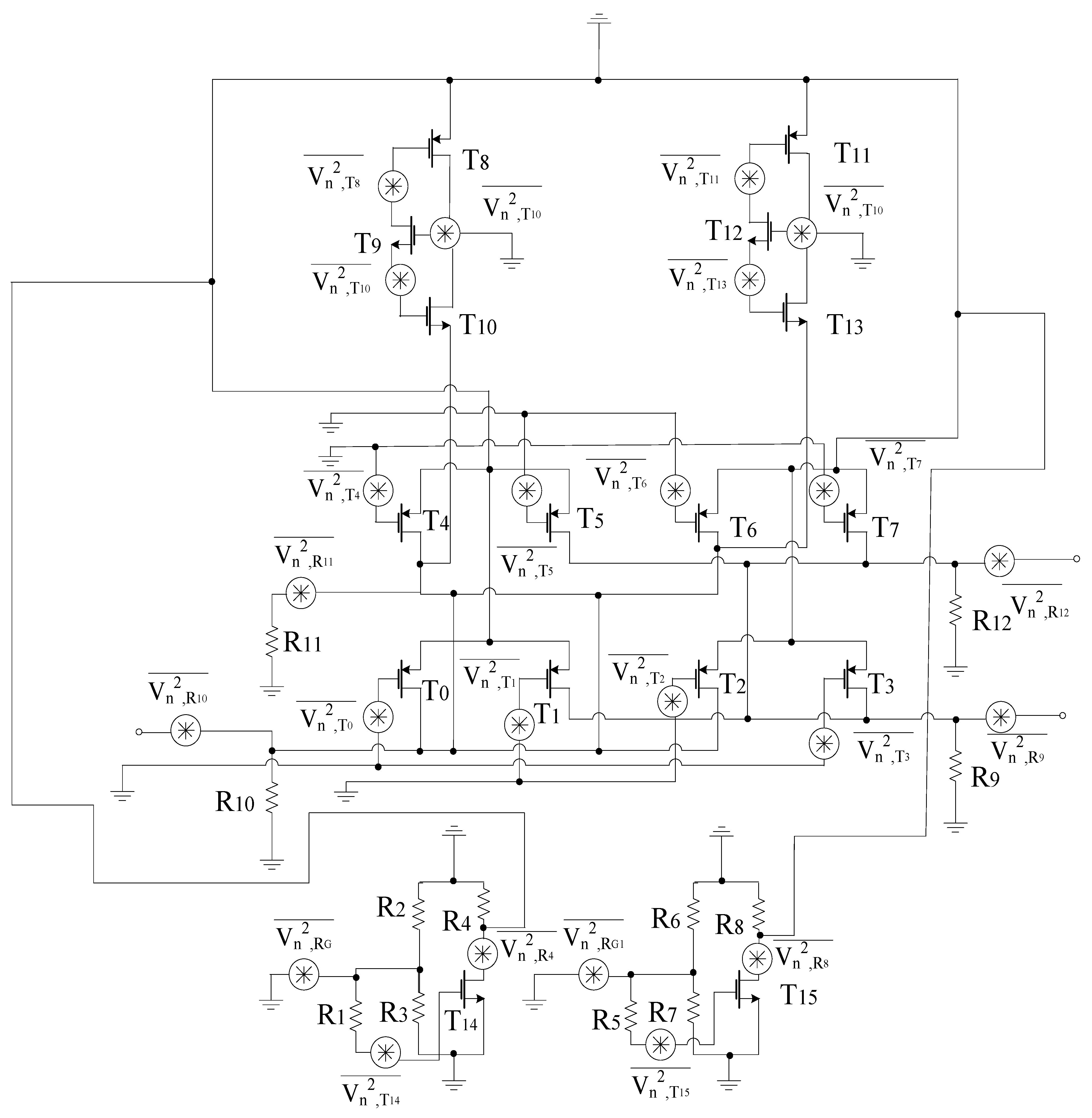

4.1. Conversion Gain

Figure 10 shows the complete small signal model used for obtaining the overall CG within the design. The CG, Av is represented by the expression below:

where all expressions in Equation (55) are obtained using the small signal model except iIF(sIF)/iRF(sRF) which can be obtained using Fourier series analysis by approximating LO signal just like a square wave.

Figure 10.

Complete small signal model.

For determining iRF(sRF)/Vgs14(sRF) ratio KCL is applied, and we obtain the expression below:

Rearranging the above equation, we get;

By substituting (56)–(61) into (55), the overall CG can be obtained.

4.2. Noise Figure

Figure 11 shows the noise model for the proposed circuit. In the circuitry, all passive elements are considered ideal, and the most important noise source is thermal noise, based on which the power spectral density of each stage is obtained. The design consists of resistors and transistors, respectively [41,46].

Figure 11.

Proposed mixer noise model.

Equation (62) defines the power spectral density, which is the combination of the power spectral density obtained from all stages present within the design.

The power spectral density for all stages is obtained based on the resistors and transistors present within each stage. Thus, the power spectral density for the RF+ stage is expressed as

Likewise, the power spectral density for RF- stage is defined below

Moreover, the power spectral densities for LOI and LOQ stages are expressed as

Finally, the power spectral densities for GM stages are expressed as

Hence, the noise figure of the proposed mixer is expressed as

Moreover, for analyzing the high-frequency noise in the proposed mixer, the thermal noise due to resistors, the thermal noise due to drain, and gate of FETs are considered [47]. The noise contribution due to RF, LOI, LOQ and output stages are considered for the proposed mixer.

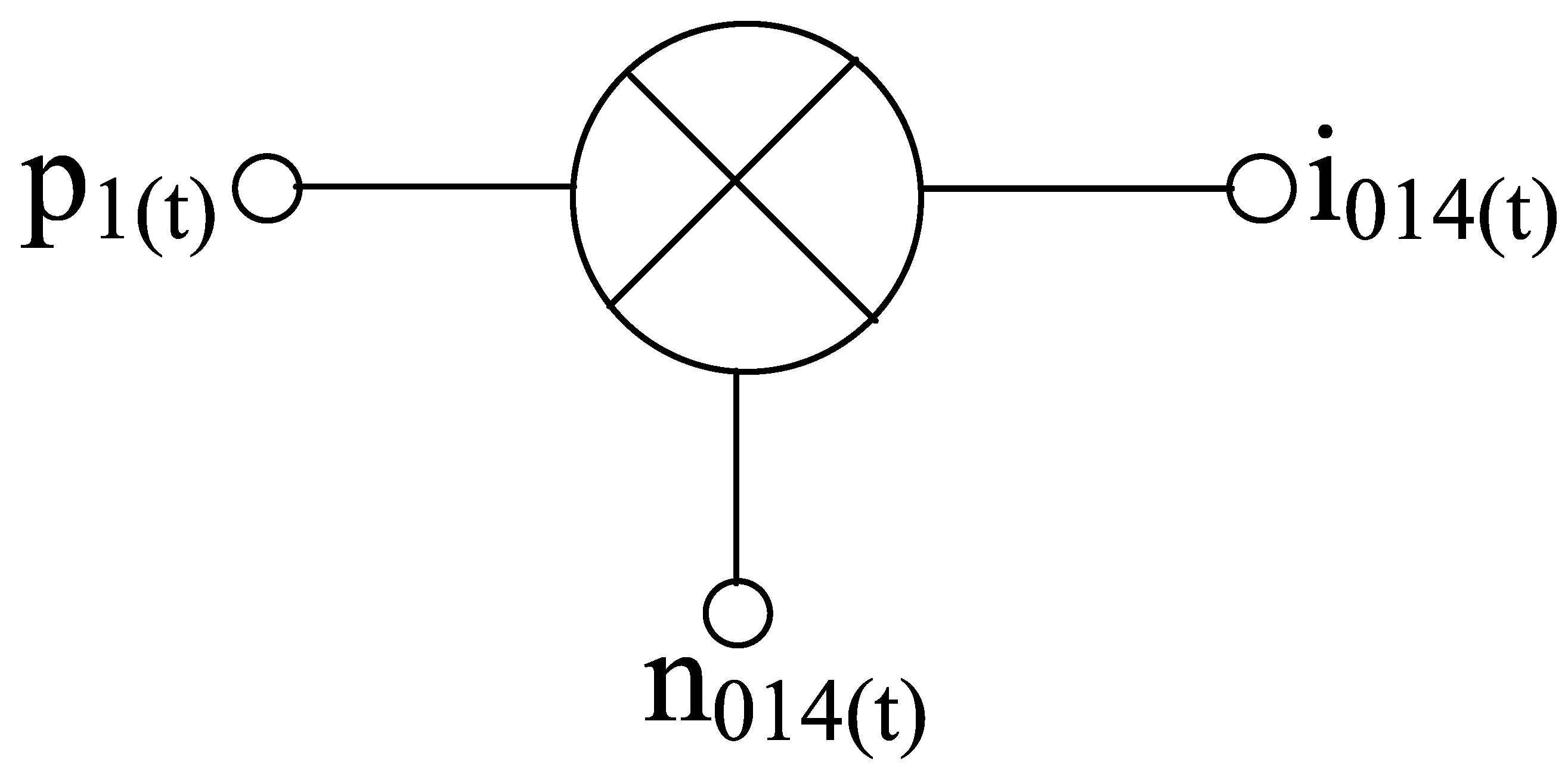

Starting with the noise contribution from the RF stage as per Figure 12, the noise signal at the output of the transconductor when multiplied with the switching pair’s instantaneous current gain p1(t) results in a current noise , io14(t) as

Figure 12.

Mixer operation for transconductance noise.

By considering the above process as a time-average wide sense stationary process, the power spectral density of the noise current is expressed as

For the overall analysis of power spectral density at the RF stage, both correlated and uncorrelated power spectral density factors have to be considered. Thus, the uncorrelated power spectral density is expressed as

where RG014, rg014 refer to the external gate resistance (parallel combination of the resistors) and internal gate resistance.

Likewise, the correlated power spectral density can be expressed as

Thus, the overall power spectral density is expressed as

Next, the power spectral density due to LO stages is expressed as

Considering the noise present at LO ports are stationary. Thus, time-averaged power spectral density of current noise at the output of the proposed mixer due to LO stages is expressed as

where RLOI, RLOQ refer to equivalent noise resistances and rG1, rG2 refer to poly gate resistances. As the image signal does not carry any important information, therefore the single sideband noise figure is considered over the double sideband noise figure as

The above expression is defined for a single balanced mixer. Similarly, for the double balanced mixer, NF can also be defined which is almost twice the one obtained for a single balanced mixer.

5. Results and Discussion

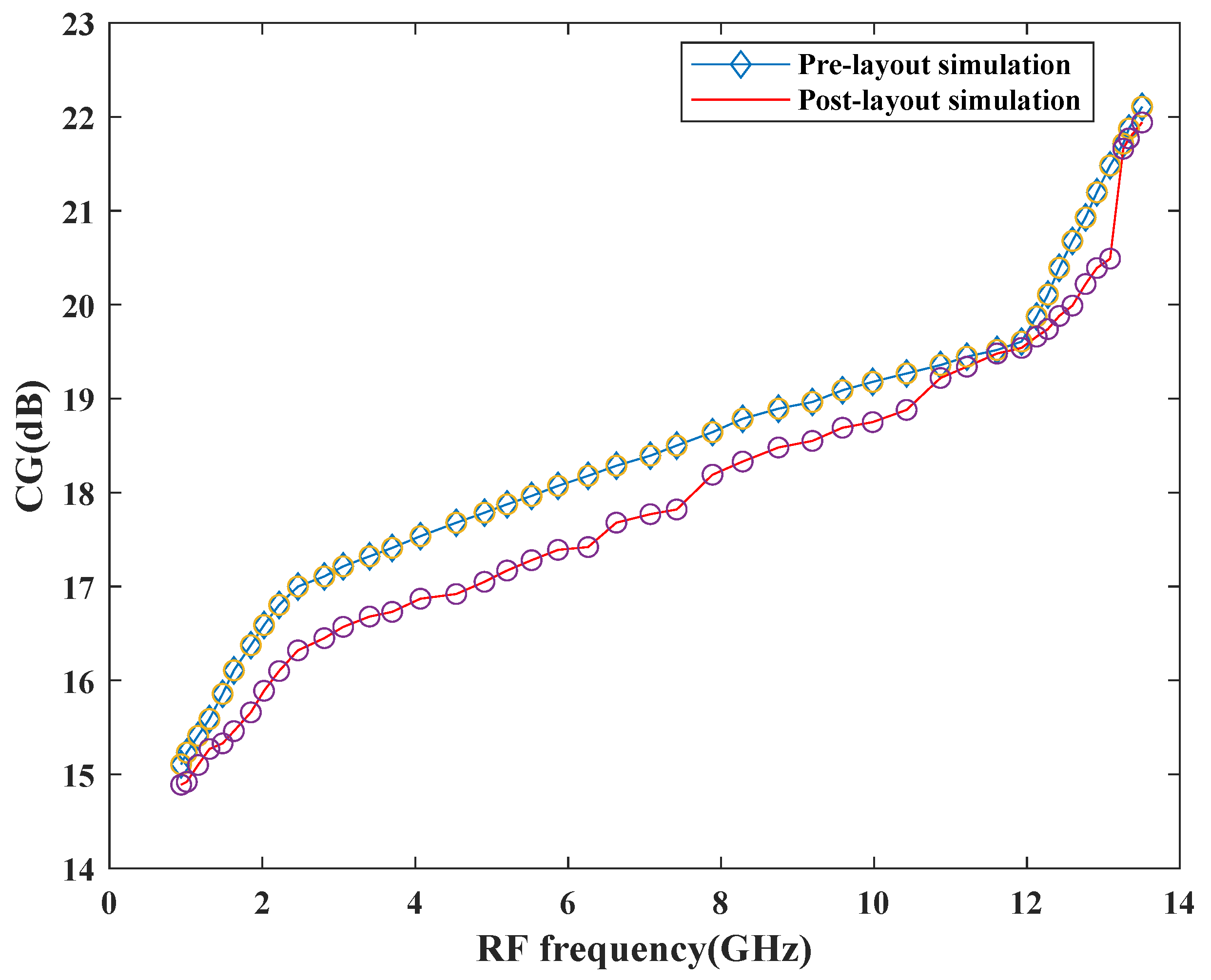

The proposed mixer is designed and simulated in the SiGe 8HP process technology. To boost the transconductance within the RF stage, gm-boosting technique has been used in the design, which leads to good CG performance. Figure 13 shows the pre-and post-layout simulation results for the conversion gain performance of the proposed mixer. As depicted in Figure 13, the CGmin and CGmax values are quite similar for both simulations. However, variation can be observed at other frequencies within a band that can be discussed by considering the parasitic effects. The pre-layout CG at the center frequency, 7 GHz is 18.39 dB and after layout, it degrades to 17.7 dB. Due to the parasitic effects of passive components within the circuitry, the CG degrades after the final layout. In particular, the quality factors of the inductors within the circuitry are responsible for the gain performance degradation. Moreover, the parasitic resistance within the inductors can also lower the voltage gain within the circuitry.

Figure 13.

Variation of CG versus frequency.

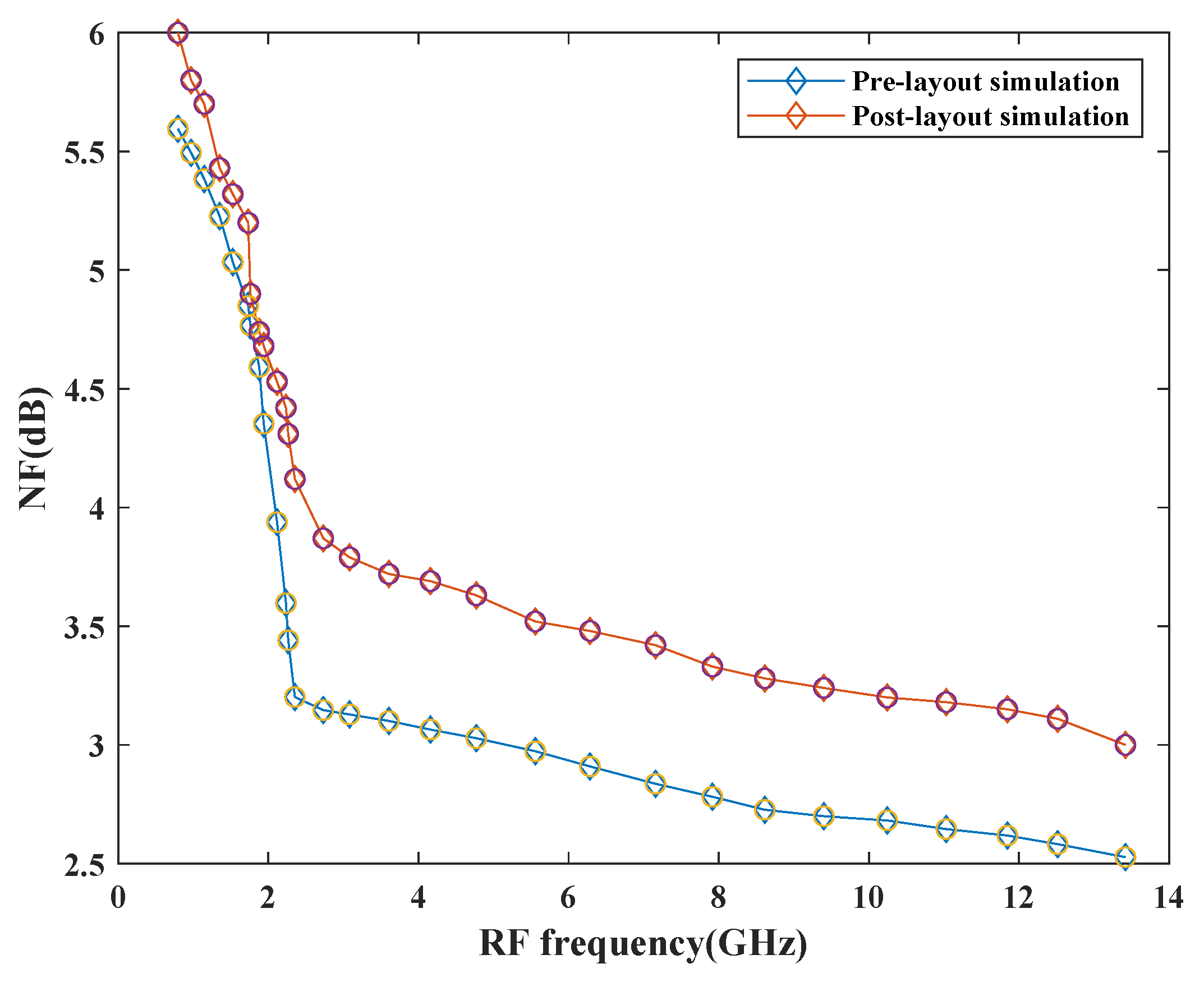

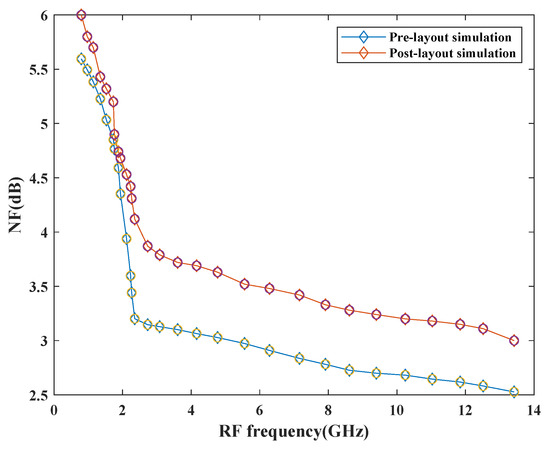

Figure 14 depicts the NF of the mixer with the variation in frequency. The simulation results show that NF is less than 3 dB before pre-layout simulation and raised by 0.8 dB upon post-layout simulation at the maximum frequency. This performance has also been affected by the parasitic effects of passive components. It also has dependency on the number of resistive components, transistors, and conversion gain performance of the design. This mixer exhibits good NF with a variation of dB across the entire frequency range.

Figure 14.

Variation of NF with RF frequency.

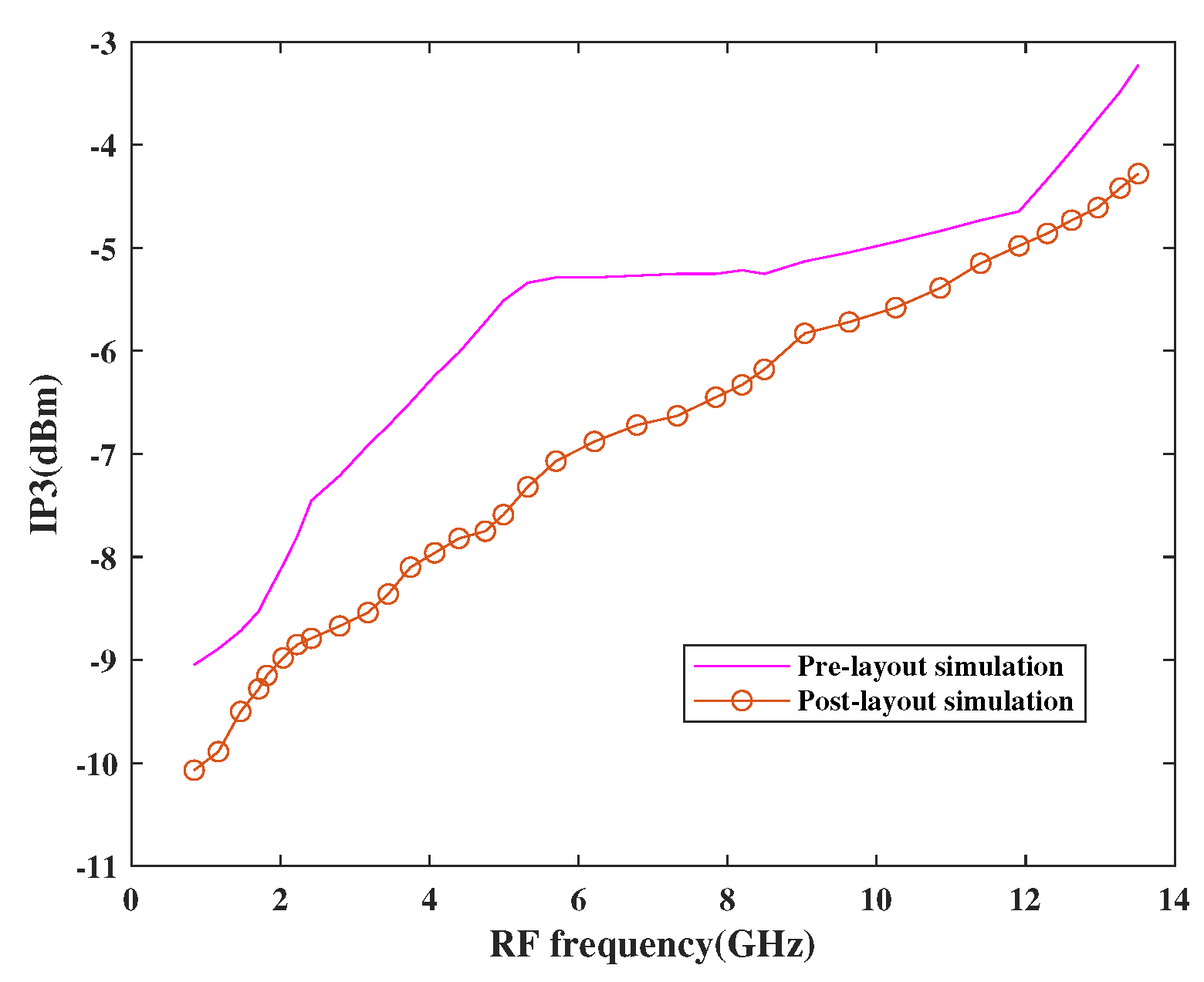

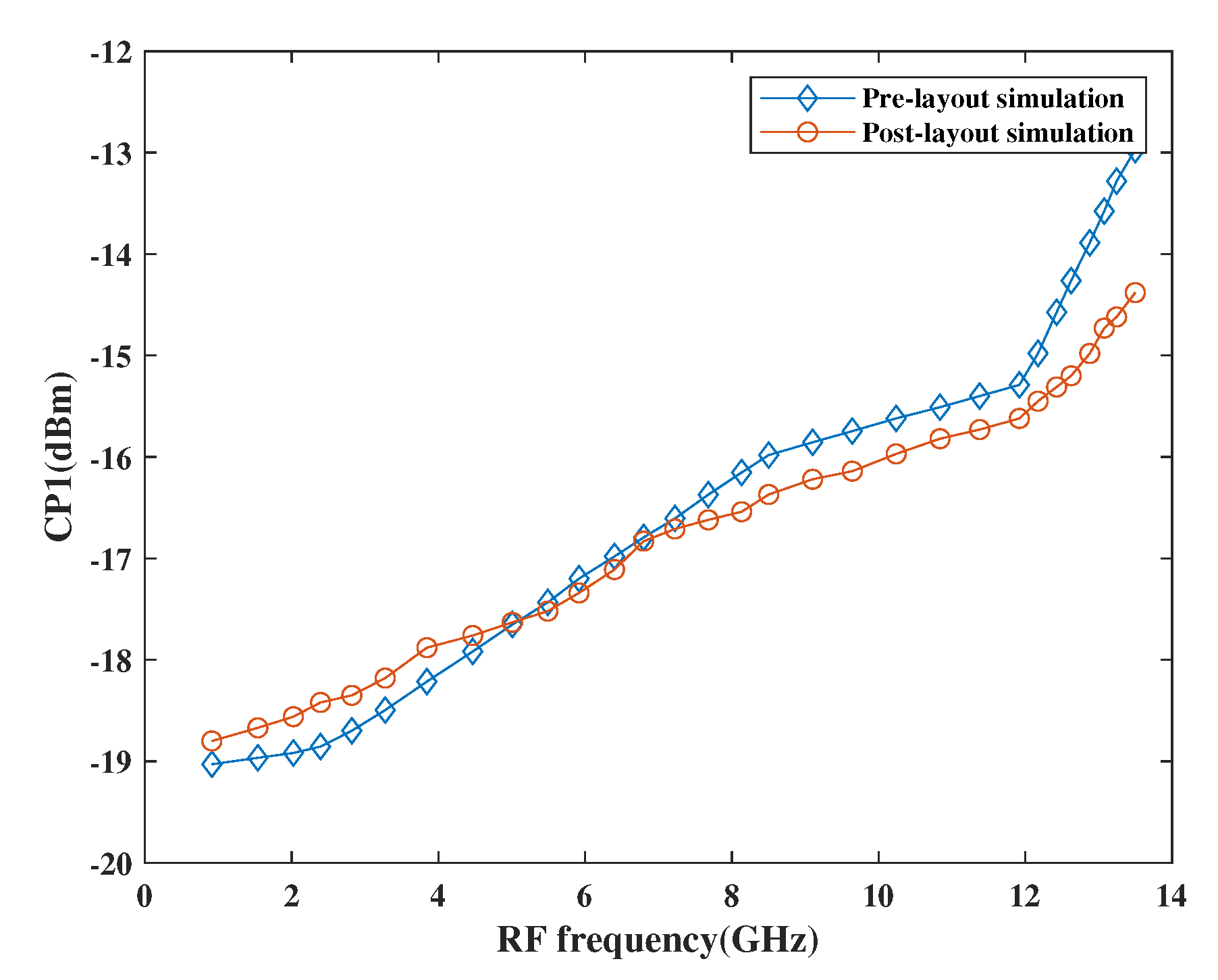

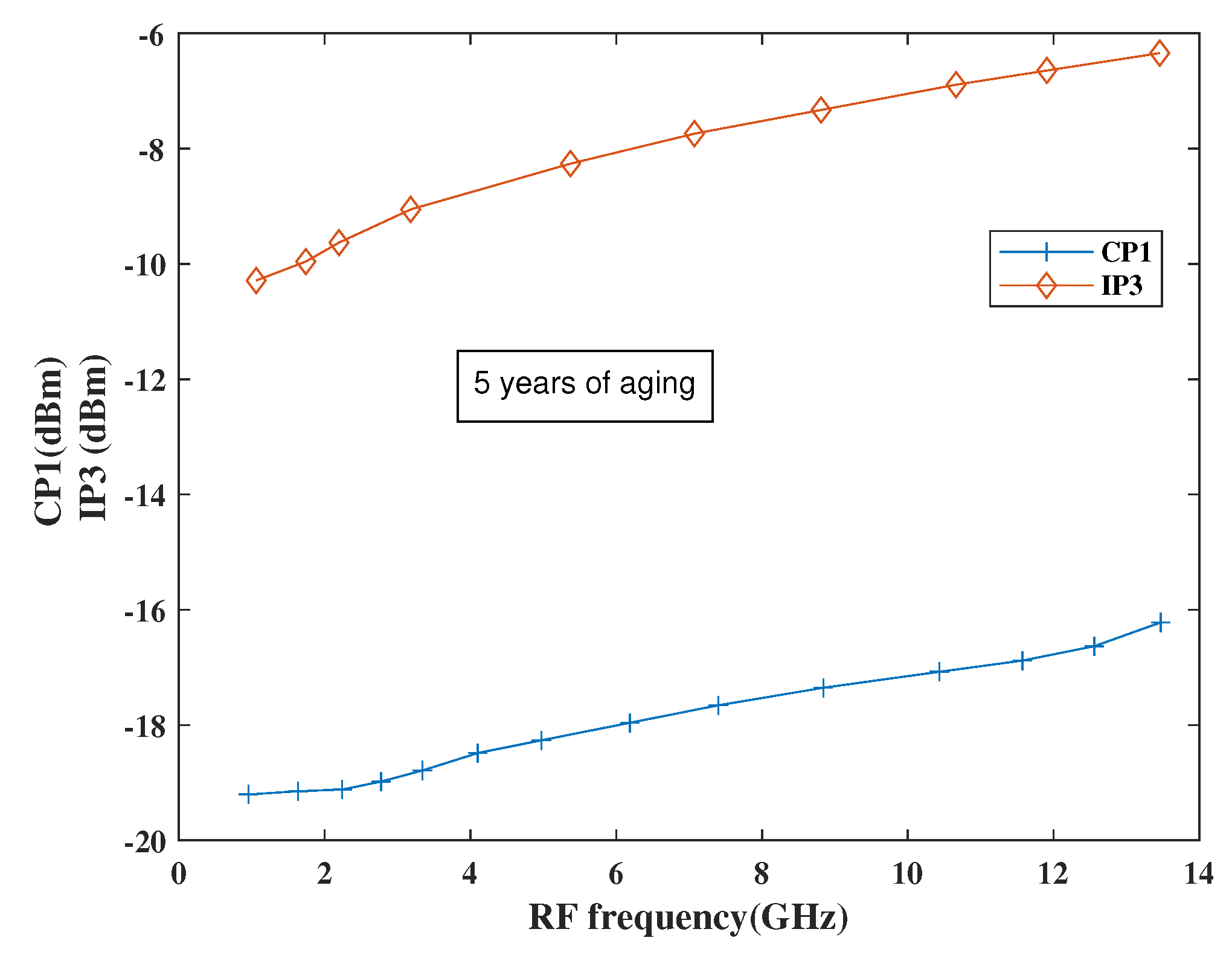

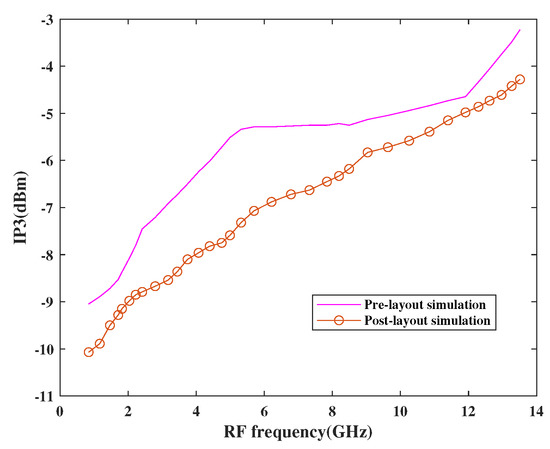

The linearity performance of the mixer has been shown in Figure 15 and Figure 16, respectively. The design is considered linear if it shows proportional behavior within the input and output. This behavior can be observed using third-order input intercept points (IP3) and 1dB compression point (CP1). The actual behavior of the mixer is well depicted in terms of pre-and post-layout simulation results. As per the simulation results, it has been observed that the design attained moderate linearity behavior when observed at different frequencies in a band where IP3 is 10 dBm higher than CP1.

Figure 15.

Variation of IP3 with RF frequency.

Figure 16.

Variation of CP1 with RF frequency.

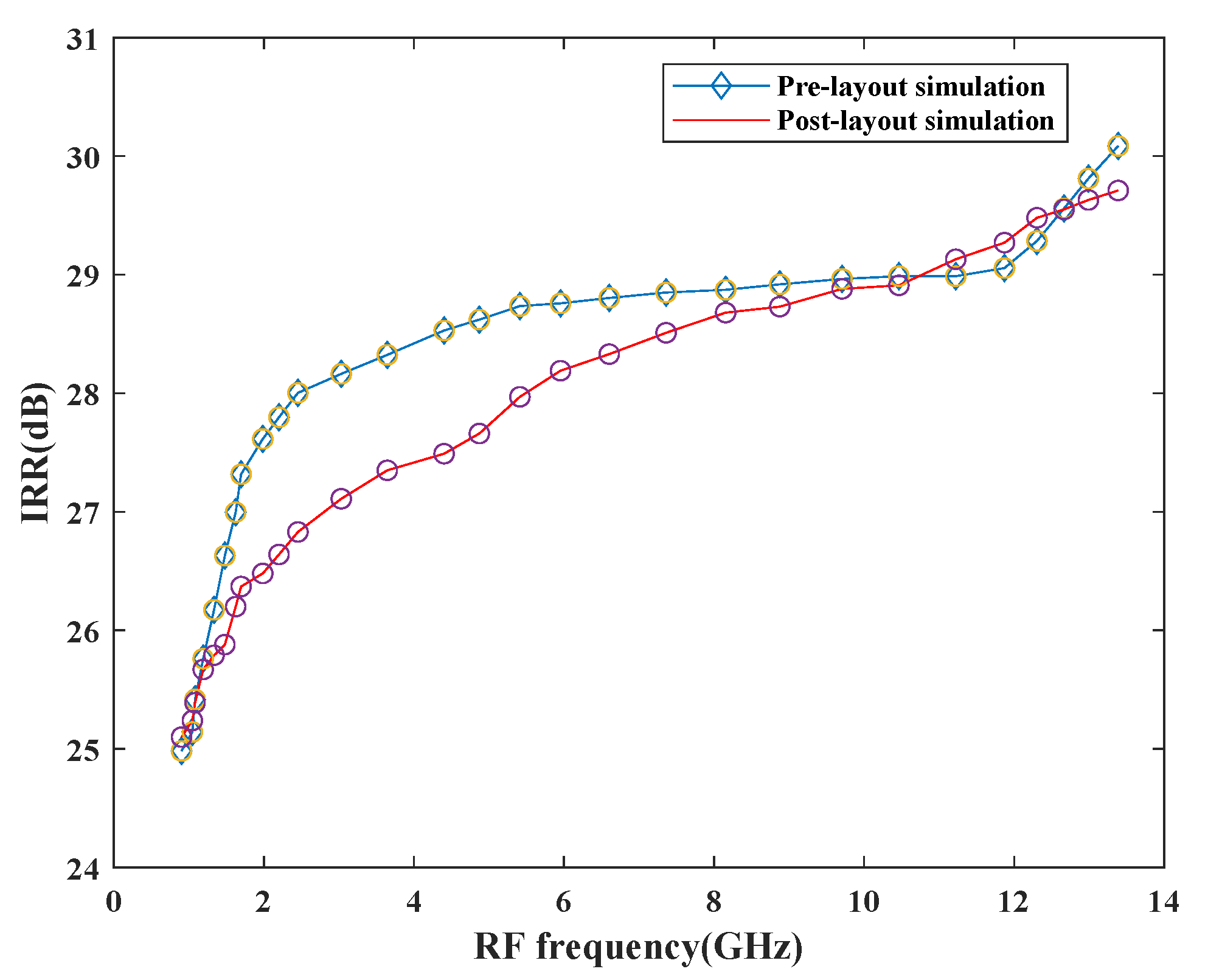

The image-rejection ratio is an important aspect while designing the mixer as depicted in Figure 17. When desired and image signals enter the input together, it degrades the overall performance of the circuitry and waste power. Therefore, to overcome this problem, the image signal must be rejected which is done in the proposed design. The mixer attains a good IRR of 28.91 dB at 10.46 GHz upon performing pre- and post-layout simulations. The maximum IRR is around 30 dB, which is within the normal specified IRR range of 20–40 dB.

Figure 17.

Variation of IRR with RF frequency.

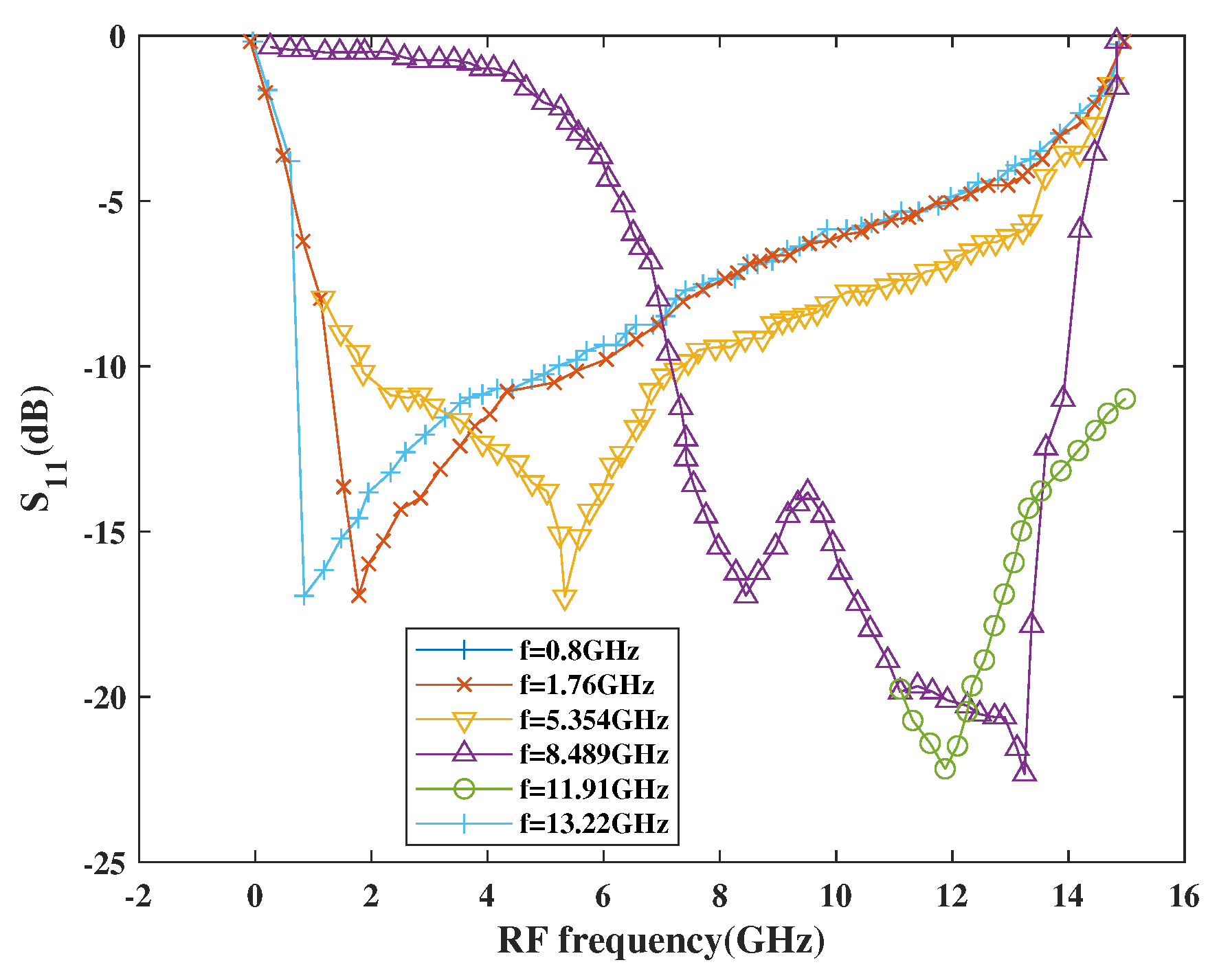

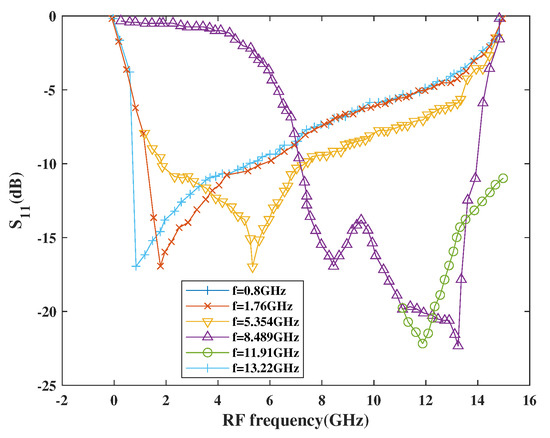

Figure 18 shows the return loss performance with respect to frequency. As per simulation results, the |S11| is below 10 dB at each centered frequency for the entire tuning band, which is as low as −22.42 dB at 11.91 GHz and 13.22 GHz, respectively.

Figure 18.

Variation of S11 with RF frequency.

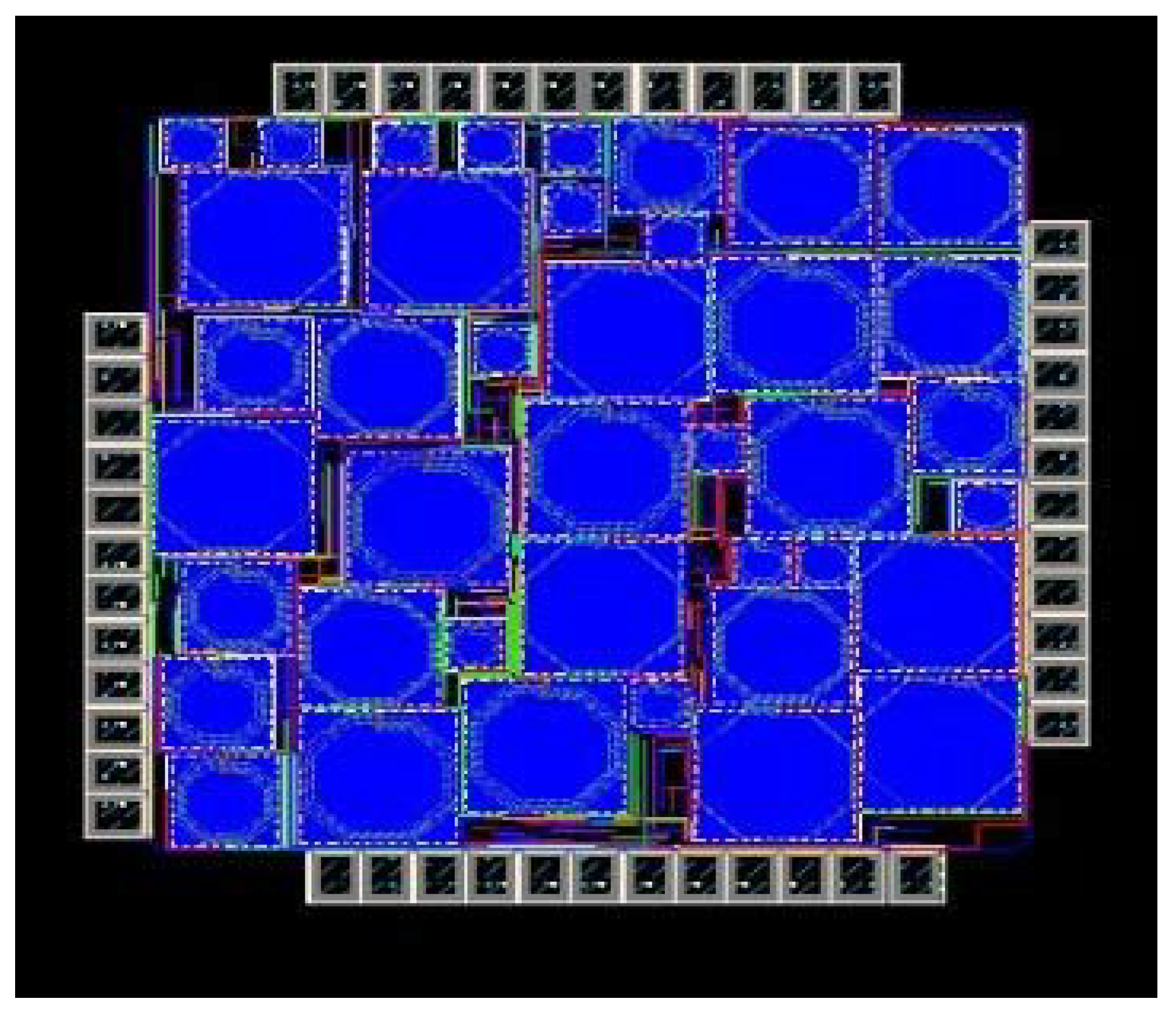

Figure 19 shows the layout of the proposed mixer designed in 8 HP process technology covering around 1.98 mm2 area. The design consists of different sections as discussed in detail in Section 3. The filter section consists of spiral inductors and capacitors. Inductors used provide accurate inductance values and are capable of achieving the maximum Q at a desired operating frequency. Additionally, variable capacitors, i.e., varactors, are used to attain the tuning capacitance.

Figure 19.

Designed Mixer Layout.

Table 1 summarizes the performance of the proposed mixer and provides a comparison of the circuit with the recent works. As per Table 1, the achievable NF is as less as 2.5 dB and the maximum S11 is −20 dB. As CG increases, the IP3 gets degraded due to CG-IP3 trade-off. Moreover, the maximum IRR is 36 dB. The overall area of the proposed mixer is higher than the other reported designs. However, the design attains high performance in terms of CG, NF, IRR and S11 simultaneously at the expense of IP3 which is the best among all reported works in the literature.

Table 1.

Performance Comparison Summary.

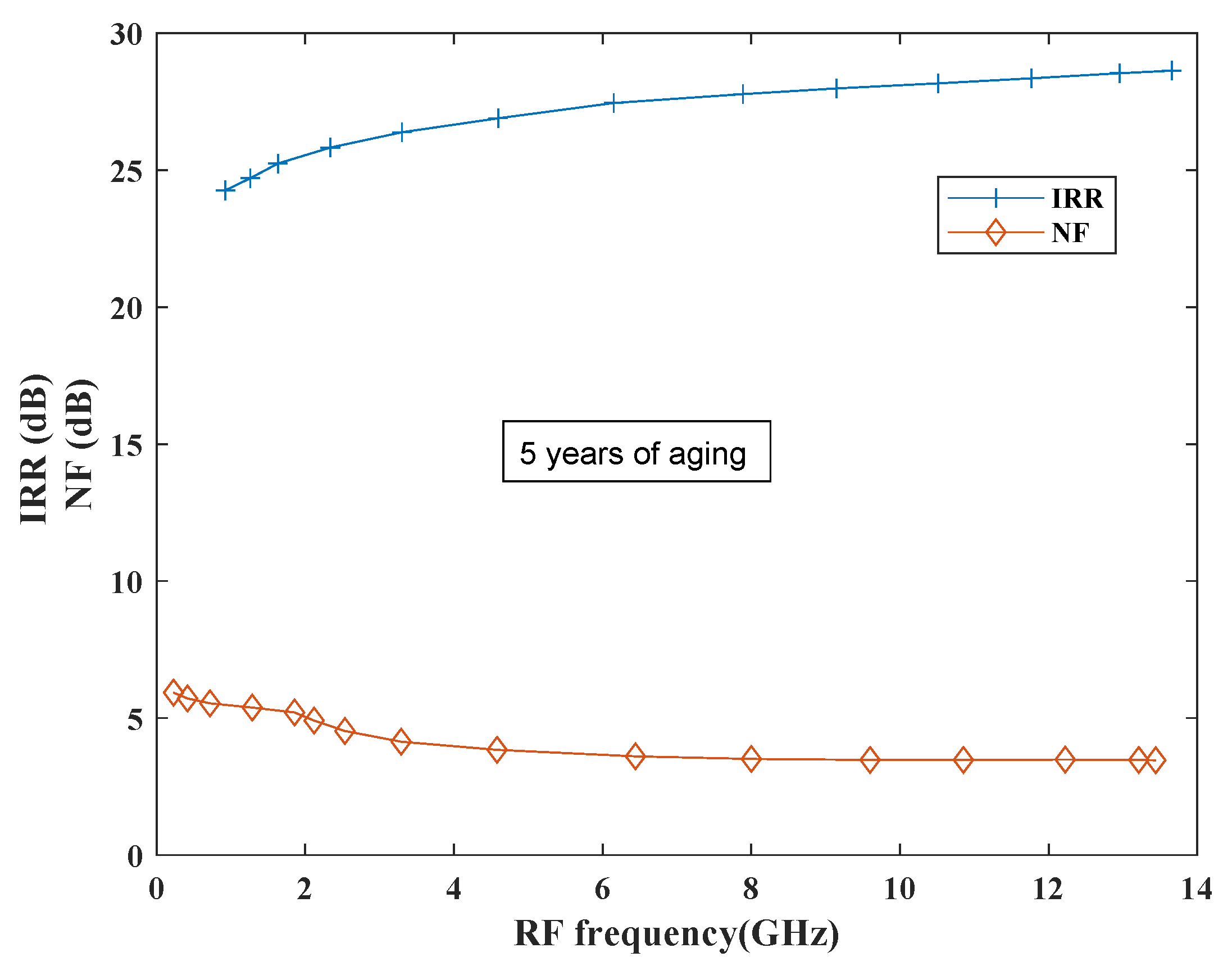

6. Design Reliability

Conventional designs were less focused on reliability analysis due to the process and design guide limitations. However, in recent years it is important to consider reliability of the designs due to time, budget, scaling and demanding profile constraints. Relxpert tool developed by Cadence is used to simulate PFET and NFET devices for determining the device degradation performance where performance is evaluated as a function of stress time and biases. Relexpert output can be observed as a “corner in time” that moves towards slow corners in case of simulation from a typical corner. This process helps the designers in analyzing the degradation in circuit behavior during the initial design flow stages [58]. Degradation performance has been evaluated in terms of all performance parameters such as CG, CP1, IP3, NF and IRR ratio. Figure 20 shows the performance of the proposed mixer in terms of IRR and NF with 5 years of aging. From the plots it has been observed that both IRR and NF show degradation; however, more degradation can be observed in NF in comparison to IRR.

Figure 20.

IRR and NF degradation performance.

Figure 21 shows the performance of the proposed mixer in terms of linearity parameters and it has been found that the linearity will degrade as expected as such variation is observed after post-layout simulation results as well. However, the NF is still ≤ 5 dB within the entire band, which is expected for a mixer.

Figure 21.

CP1 and IP3 degradation performance.

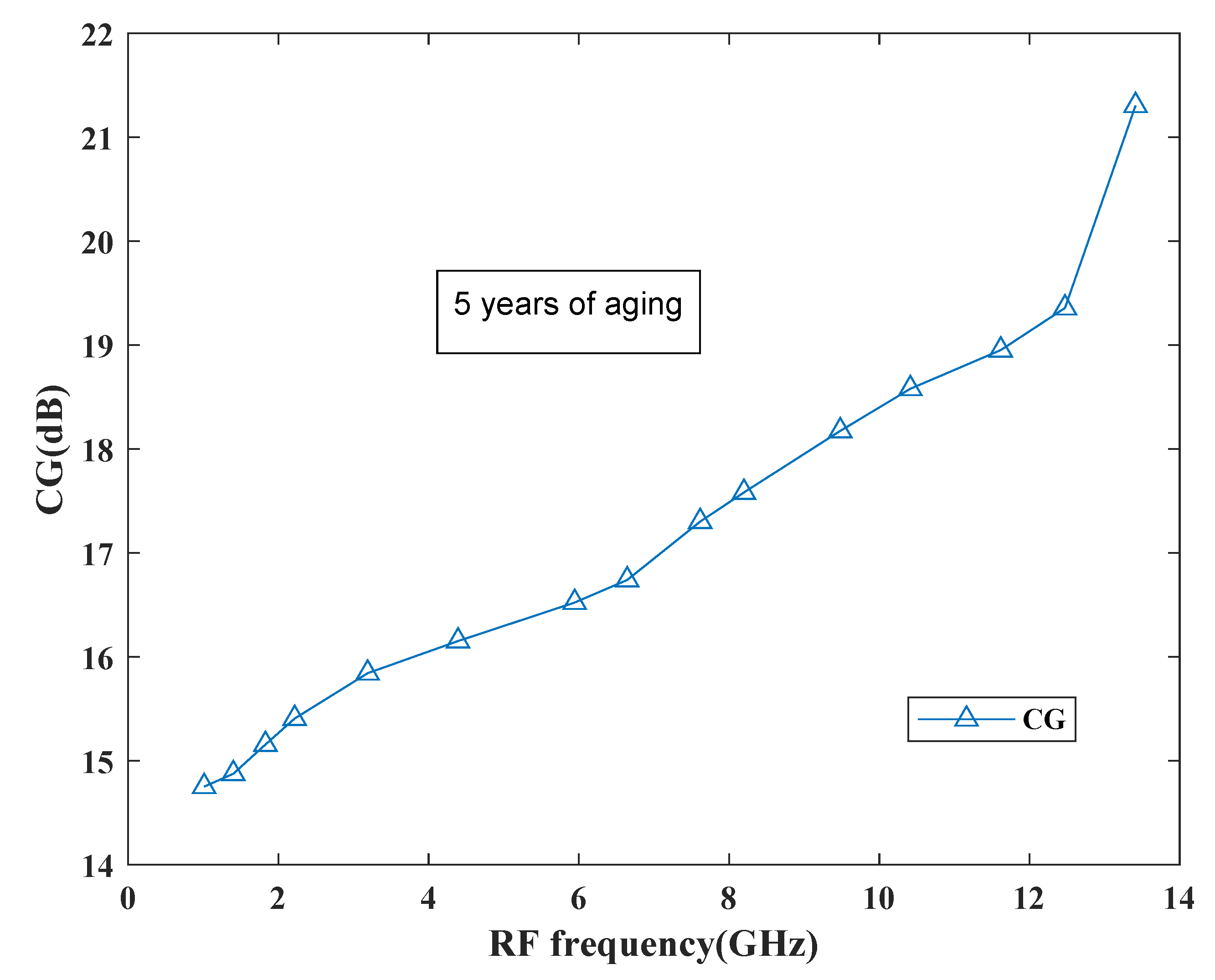

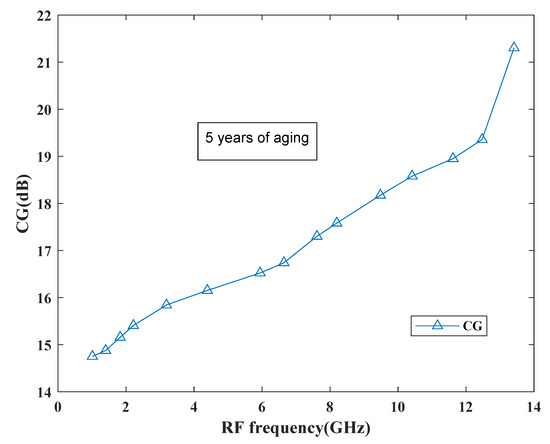

The behavior of the gain can be observed from Figure 22 which shows the performance of the proposed mixer in terms of gain. Based on the curve, it has been found that the gain degradation is very less as it reaches to 21.5 dB after 5 years and at present it is around 22.1 dB. Thus, the proposed mixer is reliable for future SDR applications.

Figure 22.

CG degradation performance.

7. Conclusions

In this paper, a novel reconfigurable I/Q Gilbert mixer has been proposed, which is designed and simulated in SiGe 8HP process technology. ninth-order tunable LC filters are embedded at the RF and IF ports for port matching and NF improvement. Moreover, a first-order tunable filter is employed to avoid the leakage through the power supply. The proposed design shows improved transconductance by using Gm-boosting technique. Additionally, the employment of peaking inductors compensates for the gain reduction at high frequencies, while extending the overall bandwidth and hence results in a high gain. Based on the simulation results, with a 1.2 V power supply, the design attains a maximum gain of 22.1 dB. The input return loss is <−10 dB and achieves a minimum of −22.7 dB at 11.9 GHz and 13.22 GHz, respectively. Furthermore, NF ranges between 2.5 and 5.6 dB. The design also shows good IRR within the entire band. Thus, the proposed mixer is compatible enough to meet the future demands of software-defined radios.

Author Contributions

Supervision, X.-J.L. and M.D.; Conceptualization, S.M. and X.-J.L.; methodology, S.M. and X.-J.L.; software, X.-J.L.; validation, S.M., X.-J.L.; formal analysis, X.-J.L.; investigation, S.M.; resources, X.-J.L.; data curation, S.M.; writing—original draft preparation, S.M. and X.-J.L.; writing—review and editing, S.M., X.-J.L. and M.D.; visualization, S.M., X.-J.L.; project administration, X.-J.L. All authors have read and agreed to the published version of the manuscript.

Funding

This research received no external funding.

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

Not applicable.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Brandolini, M.; Rossi, P.; Manstretta, D.; Svelto, F. Toward multistandard mobile terminals - fully integrated receivers requirements and architectures. IEEE Trans. Microw. Theory Tech. 2005, 53, 1026–1038. [Google Scholar] [CrossRef]

- Karanicolas, A.N. A 2.7 V 900 MHz CMOS LNA and mixer. In Proceedings of the 1996 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 10 February 1996; pp. 50–51. [Google Scholar]

- Vahidfar, M.B.; Shoaei, O.; Svelto, F. A high dynamic range multi-standard CMOS mixer for GSM, UMTS and IEEE802.11b-g-a applications. In Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium, Atlanta, GA, USA, 15–17 June 2008; pp. 193–196. [Google Scholar]

- Bao, K.; Fan, X.; Li, W.; Wang, Z. A wideband current-commutating passive mixer for multi-standard receivers in a 0.18 um CMOS. J. Semicond. 2013, 34, 1–3. [Google Scholar] [CrossRef]

- Wu, C.; Lin, Y. Design of down-conversion mixer with gm-boosted stage combining low phase noise oscillator. In Proceedings of the International Symposium on Signals, Systems and Electronics, Nanjing, China, 17–20 September 2010; Volume 2, pp. 1–4. [Google Scholar]

- Kim, C.; Jang, Y.K.; Yoo, H.J. System Level Design of Multi-standard Receiver Using Reconfigurable RF Block. J. Semicond. Technol. Sci. 2004, 4, 174–181. [Google Scholar]

- Akeela, R.; Dezfouli, B. Software-defined Radios: Architecture, state-of-the-art, and challenges. Comput. Commun. 2018, 128, 106–125. [Google Scholar] [CrossRef]

- Chen, Y.; Yan, N.; Xu, J.; Chen, Q.; Sun, J. Low power, high linearity multi-mode downconversion mixer for SDR. In Proceedings of the 2013 IEEE International Symposium on Circuits and Systems, Beijing, China, 19–23 May 2013; pp. 737–740. [Google Scholar]

- Liu, X.; Zhang, X. Multiband Spectrum Access: Great Promises for Future Cognitive Radio Networks. IEEE Trans. Ind. Inform. 2020, 16, 5379–5388. [Google Scholar] [CrossRef]

- Kalathil, D.M.; Jain, R. Spectrum Sharing through Contracts for Cognitive Radios. IEEE Trans. Mob. Comput. 2013, 12, 1999–2011. [Google Scholar] [CrossRef]

- Hattab, G.; Ibnkahla, M. Multiband Spectrum Access: Great Promises for Future Cognitive Radio Networks. Proc. IEEE 2014, 102, 282–306. [Google Scholar] [CrossRef]

- Djoumessi, E.E.; Wu, K. White Space Communication Technologies; Cambridge University Press: Cambridge, UK, 2014. [Google Scholar]

- Davis, M.; Davis, C. Sampling Mixer for Software Defined Radio Applications using 0.18 um RF CMOS Technology. Undergraduate Thesis, Department of Electrical and Computer Engineering, Virginia Polytechnic Institute and State University, Blacksburg, VA, USA, 2013. [Google Scholar]

- Asad, B.Z.J. Low-Noise 24 GHz 0.15 um GaAs pHEMT Gilbert Cell Mixer for Intelligent Transportation System Radar Receiver. Master of Applied Science Thesis, Ottawa-Carleton Institute for Electrical and Computer Engineering, Electrical and Computer Engineering, Ottawa, ON, Canada, 2014. [Google Scholar]

- Zumbahlen, H. Linear Circuit Design Handbook; Newnes/Elsevier: Wilmington, MA, USA, 2008. [Google Scholar]

- Siddiqi, A.A. Design Methodology and investigation of GHz range CMOS RF mixers. Master of Engineering Thesis, Carleton University, Ottawa, ON, Canada, 2000. [Google Scholar]

- Arun, J.; Ezra, K.; Nithin, M.; Ravi, S. Design and Analysis of Double Balanced Gilbert Cell CMOS Mixer for Heterodyne receivers. Int. J. Appl. Eng. Res. 2013, 8, 2413–2416. [Google Scholar]

- Hu, X. RF CMOS Tunable Gilbert Mixer with Wide Tuning Frequency and Controllable Bandwidth: Design Sythesis and Verification. Master of Science Thesis, Department of Electrical Engineering, Wright State University, Dayton, OH, USA, 2017. [Google Scholar]

- Piccinni, G.; Avitabile, G.; Coviello, G.; Talarico, C. Gilbert cell mixer design based on a novel systematic approach for nanoscale technologies. In Proceedings of the 2017 IEEE 18th Wireless and Microwave Technology Conference, Cocoa Beach, FL, USA, 24–25 April 2017; pp. 1–4. [Google Scholar]

- Liu, B.; Fan, F.; Zhang, H.; Zeng, C. A wideband down conversion mixer with dual cross-coupled loops for software defined radio. In Proceedings of the 2015 IEEE International Symposium on Circuits and Systems, Lisbon, Portugal, 24–27 May 2015; pp. 990–993. [Google Scholar]

- Mehta, S.; Li, X.J.; Aneja, A. A Low Noise Image-Rejection Gilbert Mixer for Software Defined Radios. In Proceedings of the 2020 IEEE International Conference on Electronics, Computing and Communication Technologies, Bangalore, India, 2–4 July 2020; pp. 1–6. [Google Scholar]

- Chrisben Gladson, S.; Bhaskar, M. A low power high-performance area efficient RF front-end exploiting body effect for 2.4 GHz IEEE 802.15.4 applications. AEU-Int. J. Electron. Commun. 2018, 96, 81–92. [Google Scholar] [CrossRef]

- Huang, W.H.; Huang, I.Y.; Tseng, Y.S.; Hsieh, C.H.; Wang, C.C. A 19.38dBm OIP3 gm-boosted up-conversion CMOS mixer for 5–6GHz application. Microelectron. J. 2017, 60, 38–44. [Google Scholar] [CrossRef]

- Tomar, V.S.; Bhatia, V. Low Cost and Power Software Defined Radio Using Raspberry Pi for Disaster Effected Regions. Procedia Comput. Sci. 2015, 58, 401–407. [Google Scholar] [CrossRef]

- Hampel, S.K.; Schmitz, O.; Tiebout, M.; Rolfes, I. Inductorless Low-Voltage and Low-Power Wideband Mixer for Multistandard Receivers. IEEE Trans. Microw. Theory Tech. 2010, 58, 1384–1390. [Google Scholar] [CrossRef]

- Vidojkovic, V.; Tang, J.V.D.; Leeuwenburgh, A.; Roermund, A.V. Mixer topology selection for a 1.8–2.5 GHz multi-standard front-end in 0.18 um CMOS. In Proceedings of the 2003 International Symposium on Circuits and Systems, Bangkok, Thailand, 25–28 May 2003; Volume 2, pp. II301–II303. [Google Scholar]

- Vahidfar, M.B.; Shoaei, O. A CMOS high IIP2 mixer for multi-standard receivers. In Proceedings of the 2008 IEEE International Symposium on Circuits and Systems, Seattle, WA, USA, 18–21 May 2008; pp. 656–659. [Google Scholar]

- Kitsunezuka, M.; Hori, S.; Maeda, T. A Widely-Tunable Reconfigurable CMOS Analog Baseband IC for Software-Defined Radio. In Proceedings of the 2008 IEEE International Solid-State Circuits Conference-Digest of Technical Papers, San Francisco, CA, USA, 3–7 February 2008; pp. 66–595. [Google Scholar]

- Peng, Y.; Zhang, L.; Fu, J.; Wang, Y. Analysis and Design of a Broadband SiGe HBT Image-Reject Mixer Integrating Quadrature Signal Generator. IEEE Trans. Microw. Theory Tech. 2016, 64, 688–698. [Google Scholar] [CrossRef]

- El-Nozahi, M.; Sanchez-Sinencio, E.; Entesari, K. A CMOS Low-Noise Amplifier With Reconfigurable Input Matching Network. IEEE Trans. Microw. Theory Tech. 2009, 57, 1054–1062. [Google Scholar] [CrossRef]

- Othman, A.; Barrak, R.; Mabrouk, M. A tunable RF filter for multistandard GSM/UMTS/WiFi/LTE receiver. In Proceedings of the 2014 Mediterranean Microwave Symposium, Marrakech, Morocco, 12–14 December 2014; pp. 1–5. [Google Scholar]

- Lee, J.; Yun, T. High-gain mixer using cascode current bleeding and gm-boosting techniques. Microw. Opt. Technol. Lett. 2016, 59, 1–5. [Google Scholar] [CrossRef]

- Raja, R.; Venkataramani, B. A Current Injection Folded-Switch Mixer for Direct Conversion Receiver. In Proceedings of the International Conference on Communication Systems, Haryana, India, 18–20 October 2013; B K Birla Institute of Engineering and Technology: Haryana, India, 2013; pp. 36–44. [Google Scholar]

- Wei, B.; Dai, Y.; Lu, Y.; Zhang, X.; Liu, H. A Sub 1V High-Gain Low-Noise CMOS Downconversion Folded Mixer for 2.4 GHz ISM Band Applications. In Proceedings of the 2008 International Symposium on Intelligent Information Technology Application Workshops, Shanghai, China, 21–22 December 2008; pp. 689–692. [Google Scholar]

- Wei, H.; Hsiao, C. A 1 V bulk-controlled gm-boosted CMOS mixer for LTE-A applications. In Proceedings of the 2013 IEEE 2nd Global Conference on Consumer Electronics, Tokyo, Japan, 1–4 October 2013; pp. 239–242. [Google Scholar]

- Vahidfar, M.B.; Shoaei, O.; Hassanzadeh, M.R. CMOS mixer enhanced for multi-standard receivers. In Proceedings of the 2007 50th Midwest Symposium on Circuits and Systems, Montreal, QC, Canada, 5–8 August 2007; pp. 1010–1013. [Google Scholar]

- Yan, J.; Lim, K.M.; Gu, J.; Wang, K.; Lim, W.M.; Ma, K.; Yeo, K.S. A double-quadrature down-conversion mixer in 0.18 um SiGe BiCMOS process. In Proceedings of the 2011 International SoC Design Conference, Jeju, Korea, 17–18 November 2011; pp. 246–249. [Google Scholar]

- Zhang, C. Reconfigurable RF Front End Components for Multi-Radio Platform Applications. Doctor of Philosophy Thesis, Electrical Engineering, University of Tennessee-Knoxville, Knoxville, TN, USA, 2009. [Google Scholar]

- Kim, J.H.; Jang, Y.K.; Yoo, H.J. Design of reconfigurable RF front-end for multi-standard receiver using switchable passive networks. Analog Integr. Circuits Signal Process. 2007, 50, 81–88. [Google Scholar] [CrossRef]

- Hu, B.; Yu, X.; He, L. A Gm-boosted and current peaking wideband merged LNA and mixer. In Proceedings of the 2010 IEEE International Conference on Ultra-Wideband, Nanjing, China, 20–23 September 2010; Volume 1, pp. 1–4. [Google Scholar]

- Carusone, T.C.; Johns, D.A.; Martin, K.W. Analog Integrated Circuit Design; Wiley: Hoboken, NJ, USA, 2012. [Google Scholar]

- Tang, S.L. A new impedance matching method of CMOS mixer with common-source input stage. In Proceedings of the 2005 6th International Conference on ASIC, Shanghai, China, 24–27 October 2005; Volume 1, pp. 512–515. [Google Scholar]

- Zhiqun, L.; Zhigong, W.; Wei, C.; Li, Z. Image rejection low noise amplifier for WLAN 802.11a application. In Proceedings of the 2005 Asia-Pacific Microwave Conference Proceedings, Suzhou, China, 4–7 December 2005; Volume 5, pp. 1–4. [Google Scholar]

- Long, J.R. A low-voltage 5.1–5.8-GHz image-reject downconverter RF IC. IEEE J. Solid-State Circuits 2000, 35, 1320–1328. [Google Scholar] [CrossRef]

- Heijningen, M.V.; Hoogland, J.A.; Hek, A.P.D.; Vliet, F.E.V. 6–12 GHz double-balanced image-reject mixer MMIC in 0.25 um AlGaN/GaN technology. In Proceedings of the 2014 9th European Microwave Integrated Circuit Conference, Rome, Italy, 6–7 October 2014; pp. 65–68. [Google Scholar]

- Razavi, B. RF Microelectronics; Pearson Education: Boston, MA, USA, 2012. [Google Scholar]

- Heydari, P. An analysis of high-frequency noise in RF active CMOS mixers. Analog Integr. Circuits Signal Process. 2006, 48, 199–209. [Google Scholar] [CrossRef]

- Yadav, V.S.; Chaturvedi, A. 2.4 GHz active CMOS mixer for Bluetooth and Zigbee receiver systems. In Proceedings of the International Conference on Recent Advances and Innovations in Engineering, Jaipur, Rajasthan, India, 9–11 May 2014; pp. 1–6. [Google Scholar]

- Chen, J.; Lin, Z. 2.4 GHz High IIP3 and Low-Noise Down-conversion Mixer. In Proceedings of the 2006 IEEE Asia Pacific Conference on Circuits and Systems, Singapore, 4–7 December 2006; pp. 37–40. [Google Scholar]

- Motieifar, A.; Pour, Z.A.; Bridges, G.; Shafai, C.; Shafai, L. An ultra wideband mixer with integrated impedance-matching circuit. In Proceedings of the 2006 12th International Symposium on Antenna Technology and Applied Electromagnetics and Canadian Radio Sciences Conference, Montreal, QC, Canada, 17–19 July 2006; pp. 1–4. [Google Scholar]

- Tedjini-Bailiche, S.A.; Trabelsi, M.; Slimane, A.; Belaroussi, M.T.; Haddad, F.; Bourdel, S. Ultra low power and high gain switched CMOS gm-boosted current reused mixer for wireless multi-standard applications. Microelectron. J. 2014, 45, 1575–1582. [Google Scholar] [CrossRef]

- Liang, K.; Chang, H.; Chan, Y. A 0.5–7.5 GHz Ultra Low-Voltage Low-Power Mixer Using Bulk-Injection Method by 0.18- um CMOS Technology. IEEE Microw. Wirel. Comp. Lett. 2007, 17, 531–533. [Google Scholar] [CrossRef]

- Wu, C.; Hsieh, H.; Lai, L.; Lu, L. A 3–5 GHz Frequency-Tunable Receiver Frontend for Multiband Applications. IEEE Microw. Wirel. Comp. Lett. 2008, 18, 638–640. [Google Scholar] [CrossRef]

- Ho, S.S.K.; Saavedra, C.E. A CMOS Broadband Low-Noise Mixer With Noise Cancellation. IEEE Trans. Microw. Theory Tech. 2010, 58, 1126–1132. [Google Scholar] [CrossRef]

- Lin, Y.; Lan, K.; Wang, C.; Chi, C.; Lu, S. 6.3 mW 94 GHz CMOS Down-Conversion Mixer With 11.6 dB Gain and 54 dB LO-RF Isolation. IEEE Microw. Wirel. Comp. Lett. 2016, 26, 604–606. [Google Scholar] [CrossRef]

- Zhu, F.; Wang, K.; Wu, K. A Reconfigurable Low-Voltage and Low-Power Millimeter-Wave Dual-Band Mixer in 65-nm CMOS. IEEE Access 2019, 7, 33359–33368. [Google Scholar] [CrossRef]

- Na, D.; Kim, T.W. A 1.2 V, 0.87–3.7 GHz Wideband Low-Noise Mixer Using a Current Mirror for Multiband Application. IEEE Microw. Wirel. Comp. Lett. 2012, 22, 91–93. [Google Scholar] [CrossRef]

- Mahajan, D.; Ruparelia, V. Reliability Simulation and Analysis of Important RF Circuits Using Cadence Relxpert. In Proceedings of the 2018 IEEE International Conference on Electronics, Computing and Communication Technologies, Bangalore, India, 16–17 March 2018; pp. 1–6. [Google Scholar]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).