Robust Pixel Design Methodologies for a Vertical Avalanche Photodiode (VAPD)-Based CMOS Image Sensor

Abstract

1. Introduction

2. Robust Pixel Design of “Guard-Ring-Free” VAPD-CIS

2.1. Device Architecture of a VAPD Pixel Compared to a Conventional SPAD Pixel

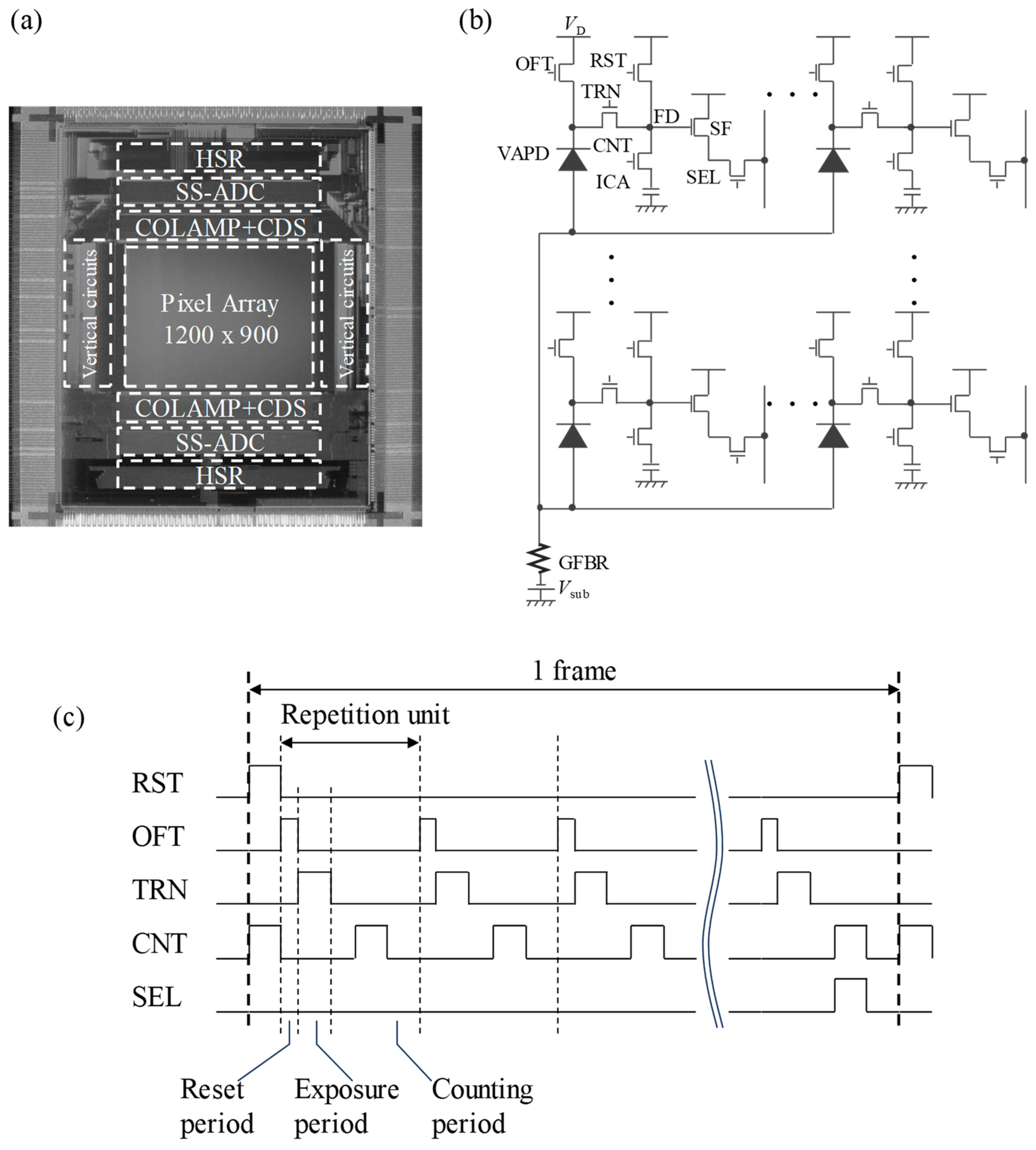

2.2. Specifications and Chip Designs for VAPD-CISs

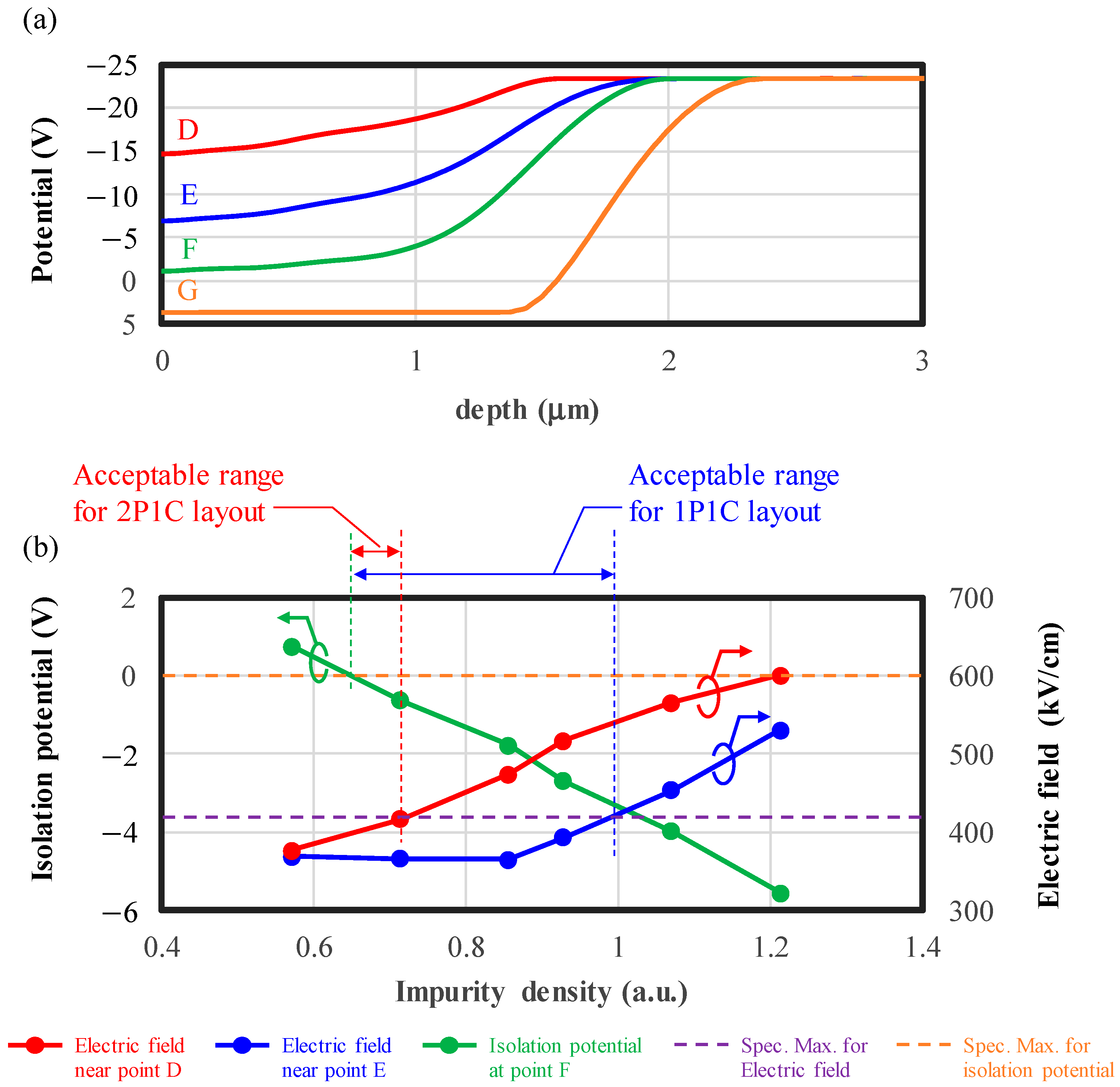

2.3. Potential and Layout Designs for Electric Field Relaxation and Pixel Isolation

3. Verification of the Robustness of VAPD-CIS

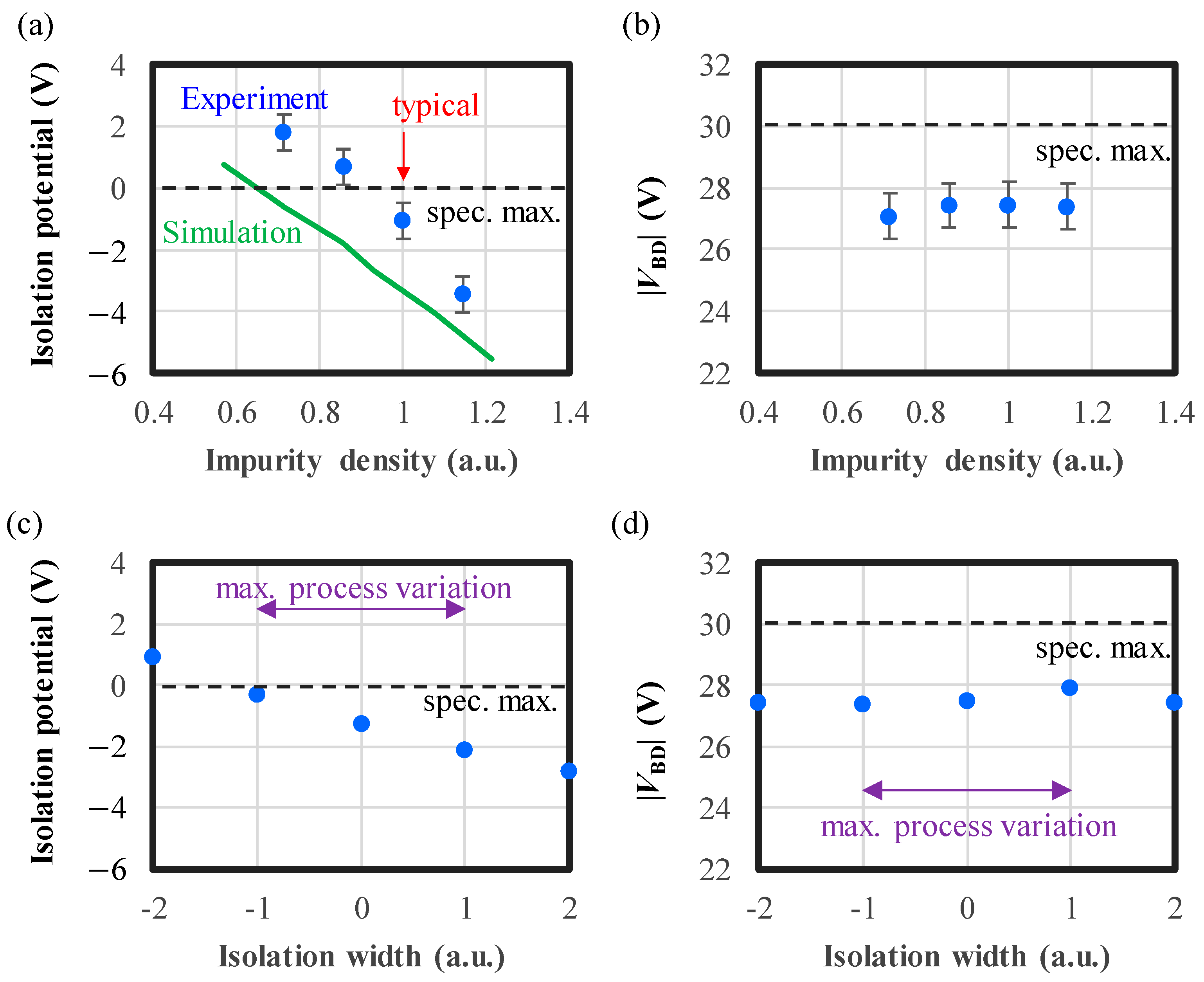

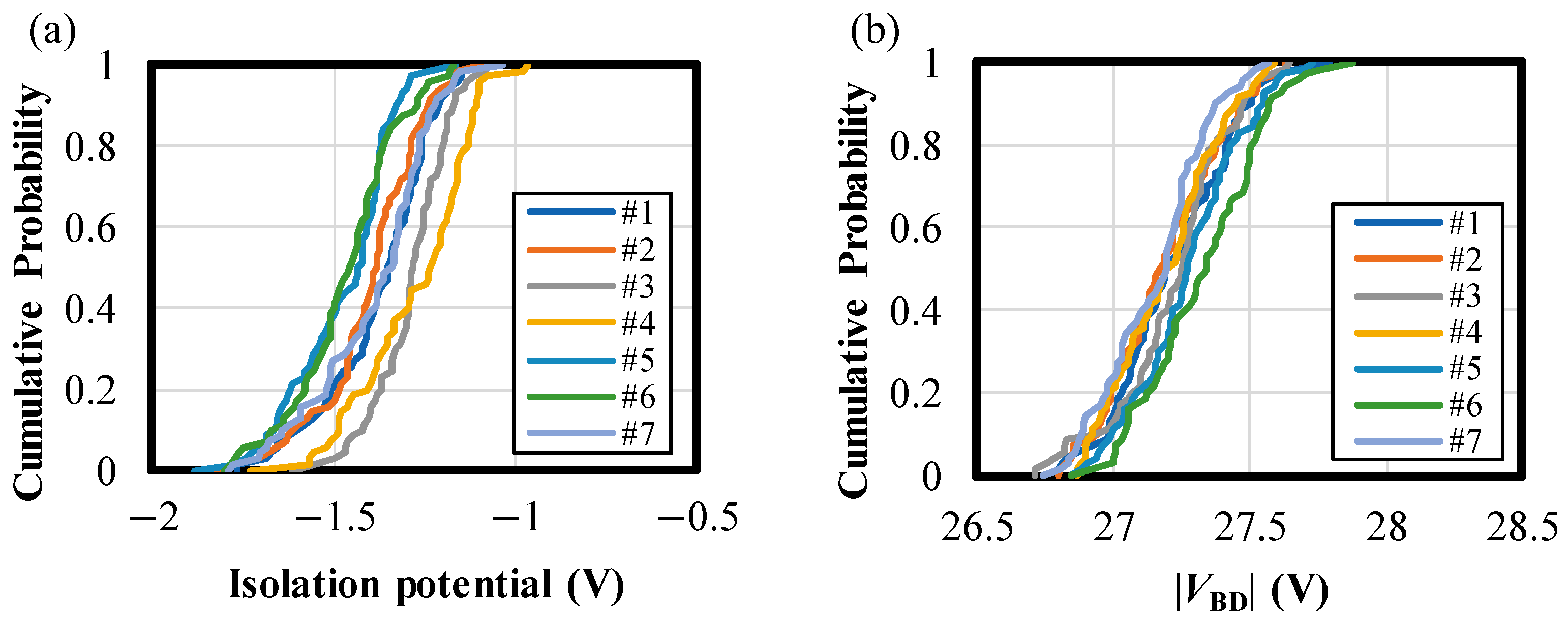

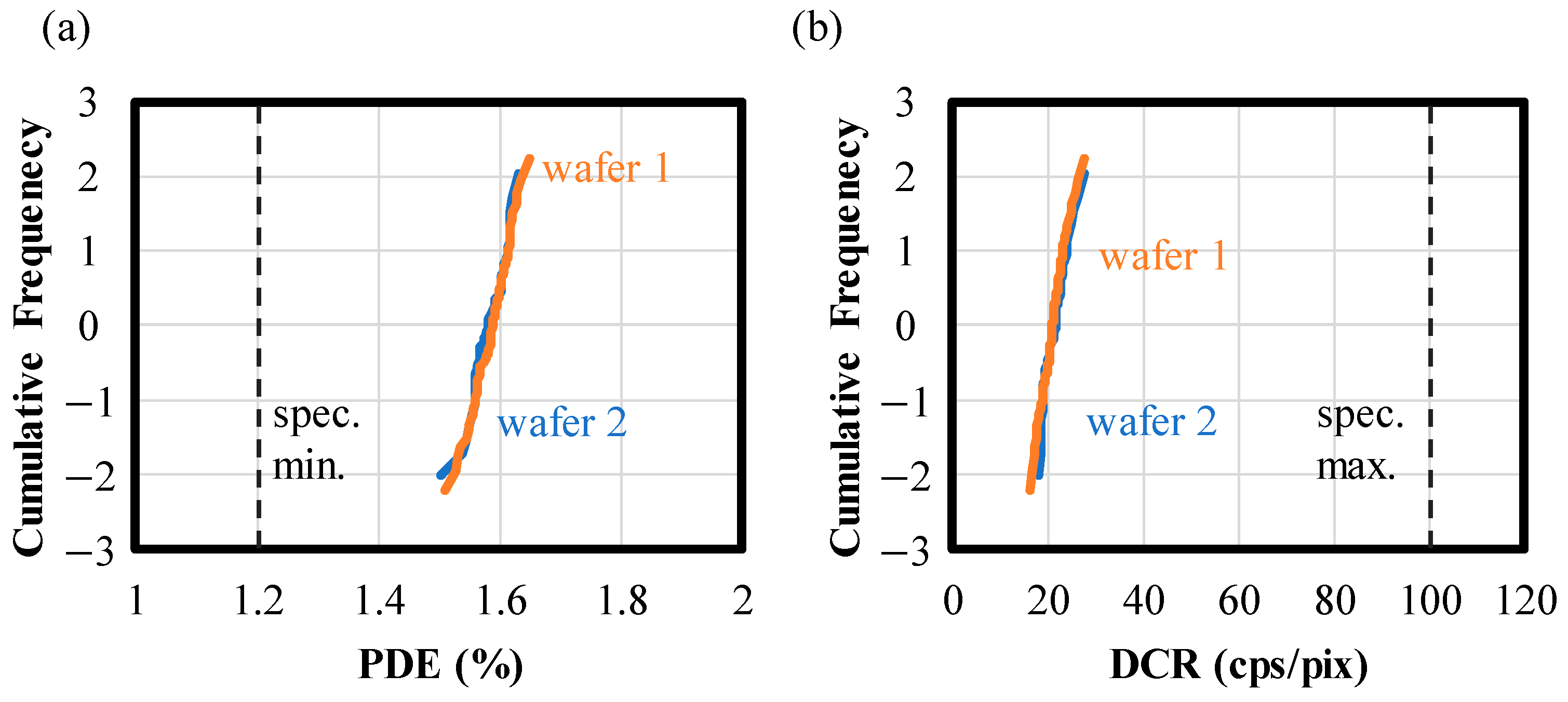

3.1. Verification of Potential Design against Process Variation

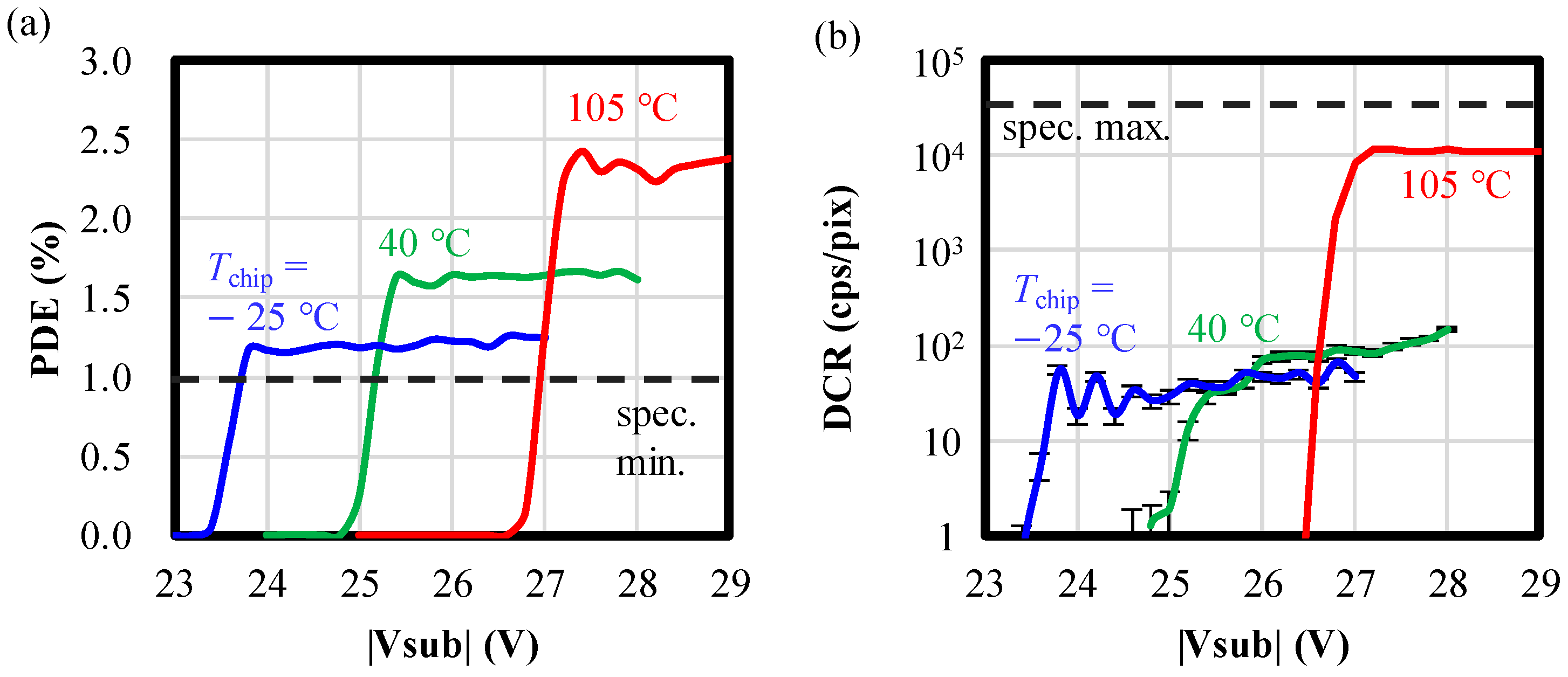

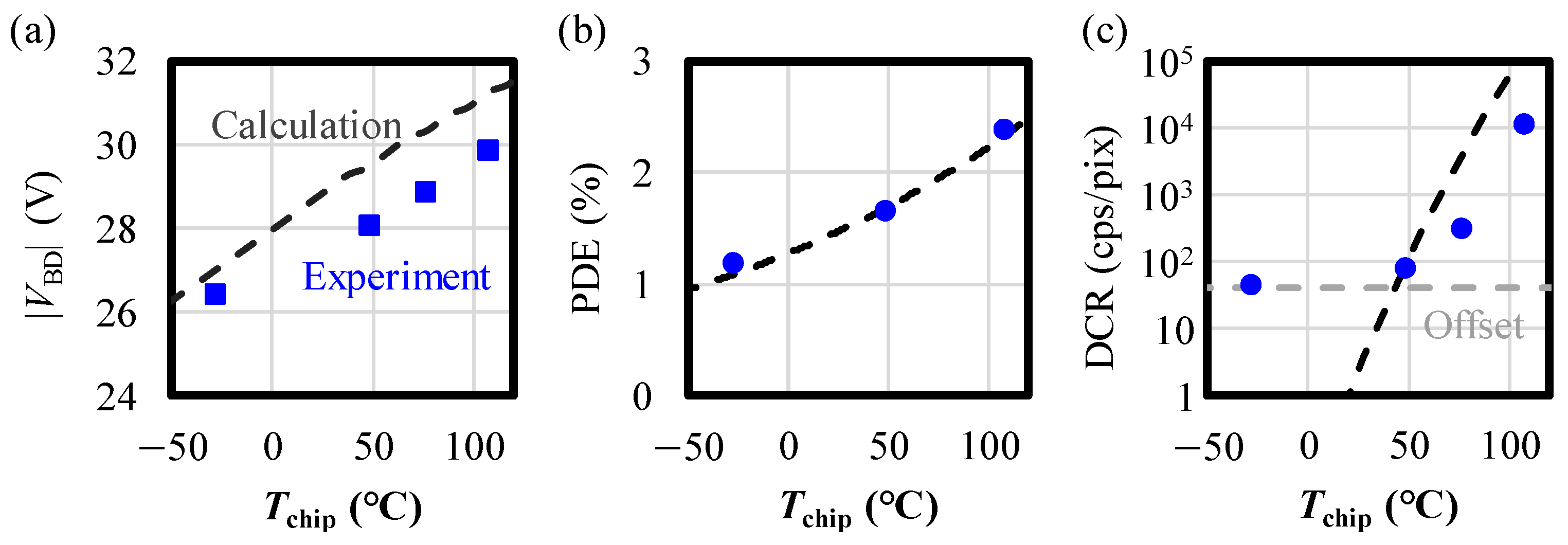

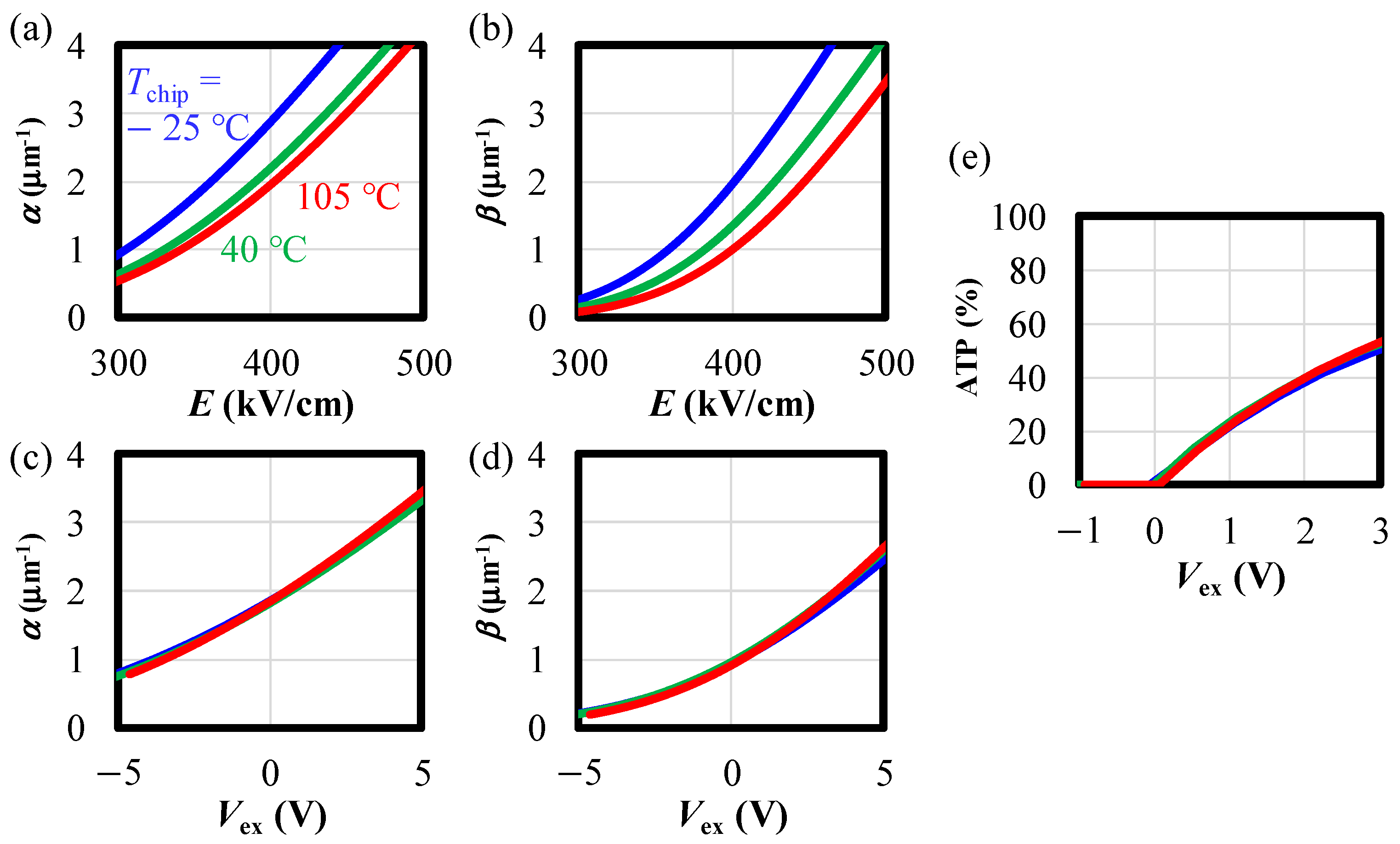

3.2. Characteristics of Robustness to Applied Voltage and Temperature

4. Robust Operation of VAPD-CIS in High-Temperature and Intense-Light-Exposure Conditions

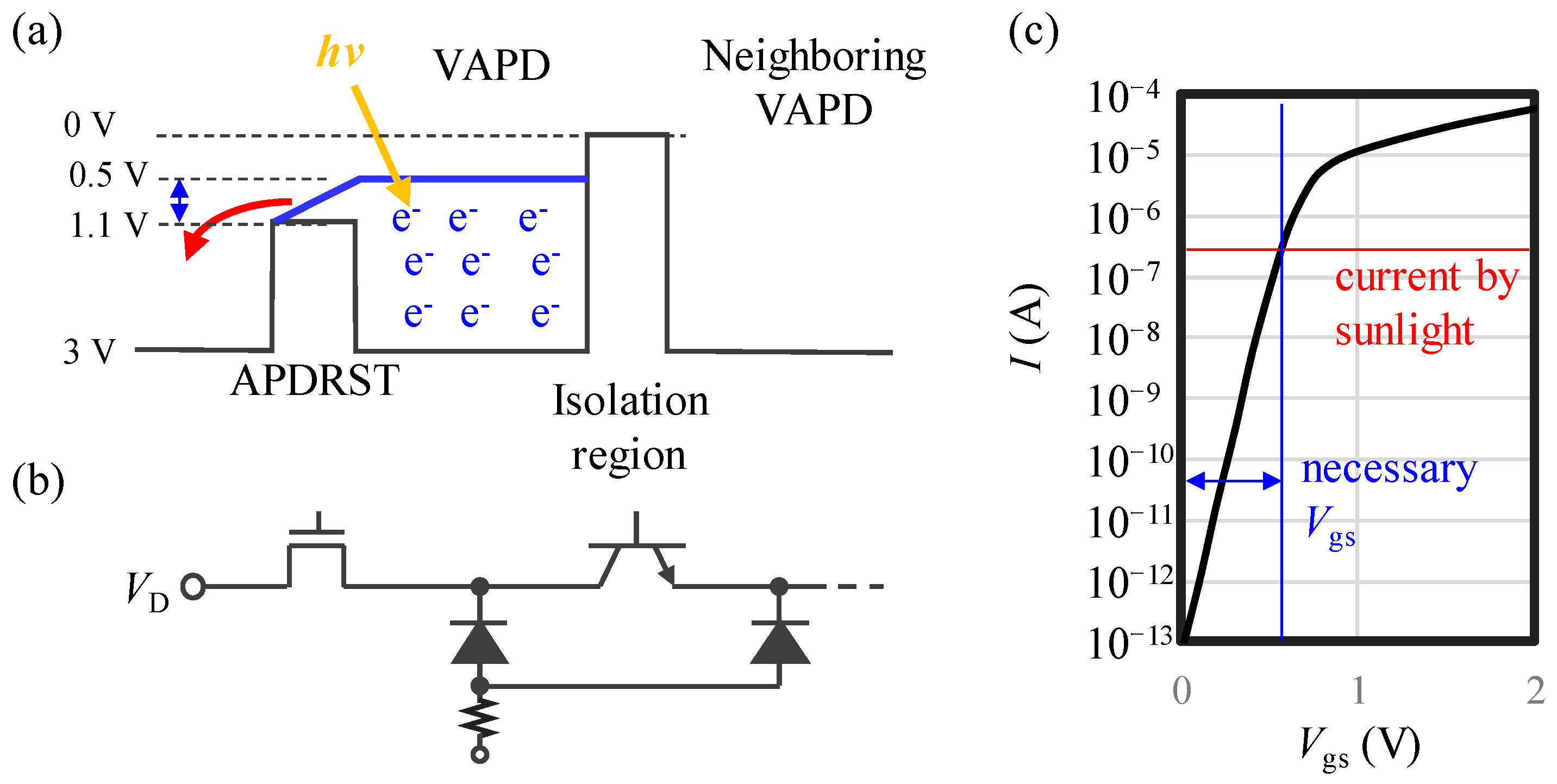

4.1. Stable Operation during Direct Imaging of the Sun (DIS)

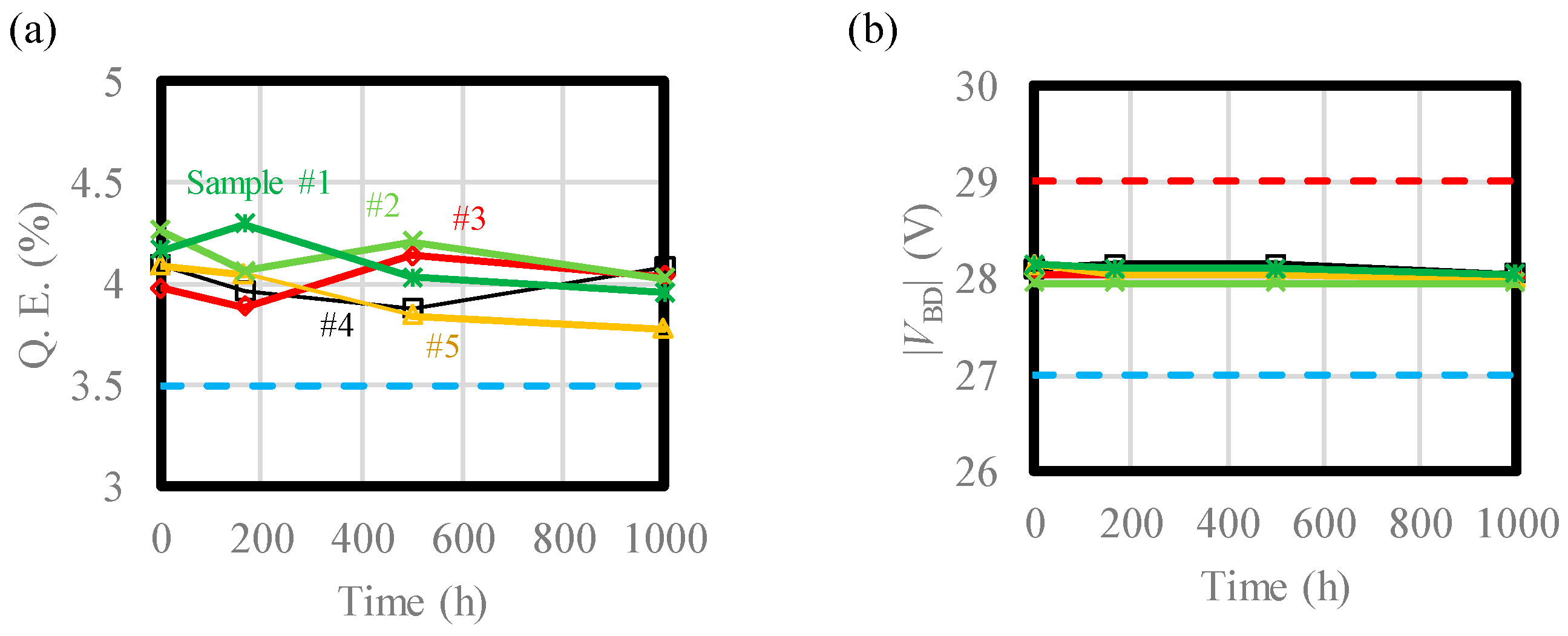

4.2. Stable Operation with No Degradation during High-Temperature/Intensity-Light-Illumination Operation Tests (HTs/ILOTs)

5. Discussion

5.1. Mechanism of Voltage Stabilizing by GFBR for Robust Operation

5.2. Temperature-Independent ATP: The Stabilizing Effect of GFBR

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

List of Selected Acronyms

| AM | (voltage) Amplitude of Multiplication |

| ATP | Avalanche Triggering Probability |

| DIS | Direct Imaging of the Sun |

| GFBR | Global Feedback Resistor |

| HT/ILOT | High-Temperature/Intensity-Light-illumination Operation Test |

| MR | (avalanche) Multiplication Region |

| OFT | Overflow Transistor |

| SRS-TOF | Subrange Synthesis Time-of-Flight |

| VAPD | Vertical Avalanche Photodiode |

Appendix A

Appendix A.1. Calculation Formulas for Main Characteristics

References

- Morimoto, K.; Ardelean, A.; Wu, M.-L.; Ulku, A.C.; Antolovic, I.M.; Bruschini, C.; Charbon, E. Megapixel time-gated SPAD image sensor for 2D and 3D imaging applications. Optica 2020, 7, 346–354. [Google Scholar] [CrossRef]

- Morimoto, K.; Iwata, J.; Shinohara, M.; Sekine, H.; Abdelghafar, A.; Tsuchiya, H.; Kuroda, Y.; Tojima, K.; Endo, W.; Maehashi, Y.; et al. 3.2 Megapixel 3D-Stacked Charge Focusing SPAD for Low-Light Imaging and Depth Sensing. In Proceedings of the 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 11–16 December 2021; pp. 20.2.1–20.2.4. [Google Scholar] [CrossRef]

- Okino, T.; Yamada, S.; Sakata, Y.; Kasuga, S.; Takemoto, M.; Nose, Y.; Koshida, H.; Tamaru, M.; Sugiura, Y.; Saito, S.; et al. A 1200 × 900 6 μm 450 fps Geiger-Mode Vertical Avalanche Photodiodes CMOS Image Sensor for a 250 m Time-of-Flight Ranging System Using Direct-Indirect-Mixed Frame Synthesis with Configurable-Depth-Resolution Down to 10 cm. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 17 February 2020; pp. 96–98. [Google Scholar] [CrossRef]

- Henderson, R.K.; Johnston, N.; Hutchings, S.W.; Gyongy, I.; Abbas, T.A.; Dutton, N.; Tyler, M.; Chan, S.; Leach, J. A 256 × 256 40 nm/90 nm CMOS 3D-Stacked 120 dB- dynamic-range reconfigurable time-resolved SPAD imager. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 18 February 2019; pp. 106–108. [Google Scholar]

- Takatsuka, T.; Ogi, J.; Ikeda, Y.; Hizu, K.; Inaoka, Y.; Sakama, S.; Watanabe, I.; Ishikawa, T.; Shimada, S.; Suzuki, J.; et al. A 3.36 µm-pitch SPAD photon-counting image sensor using clustered multi-cycle clocked recharging technique with intermediate most-significant-bit readout. In Proceedings of the 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Kyoto, Japan, 11–16 June 2023; pp. 1–2. [Google Scholar] [CrossRef]

- Dutton, N.A.; Gyongy, I.; Parmesan, L.; Gnecchi, S.; Calder, N.; Rae, B.R.; Pellegrini, S.; Grant, L.A.; Henderson, R.K. A SPAD-Based QVGA Image Sensor for Single-Photon Counting and Quanta Imaging. IEEE Trans. Electron Devices 2016, 63, 189–196. [Google Scholar] [CrossRef]

- Yamada, S.; Ishii, M.; Kasuga, S.; Takemoto, M.; Kitajima, H.; Okino, T.; Sakata, Y.; Usuda, M.; Nose, Y.; Koshida, H.; et al. A Nearly Interference-Free and Depth-Resolution-Configurable Time-of-Flight System Based on a Mega-Pixel Vertical Avalanche Photodiodes CMOS Image Sensor. IEEE Open J. Circuits Syst. 2022, 3, 324–335. [Google Scholar] [CrossRef]

- Zhang, C.; Zhang, N.; Ma, Z.; Wang, L.; Qin, Y.; Jia, J.; Zang, K. A 240 × 160 3D-Stacked SPAD dToF Image Sensor with Rolling Shutter and In-Pixel Histogram for Mobile Devices. IEEE Open J. Solid-State Circuits Soc. 2022, 2, 3–11. [Google Scholar] [CrossRef]

- Portaluppi, D.; Conca, E.; Villa, F.; Zappa, F. Time-gated SPAD camera with reconfigurable macropixels for LIDAR applications. In Proceedings of the SPIE 11051, 32nd International Congress on High-Speed Imaging and Photonics, Enschede, The Netherlands, 8–12 October 2018; p. 110510J. [Google Scholar] [CrossRef]

- Perenzoni, M.; Massari, N.; Perenzoni, D.; Gasparini, L.; Stoppa, D. 160 × 120 Pixel Analog-Counting Single-Photon Imager With Time-Gating and Self-Referenced Column-Parallel A/D Conversion for Fluorescence Lifetime Imaging. IEEE J. Solid-State Circuits 2016, 51, 155–167. [Google Scholar]

- Marisaldi, M.; Maccagnani, P.; Moscatelli, F.; Labanti, C.; Fuschino, F.; Prest, M.; Berra, A.; Bolognini, D.; Ghioni, M.; Rech, I.; et al. Single Photon Avalanche Diodes for Space Applications. In Proceedings of the 2011 IEEE Nuclear Science Symposium Conference Record, Valencia, Spain, 23–29 October 2011; pp. 129–134. [Google Scholar] [CrossRef]

- Michálek, V.; Procházka, I.; Blažej, J. Twenty Years of Rad-Hard K14 SPAD in Space Projects. Sensors 2015, 15, 18178–18196. [Google Scholar] [CrossRef]

- Manuzzato, E.; Tontini, A.; Seljak, A.; Perenzoni, M. A 64 × 64-Pixel Flash LiDAR SPAD Imager with Distributed Pixel-to-Pixel Correlation for Background Rejection, Tunable Automatic Pixel Sensitivity and First-Last Event Detection Strategies for Space Applications. In Proceedings of the 2022 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 20–26 February 2022; pp. 96–98. [Google Scholar] [CrossRef]

- Ito, K.; Otake, Y.; Kitano, Y.; Matsumoto, A.; Yamamoto, J.; Ogasahara, T.; Hiyama, H.; Naito, R.; Takeuchi, K.; Tada, T.; et al. A Back Illuminated 10 μm SPAD Pixel Array Comprising Full Trench Isolation and Cu-Cu Bonding with Over 14% PDE at 940 nm. In Proceedings of the 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 12–18 December 2020; pp. 16.6.1–16.6.4. [Google Scholar] [CrossRef]

- Ota, Y.; Morimoto, K.; Sasago, T.; Shinohara, M.; Kuroda, Y.; Endo, W.; Maehashi, Y.; Maekawa, S.; Tsuchiya, H.; Abdelahafar, A.; et al. A 0.37 W 143 dB-Dynamic-Range 1Mpixel Backside-Illuminated Charge-Focusing SPAD Image Sensor with Pixel-Wise Exposure Control and Adaptive Clocked Recharging. In Proceedings of the 2022 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 20–26 February 2022; pp. 94–96. [Google Scholar] [CrossRef]

- Morimoto, K.; Charbon, E. A Scaling Law for SPAD Pixel Miniaturization. Sensors 2021, 21, 3447. [Google Scholar] [CrossRef] [PubMed]

- Inoue, A. Stochastic Quenching Mechanisms and a Scaling Law for Single Photon Avalanche Diodes. IEEE Trans. Electron Devices 2024, 71, 904–910. [Google Scholar] [CrossRef]

- Morimoto, K.; Charbon, E. High fill-factor miniaturized SPAD arrays with a guard-ring-sharing technique. Opt. Express 2020, 28, 13068–13080. [Google Scholar] [CrossRef] [PubMed]

- Inoue, A.; Okino, T.; Koyama, S.; Hirose, Y. Modeling and analysis of capacitive relaxation quenching in a single photon avalanche diode (SPAD) applied to a CMOS image sensor. Sensors 2020, 20, 3007. [Google Scholar] [CrossRef]

- Charbon, E. Single-photon imaging in complementary metal oxide semiconductor processes. Philos. Trans. A Math. Phys. Eng. Sci. 2014, 372, 20130100. [Google Scholar] [CrossRef] [PubMed] [PubMed Central]

- Kataoka, J.; Sato, R.; Ikagawa, T.; Kotoku, J.; Kuramoto, Y.; Tsubuku, Y.; Saito, T.; Yatsu, Y.; Kawai, N.; Ishikawa, Y.; et al. An active gain-control system for Avalanche photo-diodes under moderate temperature variations. Nucl. Instrum. Methods Phys. Res. Sect. A Accel. Spectrometers Detect. Assoc. Equip. 2006, 564, 300–307. [Google Scholar] [CrossRef][Green Version]

- S15415-02, High-Speed, Compact Si APD that Does Not Require Temperature Adjustment, Hamamatsu Photonics. Available online: https://www.hamamatsu.com/eu/en/product/optical-sensors/apd/si-apd/S15415-02.html (accessed on 9 August 2024).

- Pellegrini, S.; Rae, B. Fully industrialised single photon avalanche diodes. In Proceedings of the SPIE 10212, Advanced Photon Counting Techniques XI, Anaheim, CA, USA, 9–13 April 2017; p. 102120D. [Google Scholar] [CrossRef]

- Jackson, C.; O’neill, K.; Wall, L.A.; McGarvey, B. High-volume silicon photomultiplier production, performance, and reliability. Opt. Eng. 2014, 53, 081909. [Google Scholar] [CrossRef]

- Itzler, M. InP-based SPADs for Automotive Lidar. In Proceedings of the 2020 International SPAD Sensor Workshop (ISSW), Virtual, 8–10 June 2020. [Google Scholar]

- Gnani, E.; Reggiani, S.; Rudan, M.; Baccarani, G. Extraction method for the impact-ionization multiplication factor in silicon at large operating temperatures. In Proceedings of the 32nd European Solid-State Device Research Conference (ESSDERC), Florence, Italy, 24–26 September 2002; pp. 227–230. [Google Scholar]

- Martin, A.G. Self-consistent optical parameters of intrinsic silicon at 300 K including temperature coefficients. Sol. Energy Mater. Sol. Cells 2008, 92, 1305–1310. [Google Scholar]

- Gueymard, C.A. Parameterized Transmittance Model for Direct Beam and Circumsolar Spectral Irradiance. Sol. Energy 2001, 71, 325–346. [Google Scholar] [CrossRef]

- AEC-Q100-REV-J Failure Mechanism Based Stress Test Qualification for Integrated Circuits in Automotive Applications, Automotive Electronics Council. 2023. Available online: http://www.aecouncil.com/Documents/AEC_Q100_Rev_J_Base_Document.pdf (accessed on 9 August 2024).

- Inoue, A.; Hirose, Y. Non-linear carrier dynamics in a single photon avalanche diode: Stability, bifurcation and quenching condition. IEEE Trans. Electron Devices 2021, 68, 6222–6227. [Google Scholar] [CrossRef]

- Sze, S.M.; Gibbons, G. Avalanche breakdown voltages of abrupt and linearly graded pn junctions in Ge, Si, GaAs, and GaP. Appl. Phys. Lett. 1966, 8, 111–113. [Google Scholar] [CrossRef]

- Oldham, W.G.; Samuelson, R.R.; Antognetti, P. Triggering phenomena in avalanche diodes. IEEE Trans. Electron Devices 1972, 19, 1056–1060. [Google Scholar] [CrossRef]

- Muller, R.S.; Kamins, T.I. Device Electronics for Integrated Circuits, 3rd ed.; Wiley: Hoboken, NJ, USA, 2003. [Google Scholar]

| Items | Specifications | Typical Experimental Results |

|---|---|---|

| CMOS technology | 65 nm 1P4M1MIM | |

| Pixel pitch | 6 μm | |

| Array size | 1200 × 900 | |

| Frame rate | 30 fps | |

| Fill factor | 30.6% (including circuit area) 57.3% (excluding circuit area) | |

| |VBD| | <32 V | 29.8 V @−25 °C 27.5 V @RT |

| Isolation potential | <0 V | −1.3 V @RT |

| PDE @940 nm | >1% >1.2%@RT | 1.2% @−25 °C 1.6% @RT |

| DCR | <100 cps/pix @RT <54,000 cps/pix @105 °C | 21 cps/pix @RT 10,000 cps/pix @105 °C |

| Voltage swings | >1 V | 1.5 V |

| Item | Before | After | Variation | Test Spec. |

|---|---|---|---|---|

| Q.E. (%) | 4.38% | 4.20% | −4.0% | 3.5% max. |

| |VBD| (V) | 28.15 V | 28.15 V | 0% | 27 V~29 V |

| DCR (cps) | 21.5 cps | 20.4 cps | −5.0% | 50 cps max. |

| PDE (%) | 1.46% | 1.46% | 0% | 1% min. |

| AM (V) | 1.50 V | 1.50 V | 0% | 1 V min. |

| σAM (V) | 0.083 V | 0.084 V | 1.4% | 0.17 V max. |

| Temperature | 125 °C |

| Illumination power | 827 μW/cm2 |

| Wavelength | 940 nm |

| Exposure Time | 1000 h. |

| Optical Filters Condition | w. BPF and Lens |

| Driving mode | Time-of-Flight (45,000 exposures/s) |

| Read-out speed | 450 fps |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Inoue, A.; Torazawa, N.; Yamada, S.; Sugiura, Y.; Ishii, M.; Sakata, Y.; Kunikyo, T.; Tamaru, M.; Kasuga, S.; Yuasa, Y.; et al. Robust Pixel Design Methodologies for a Vertical Avalanche Photodiode (VAPD)-Based CMOS Image Sensor. Sensors 2024, 24, 5414. https://doi.org/10.3390/s24165414

Inoue A, Torazawa N, Yamada S, Sugiura Y, Ishii M, Sakata Y, Kunikyo T, Tamaru M, Kasuga S, Yuasa Y, et al. Robust Pixel Design Methodologies for a Vertical Avalanche Photodiode (VAPD)-Based CMOS Image Sensor. Sensors. 2024; 24(16):5414. https://doi.org/10.3390/s24165414

Chicago/Turabian StyleInoue, Akito, Naoki Torazawa, Shota Yamada, Yuki Sugiura, Motonori Ishii, Yusuke Sakata, Taiki Kunikyo, Masaki Tamaru, Shigetaka Kasuga, Yusuke Yuasa, and et al. 2024. "Robust Pixel Design Methodologies for a Vertical Avalanche Photodiode (VAPD)-Based CMOS Image Sensor" Sensors 24, no. 16: 5414. https://doi.org/10.3390/s24165414

APA StyleInoue, A., Torazawa, N., Yamada, S., Sugiura, Y., Ishii, M., Sakata, Y., Kunikyo, T., Tamaru, M., Kasuga, S., Yuasa, Y., Kitajima, H., Koshida, H., Kabe, T., Usuda, M., Takemoto, M., Nose, Y., Okino, T., Shirono, T., Nakanishi, K., ... Tanaka, T. (2024). Robust Pixel Design Methodologies for a Vertical Avalanche Photodiode (VAPD)-Based CMOS Image Sensor. Sensors, 24(16), 5414. https://doi.org/10.3390/s24165414