Optoelectronics Interfaces for a VLC System for UHD Audio-Visual Content Transmission in a Passenger Van: HW Design

Abstract

1. Introduction

2. Materials and Methods

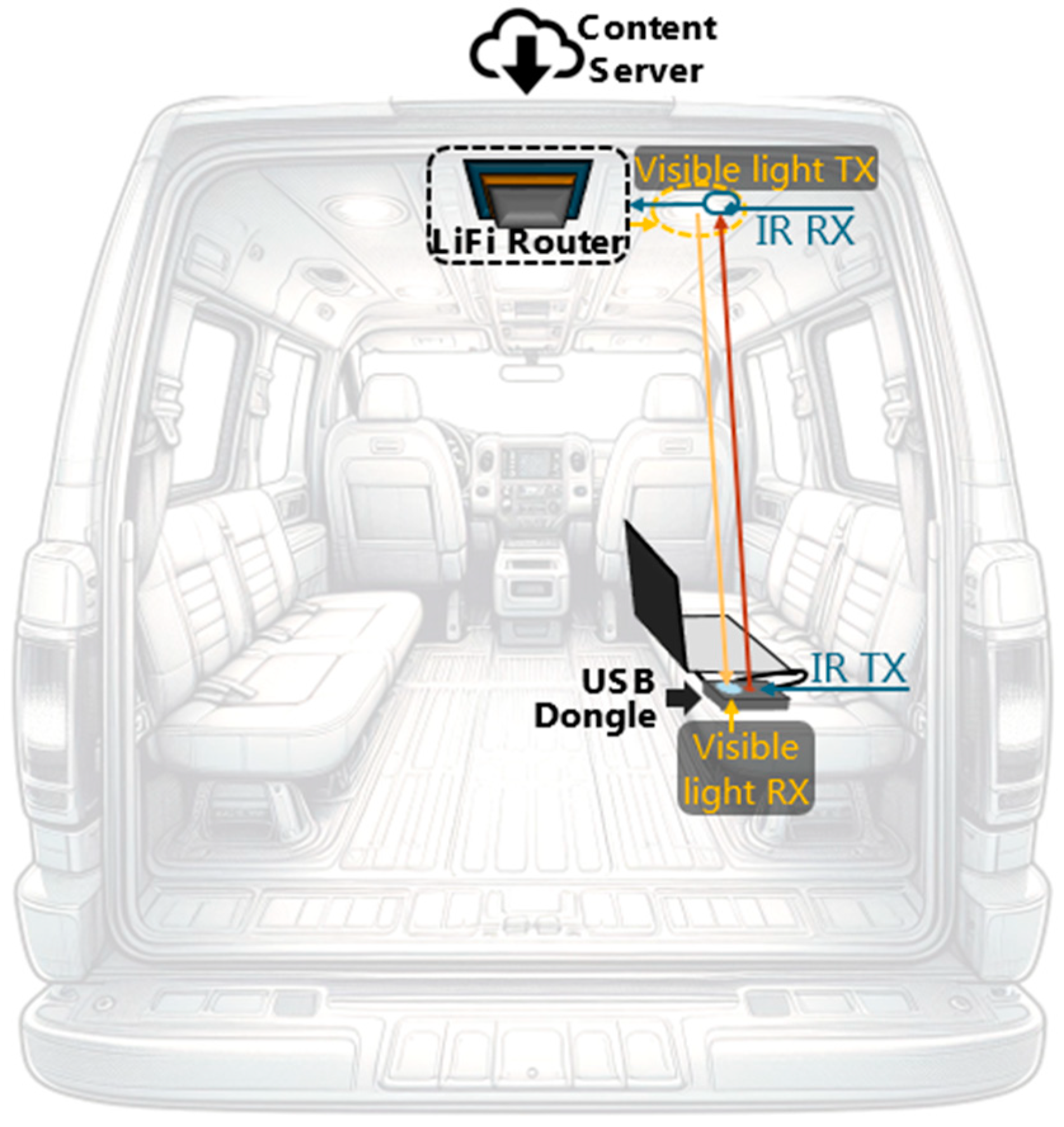

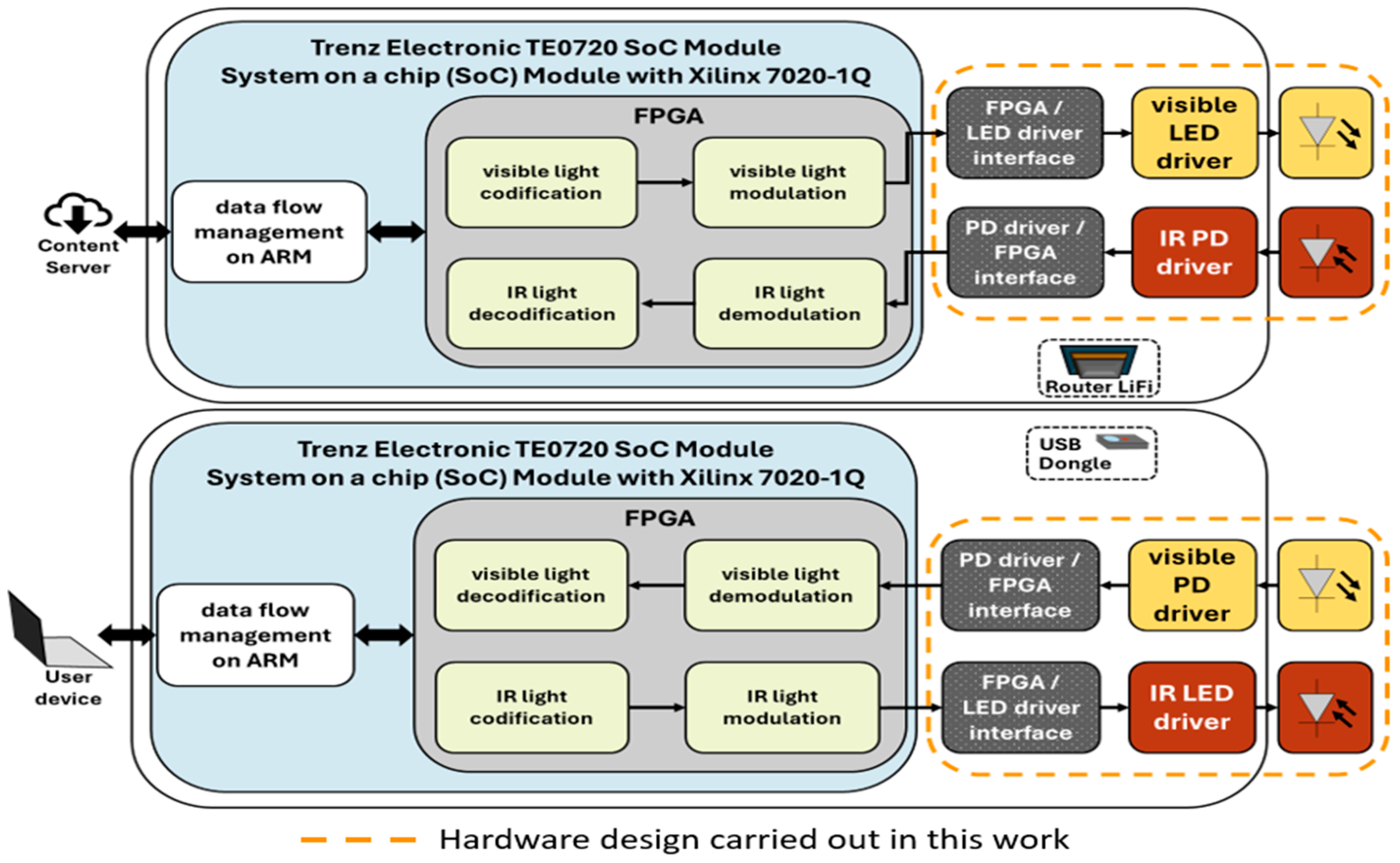

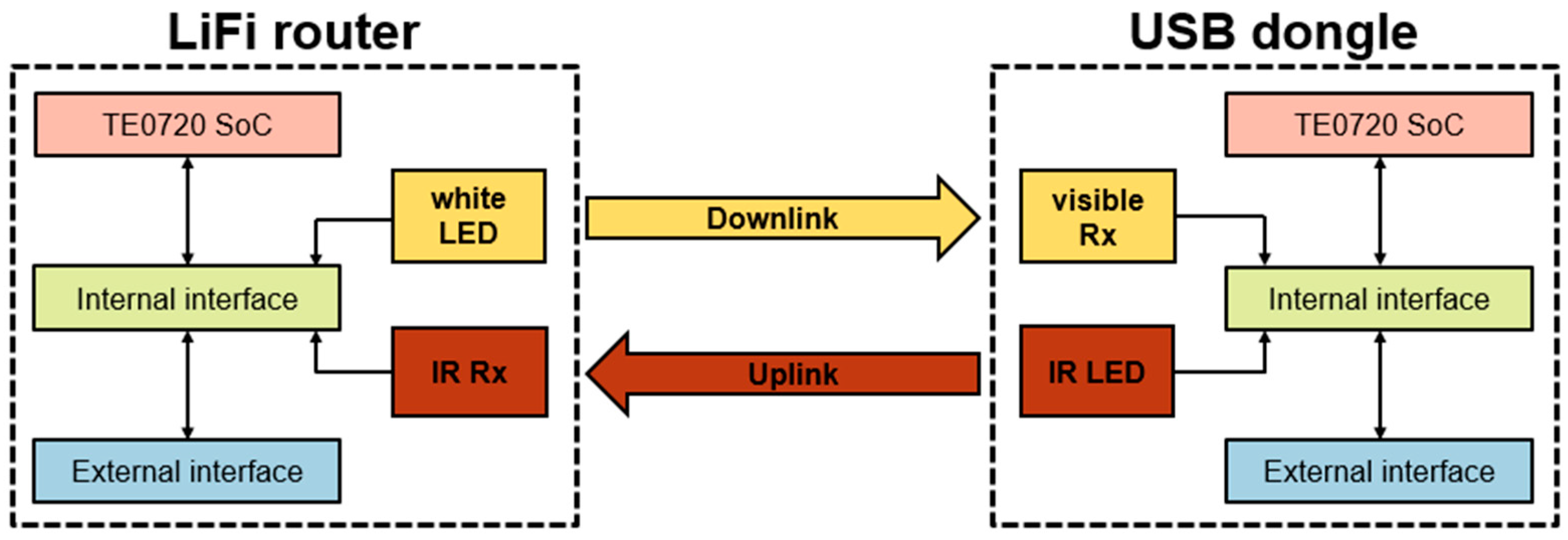

2.1. Description of the Proposed System

2.2. Definition and Design of the System’s Components

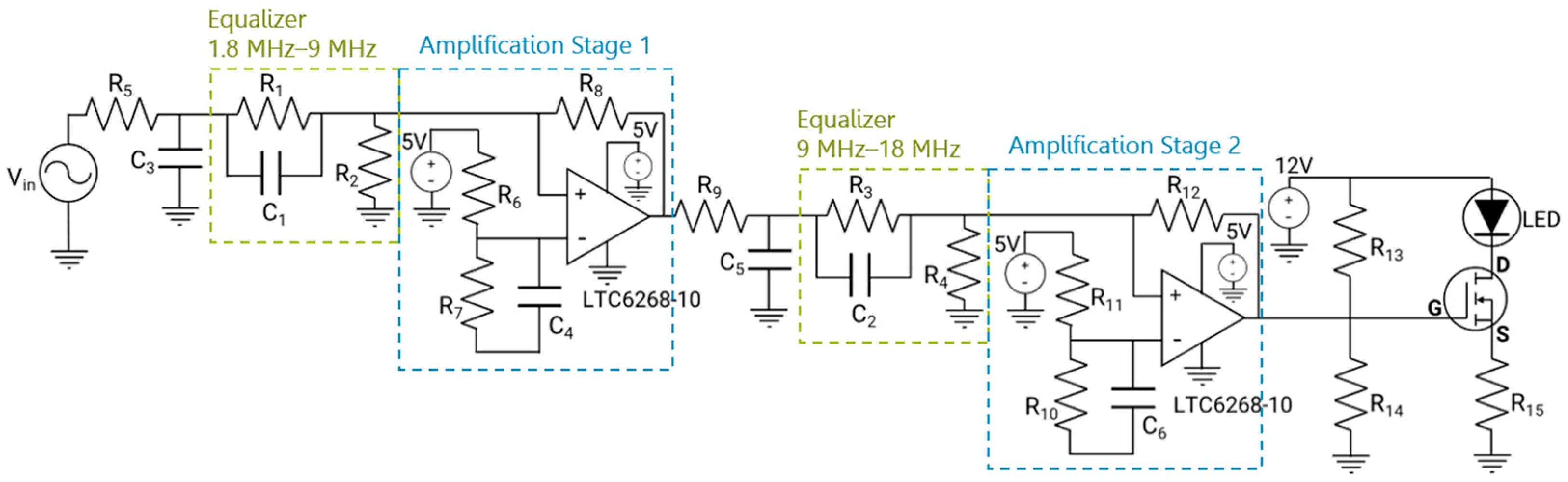

2.2.1. LED Driver

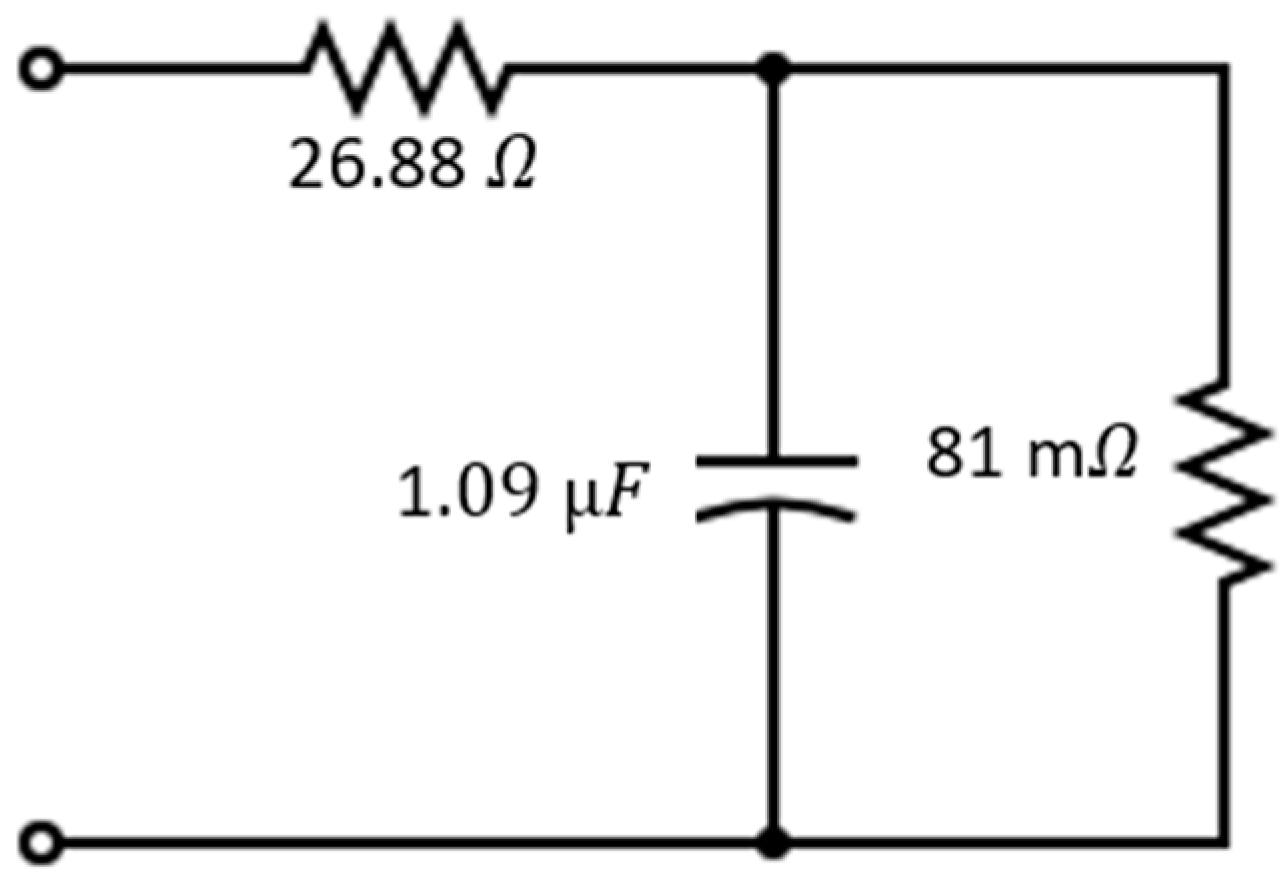

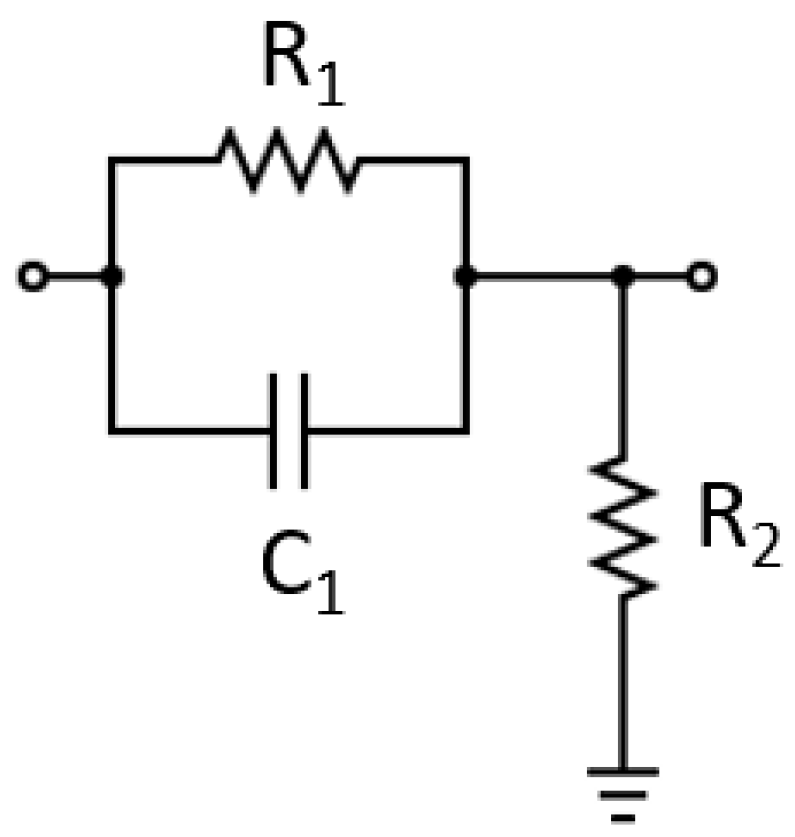

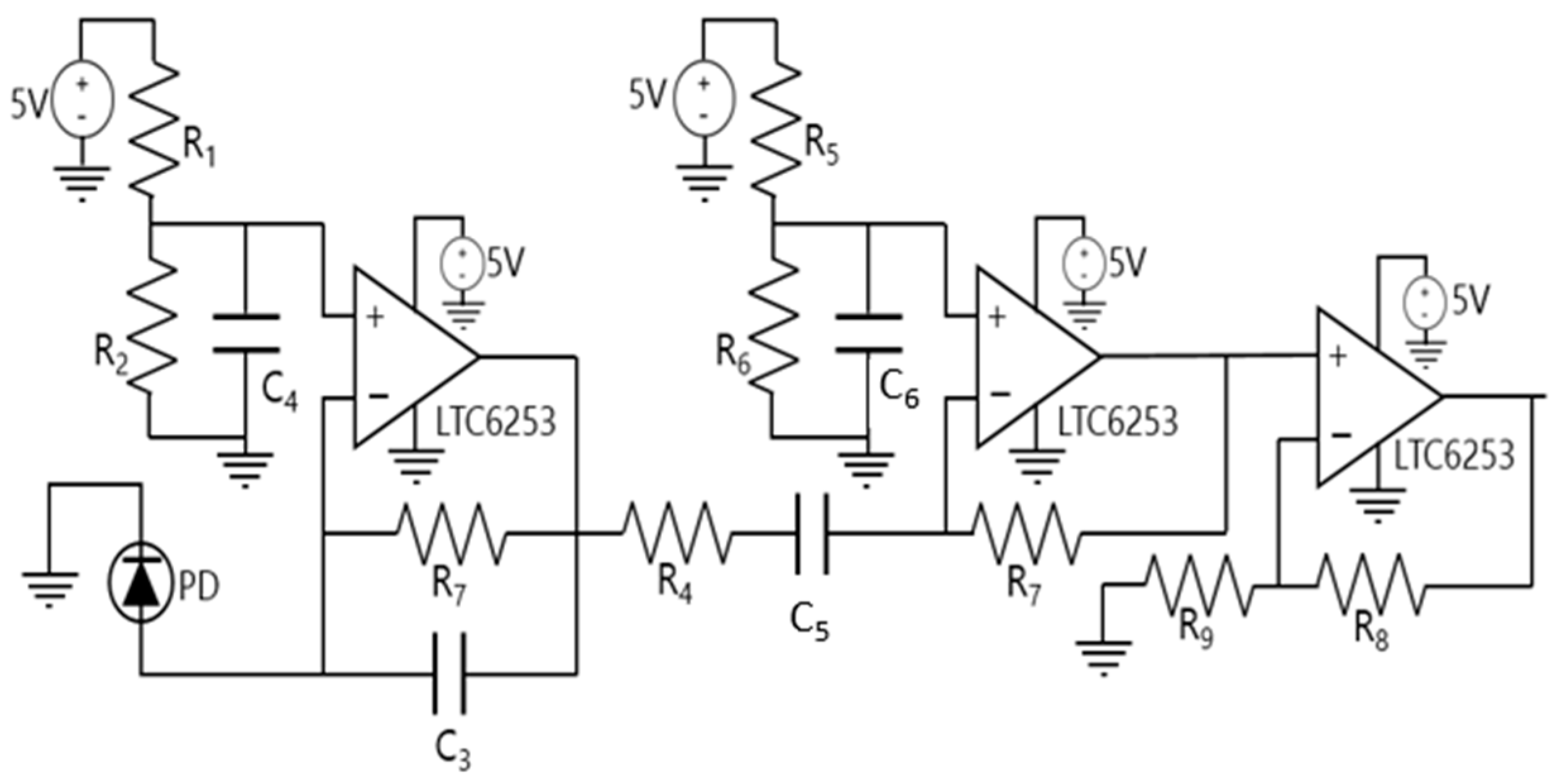

2.2.2. PD Driver

2.2.3. Internal Interfaces to Connect FPGA/LED Driver and FPGA/PD Driver

Interface Module for FPGA/LED Driver Connection

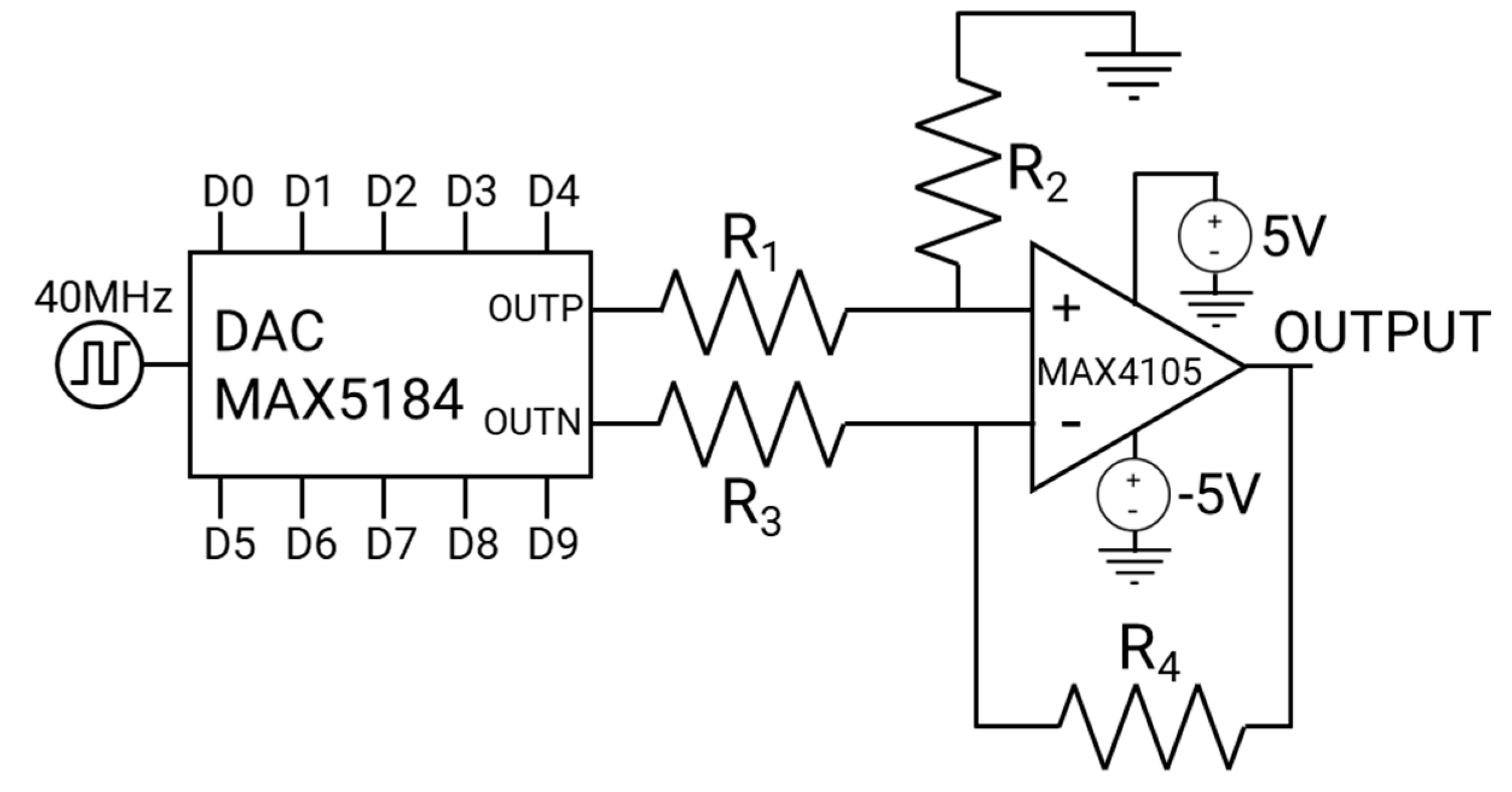

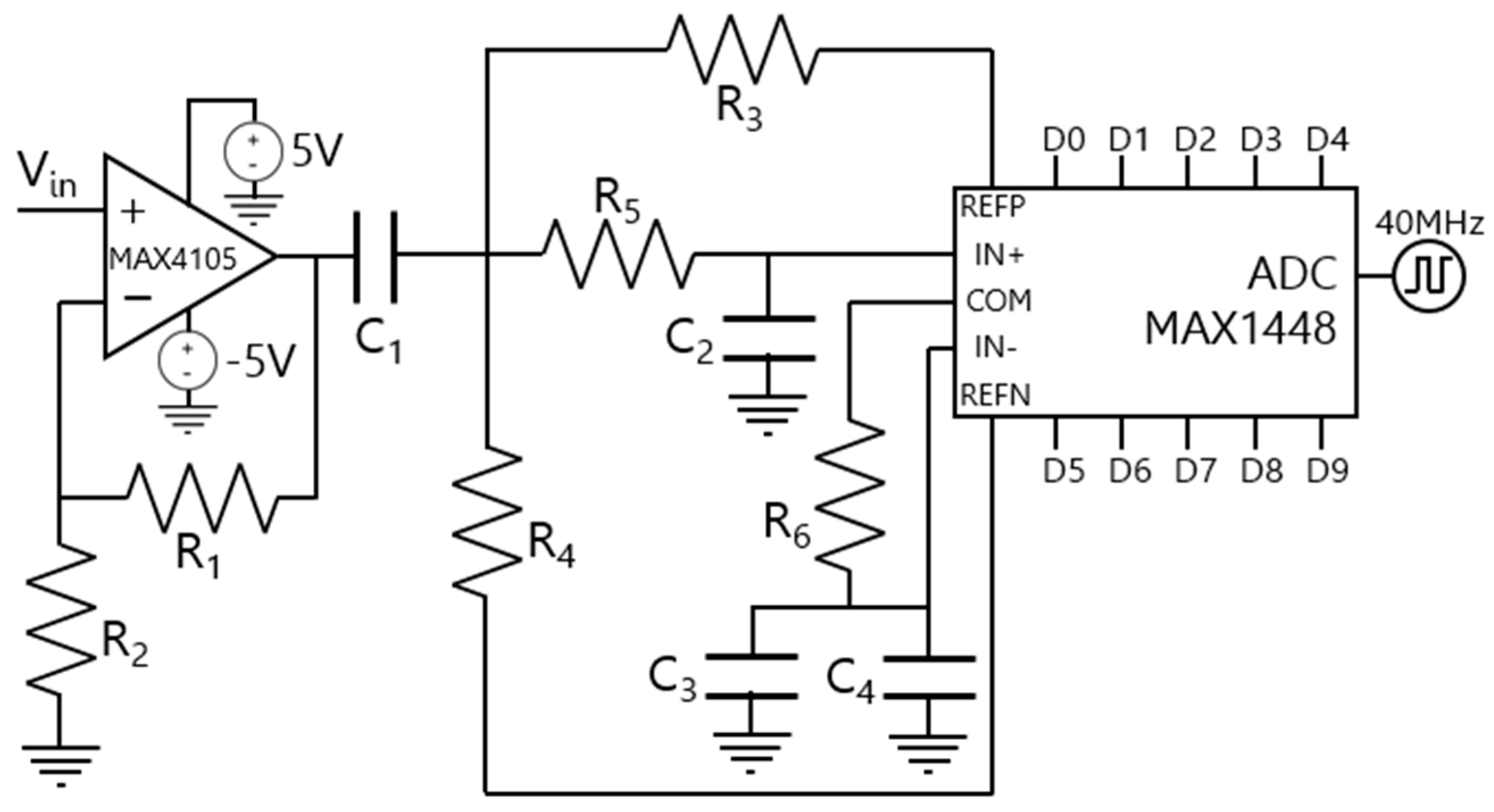

Interface Module for PD Driver/FPGA Connection

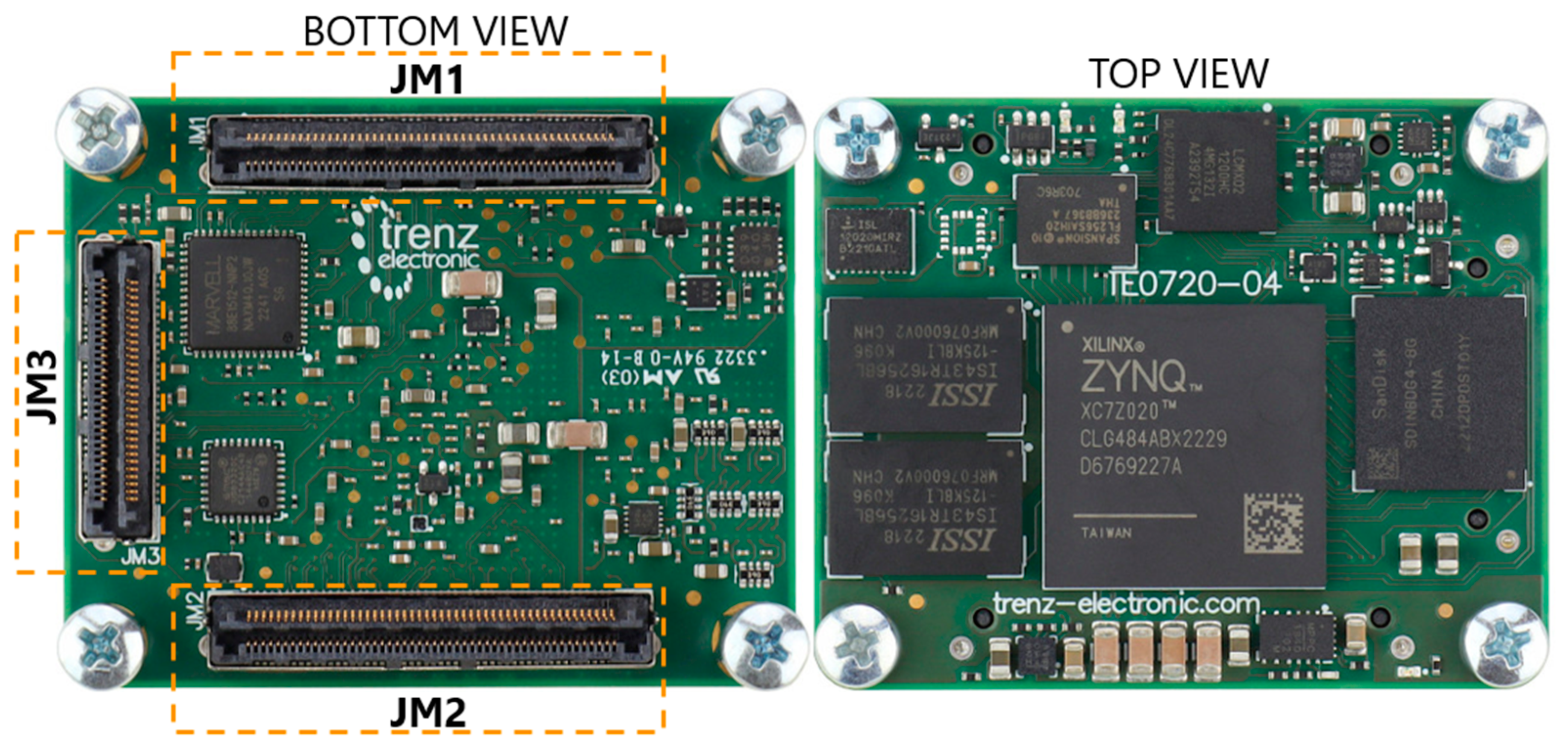

2.2.4. TE0720 SoC

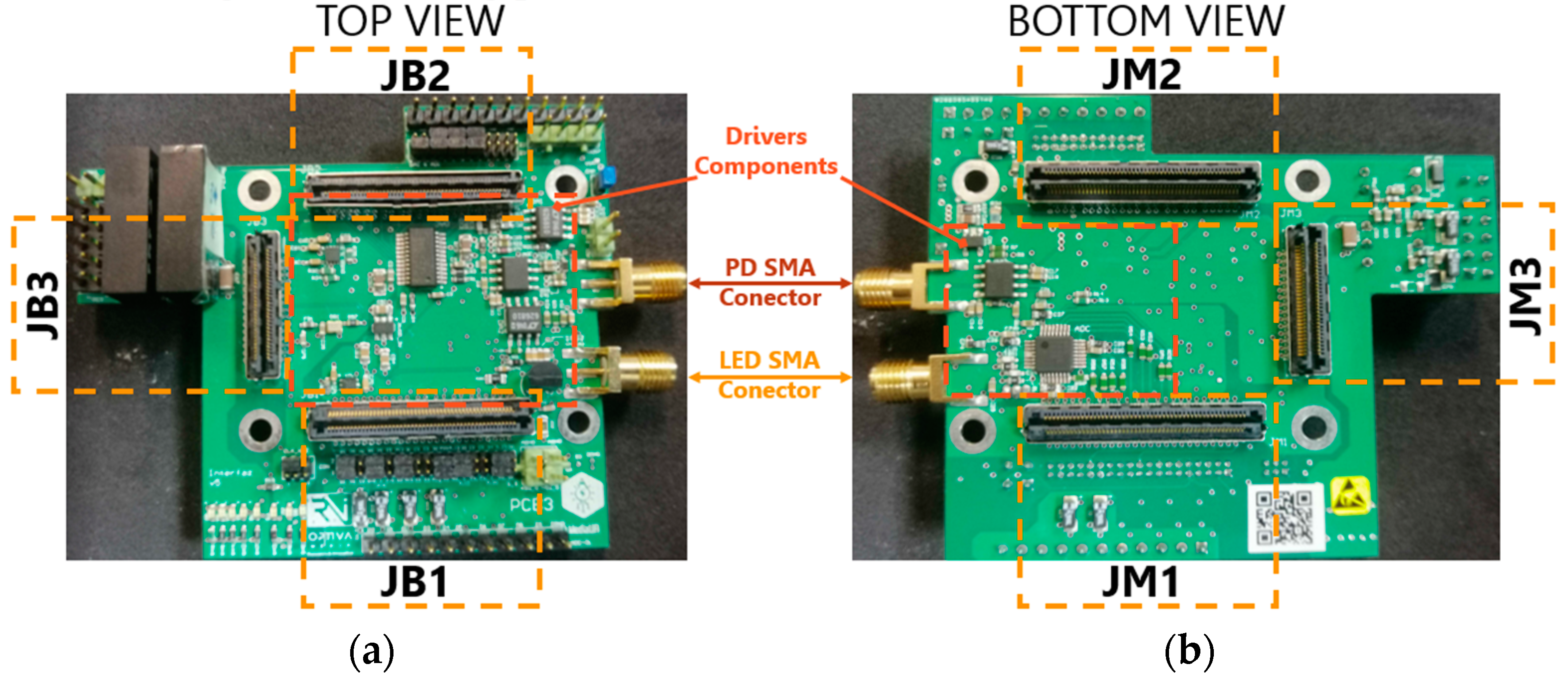

2.2.5. Merged Internal Interfaces in a PCB

2.2.6. External Interfaces

External Ports

2.3. Integration of the System’s Components

2.4. LiFi Router PCB Connections

2.5. USB Dongle PCB Connections

2.6. Experimental Set-Up and Testing Procedures

2.6.1. Testing Procedure for the Transmitter Block

2.6.2. Testing Procedure for the Receiver Block

2.6.3. Testing Procedure for the Transmitter and Receiver Block Located in the Same PCB

2.7. Deployment of the System in a Van

3. Results

3.1. Supply Voltages and Current Consumption

3.2. Energy Harvesting Performance

3.3. Electro-Optical Measurements of the Optical Links

3.3.1. Electro-Optical Measurements of the Visible Link

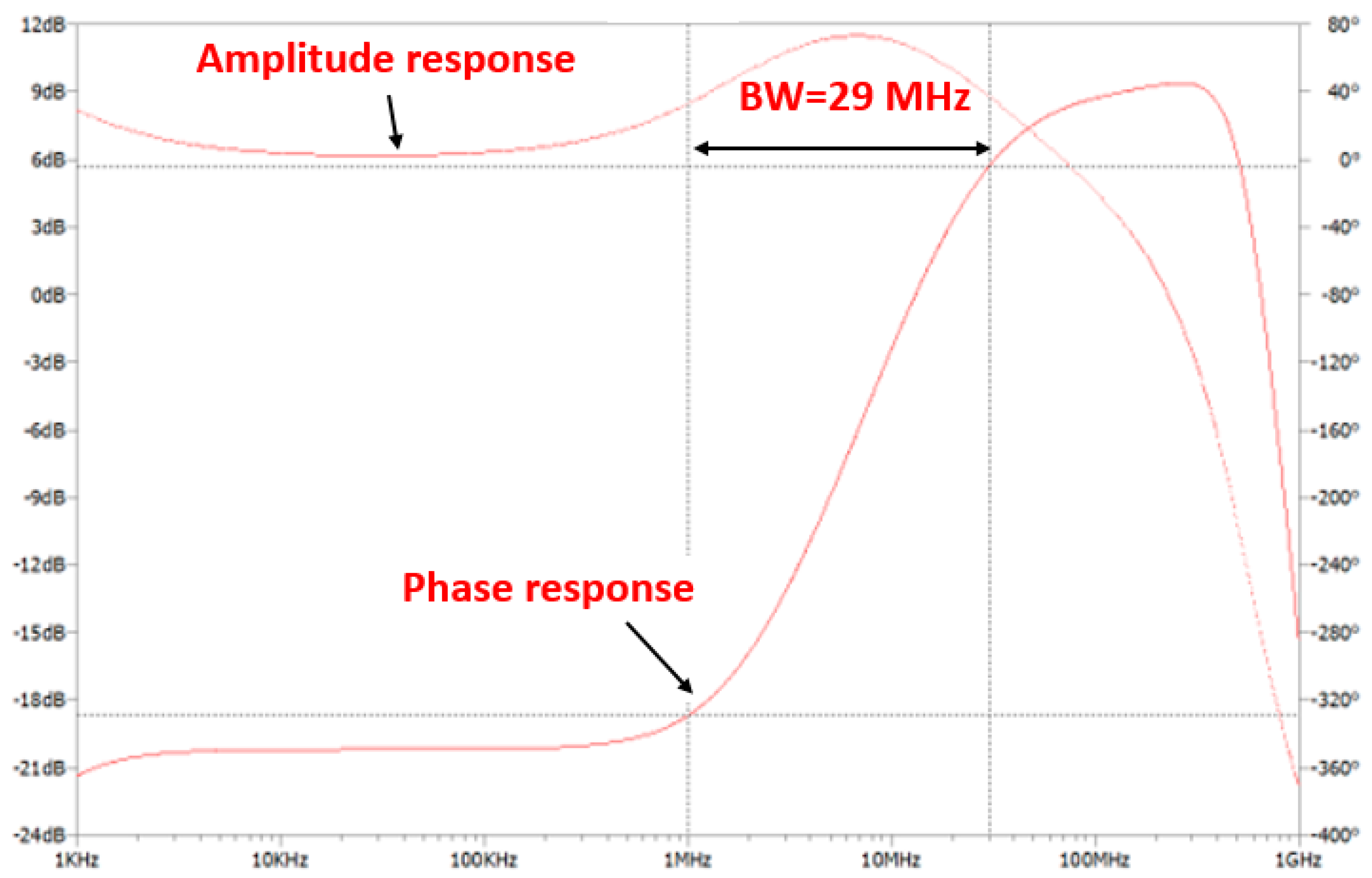

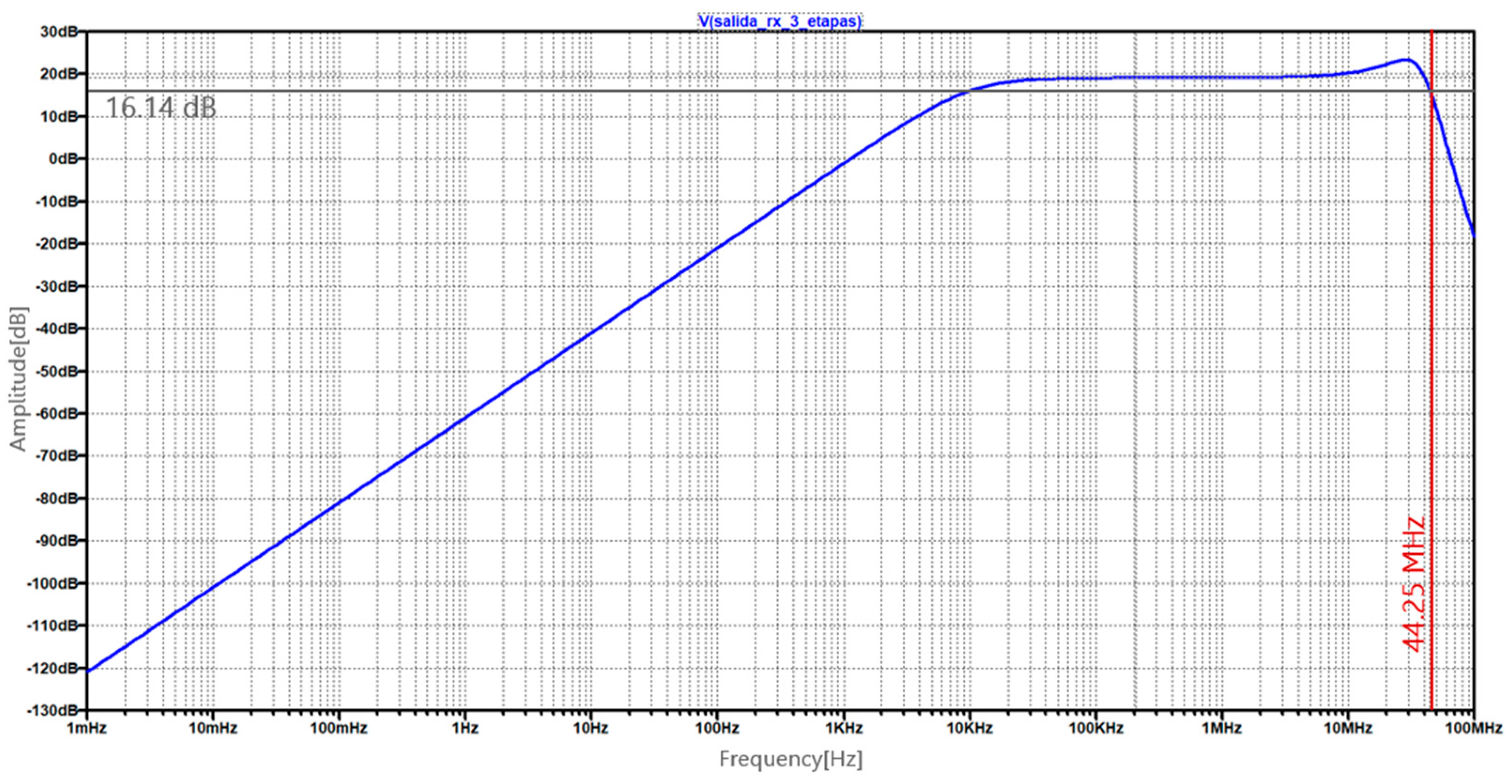

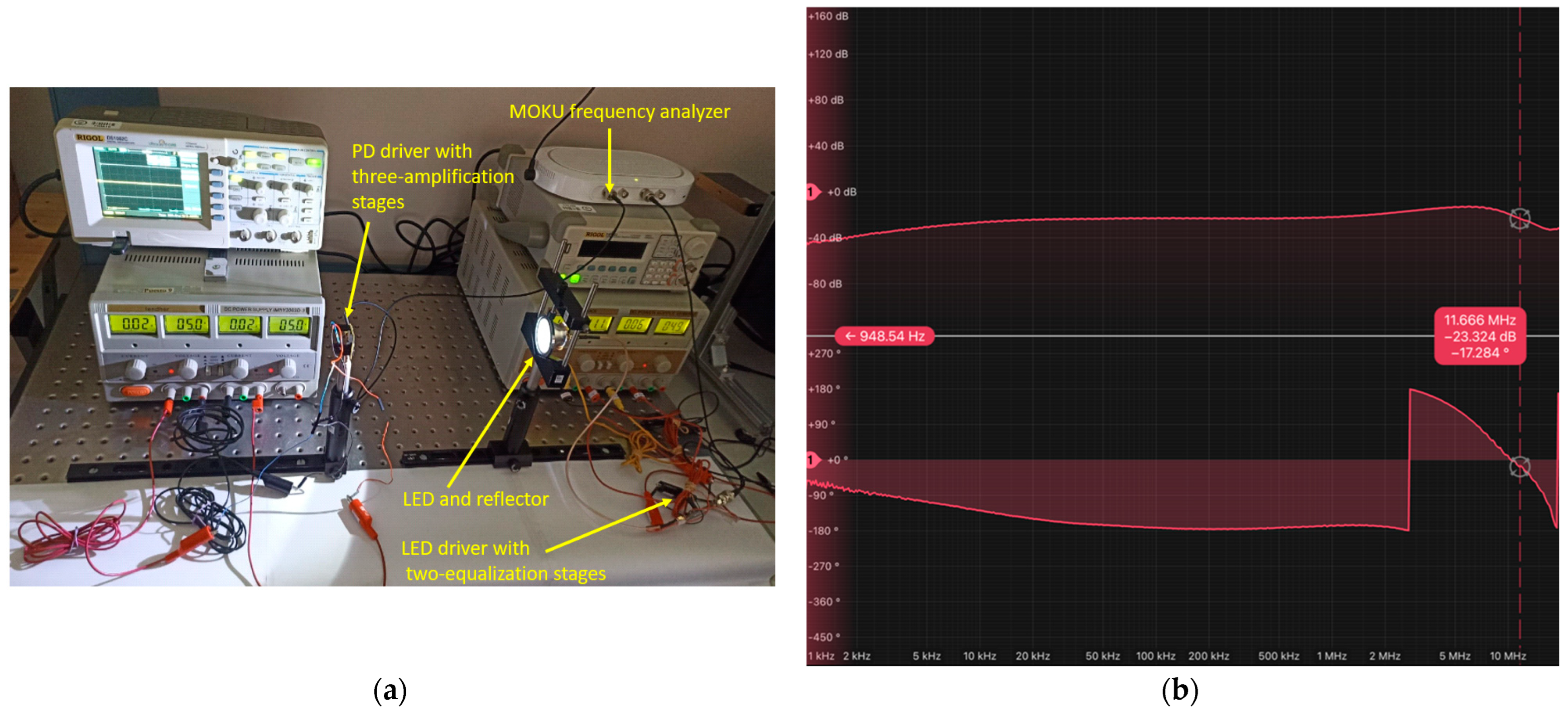

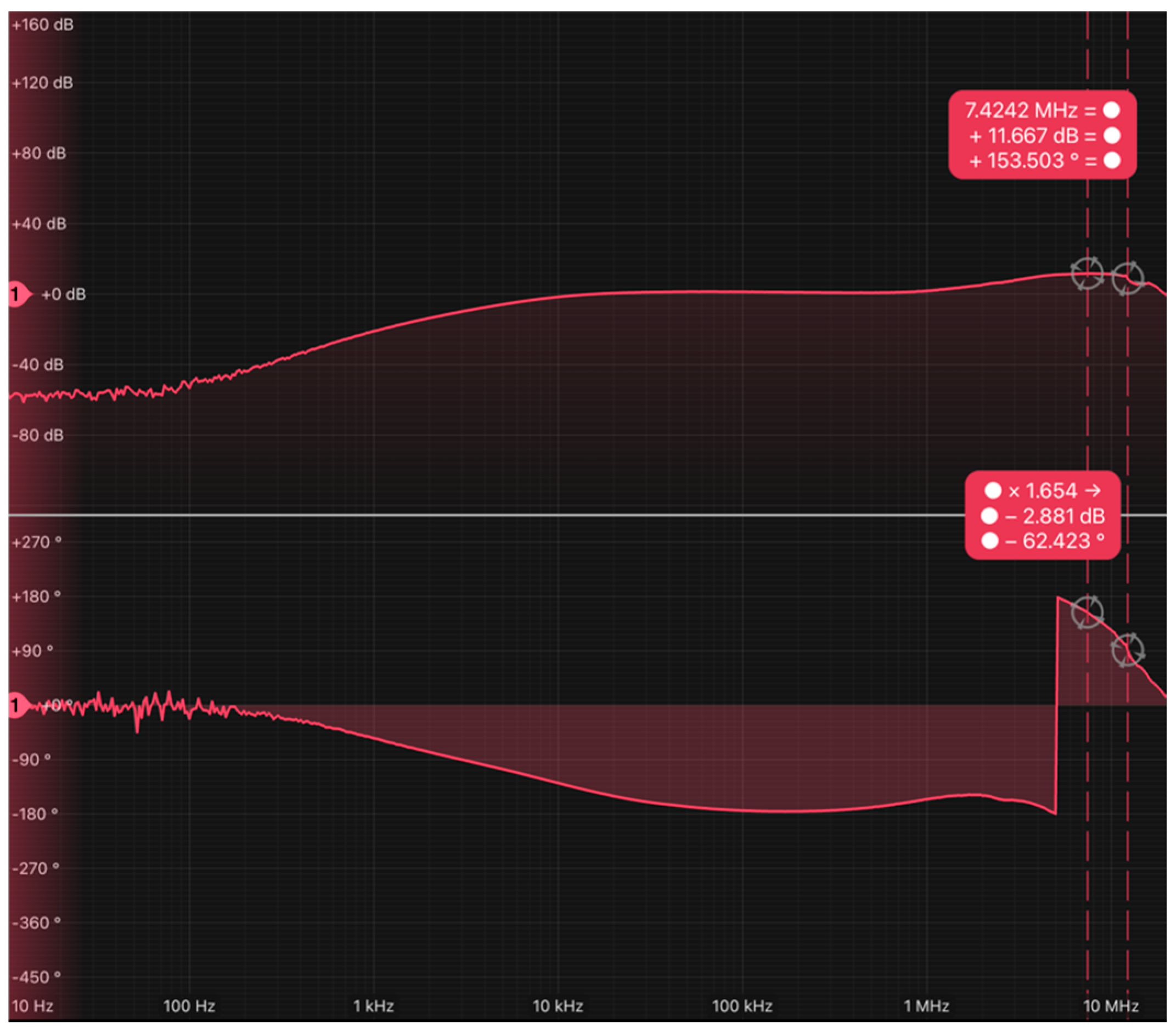

Bandwidth (BW) of the Visible Link

Illumination Level

Signal-to-Noise Ratio (SNR) of the Visible Link

3.3.2. Data Transmission Parameters of the Visible Link

Bit Rate of the Visible Link

Bit Error Rate (BER) and Packet Error Rate (PER) of the Visible Link

Optical Link Length of the Visible Link

3.3.3. Electro-Optical Measurements of the IR Link

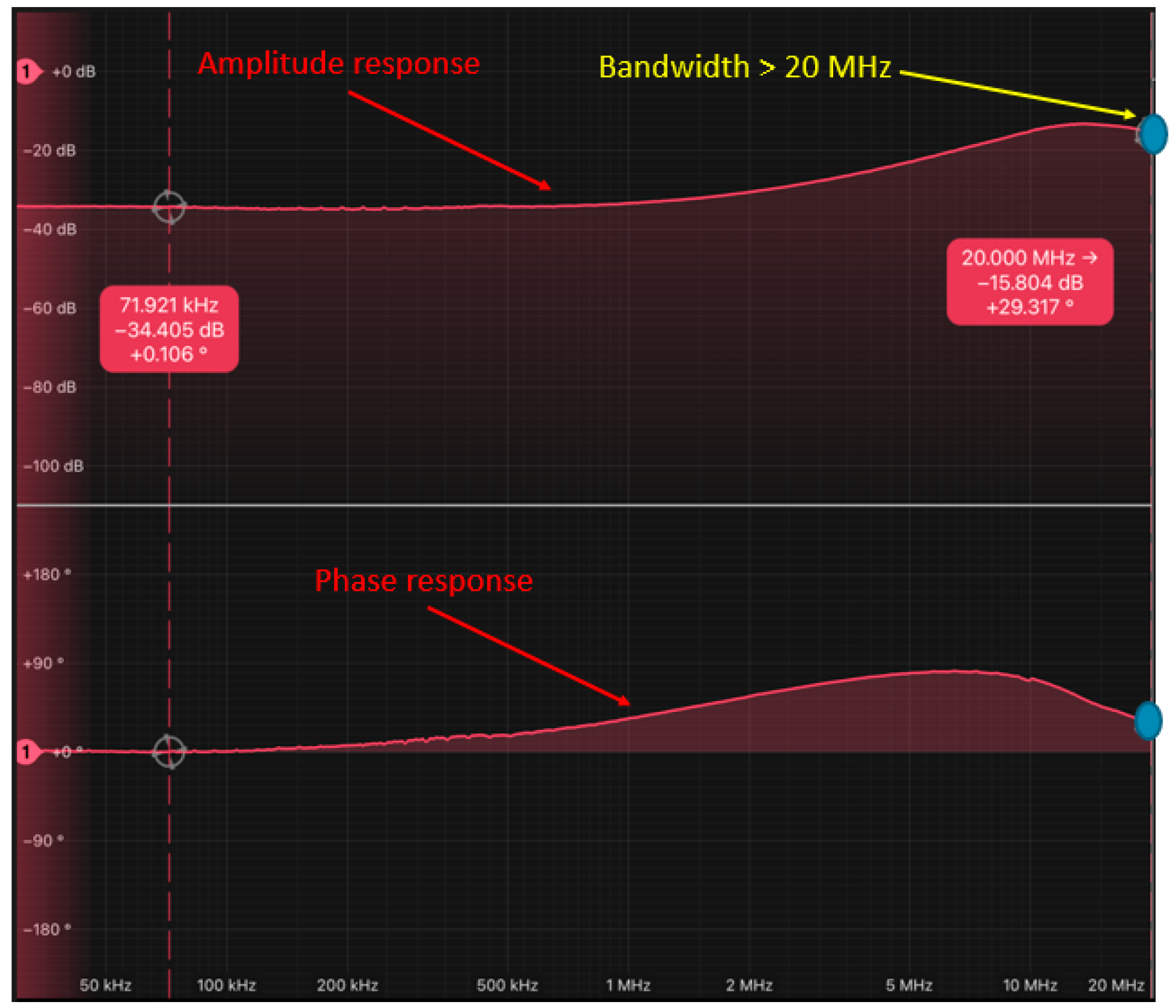

Bandwidth (BW) of the IR Link

Signal-to-Noise Ratio (SNR) of the IR Link

3.3.4. Data Transmission Parameters of the IR Link

Bit Rate of the IR Link

Bit Error Rate (BER) of the IR Link

Optical Link Length of the IR Link

4. Discussion and Conclusions

Supplementary Materials

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Han, L.; Peng, C.; Xu, Z. The Effect of Commuting Time on Quality of Life: Evidence from China. Int. J. Environ. Res. Public Health 2022, 20, 573. [Google Scholar] [CrossRef] [PubMed]

- January 2023 • News/Media Release • Bookmark +, ‘Study Reveals Shocking Number of People Who Prefer Public Transport Over Driving’. Available online: https://www.metro-magazine.com/10191071/study-reveals-shocking-number-of-people-who-prefer-public-transport-over-driving (accessed on 11 June 2024).

- EmodoInc, ‘CTV Trends in 2024’, Emodo. Available online: https://www.emodoinc.com/blog/connected-tv-trends/ (accessed on 11 June 2024).

- R. P. DCN Research VP-, ‘Understanding Consumer Choices in the Evolving TV Market’, Digital Content Next. Available online: https://digitalcontentnext.org/blog/2023/05/26/understanding-consumer-choices-in-the-evolving-tv-market/ (accessed on 11 June 2024).

- Jean, M.; Schulmeister, K.; Lund, D.J.; Stuck, B.E. Laser-induced corneal injury: Validation of a computer model to predict thresholds. Biomed. Opt. Express 2020, 12, 336–353. [Google Scholar] [CrossRef] [PubMed]

- Horton, L.; Brady, J.; Kincaid, C.M.; Torres, A.E.; Lim, H.W. The effects of infrared radiation on the human skin. Photodermatol. Photoimmunol. Photomed. 2023, 39, 549–555. [Google Scholar] [CrossRef] [PubMed]

- Son, D.K.; Cho, E.; Moon, I.; Ghassemlooy, Z.; Kim, S.; Lee, C.G. Simultaneous transmission of audio and video signals using visible light communications. EURASIP J. Wirel. Commun. Netw. 2013, 2013, 250. [Google Scholar] [CrossRef]

- Chen, M.; Guo, J.; Xu, X.; Liang, M. Real-Time Video Transmission of Visible Light Communication Based on LED. Int. J. Commun. Netw. Syst. Sci. 2017, 10, 58–68. [Google Scholar] [CrossRef]

- Badri, S.; Badri, S. Audio and Video Transmission Using Visible Light Transmission. In Proceedings of the 2019 IEEE International Conference on Advanced Networks and Telecommunications Systems (ANTS), Goa, India, 16–19 December 2019; pp. 1–4. [Google Scholar] [CrossRef]

- Yan, Y.; Ding, W.; Yang, H.; Song, J. The video transmission platform for The PLC and VLC integrated system. In Proceedings of the 2015 IEEE International Symposium on Broadband Multimedia Systems and Broadcasting, Ghent, Belgium, 17–19 June 2015; pp. 1–5. [Google Scholar] [CrossRef]

- Galisteo, A.; Juara, D.; Cordobes, H.; Giustiniano, D. Video Transmission Using Low-Cost Visible Light Communication. In Proceedings of the Twentieth ACM International Symposium on Mobile Ad Hoc Networking and Computing, in Mobihoc ’19, Catania, Italy, 2–5 July 2019; Association for Computing Machinery: New York, NY, USA, 2019; pp. 401–402. [Google Scholar] [CrossRef]

- Hocaoğlu, K.; Adar, A.; Arıkök, Y.A.; Rodoplu, V. Design of a Low-Cost Visible Light Communication (VLC) System for Music and Video Streaming. In Proceedings of the 2019 Innovations in Intelligent Systems and Applications Conference (ASYU), Izmir, Turkey, 31 October–2 November 2019; pp. 1–6. [Google Scholar] [CrossRef]

- Poonguhali, I.; Anusha, M.; Anciline, V.; Kavitha, D. Visible Light Communication for Video Transmission. 2020, 07, no. 03. International Research Journal of Engineering and Technology. Available online: https://www.irjet.net/archives/V7/i3/IRJET-V7I31087.pdf (accessed on 5 September 2024).

- Imran, M.; Bai, Y.; Javid, M. Data (Audio; Video, and Image) Transmission through Visible Light Communication: Li-Fi Technology. N. Am. Acad. Res. 2021, 4, 245–256. [Google Scholar] [CrossRef]

- Zhan, Y.; Sun, Y.; Shi, Z.; Yang, N.; Yang, L. Demonstration of 100Gbit/s Real-Time Ultra High Definition Video Transmission Over Free Space Optical Communication Links. In Proceedings of the 2021 Optical Fiber Communications Conference and Exhibition (OFC), San Francisco, CA, USA, 6–11 June 2021; pp. 1–3. [Google Scholar]

- He, C.; Chen, C. A Review of Advanced Transceiver Technologies in Visible Light Communications. Photonics 2023, 10, 648. [Google Scholar] [CrossRef]

- Cahyadi, W.A.; Chung, Y.H.; Ghassemlooy, Z.; Hassan, N.B. Optical Camera Communications: Principles, Modulations, Potential and Challenges. Electronics 2020, 9, 1339. [Google Scholar] [CrossRef]

- Kamalakis, T.; Ghassemlooy, Z.; Zvanovec, S.; Alves, L.N. Analysis and simulation of a hybrid visible-light/infrared optical wireless network for IoT applications. J. Opt. Commun. Netw. 2022, 14, 69–78. [Google Scholar] [CrossRef]

- Fonseca, D.F.; Mir, M.S.; Guzman, B.G.; Giustiniano, D. Visible light or infrared? Modulating LiFi for dual operation in the visible and infrared spectra. In Proceedings of the 2023 18th Wireless On-Demand Network Systems and Services Conference (WONS), Madonna di Campiglio, Italy, 30 January–1 February 2023; pp. 47–50. [Google Scholar] [CrossRef]

- Fuada, S.; Ahmed, F.; Adiono, T.; Kaewpukdee, A.; Mardiana, V.A. Linear LED driver design and its implementation for visible light communication applications. Optik 2023, 274, 170533. [Google Scholar] [CrossRef]

- Wang, K.; Song, T.; Wang, Y.; Fang, C.; He, J.; Nirmalathas, A.; Lim, C.; Wong, E.; Kandeepan, S. Evolution of Short-Range Optical Wireless Communications. J. Lightwave Technol. 2023, 41, 1019–1040. [Google Scholar] [CrossRef]

- T. E. GmbH, ‘TE0720–ZynqTM SoC’, Trenz Electronic GmbH Online Shop (EN). Available online: https://shop.trenz-electronic.de/en/Products/Trenz-Electronic/TE07XX-Zynq-SoC/TE0720-Zynq-SoC/ (accessed on 15 April 2024).

- ‘LUW CN7N-KYLX-EMKM ams OSRAM|Mouser’, Mouser Electronics. Available online: https://www.mouser.es/ProductDetail/720-LUWCN7NLXEMKM46Z (accessed on 20 March 2024).

- L130-2780002011001 Lumileds|Mouser’, Mouser Electronics. Available online: https://www.mouser.es/ProductDetail/Lumileds/L130-2780002011001?qs=Rt2YTNbomKgTSpfP%2FjCvlA%3D%3D (accessed on 6 May 2024).

- Perlaza, J.S.B.; Zafra, J.C.T.; Céspedes, M.M.; Martínez-Sarriegui, I.; del Valle, C.I.; Pena, J.M.S. An Enhanced Method for Dynamic Characterization of High-Power LEDs for Visible Light Communication Applications. Electronics 2022, 11, 292. [Google Scholar] [CrossRef]

- ‘TN0110N3-G’, DigiKey Electronics. Available online: https://www.digikey.es/en/products/detail/microchip-technology/TN0110N3-G/4902371 (accessed on 14 May 2024).

- ‘Frequency Response Analyzer’, Liquid Instruments. Available online: https://www.liquidinstruments.com/products/integrated-instruments/frequency-response-analyzer/ (accessed on 1 March 2024).

- Thorlabs—PDA10A2 Si Fixed Gain Detector, 200–1100 nm, 150 MHz BW, 0.8 mm2, Universal 8-32/M4 Taps. Available online: https://www.thorlabs.com (accessed on 15 April 2024).

- Mavolux 5032c USB. Available online: https://www.fotoboom.com/gossen-mavolux-5032c-usb-certificado-enac-76948 (accessed on 20 March 2024).

- ‘HSDL-4250 Lite-On|Mouser’, Mouser Electronics. Available online: https://www.mouser.es/ProductDetail/Lite-On/HSDL-4250?qs=hH%252BOa0VZEiDpY4PdG7bROQ%3D%3D (accessed on 15 April 2024).

- ‘BP 104 SR-Z ams OSRAM|Mouser’, Mouser Electronics. Available online: https://www.mouser.es/ProductDetail/720-BP104SR-Z (accessed on 20 March 2024).

- ‘LTC6268IS6-10#TRMPBF Analog Devices|Mouser’, Mouser Electronics. Available online: https://www.mouser.es/ProductDetail/Analog-Devices/LTC6268IS6-10TRMPBF?qs=oahfZPh6IAK%2Fgwt4Y8oAdg%3D%3D (accessed on 15 May 2024).

- ‘LTC6253CDC#TRMPBF Analog Devices|Mouser’, Mouser Electronics. Available online: https://www.mouser.es/ProductDetail/Analog-Devices/LTC6253CDCTRMPBF?qs=hVkxg5c3xu%252BJ1jwIEDenzQ%3D%3D (accessed on 16 May 2024).

- MAX5184 Datasheet and Product Info|Analog Devices. Available online: https://www.analog.com/en/products/max5184.html (accessed on 1 February 2024).

- MAX4105 Datasheet and Product Info|Analog Devices. Available online: https://www.analog.com/en/products/max4105.html (accessed on 5 February 2024).

- TCXO HCMOS SMD ECS-TXO-2520—ECS|DigiKey. Available online: https://www.digikey.com/es/product-highlight/e/ecs/ecs-txo-2520-hcmos-smd-tcxo (accessed on 9 February 2024).

- Zynq-7000 SoC Data Sheet: Overview (DS190). 2018. Available online: https://www.mouser.com/datasheet/2/903/ds190-Zynq-7000-Overview-1595492.pdf (accessed on 5 September 2024).

- MAX1448 Datasheet and Product Info|Analog Devices. Available online: https://www.analog.com/en/products/max1448.html (accessed on 8 February 2024).

- Wang, S.-F.; Chen, H.-P.; Ku, Y.; Zhong, M.-X. Analytical Synthesis of High-Pass, Band-Pass and Low-Pass Biquadratic Filters and its Quadrature Oscillator Application Using Current-Feedback Operational Amplifiers. IEEE Access 2021, 9, 13330–13343. [Google Scholar] [CrossRef]

- Rezmeriță, G.; Bordianu, A.; Pușcașu, S. Low-Pass Filter Analysis. In Proceedings of the 2023 13th International Symposium on Advanced Topics in Electrical Engineering (ATEE), Bucharest, Romania, 23–25 March 2023; pp. 1–4. [Google Scholar] [CrossRef]

- Zybo Z7 Reference Manual—Digilent Reference. Available online: https://digilent.com/reference/programmable-logic/zybo-z7/reference-manual (accessed on 20 March 2024).

- ‘TE0720-03-1CFA Trenz Electronic|Mouser’, Mouser Electronics. Available online: https://www.mouser.es/ProductDetail/Trenz-Electronic/TE0720-03-1CFA?qs=EBDBlbfErPyUlVPsc1gYaA%3D%3D (accessed on 9 April 2024).

- Béchadergue, B.; Shen, W.-H.; Tsai, H.-M. Comparison of OFDM and OOK modulations for vehicle-to-vehicle visible light communication in real-world driving scenarios. Ad Hoc Netw. 2019, 94, 101944. [Google Scholar] [CrossRef]

- Ghimire, J.S.B. Indoor Positioning using OFDM-based Visible Light Communications Systems. In Proceedings of the International Conference on Indoor Positioning and Indoor Navigation (IPIN), Nantes, France, 24–27 September 2018. [Google Scholar]

- ‘61500814221 Wurth Elektronik|Mouser’, Mouser Electronics. Available online: https://www.mouser.es/ProductDetail/Wurth-Elektronik/61500814221?qs=rS3zZhy2AQOW6FITBQg0lg%3D%3D (accessed on 12 April 2024).

- ‘LSHM-130-04.0-L-DV-A-S-TR Samtec|Mouser’, Mouser Electronics. Available online: https://www.mouser.es/ProductDetail/Samtec/LSHM-130-04.0-L-DV-A-S-TR?qs=PB6%2FjmICvI2ZbBy9gGXpxQ%3D%3D (accessed on 9 April 2024).

- ‘88E1512-A0-NNP2I000 Marvell|Mouser’, Mouser Electronics. Available online: https://www.mouser.es/ProductDetail/Marvell/88E1512-A0-NNP2I000?qs=vdi0iO8H4N0XzuXqBRxTqg%3D%3D (accessed on 12 April 2024).

- ‘LSHM-150-04.0-L-DV-A-S-K-TR Samtec|Mouser’, Mouser Electronics. Available online: https://www.mouser.es/ProductDetail/Samtec/LSHM-150-04.0-L-DV-A-S-K-TR?qs=PB6%2FjmICvI0kfKxky75CoQ%3D%3D (accessed on 9 April 2024).

- ‘USB3320C-EZK Microchip Technology|Mouser’, Mouser Electronics. Available online: https://www.mouser.es/ProductDetail/Microchip-Technology/USB3320C-EZK?qs=pA5MXup5wxEV58aAJyVneA%3D%3D (accessed on 12 April 2024).

- Digilent 410-299, para JTAG-HS3, Xilinx Tool|RS. Available online: https://es.rs-online.com/web/p/accesorios-para-kits-de-desarrollo/1346435?cm_mmc=ES-PLA-DS3A-_-google-_-CSS_ES_ES_Pmax_Test-_--_-1346435&matchtype=&&gad_source=1&gclid=CjwKCAjwt-OwBhBnEiwAgwzrUjK6jSBzePz6_EWYybe1ZfAuLM-_CRGlghtbyhFcrAAWRSxMc_LLQxoCXssQAvD_BwE&gclsrc=aw.ds (accessed on 12 April 2024).

- ‘TTL-232RG-VREG3V3-WE FTDI|Mouser’, Mouser Electronics. Available online: https://www.mouser.es/ProductDetail/FTDI/TTL-232RG-VREG3V3-WE?qs=D1%2FPMqvA103YESiuBsLf1Q%3D%3D (accessed on 12 April 2024).

- 61301011121—Conector de Pines, Placa a Placa, 2.54 mm, 1 Filas, 10 Contactos, Agujero Pasante, WR-PHD. Available online: https://es.farnell.com/wurth-elektronik/61301011121/macho-2-54-mm-pin-10-v-as/dp/1841229 (accessed on 15 April 2024).

- ‘PDQE20-Q24-S12-D CUI Inc.|Mouser’, Mouser Electronics. Available online: https://www.mouser.es/ProductDetail/CUI-Inc/PDQE20-Q24-S12-D?qs=T3oQrply3y%252BFQp9j4U5RaQ%3D%3D (accessed on 12 April 2024).

- Cho, J.; Xie, C.; Winzer, P.J. Analysis of soft-decision FEC on non-AWGN channels. Opt. Express 2012, 20, 7915–7928. [Google Scholar] [CrossRef] [PubMed]

- Winzer, P.J.; Pfennigbauer, M.; Essiambre, R.-J. Coherent Crosstalk in Ultradense WDM Systems. IEEE J. Light. Technol. 2005, 23, 1734. [Google Scholar] [CrossRef]

- Perlaza, J.S.B.; Domínguez, R.L.; Heredia, E.S.M. Phase Characterization and Correction in a Hardware Implementation of an OFDM-Based System for VLC Applications. IEEE Photonics J. 2023, 15, 1–7. [Google Scholar] [CrossRef]

| Input | Equalizer 1 | Amplification Stage 1 | Equalizer 2 | Amplification Stage 2 | Current Source | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| R5 | 200 Ω | R1 | 3.9 kΩ | R6 | 20 kΩ | R3 | 1 kΩ | R10 | 1 kΩ | R13 | 10.7 kΩ |

| C3 | 1 pF | C1 | 22 pF | R7 | 1 kΩ | C2 | 25 pF | R11 | 12 kΩ | R14 | 5 kΩ |

| Vin(AC) | 0.8Vpp | R2 | 1 kΩ | R8 | 500 Ω | R4 | 50 Ω | R12 | 1 kΩ | R15 | 5.5 Ω |

| Vin (DC) | 0 V | C4 | 56 nF | C6 | 56 nF | C6 | 56 nF | TRT | TN0110N3 | ||

| Ampl | LTC6268-10 | Ampl | LTC6268-10 | Vdd | 12 V | ||||||

| R9 | 200 Ω | ||||||||||

| C5 | not mounted | ||||||||||

| Amplification Stage 1 | Amplification Stage 2 | Amplification Stage 3 | |||

|---|---|---|---|---|---|

| R1 | 5 kΩ | R4 | 200 Ω | R8 | 900 Ω |

| R2 | 5 kΩ | C5 | 100 nF | R9 | 100 Ω |

| C4 | 56 nF | R7 | 1 kΩ | Amplifier | LTC6253 |

| R7 | 15 kΩ | R5 | 16 kΩ | ||

| C3 | 0.25 pF | R6 | 1 kΩ | ||

| Amplifier | LTC6253 | C6 | 100 nF | ||

| Amplifier | LTC6253 | ||||

| R1 | 402 Ω | R2 | 1 kΩ | DAC | MAX5184 |

| R3 | 402 Ω | R4 | 1 kΩ | Amplifier | MAX4105 |

| Oscillator | TXO crystal 40 MHz |

| R1 | 100 Ω | R3 | 1 kΩ | C2 | 22 pF |

| R2 | 100 Ω | R4 | 1 kΩ | R6 | 50 Ω |

| C1 | 100 nF | R5 | 50 Ω | C3 | 22 pF |

| ADC | MAX1448 | Amplifier | MAX4105 | C4 | 100 nF |

| Oscillator | TXO crystal 40 MHz |

| Modulation and Codification | MB/s | Mbps |

|---|---|---|

| OOK (8b10b) | 1.91 | 15.25 |

| OFDM (BPSK, R = 1) | 0.71 | 5.69 |

| OFDM (QPSK, R = 1) | 1.41 | 11.25 |

| ) | 1.23 | 9.83 |

| ) | 1.05 | 8.44 |

| ) | 0.71 | 5.69 |

| Distance (cm) | BER | Errors per Packet | Number of Packets with Errors | PER |

|---|---|---|---|---|

| 62.5 (1) | 3 | 48 | 0.1875 | |

| 72.5 (1) | 3 | 93 | 0.3632 | |

| 82.5 (2) | 5 | 124 | 0.4843 | |

| 92.5 (2) | 8 | 160 | 0.625 | |

| 102.5 (2) | 28 | 220 | 0.8593 |

| AC | Alternating Current | PCB | Printed Circuit Board |

| ADC | Analog-to-Digital Converter | PD | Photodiode |

| AlGaAs | Aluminum Gallium Arsenide | PER | Packet Error Rate |

| APD | Avalanche Photodiode | PHY | Physical |

| ARM | Advanced RISC Machine | PIN | Positive–Intrinsic–Negative |

| BW | Bandwidth | QSPI | Quad Serial Peripheral Interface |

| DAC | Digital-to-Analog Converter | QPSK | Quadrature Phase Shift Keying |

| DC | Direct Current | RF | Radio-Frequency |

| DDR3 | Double Data Rate version 3 | Rx | Receiver |

| FPGA | Field-Programmable Gate Array | RISC | Reduced Instruction Set Computer |

| FSO | Free Space Optical | SD | Secure Digital |

| GBW | Gain-Bandwidth | SDRAM | Synchronous Dynamic Random-Access Memory |

| IC | Integrated Circuit | SIMO | Single-Input Multiple-output |

| IFFT | Inverse Fast Fourier Transform | SMA | Subminiature version A |

| ILA | Integrated Logic Analyzer | SNR | Signal-to-Noise Ratio |

| IoT | Internet-of-Things | SoC | System On a Chip |

| IR | Infrared | TTL | Transistor–Transistor Logic |

| JTAG | Joint Test Action Group | TV | Television |

| LAN | Local Area Network | Tx | Transmitter |

| LED | Light-Emitting Diode | UART | Universal Asynchronous Receiver–Transmitter |

| LiFi | Light Fidelity | UHD | Ultra-High Definition |

| LoRa | Long-Range | USB | Universal Serial Bus |

| MAC | Medium Access Control | VLC | Visible-Light Communication |

| OFDM | Orthogonal Frequency-Division Multiplexing | WAN | Wide Area Network |

| OOK | On–Off Keying | WiFi | Wireless Fidelity |

| OWC | Optical Wireless Communication |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

del Valle Morales, C.I.; Betancourt Perlaza, J.S.; Torres Zafra, J.C.; Martinez-Sarriegui, I.; Sánchez-Pena, J.M. Optoelectronics Interfaces for a VLC System for UHD Audio-Visual Content Transmission in a Passenger Van: HW Design. Sensors 2024, 24, 5829. https://doi.org/10.3390/s24175829

del Valle Morales CI, Betancourt Perlaza JS, Torres Zafra JC, Martinez-Sarriegui I, Sánchez-Pena JM. Optoelectronics Interfaces for a VLC System for UHD Audio-Visual Content Transmission in a Passenger Van: HW Design. Sensors. 2024; 24(17):5829. https://doi.org/10.3390/s24175829

Chicago/Turabian Styledel Valle Morales, Carlos Iván, Juan Sebastián Betancourt Perlaza, Juan Carlos Torres Zafra, Iñaki Martinez-Sarriegui, and José Manuel Sánchez-Pena. 2024. "Optoelectronics Interfaces for a VLC System for UHD Audio-Visual Content Transmission in a Passenger Van: HW Design" Sensors 24, no. 17: 5829. https://doi.org/10.3390/s24175829

APA Styledel Valle Morales, C. I., Betancourt Perlaza, J. S., Torres Zafra, J. C., Martinez-Sarriegui, I., & Sánchez-Pena, J. M. (2024). Optoelectronics Interfaces for a VLC System for UHD Audio-Visual Content Transmission in a Passenger Van: HW Design. Sensors, 24(17), 5829. https://doi.org/10.3390/s24175829