Design and Implementation of a Low-Power Biopotential Amplifier in 28 nm CMOS Technology with a Compact Die-Area of 2500 μm2 and an Ultra-High Input Impedance

Abstract

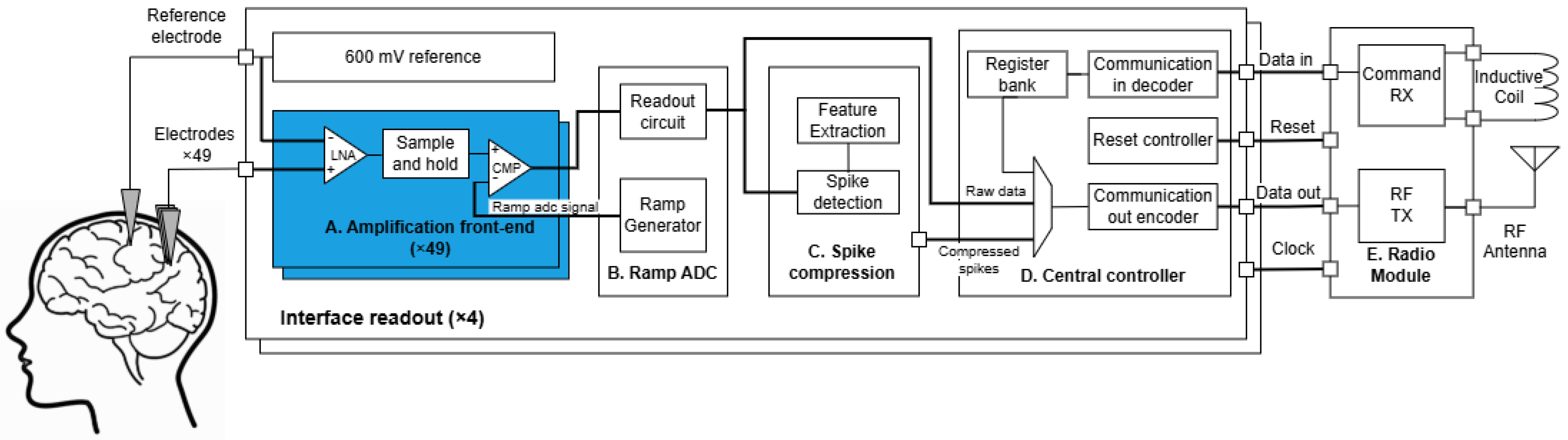

:1. Introduction

2. System Requirements

3. Review of the State of the Art

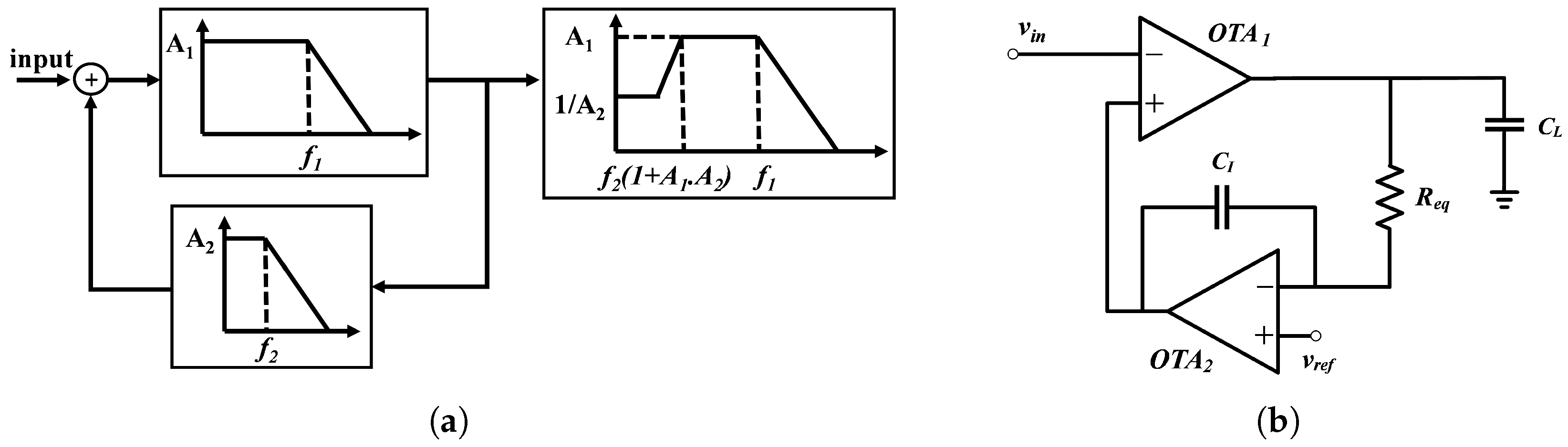

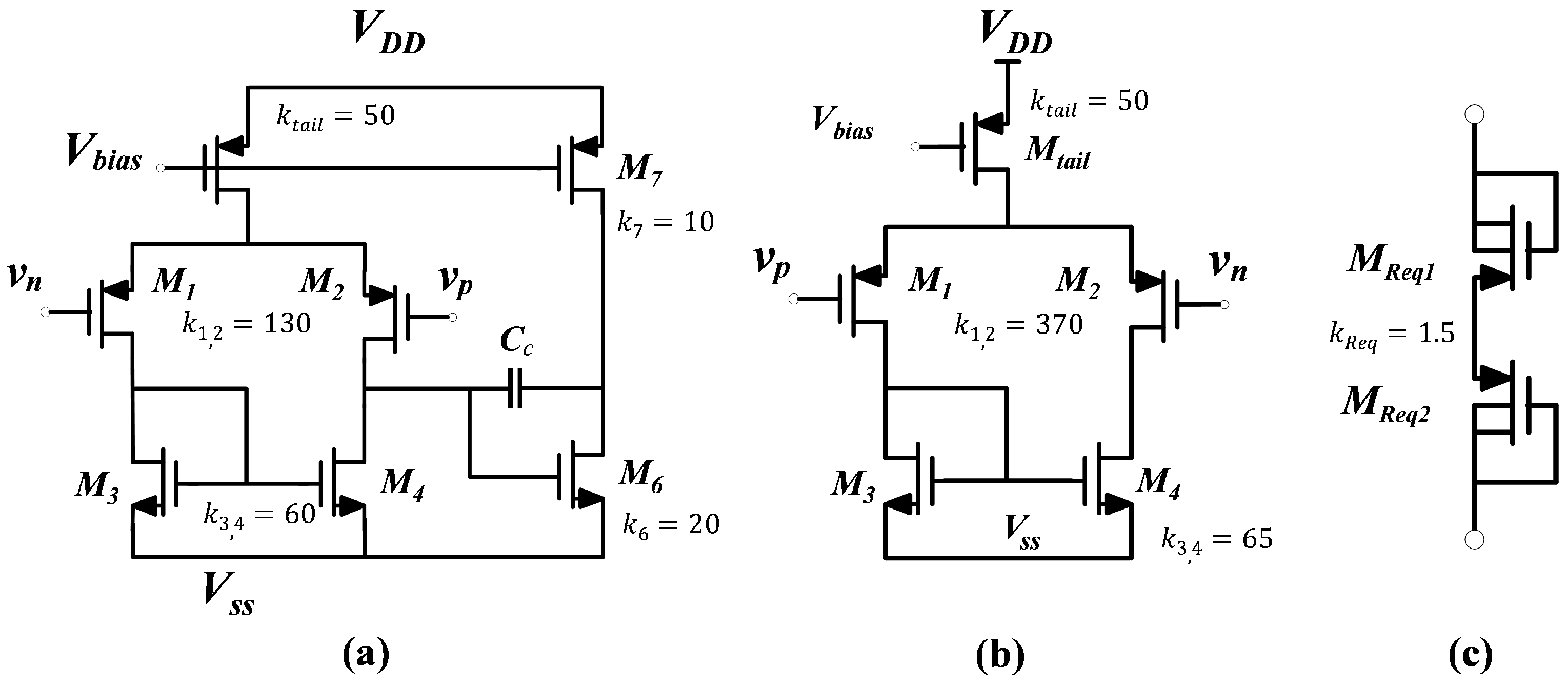

4. Bioamplifier Circuit Design

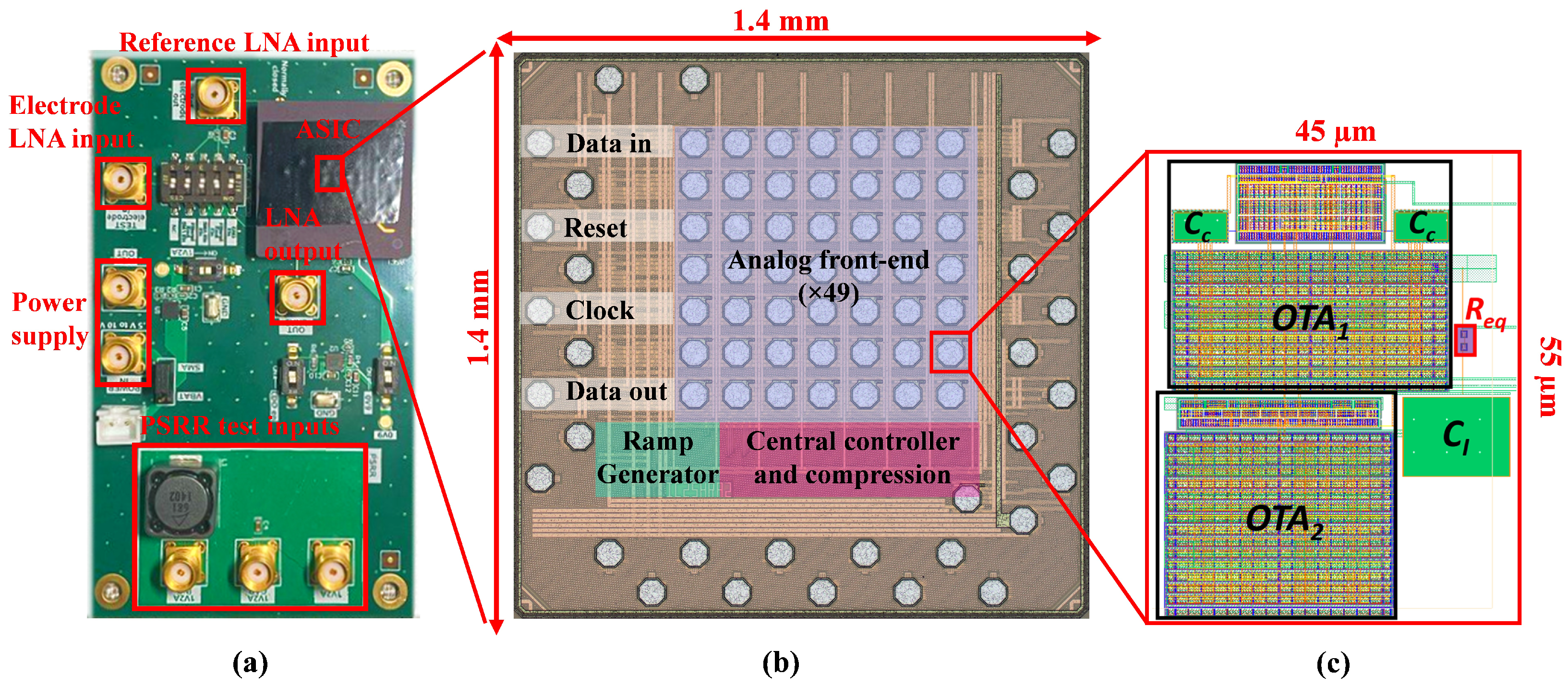

5. Methods

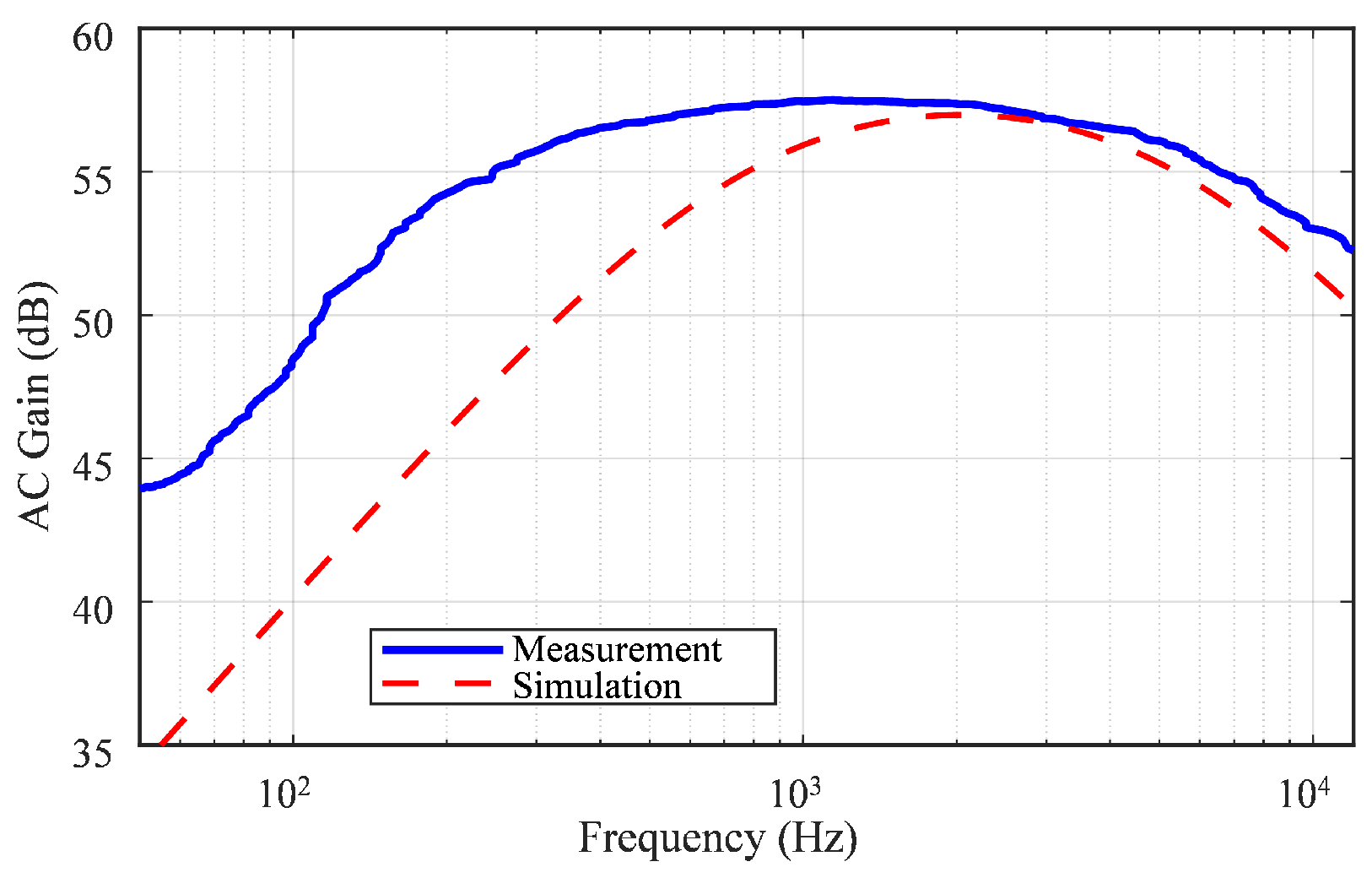

5.1. Frequency Bandwidth and Mid-Band Gain

5.2. CMRR

5.3. Power Supply Rejection Ratio (PSRR)

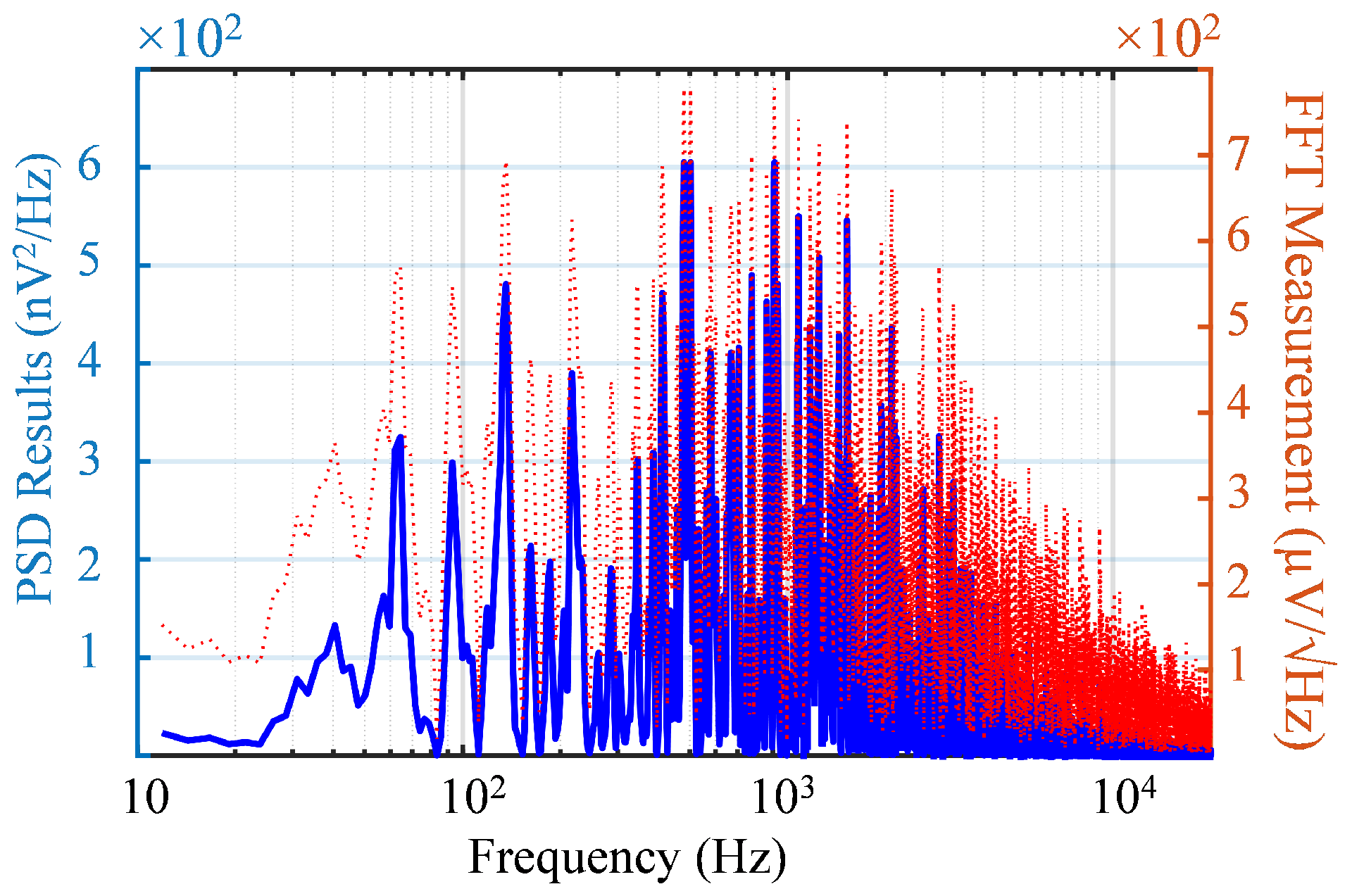

5.4. Input-Referred Noise

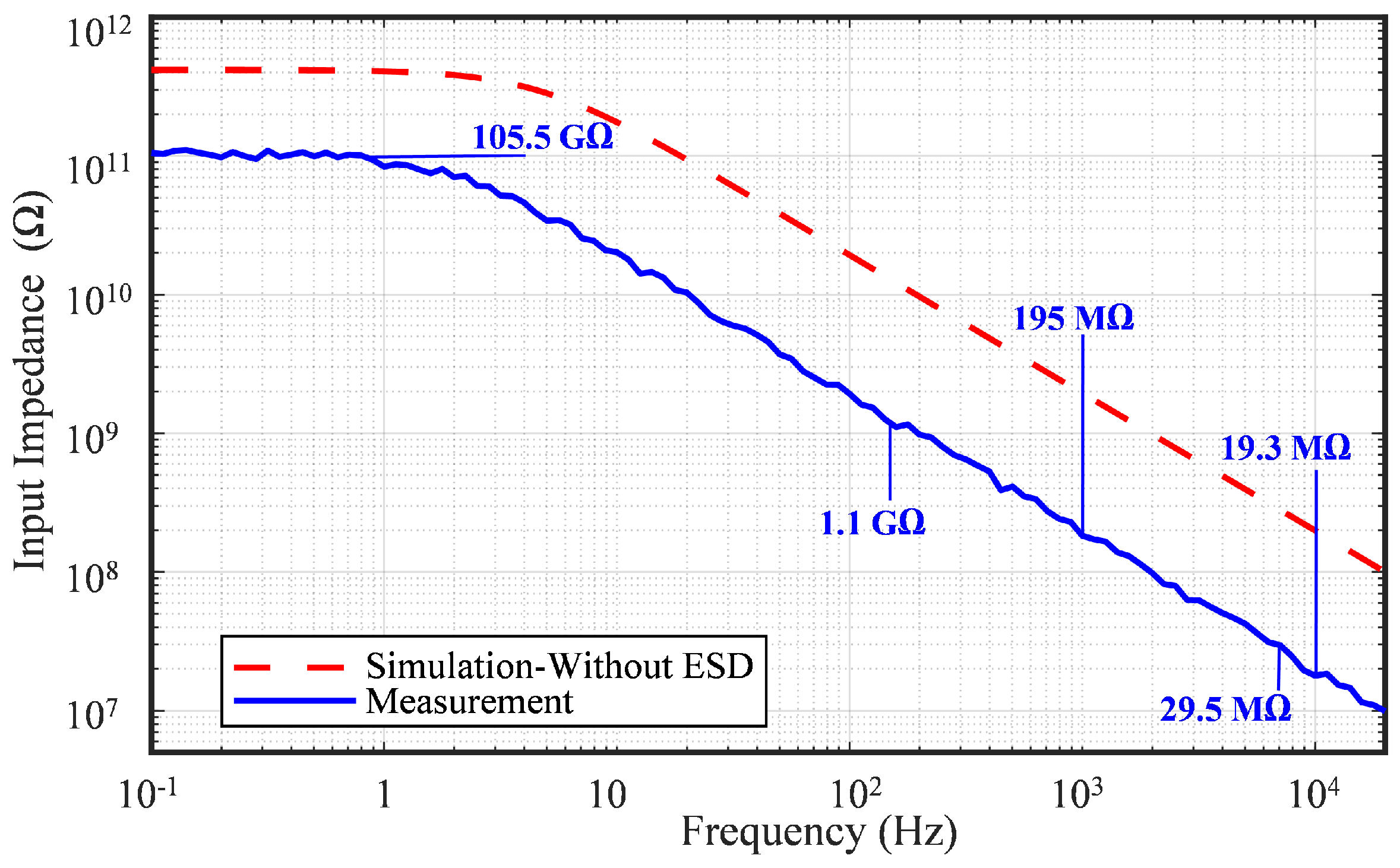

5.5. Input Impedance

5.6. Electrode Offset Tolerance

5.7. Linearity

5.8. Efficiency

6. Results

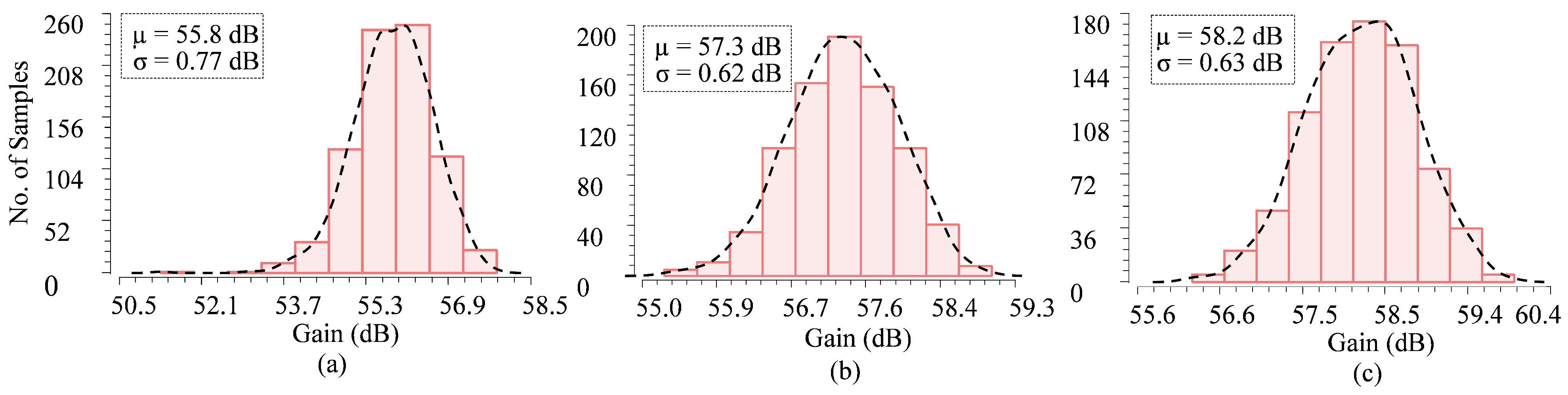

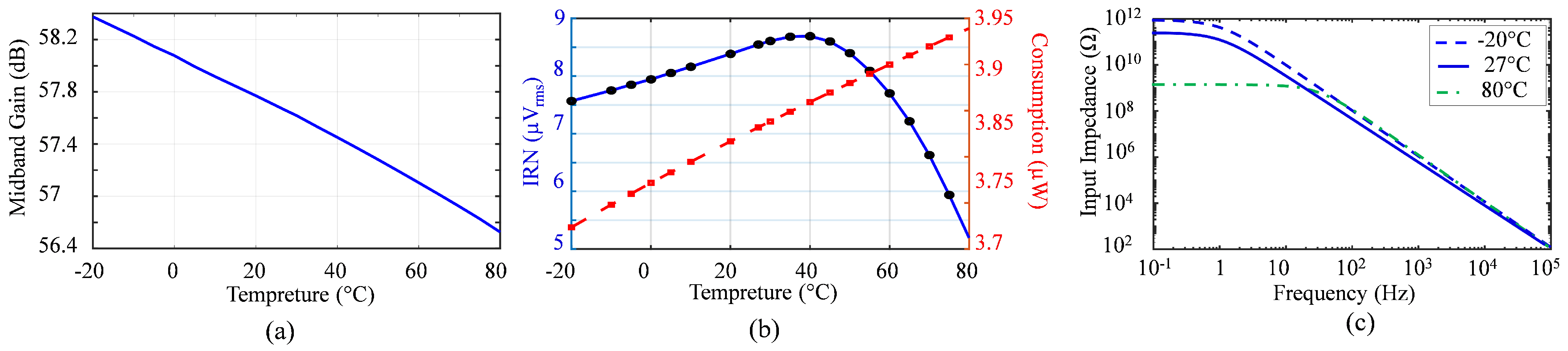

6.1. Frequency Bandwidth and Mid-Band Gain

6.2. CMRR

6.3. PSRR

6.4. Noise Measurement

6.5. Input Impedance

6.6. Electrode Offset Tolerance

6.7. Linearity

6.8. Efficiency

7. Discussion and Comparative Examination

7.1. Neural Signal Recording Using 28 nm CMOS Technology

7.2. Comparative Assessment with Previous Studies

- Improved recording spatial resolution: Closer electrode spacing enhances the ability to resolve individual neural units and reduces signal cross-talk.

- Enhanced signal-to-noise ratio (SNR): By positioning electrodes nearer to neural sources, the amplitude of recorded spikes increases, improving detectability and selectivity.

| Reference | This Work | VLSI’23 [21] | TCAS-II’21 [48] | JSSC’17 [8] | JSSC’11 [45] | TCAS-II’20 [49] |

|---|---|---|---|---|---|---|

| Tech. | 28 nm | 180 nm | 180 nm | 40 nm | 65 nm | 180 nm |

| VDD (V) | 1.2 | 1.8 | 0.8 | 1.2 | 0.5 | 1.2 |

| Power (μW) | 3.4 | 13.9 | 0.52 | 2.8 | 5.13 | 3 |

| Area (mm2) | 0.0025 | 0.085 | 0.24 | 0.069 | 0.013 | 0.2 |

| Input Impedance | 105.5 G @DC | 64 M @60 Hz | - | 1.6 G @DC | - | - |

| EOT (mV) | 910 | 50 | - | - | 100 | ±300 |

| Gain (dB) | 57 | 40 | 40 | 25.7 | - | 40 |

| BW (Hz) | 150–7.1k | 1–100 | 800 | 0.12–5k | 300–10k | 0.5–200 |

| Noise (Vrms) | 11.1 | 0.59 | 1.1 | 5.6 | 4.9 | 0.67~1.49 |

| PSRR (dB) | 52 | - | 75 | 76 | 50 | - |

| CMRR (dB) | 55 @BW | 106 @50 Hz | 104 | 78 | 75 | - |

| NEF | 8.4 | 6.4 | 2.1 | 4.4 | 6 | 2.88~6.41 |

| PEF | 85 | 73.7 | 1.2 | 23.2 | 18 | 10~49.3 |

| AEF | 0.21 | 6.3 | 0.29 | 1.6 | 0.23 | 1.99~9.86 |

8. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Mazandarani, M.S.; Bostani, R.; Papi, R.; Ebrahimi, Z.; Koleibi, E.R.; Fontaine, R.; Gagnon-Turcotte, G.; Gosselin, B. A Highly Duty-Cycled PPG Sensor With Ultra-Low-Power Consumption and Wide Input Range. IEEE Sens. J. 2024, 24, 39169–39181. [Google Scholar]

- Bostani, R.; Gagnon-Turcotte, G.; Bhadra, S.; Gosselin, B. A 200-mV Linear Dynamic Range VCO-Based Readout Interface with Offset Compensation for Resistive Bridge Sensors. In Proceedings of the 2024 22nd IEEE Interregional NEWCAS Conference (NEWCAS), Sherbrooke, QC, Canada, 16–19 June 2024; pp. 188–192. [Google Scholar]

- Steinmetz, N.A.; Aydin, C.; Lebedeva, A.; Okun, M.; Pachitariu, M.; Bauza, M.; Beau, M.; Bhagat, J.; Böhm, C.; Broux, M.; et al. Neuropixels 2.0: A Miniaturized High-Density Probe for Stable, Long-Term Brain Recordings. Science 2021, 372, eabf4588. [Google Scholar] [CrossRef] [PubMed]

- Chen, J.; Wu, H.; Eskandari, R.; Liu, X.; Lin, S.; Hou, Q.; Tian, F.; Zou, W.; Yang, J.; Sawan, M. A Neuron-Inspired 0.0032 mm2-1.38 μW/Ch Wireless Implantable Neural Interface with Direct Multiplexing Front-End and Event-Driven Spike Detection and Transmission. In Proceedings of the 2024 IEEE Custom Integrated Circuits Conference (CICC), Denver, CO, USA, 21–24 April 2024; pp. 1–2. [Google Scholar]

- Shahrokhi, F.; Abdelhalim, K.; Serletis, D.; Carlen, P.L.; Genov, R. The 128-channel fully differential digital integrated neural recording and stimulation interface. IEEE Trans. Biomed. Circuits Syst. 2010, 4, 149–161. [Google Scholar] [CrossRef] [PubMed]

- Mohseni, P.; Najafi, K. A fully integrated neural recording amplifier with DC input stabilization. IEEE Trans. Biomed. Eng. 2004, 51, 832–837. [Google Scholar] [CrossRef]

- Gosselin, B.; Sawan, M.; Chapman, C.A. A low-power integrated bioamplifier with active low-frequency suppression. IEEE Trans. Biomed. Circuits Syst. 2007, 1, 184–192. [Google Scholar] [CrossRef]

- Chandrakumar, H.; Marković, D. A high dynamic-range neural recording chopper amplifier for simultaneous neural recording and stimulation. IEEE J. Solid State Circuits 2017, 52, 645–656. [Google Scholar] [CrossRef]

- Jomehei, M.G.; Sheikhaei, S. A low-power low-noise CMOS bio-potential amplifier for multi-channel neural recording with active DC-rejection and current sharing. Microelectron. J. 2019, 83, 197–211. [Google Scholar] [CrossRef]

- Lemaire, W.; Koleibi, E.R.; Omrani, T.; Benhouria, M.; Koua, K.; Quesnel, C.; Gauthier, L.P.; Ménard, J.; Gagnon, K.; Roy, S.; et al. Preliminary Results from a 49-Channel Neural Recording ASIC with Embedded Spike Compression in 28 nm CMOS. In Proceedings of the 2022 20th IEEE Interregional NEWCAS Conference (NEWCAS), Quebec City, QC, Canada, 19–22 June 2022; pp. 285–289. [Google Scholar]

- Koleibi, E.R.; Bostani, R.; Mazandarani, M.S.; Askarian, A.; Koua, K.; Tétrault, M.A.; Roy, S.; Nabki, F.; Gosselin, B.; Fontaine, R. 2.32-V Peak-to-Peak Carrier-Based IR-UWB Transmitter for High-Density On-Cortex Neural Recorder Implants in 28nm CMOS Technology. In Proceedings of the 2025 IEEE 15th Latin America Symposium on Circuits and Systems (LASCAS), Bento Gonçalves, Brazil, 25–28 February 2025; pp. 1–5. [Google Scholar]

- Koleibi, E.R.; Bostani, R.; Mazandarani, M.S.; Koua, K.; Lemaire, W.; Besrour, M.; Gosselin, B.; Roy, S.; Nabki, F.; Fontaine, R. Tunable impulse radio uwb transmitter for high-density neural recorder implants in 28 nm cmos technology. In Proceedings of the 2024 31st IEEE International Conference on Electronics, Circuits and Systems (ICECS), Nancy, France, 18–20 November 2024; pp. 1–4. [Google Scholar]

- Koleibi, E.R.; Bostani, R.; Koua, K.; Lessard, G.; Nti, R.B.; Roy, S.; Nabki, F.; Gosselin, B.; Fontaine, R. 28nm CMOS Technology-Based Ultra-Compact Tunable IR-UWB Transmitter for Neural Implants: Compliance With FCC, ECC, and Japanese Spectral Masks under IEEE 802.15.6. In Proceedings of the 2024 International Conference on Microelectronics (ICM), Doha, Qatar, 14–17 December 2024; pp. 1–6. [Google Scholar] [CrossRef]

- Koleibi, E.R.; Benhouria, M.; Koua, K.; Lemaire, W.; Roy, S.; Fontaine, R. A Low-Power Low-Noise Biopotential Amplifier in 28 nm CMOS. In Proceedings of the 2022 20th IEEE Interregional NEWCAS Conference (NEWCAS), Quebec City, QC, Canada, 19–22 June 2022; pp. 143–147. [Google Scholar]

- Chandrakumar, H.; Marković, D. An 80-mVpp Linear-Input Range, 1.6-GΩ Input Impedance, Low-Power Chopper Amplifier for Closed-Loop Neural Recording That Is Tolerant to 650-mVpp Common-Mode Interference. IEEE J. Solid State Circuits 2017, 52, 2811–2828. [Google Scholar] [CrossRef]

- Seese, T.M.; Harasaki, H.; Saidel, G.M.; Davies, C.R. Characterization of tissue morphology, angiogenesis, and temperature in the adaptive response of muscle tissue to chronic heating. Lab. Investig. 1998, 78, 1553–1562. [Google Scholar]

- Bharucha, E.; Sepehrian, H.; Gosselin, B. A survey of neural front end amplifiers and their requirements toward practical neural interfaces. J. Low Power Electron. Appl. 2014, 4, 268–291. [Google Scholar] [CrossRef]

- Jochum, T.; Denison, T.; Wolf, P. Integrated circuit amplifiers for multi-electrode intracortical recording. J. Neural Eng. 2009, 6, 012001. [Google Scholar] [CrossRef] [PubMed]

- Park, Y.; Cha, J.H.; Han, S.H.; Park, J.H.; Kim, S.J. A 3.8-μW 1.5-NEF 15-GΩ total input impedance chopper stabilized amplifier with auto-calibrated dual positive feedback in 110-nm CMOS. IEEE J. -Solid-State Circuits 2022, 57, 2449–2461. [Google Scholar] [CrossRef]

- Zhou, Y.; Song, S.; Zheng, Y.; Yang, T.; Li, M.; Cao, Y.; Zheng, F.; Huang, K.; Tan, Z.; Zhao, M. A 20.3 μW 1.9 GΩ Input Impedance Capacitively-Coupled Chopper-Stabilized Amplifier for Bio-Potential Readout. IEEE Trans. Circuits Syst. I Regul. Pap. 2024, 71, 1520–1530. [Google Scholar] [CrossRef]

- Huang, Y.K.; Rodriguez, S. Noise Analysis and Design Methodology of Chopper Amplifiers with Analog DC-Servo Loop for Biopotential Acquisition Applications. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2023, 32, 55–67. [Google Scholar] [CrossRef]

- Muller, R.; Le, H.P.; Li, W.; Ledochowitsch, P.; Gambini, S.; Bjorninen, T.; Koralek, A.; Carmena, J.M.; Maharbiz, M.M.; Alon, E.; et al. 24.1 A miniaturized 64-channel 225μW wireless electrocorticographic neural sensor. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 412–413. [Google Scholar]

- Thanapitak, S.; Surakampontorn, W.; Sawigun, C. A micropower chopper CBIA using DSL-embedded input stage with 0.4 V EO tolerance for dry-electrode biopotential recording. IEEE Trans. Biomed. Circuits Syst. 2023, 17, 458–469. [Google Scholar] [CrossRef]

- Harrison, R.R.; Charles, C. A low-power low-noise CMOS amplifier for neural recording applications. IEEE J. -Solid-State Circuits 2003, 38, 958–965. [Google Scholar] [CrossRef]

- Harrison, R.R. The design of integrated circuits to observe brain activity. Proc. IEEE 2008, 96, 1203–1216. [Google Scholar] [CrossRef]

- Harrison, R.R.; Watkins, P.T.; Kier, R.J.; Lovejoy, R.O.; Black, D.J.; Greger, B.; Solzbacher, F. A low-power integrated circuit for a wireless 100-electrode neural recording system. IEEE J. Solid State Circuits 2006, 42, 123–133. [Google Scholar] [CrossRef]

- Lee, J.; Rhew, H.G.; Kipke, D.R.; Flynn, M.P. A 64 channel programmable closed-loop neurostimulator with 8 channel neural amplifier and logarithmic ADC. IEEE J. Solid State Circuits 2010, 45, 1935–1945. [Google Scholar] [CrossRef]

- Chen, W.M.; Chiueh, H.; Chen, T.J.; Ho, C.L.; Jeng, C.; Ker, M.D.; Lin, C.Y.; Huang, Y.C.; Chou, C.W.; Fan, T.Y.; et al. A fully integrated 8-channel closed-loop neural-prosthetic CMOS SoC for real-time epileptic seizure control. IEEE J. Solid State Circuits 2013, 49, 232–247. [Google Scholar] [CrossRef]

- Fan, Q.; Sebastiano, F.; Huijsing, J.H.; Makinwa, K.A. A 1.8 μW 60 nV/Hz Capacitively-Coupled Chopper Instrumentation Amplifier in 65 nm CMOS for Wireless Sensor Nodes. IEEE J. Solid State Circuits 2011, 46, 1534–1543. [Google Scholar]

- Spinelli, E.M.; Martínez, N.; Mayosky, M.A.; Pallàs-Areny, R. A novel fully differential biopotential amplifier with DC suppression. IEEE Trans. Biomed. Eng. 2004, 51, 1444–1448. [Google Scholar] [PubMed]

- Bafar, V.M.; Schmid, A. Wireless Cortical Implantable Systems; Springer: Berlin/Heidelberg, Germany, 2013. [Google Scholar]

- Hashemi Noshahr, F.; Nabavi, M.; Sawan, M. Multi-channel neural recording implants: A review. Sensors 2020, 20, 904. [Google Scholar] [CrossRef] [PubMed]

- Ranjbar, E.; Danaie, M. Frequency compensation of three-stage operational amplifiers: Sensitivity and robustness analysis. Microelectron. J. 2017, 66, 155–166. [Google Scholar] [CrossRef]

- Danaie, M.; Ranjbar, E.; Khanesar, M.A. MOSCAP compensation of three-stage operational amplifiers: Sensitivity and robustness, modeling and analysis. Integration 2018, 62, 34–49. [Google Scholar]

- Zhao, W.; Li, H.; Zhang, Y. A low-noise integrated bioamplifier with active DC offset suppression. In Proceedings of the 2009 IEEE Biomedical Circuits and Systems Conference, Beijing, China, 26–28 November 2009; pp. 5–8. [Google Scholar]

- Sharma, K.; Pathania, A.; Pandey, R.; Madan, J.; Sharma, R. MOS based pseudo-resistors exhibiting Tera Ohms of Incremental Resistance for biomedical applications: Analysis and proof of concept. Integration 2021, 76, 25–39. [Google Scholar] [CrossRef]

- Motchenbacher, C.D.; Connelly, J.A. Low-Noise Electronic System Design; Wiley: New York, NY, USA, 1993; Volume 269. [Google Scholar]

- Aziz, J.N.; Abdelhalim, K.; Shulyzki, R.; Genov, R.; Bardakjian, B.L.; Derchansky, M.; Serletis, D.; Carlen, P.L. 256-channel neural recording and delta compression microsystem with 3D electrodes. IEEE J. Solid State Circuits 2009, 44, 995–1005. [Google Scholar]

- Gosselin, B. Circuits Mixtes et Microsystèmes Implantables Dédiés à L’enregistrement Sans Fil des Biopotentiels Neuronaux; Library and Archives Canada: Ottawa, ON, USA, 2011. [Google Scholar]

- Allen, P.E.; Dobkin, R.; Holberg, D.R. CMOS Analog Circuit Design; Elsevier: Amsterdam, The Netherlands, 2011. [Google Scholar]

- Van Oosterhout, K.; Timmermans, M.; Fattori, M.; Cantatore, E. A 250MΩ Input Impedance a-IGZO Front-End for Biosignal Acquisition from Non-Contact Electrodes. In Proceedings of the 2024 IEEE International Symposium on Circuits and Systems (ISCAS), Singapore, 19–22 May 2024; pp. 1–5. [Google Scholar]

- Zhang, F.; Holleman, J.; Otis, B.P. Design of ultra-low power biopotential amplifiers for biosignal acquisition applications. IEEE Trans. Biomed. Circuits Syst. 2012, 6, 344–355. [Google Scholar]

- Tilden, S.J.; Linnenbrink, T.E.; Green, P.J. Overview of IEEE-STD-1241 “standard for terminology and test methods for analog-to-digital converters”. In Proceedings of the IMTC/99 16th IEEE Instrumentation and Measurement Technology Conference (Cat. No. 99CH36309), Venice, Italy, 24–26 May 1999; Volume 3, pp. 1498–1503. [Google Scholar]

- Steyaert, M.S.; Sansen, W.M. A micropower low-noise monolithic instrumentation amplifier for medical purposes. IEEE J. Solid State Circuits 1987, 22, 1163–1168. [Google Scholar]

- Muller, R.; Gambini, S.; Rabaey, J.M. 0.013 mm2, 5 μW, A DC-Coupled Neural Signal Acquisition IC With 0.5 V Supply. IEEE J. Solid State Circuits 2011, 47, 232–243. [Google Scholar]

- Gauthier, L.P.; Lemaire, W.; Gagnon, K.; Quesnel, C.; Larouche, J.B.; Rossignol, J.; Paulin, C.; Benhouria, M.; Koua, K.; Roy, S.; et al. Preliminary Results of a Low-Power Wireless Telemetry Module For Long-Term μECoG Recordings. In Proceedings of the 2022 20th IEEE Interregional NEWCAS Conference (NEWCAS), Quebec City, QC, Canada, 19–22 June 2022; pp. 337–341. [Google Scholar] [CrossRef]

- Scott, K.M.; Du, J.; Lester, H.A.; Masmanidis, S.C. Variability of acute extracellular action potential measurements with multisite silicon probes. J. Neurosci. Methods 2012, 211, 22–30. [Google Scholar] [CrossRef] [PubMed]

- Pham, X.T.; Nguyen, V.N.; Kim, J.S.; Lee, J.W. A 0.52 μW, 38 nV/Hz chopper amplifier with a low-noise DC servo loop, an embedded ripple reduction loop, and a squeezed inverter stage. IEEE Trans. Circuits Syst. II Express Briefs 2020, 68, 1793–1797. [Google Scholar] [CrossRef]

- Liu, L.; Hua, T.; Zhang, Y.; Mu, J.; Zhu, Z. A robust bio-IA with digitally controlled DC-servo loop and improved pseudo-resistor. IEEE Trans. Circuits Syst. II Express Briefs 2019, 67, 440–444. [Google Scholar] [CrossRef]

| Parameter | [21] | [22] | [23] | Required |

|---|---|---|---|---|

| Power/ch (μW) | 13.9 | 2.3 | 1.19 | <10 |

| BW (Hz) | 1–100 | 300 | 0.1–100 | 300–10k |

| EOT (mV) | 50 | 50 | 400 | >50 |

| IRN (μVrms) | 0.59 | 7 | 0.91 | 4–8 |

| Area/ch (mm2) | 0.085 | 0.025 | 0.41 | <0.01 |

| DC Zin | 64 M @60 Hz | 28 M @100 Hz | 469 M @50 Hz | >1 G |

| Noise Source | IRN (μVrms) |

|---|---|

| IRNOTA1 * | 6.4 |

| IRNOTA2 * | 5.5 |

| ESD * | 3.3 |

| Vref | 10 ± 3 |

| Total | 15.8 |

| Process | TT | FF | FS | SF | SS |

|---|---|---|---|---|---|

| IRN (μVrms) | 8.4 | 8.5 | 8.8 | 8 | 8.5 |

| Gain (dB) | 57 | 55.7 | 56.7 | 57.1 | 58.1 |

| Output noise(mVrms) | 6 | 5.2 | 5.9 | 5.8 | 6.9 |

| Power (μW) | 3.55 | 3.71 | 2.36 | 3.61 | 2.34 |

| BW (kHz) | 0.6–7 | 1.45–12.2 | 0.37–5.2 | 1.1–8.4 | 0.33–3.9 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ranjbar Koleibi, E.; Lemaire, W.; Koua, K.; Benhouria, M.; Bostani, R.; Serri Mazandarani, M.; Gauthier, L.-P.; Besrour, M.; Ménard, J.; Majdoub, M.; et al. Design and Implementation of a Low-Power Biopotential Amplifier in 28 nm CMOS Technology with a Compact Die-Area of 2500 μm2 and an Ultra-High Input Impedance. Sensors 2025, 25, 2320. https://doi.org/10.3390/s25072320

Ranjbar Koleibi E, Lemaire W, Koua K, Benhouria M, Bostani R, Serri Mazandarani M, Gauthier L-P, Besrour M, Ménard J, Majdoub M, et al. Design and Implementation of a Low-Power Biopotential Amplifier in 28 nm CMOS Technology with a Compact Die-Area of 2500 μm2 and an Ultra-High Input Impedance. Sensors. 2025; 25(7):2320. https://doi.org/10.3390/s25072320

Chicago/Turabian StyleRanjbar Koleibi, Esmaeil, William Lemaire, Konin Koua, Maher Benhouria, Reza Bostani, Mahziar Serri Mazandarani, Luis-Philip Gauthier, Marwan Besrour, Jérémy Ménard, Mahdi Majdoub, and et al. 2025. "Design and Implementation of a Low-Power Biopotential Amplifier in 28 nm CMOS Technology with a Compact Die-Area of 2500 μm2 and an Ultra-High Input Impedance" Sensors 25, no. 7: 2320. https://doi.org/10.3390/s25072320

APA StyleRanjbar Koleibi, E., Lemaire, W., Koua, K., Benhouria, M., Bostani, R., Serri Mazandarani, M., Gauthier, L.-P., Besrour, M., Ménard, J., Majdoub, M., Gosselin, B., Roy, S., & Fontaine, R. (2025). Design and Implementation of a Low-Power Biopotential Amplifier in 28 nm CMOS Technology with a Compact Die-Area of 2500 μm2 and an Ultra-High Input Impedance. Sensors, 25(7), 2320. https://doi.org/10.3390/s25072320