Abstract

In this paper, we propose adaptive nonlinear controllers for the Single-Ended Primary Inductance Converter (SEPIC). We also consider four distinct situations: AC-DC, DC-DC, Continuous Conduction Mode (CCM) and Discontinuous Conduction Mode (DCM). A comparative analysis between classic linear and nonlinear approaches to regulate the control loop is made. Three adaptive nonlinear control laws are designed: Feedback Linearization Control (FLC), Passivity-Based Control (PBC) and Interconnection and Damping Assignment Passivity-Based Control (IDAPBC). In order to compare the performance of these control techniques, numerical simulations were made in Software and Hardware in the Loop (HIL) for nominal conditions and operation disturbances. We recommend adaptive controllers for the two different situations: Adaptive Passivity-Based Feedback Linearization Control (APBFLC) for the PFC (Power Factor Correction) AC-DC system and IDAPBC-BB (IDAPBC Based on Boost converter) for the regulator DC-DC system.

1. Introduction

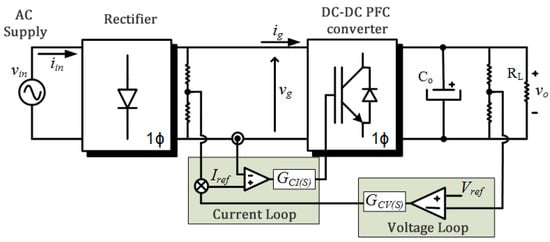

Conventional power supplies usually only have one full-bridge diode rectifier and one large capacitive filter in the input stage. This front-end circuit operates with a high Total Harmonic Distortion (THDi) in the grid current, a low power factor (0.5–0.7) and normally does not meet regulatory standards, such as the important international standard IEC 61000-3-2 [1]. Among the possible alternatives to improve the performance of switched sources, a highlight is the use of a DC-DC converter to creation a Power Factor Correction (PFC) system. As shown in Figure 1, this solution makes it possible to build nearly ideal rectifiers (emulates a resistor) and still achieve voltage, current or power regulation.

Figure 1.

Schematic diagram of the DC-rectification system with the power factor correction stage.

Several topologies of converters used in power factor correction are present in the literature [2,3]. Among them, the most popular topology is the boost converter [4,5]. However, this converter has some disadvantages:

- Relatively high output voltage (at least equal to the AC source voltage), which can generate over-voltage stress in the switches;

- Difficulty in implementing insulation between input and output;

- Lack of overload and over-current control due to the absence of a serial switch between the input and the output;

- Inability to start-up.

However, the CUK and SEPIC topologies overcome these drawbacks presented by the boost converter, which becomes a good choice in PFC applications. In time, SEPIC converters have attracted much attention from modern applications, especially those involving renewable energy [6] such as LED (Light Emitting Diode) [7,8], fuel cells [9], battery chargers [10], photovoltaics [11] and eolic systems [12,13].

In this work, the operation characteristics, the modeling and control system of the SEPIC PFC converter in CCM and DCM are presented. Initially, a comparative analysis between two control techniques will be performed for this converter. The first one deals with the Classical Linear Control (CLC) based on the small-signal model, and the other is based on the Feedback Linearization Control (FLC) approach. Next, we suggest a new nonlinear controller, which works around the drawbacks of the CLC and FLC methods. The proposed control law, explained in the dedicated section, we call Adaptive Passivity-Based Feedback Linearization Control (APBFLC).

In order to analyze the operation of the SEPIC PFC converter, numerical simulations were performed in software for both the nominal condition and disturbances in the operation of this converter, by analyzing the Power Factor (PF) on the AC side, the harmonic distortion (THDi) of the input current and the DC side voltage regulation.

We list the main contributions of this paper:

- a comparative analysis between linear and nonlinear control;

- the proposal of an adaptive nonlinear control without current measurement in the intermediate inductor and with low harmonic distortion: APBFLC;

- recent IDAPBC methods adapted from the boost converter adjusted to the SEPIC converter with very low overshoot in view of load disturbances: IDAPBC-BB;

- HIL simulation of nonlinear control techniques applied to DC-DC SEPIC in CCM mode.

This work is organized as follows. Section 2 introduces the modeling and analysis of the converters in CCM and DCM. The description of the design and the control techniques implemented for the PFC system, as well as the control law for DC-DC are shown in Section 3. Section 4 presents the proposed APBFLC controller. Section 5 includes the adaptation of new and efficient boost control laws to SEPIC converters. Section 6 demonstrates and discusses the main simulations and the HIL experimental results. Finally, in Section 7, the final comments and conclusions are presented.

2. Modeling

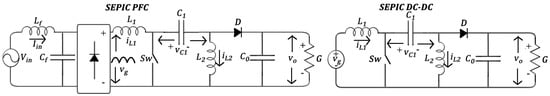

The PFC and DC-DC SEPIC converter circuits are illustrated in Figure 2. Based on [14,15], the average State-Space Model (SSM) and Euler–Lagrange Model (ELM) are presented in Table 1. Note that and are the average currents in the inductors and , is the capacitor voltage , is the output voltage across the capacitor , d is duty cycle, G is the load conductance and is the input voltage. Note in Table 1 that the differences between the two conduction modes basically consist of the residual term presented in the states representing the inductors currents ( for CCM and for DCM).

Figure 2.

SEPIC PFC and SEPIC DC-DC.

Table 1.

Converter models.

2.1. CCM and DCM Analysis

The operation details of the SEPIC converter in DCM, illustrated in Figure 3, outline three mode configurations, which depend on the states of the semiconductor switch S and the diode D. The third configuration (c) represents the discontinuous operation mode, which is characterized by the annulment of the current drained through the diode. This is due to the inversion in one of the inductor currents of the converter, which will also equal in intensity the current of the other inductor; so the sum of these currents () will become zero during a short time interval. If the sum of these currents is always greater than zero over the entire span where the switch remains open, there will be a current across the diode, and only the configurations (a) and (b) will be observed, which will represent the operation of the converter in continuous mode.

Figure 3.

Electrical configuration of the SEPIC DCM converter operation: (a) closed switch; (b) open switch and diode conduction; and (c) open switch and blocked diode.

According to [14], the operation of the SEPIC converter in DCM can be analytically represented by (1), where and are the switching and the threshold functions, respectively. These functions of the switch model are presented in (2) and (3), where . In addition, and are their respective complements.

Let us derive the state-space averaging approach of (1), considering the DCM SEPIC converter operation, to obtain:

where d is the duty cycle of the semiconductor switch. According to [16], the average output current of the SEPIC converter in DCM for a half cycle of the AC line and the AC current grid can be written, respectively, as follows:

where is the equivalent inductance derived from the parallel association of the inductors and is given by:

2.2. PFC Converter Characteristics

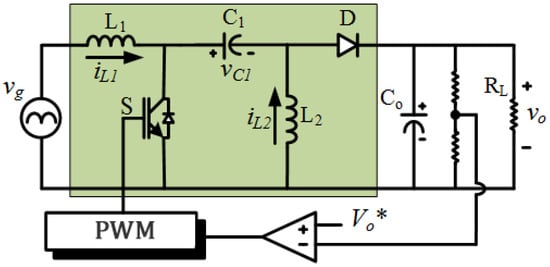

In power factor correction applications (AC-DC), as shown in Figure 4, the input voltage and current can be described by:

where and are the amplitude values of these input quantities and w is the angular frequency. Note that for a DC-DC system, the input is constant.

Figure 4.

Schematic of the SEPIC PFC converter.

On the other hand, the output voltage remains practically constant throughout each half cycle due to the presence of the large output capacitor . Hence, this voltage can be approximated by a constant value .

In addition, the PFC converter operates under very special conditions where the nominal DC voltage transformation and the load “seen” by the converter, at each period, are given by:

where these quantities periodically vary from a minimum value M and () to infinity (, with ) in each half cycle of the grid frequency. Such features extend to any type of DC-DC converter used as PFC.

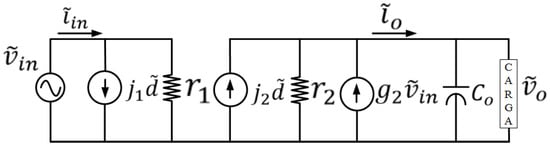

2.3. CIECA Modeling

The CIECA approach (Current Injected Equivalent Circuit Approach), proposed by [17], works to simplify the DCM SEPIC modeling taking into account some desired characteristics:

- Simple, clear, works in both continuous and discontinuous conduction mode (CCM or DCM);

- Can produce a well-suited approximated version of a real converter;

- The equivalent circuit can be used directly in digital software simulators (SPICE, MATLAB, PSIM and others).

In the CIECA design procedure, the first step is to identify the nonlinear part of the converter circuit (containing the switch). The second is the linearization, which is done through the average current. This fact makes simple the application of this approach, and the final result of the modeling becomes a set of small-signal equations. Therefore, a linear equivalent circuit model for the nonlinear converter is sketched in Figure 5, representing the transfer ratios of the converter. The CIECA modeling can be applied to CLC control.

Figure 5.

Equivalent small-signal circuit of the SEPIC PFC.

The dynamic properties of the converter are determined from an introduction of an AC small-signal variation on the steady-state operating point, where the small signal values are considered to be much smaller than the quiescent values: , , , and , where “−” indicates the steady-state value and “∼” represents the small-signal disturbance introduced.

Applying these disturbances in (5), which shows the value of the output current, and upon eliminating nonlinear second-order terms, this leads to:

where: , and .

Using these same perturbations in (7), we have:

where: and .

The expressions (12) and (13) represent the model of small low-frequency signals of the SEPIC converter. They are also used to obtain the equivalent small-signal circuit, illustrated in Figure 5. From this equivalent circuit, the desired transfer functions of the SEPIC converter can be obtained. In addition, it should be noted that the equivalent small signal impedance of the load () directly depends on the load to which the PFC converter is connected. In this case, making use of a purely resistive load (), the equivalent small signal impedance shall be considered equal to the load itself, i.e., .

3. Control System

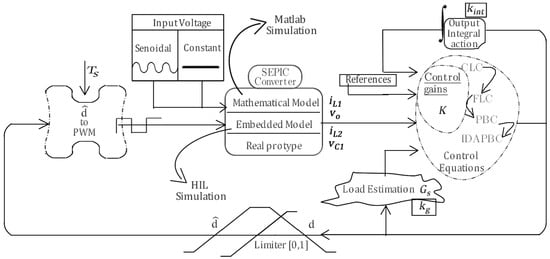

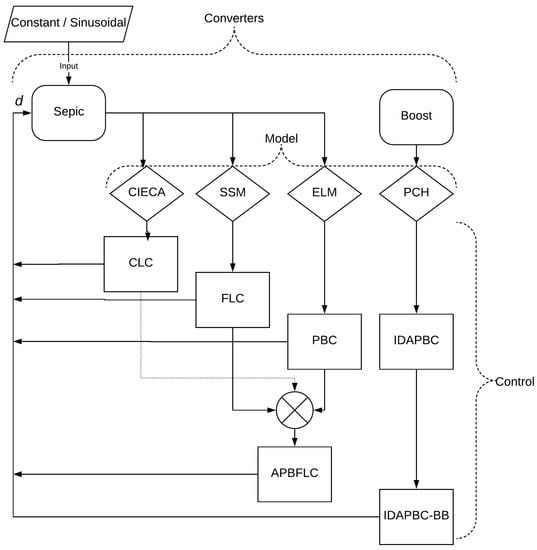

Several control techniques for switched converters are presented in the literature. In this work, an initial comparison is made between two of them: the traditional approach, using a Proportional-Integral (PI) controller and the nonlinear technique based on FLC (Feedback Linearization Control). A generalized procedure for both linear and non-linear control is shown in Figure 6. The complementary flowchart, sketched in Figure 7, outlines important observations:

Figure 6.

Standard control procedure. The control goal is to get the equation for d. With the signal of the duty cycle synthesized, it is necessary to limit it between zero and one, and then, the corresponding PWM (Pulse Width Modulation) signal is produced for input to the converter. Therefore, it is necessary to estimate the value of the load represented by and add an integral action.

Figure 7.

Flowchart of the methods used in this work.

- CLC needs CIECA modeling (Section 3.1);

- FLC and PBC employ SSM and ELM models, respectively;

- The APBFLC control (Section 4) incorporates the advantages of FLC and PBC. The integral action used in the classical control can also be added.

- The IDAPBC-BB control (Section 5) is obtained through the simplified modeling based on the boost converter and the IDABPBC control, which utilizes the Port-Controlled Hamiltonian (PCH) model (Appendix B);

When considering the classic control system of the PFC converters, there are two main methods: the multiplicative and the follower voltage, portrayed in [16]. In the case of SEPIC PFC in DCM mode operation, there is an inherent characteristic that simplifies and establishes the control system, explained in the following subsection.

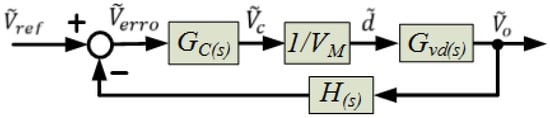

3.1. Classic Control

In the traditional linear approach, the control system is reduced to a single voltage loop, which is sketched in Figure 4. This control system can also be represented in the form of block diagrams of Figure 8, where the SEPIC converter and the PWM controller (Pulse-Width Modulation) are replaced by their respective transfer functions: and . The other elements correspond to the amplitude of the triangular wave and voltage sensor gain .

Figure 8.

Block diagram of the control system in voltage mode.

The voltage-proportional-integral PWM controller is designed using the classical frequency domain technique presented in [18]. The transfer function relates the output voltage to the duty cycle, obtained from the small-signal equivalent circuit of the Figure 5, as follows:

In addition, this classical PI controller adjustment is based on the definition of the transfer function , which is given by:

3.2. Feedback Linearization Control

In the case of the FLC technique, there is a linearization of the nonlinear dynamics of the system by state feedback, which is applied to the entire domain of the state space except for some singular points, so, it is global. Thus, this approach differs from linearization in the neighborhood of an equilibrium point, which was used to construct the equivalent model of Figure 5.

The design of the control system in the FLC approach is performed including a variable change, which shows the structure of the designed controller [14]. In addition, the control law is based on the knowledge of the average converter model, which was presented in (4). In relation to this model, it is observed that the system presents a unity relative degree. This fact makes possible the derivation of the current control law from the first equation of this average model:

which:

where is the output of the FLC controller, corresponds to the amplitude of the triangular wave and is the new variable, given by:

In turn, the reference current , whose amplitude was defined in (7), is represented by:

In addition, due to possible regime errors caused by the parametric uncertainties and in order to regulate the output voltage at the desired value , it is necessary to introduce an integral action, which is represented as follows:

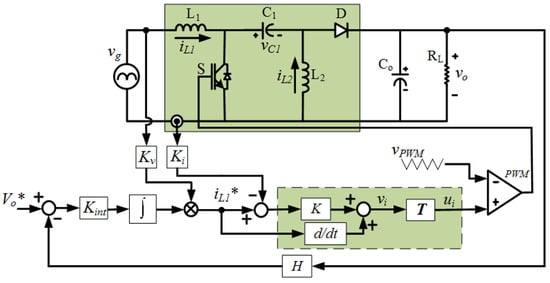

Finally, Figure 9 shows the control system in the FLC approach, where the function T represents the relation between the auxiliary variable and the controller output . Such a function can be obtained by solving the expressions (16)–(18). FLC and PBC control equations for CCM and DCM SEPIC are summarized in Table 3. Note that PBC has the same first Equation (16) and three morestate equations.

Figure 9.

FLC control in block diagrams.

3.3. Numerical and Initial Implementations for SEPIC DCM PFC

The reactive power elements of SEPIC is presented in Appendix A. An important quantity to be calculated is the transfer function shown in (14), which is given numerically by:

where: and .

This transfer function has great importance for the control loop adjustment in the classical approach, which must be sufficiently slow in order to avoid the injection of the second harmonic of the output in the input current. In this case, an expressive third order harmonic component can appear. As suggested in [19,20], it is necessary to allocate the crossover frequency of the control at least three times less than the AC input frequency, which makes the control system naturally slow.

Again, the PI controller was tuned using the classical frequency domain technique. The characteristics of this control system are shown in Table 2 together with the FLC control parameters. The next step is to analyze the AC side Power Factor (PF), the Total Harmonic Distortion of the input current (THDi) and the DC side voltage regulation in the simulated system for both the nominal condition and operation disturbances.

Table 2.

Control system specifications.

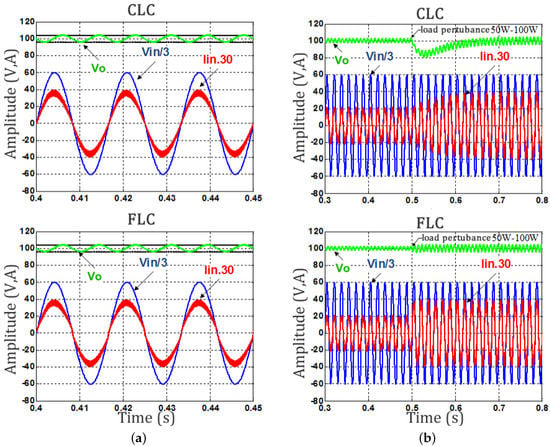

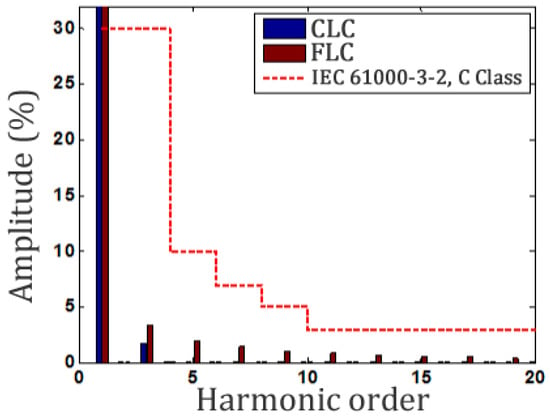

The first analysis considers the operation of the full load converter (100 W), as shown in Figure 10a. In this figure, it is possible to observe the power factor correction characteristic of the SEPIC PFC converter, which has a high power factor (—0.9975, —0.9971), low harmonic content (—6.33%; —7.60%) and is still able to maintain the output voltage at the reference of 100 V within the limits imposed by the design. The low harmonic content of the input current is evidenced in the spectral analysis shown in Figure 11, where it is noted that the values obtained in the two control approaches are far below the limits imposed by the IEC 61000-3-2, Standard Class C.

Figure 10.

(a) Steady-state. Full-load operation (100 W) and (b) transient. Transient response to a load variation (50–100 W).

Figure 11.

Comparison of the harmonic current with the limits imposed by IEC 61000-3-2.

It can be seen from Figure 10b that the dynamic behavior of the SEPIC converter is able to regulate the output voltage in both control strategies, although it takes different times to achieve this regulation, for a load variation of 50 W–100 W. In the case of the linear approach, the SEPIC converter spends approximately 120 ms to perform the voltage regulation, allowing that voltage to decrease by approximately 20 V. On the other hand, the converter has been able to regulate this output voltage in less than one grid cycle in the FLC approach. In addition, in the nonlinear technique, an overvoltage or current signal is not verified in the voltage regulation, surpassing the linear approach in this discussion point.

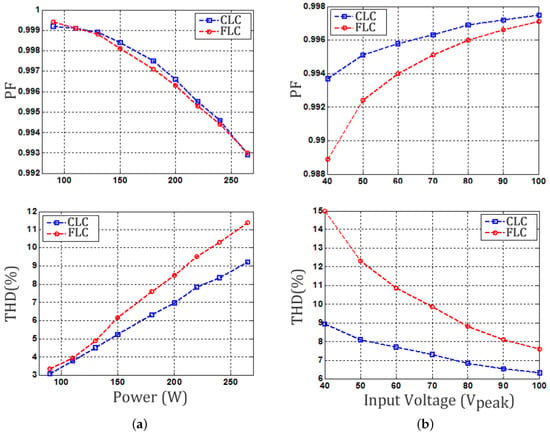

Finally, an analysis of the power factor and harmonic distortion of the AC input current is performed for both the universal input voltage values (90–265 V peak) at full load (100 W) and for different values of the load connected to the SEPIC converter. The first one is presented in Figure 12a and shows that the converter has a high power factor and low harmonic content in the AC current along the entire voltage range of the universal input in both methods. However, it is noted that the linear technique presents a slight superiority in this test.

Figure 12.

Power factor and Total Harmonic Distortion (THD) for: (a) universal input voltage. Universal input voltage (90–265 V) and (b) load variation. Different load values.

The other analysis is presented in Figure 12b, and again, the converter is able to maintain a high power factor and low harmonic content in both control approaches, now for different load values. In addition, it is observed that there is a more evident superiority of the linear approach in this last analysis to the different values of the load, which can be explained by the distortion in the waveform of the current in the passage through zero due to the presence of a derivative action in the FLC methodology.

4. Proposed Adaptive Non Linear Control Law

The two control laws discussed above, both linear and non-linear, have some drawbacks, which will be discussed below. First, for the classic controller shown in Figure 7, the control structure directly depends on the output signal of a voltage error amplifier (which contains a second harmonic component) and the input rectified sine wave voltage. As explained in [20], the linear controller ends up leading to higher levels in the third harmonic of the input current. To minimize this aggravating factor, the control loop is intentionally slow. The other disadvantage is the restriction at the operation point of the system since linearization is local around the equilibrium point. It should also be added that linear control works for DCM mode; the same performance does not occur in CCM mode.

The FLC control presents a major practical implementation problem: it needs the known value of the load G. Note that (7) depends on the desired current value in the primary inductor, which in turn depends on the value of G. Figure 11 shows this deficiency in the FLC control. In view of these two major disadvantages, we propose the following adaptive control law based on the passivity-based control and feedback linearization control Table 3, which we call APBFLC.

Table 3.

FLC and PBC control equations in CCM and DCM SEPIC.

When the load is unknown, although constant, an adaptive control strategy, as presented in [21], can be applied, where the unknown load conductance is adapted as follows:

For a DC-DC system:

Note that it is necessary to estimate an additional state: the output voltage given by (23). The integral action, given by (20), can also be included in the control law. We list the following advantages of the proposed law:

- In contrast to the classical control, it gives an indirect and less dependent control of the 120-Hz ripple output voltage, which, therefore, allows for lower THDi levels; a higher phase margin due to non-restriction operating point. The integral gain can be stipulated for a faster response.

- Complements the FLC control and allows load estimation given by (26), being more robust to load disturbances;

- Given the caveats imposed by (22), the adaptive control law works for both conduction current modes (DCM and CCM);

- Neglecting the current measurement of the intermediate inductor ; this characteristic is motivated by the analysis discussed in the following section.

5. Revised SEPIC as a Boost Converter and Derived Equations

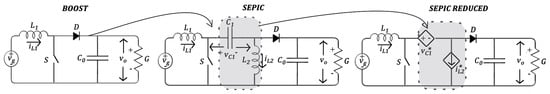

The SEPIC converter has two inductors and two capacitors (a fourth order system), so it is necessary to reduce the number of states and measurements, for cost and error propagation reasons. In view of this concern, Ref. [15,22] use observers and immersion techniques. In [23], the fourth order transfer function of SEPIC is reduced to second order using the Pade approximation method, where the designed compensator closely follows the original system’s response. Furthermore, Ref. [24] employ a simplified second order state-averaged model, using the sliding surface-regulated current-mode PWM controller. In addition, the CIECA modeling discussed in Section 2.3 motivates an interesting question: Is it possible to reduce the states of the SEPIC converter, for example, considering only the output voltage and the input current?

In Figure 13, the boost and SEPIC converters are placed side by side for comparison. It is observed that when removing the intermediate elements (, ) highlighted by the dotted line, the SEPIC converter becomes similar to the boost converter, having similar equilibrium points as shown in Table 4. This is the reason that these converters are recommended to work in PFC systems. What is the advantage of this adaptation?

Figure 13.

PFC SEPIC and DC-DC SEPIC.

Table 4.

Equilibrium points of the converters.

Therefore, we can use the boost equations and apply them to control the SEPIC converter replacing the state variables eliminated ( and ) by the equilibrium points, provided in Table 4, represented by dependent sources in the model. If we substitute, for example, by and by in the SEPIC converter, it saves two sensors. Figure 13 summarizes this process. The other option is to replace the desired state reference by the measurement of the state itself, as seen in (23).

To illustrate an example application, we consider two control laws based on IDAPBC. In [22], IDAPBC control is applied to boost converters achieving an effortless and open loop control equation:

IDAPBC-1:

Yet, Ref. [25] proposed an evolution of (28) given by:

IDAPBC-2:

Equations (28) and (29) can be applied to SEPIC converters, which we denominate as IDAPBC-BB control equations. Again, the integral action, given by (20), can also be added. In order to illustrate how to insert this term in the control law, just replace the desired variable in the output voltage () by the integral of the error between the measured variable () and the reference constant value (). Thus, the new control law becomes:

The boost IDAPBC control equations are presented in Appendix B.

6. Main Results

In order to verify the performance of the control systems applied to the SEPIC DC-DC CCM and SEPIC PFC DCM, software and HIL simulations were performed using the specifications presented in Table 5.

Table 5.

Initial and converters parameters.

6.1. SEPIC DC-DC CCM and HIL Simulation Results

This section presents the digital simulation results using MATLAB and Hardware in the Loop (HIL) procedure described in [26]. The converter is implemented according to the design specifications of Table 5 and the three control laws: FLC, APBFLC and IDAPBC-BB.

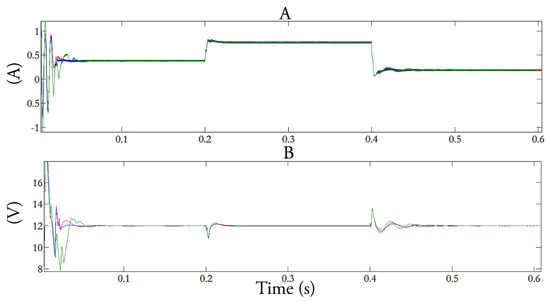

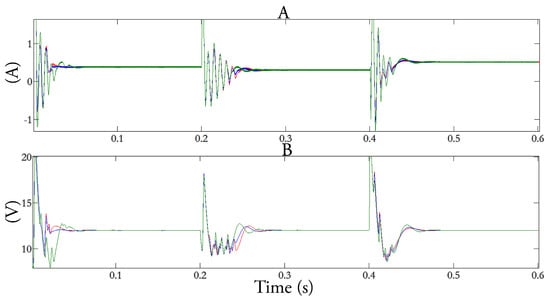

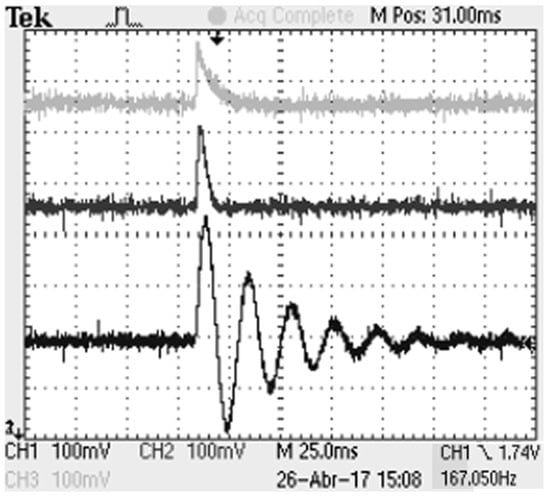

Figure 14 shows the capacitor voltage and inductor current response for load perturbation, respectively, in the SEPIC converter simulated in software. In the same way, Figure 15 presents the voltage and current response to an input voltage variation. In both input and load variation, consecutive steps of 50–100% are applied in the simulated systems. Figure 16 shows the out capacitor voltage of SEPIC converter, respectively, for the HIL application.

Figure 14.

Input current (A) and output voltage (B) in the MATLAB simulation with load change (20 – 10 – 40 ). FLC (blue), APBFLC (green) and IDAPBC-BB-1 (red).

Figure 15.

Input current (A) and output voltage (B) in the MATLAB simulation with input voltage variation (20 – 15 – 25 V). FLC (blue), APBFLC (green) and IDAPBC-BB-1 (red).

Figure 16.

HIL experimental result for SEPIC converter. Normalized output voltage in view of load perturbation (50–100%). FLC (top), APBFLC (middle) and IDAPBC-BB-1 (bottom).

As seen in Figure 14, Figure 15 and Figure 16, both software simulations and HIL results converged to the steady state value after the consecutive step applications. It is notable that the behavior of the systems are compatible, since the same transient dynamics is seen, even for the IDA-PBC’s oscillatory dynamics. None of the implemented systems in software or in HIL converged to instability. This means that the embedded models and control equations are capable of controlling the systems, so validating the control techniques.

The processing time for the DSP to compute the control law and therefore to run a real-time simulation is 1.2 µs. Using a switching frequency of 50 kHz (20 µs), the processing time of all control equations (1.2 µs) demands 6% of the bandwidth.

6.2. APBFLC Results

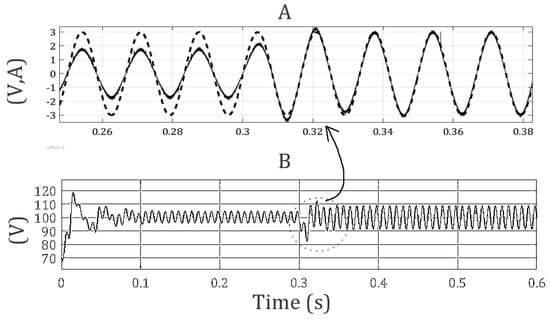

As sketched in Figure 17, the output voltage can asymptotically track the set-point even if the load perturbation is present. The APBFLC controller features low THDi (<2%), low overshoot (<10%) and fast response speed (<0.05 s). The power factor achieved for the nominal condition is PF = 0.99.

Figure 17.

Detail of the input current (A continue) and normalized grid voltage (A dashed) and the output voltage transient (B) with a load change from R = 100 to R = 50 for APBFLC control.

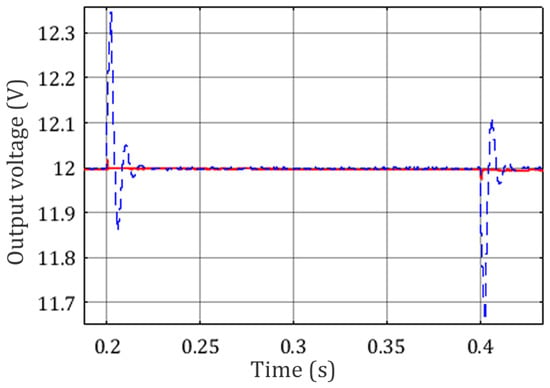

6.3. IDAPBC-BB Results

Next, the two control laws (28) and (29) are validated in simulation. We can again observe the stability of the adapted nonlinear controllers by analyzing the change in perturbation of the output voltage waveform over a load step (note the insignificant overshoot of IDAPBC-BB-2 response). Hence, this variable is controlled at the desired value . The steady-state and perturbed waveforms are sketched in Figure 18 showing that the two methods have low overshoot and fast response, even considering a control law adapted from the boost converter, taking into account only the measurement of the output voltage.

Figure 18.

IDAPBC-BB-1 (dashed blue) and IDAPBC-BB-2 (continue red) simulations. Output voltage for load perturbation (70–100%).

7. Conclusions

The intrinsic power factor correction includes SEPIC in a particular group of converters. Hence, the design of the control system derived from the model based on CIECA and the boost converter is satisfactory, revealing that it is possible to obtain high performance controllers using a simplified modeling. In addition, the effectiveness of the nonlinear approaches was verified, whose control laws proved to be efficient, especially for the voltage regulation and transient dynamics.

The performance of the proposed nonlinear controllers was analyzed under variations in load and input voltage. The software and HIL simulations demonstrated the feasibility of the nonlinear algorithms that can be used in embedded systems and practical applications, with simplicity and high accuracy.

Thus, we recommend:

- For DC-DC SEPIC: the IDAPBC-BB-2 controller, because it presents ultra-low overshoot and ultra-fast response speed; all these benefits are sufficiently attained using only one measure (output voltage );

- For PFC SEPIC: the APBFLC control method, which offers high robustness, low THDi, low overshoot, load estimation possibility and fast response; all these advantages were achieved regardless of mode operation (CCM or DCM).

Acknowledgments

This work has been supported by the Brazilian agencies CAPES and FAPEMIG.

Author Contributions

A.H.R.R., L.M.F.M. and S.I.S.J. conceived and designed the experiments; A.H.R.R., T.M.d.S. and. L.M.F.M. performed the experiments; A.H.R.R., T.M.d.S., L.M.F.M. and S.I.S.J. analyzed the data; A.H.R.R., L.M.F.M. and S.I.S.J. contributed materials/analysis tools; A.H.R.R. and T.M.S. wrote the paper.

Conflicts of Interest

The authors declare no conflict of interest.

Abbreviations

The following abbreviations are used in this manuscript:

| AC | Alternating Current |

| DC | Direct Current |

| CCM | Continuous Conduction Mode |

| CIECA | Current Injected Equivalent Circuit Approach |

| DCM | Discontinuous Conduction Mode |

| ELM | Euler–Lagrange Model |

| FLC | Feedback Linearization Control |

| PBC | Passivity-Based Control |

| IDAPBC | Interconnection and Damping Assignment Passivity-Based Control |

| IDAPBC-BB | Interconnection and Damping Assignment Passivity-Based Control—Based on the Boost Converter |

| PCH | Port-Controlled Hamiltonian |

| SSM | State-Space Model |

Nomenclature

| vg | Input voltage |

| d | Duty cycle |

| iL1 | Inductor current |

| iL2 | Inductor current |

| vo | Capacitor voltage |

| io | Output load current |

| L1 | Primary-side inductance |

| L2 | Secondary-side inductance |

| Co | Output capacitance |

| G | Load conductance |

| RL | Load resistance |

Appendix A. Reactive Elements of Power Circuits

The choice of the power circuit reactive elements of the SEPIC PFC converter in DCM, discussed in this work, is directly influenced by the operation mode of this converter. Based on the work of [16], these design specification are calculated, as seen in Table A1.

Table A1.

Design specifications.

Table A1.

Design specifications.

| Parameters | Value | Unity |

|---|---|---|

| Input voltage () | 127 | |

| Frequency (f) | 60 | Hz |

| Nominal power () | 100 | W |

| Output voltage () | 100 | V |

| Resistive load () | 100 | |

| Switch frequency () | 50 | kHz |

| Inductors () | 4/100 | mH/µH |

| Capacitors () | 470/330 | nF/µF |

Thus, the DCM operation requires:

Note that in Figure 3, the average current in the load can be represented by the ratio of the output voltage and the load impedance . However, the amplitude of this current was previously defined in (5). Therefore, the nominal duty cycle can now be calculated as:

where is the parameter given by:

At this discussion point, from the results presented in (A1) and (A2), it is necessary to establish a critical parameter, which will define the operating modes of the PFC SEPIC, in terms of the ratio M. Hence, we have:

Note that the DCM operation requires .

Next, the inductor parameters and are calculated in view of the current ripple term:

Therefore, considering the worst case ( = 90°), the value is defined by evaluation of (A5) and the specification of the maximum admissible ripple :

Finally, the value of the intermediate capacitor , which strongly influences the input current waveform of the SEPIC PFC converter, will be calculated. According to [16], a good choice is:

where is the angular frequency of , and , generally allocated between the angular frequency of the ac w and switching frequency , that is .

Appendix B. IDA-PBC Control for Boost Converter

The average boost converter circuit can be written by Euler–Lagrange equations, as:

with:

The equivalent state space equations are:

The modeling and IDA-PBC control of the boost converter are presented in [22]. Consecutively, the Port-Controlled Hamiltonian model (PCH) can be rearranged by the ELM to obtain:

By the equation, d as a constant value in (A14), (A15) and , as an equilibrium value, this leads to:

Let us now consider the desired output capacitor voltage as , the equilibrium point to stabilize and the constant input control given by:

The main objective of IDA-PCB control is to find a static function through space state feedback, . Thus, the closed loop dynamics becomes a Port-Controlled Hamiltonian (PCH), given by:

where the new function has a local minimum at the desired equilibrium point, . The terms and are the desired interconnection and damping matrices, respectively. Now, given the system:

Taking into account the damping term , given by:

this leads to the following matrix:

Substituting in (A18), (A19) and assuming and invertible, the gain control vector K is obtained:

The sufficient and necessary condition for making the K vector a gradient of a scalar function is:

Then, this condition is reduced to a simple Ordinary Differential Equation (ODE):

which can be easily solved through the variable separation method, leading to:

The constant is chosen in such a way so as to ensure the equilibrium form:

which implies:

and the IDA-PBC control equation:

Substituting (A17) in (A28) derives:

References

- Abidin, M.N.Z. IEC 61000-3-2 Harmonics Standards Overview; Schaffner EMC Inc.: Edsion, NJ, USA, 2006. [Google Scholar]

- Liu, Y.; Sun, Y.; Su, M. A Control Method for Bridgeless Cuk/Sepic PFC Rectifier to Achieve Power Decoupling. IEEE Trans. Ind. Electron. 2017, 64, 7272–7276. [Google Scholar] [CrossRef]

- Huang, L.; Chen, F.; Yao, W.; Lu, Z. Flexible Mode Bridgeless Boost PFC Rectifier with High Efficiency over a Wide Range of Input Voltage. IEEE Trans. Power Electron. 2017, 32, 3513–3524. [Google Scholar] [CrossRef]

- Youn, H.; Park, J.; Park, K.; Baek, J.; Moon, G. A digital predictive peak current control for power factor correction with low-input current distortion. IEEE Trans. Power Electron. 2016, 31, 900–912. [Google Scholar] [CrossRef]

- Kim, Y.; Sung, W.; Lee, B. Comparative performance analysis of high density and efficiency PFC topologies. IEEE Trans. Power Electron. 2014, 29, 2666–2679. [Google Scholar] [CrossRef]

- Moradpour, R.; Ardi, H.; Tavakoli, A. Design and Implementation of a New SEPIC-Based High Step-up DC/DC Converter for Renewable Energy Applications. IEEE Trans. Ind. Electron. 2018, 85, 1290–1297. [Google Scholar] [CrossRef]

- Wang, Y.; Qi, N.; Guan, Y.; Cecati, C.; Xu, D. A Single-Stage LED Driver Based on SEPIC and LLC Circuits. IEEE Trans. Ind. Electron. 2017, 64, 5766–5776. [Google Scholar] [CrossRef]

- Poorali, B.; Adib, E. Analysis of the integrated SEPIC-flyback converter as a single-stage single-switch power-factor-correction LED driver. IEEE Trans. Ind. Electron. 2016, 63, 3562–3570. [Google Scholar] [CrossRef]

- Al-Saffar, M.; Ismail, E. A high voltage ratio and low stress DC–DC converter with reduced input current ripple for fuel cell source. Renew. Energy 2015, 82, 35–43. [Google Scholar] [CrossRef]

- Shi, C.; Khaligh, A.; Wang, H. Interleaved SEPIC Power Factor Preregulator Using Coupled Inductors in Discontinuous Conduction Mode with Wide Output Voltage. IEEE Trans. Ind. Appl. 2016, 52, 3461–3471. [Google Scholar] [CrossRef]

- Sabzali, A.; Ismail, E.H.; Behbehani, H. High voltage step-up integrated double Boost–Sepic DC–DC converter for fuel-cell and photovoltaic applications. Renew. Energy 2015, 82, 44–53. [Google Scholar] [CrossRef]

- Kumar, K.; Babu, N.R.; Prabhu, K. Design and Analysis of an Integrated Cuk-SEPIC Converter with MPPT for Standalone Wind/PV Hybrid System. Int. J. Renew. Energy Res. 2017, 7, 96–106. [Google Scholar]

- Hussain, J.; Mishra, M. Adaptive maximum power point tracking control algorithm for wind energy conversion systems. IEEE Trans. Energy Convers. 2016, 31, 697–705. [Google Scholar] [CrossRef]

- Kanaan, H.Y.; Al-Haddad, K. A novel averaged-model-based control of a SEPIC power factor corrector using the input/output feedback linearization technique. In Proceedings of the IEEE 36th Power Electronics Specialists Conference, PESC’05, Recife, Brazil, 16 June 2005; pp. 565–571. [Google Scholar]

- Meghnous, A.R.; Pham, M.T.; Lin-Shi, X. Nonlinear observer and Lyapunov-based control for SEPIC converter: Design and experimental results. In Proceedings of the IEEE American Control Conference (ACC), Washington, DC, USA, 17–19 June 2013; pp. 5833–5838. [Google Scholar]

- Simonetti, D.S.L.; Sebastian, J.; Uceda, J. The discontinuous conduction mode Sepic and Cuk power factor preregulators: Analysis and design. IEEE Trans. Ind. Electron. 1997, 44, 630–637. [Google Scholar] [CrossRef]

- Chetty, P. Current injected equivalent circuit approach to modeling switching dc-dc converters. IEEE Trans. Aerosp. Electron. Syst. 1981, 802–808. [Google Scholar] [CrossRef]

- Erickson, R.W.; Maksimovic, D. Fundamentals of Power Electronics; Springer Science & Business Media: New York, NY, USA, 2007. [Google Scholar]

- Stepins, D.; Huang, J. Effects of Switching Frequency Modulation on Input Power Quality of Boost Power Factor Correction Converter. Int. J. Power Electron. Drive Syst. 2017, 8, 882–899. [Google Scholar] [CrossRef][Green Version]

- Rao, V.M.; Jain, A.K.; Reddy, K.K.; Behal, A. Experimental comparison of digital implementations of single-phase PFC controllers. IEEE Trans. Ind. Electron. 2008, 55, 67–78. [Google Scholar] [CrossRef]

- Sira-Ramírez, H.; Ortega, R.; García-Esteban, M. Adaptive passivity-based control of average DC-to-DC power converter models. Int. J. Adapt. Control Signal Process. 1998, 12, 63–80. [Google Scholar] [CrossRef]

- Rodriguez, H.; Ortega, R.; Escobar, G. A new family of energy-based non-linear controllers for switched power converters. In Proceedings of the ISIE 2001 IEEE International Symposium on Industrial Electronics, Pusan, Korea, 12–16 June 2001; Volume 2, pp. 723–727. [Google Scholar]

- Padhi, B.K.; Padhy, S.N. Controller Design for Reduced Order model of SEPIC Converter. In Proceedings of the 2016 International Conference on Signal Processing, Communication, Power and Embedded System (SCOPES), Paralakhemundi, India, 3–5 October 2016; Volume 1, pp. 1533–1538. [Google Scholar]

- Shieh, H.J.; Chen, Y.Z. A Sliding Surface-Regulated Current-Mode Pulse-Width Modulation Controller for a Digital Signal Processor-Based Single Ended Primary Inductor Converter-Type Power Factor Correction Rectifier. Energies 2017, 10, 1175. [Google Scholar] [CrossRef]

- Zhang, M.; Ortega, R.; Liu, Z.; Su, H. A new family of interconnection and damping assignment passivity-based controllers. Int. J. Robust Nonlinear Control 2017, 27, 50–65. [Google Scholar] [CrossRef]

- Rosa, A.H.R.; Morais, L.M.F.; Seleme, I.S. Hardware in the loop simulation of non linear control methods applied for power converters. In Proceedings of the 2015 IEEE 13th Brazilian Power Electronics Conference and 1st Southern Power Electronics Conference (COBEP/SPEC), Fortaleza, Brazil, 29 November– 2 December 2015; pp. 1–6. [Google Scholar]

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).