Initialization and Synchronization of Power Hardware-In-The-Loop Simulations: A Great Britain Network Case Study

Abstract

:1. Introduction

- The power network within the DRTS is initialized, allowing for it to achieve steady state (referred to as initialization in this work).

- Interface signals from the initialized DRTS simulation are reproduced by the power interface.

- The HUT response to the reproduced signals is measured and fed back to the DRTS to complete the loop (referred to as synchronization in this work).

2. PHIL Initialization and Synchronization

2.1. The Challenge

- HUT critical for initialization: In such cases, the initialization and synchronization of the PHIL experiment present a paradoxical scenario where the DRTS simulation cannot be initialized without the hardware currents, while the hardware currents cannot be produced without the DRTS simulation being initialized. To elaborate, the DRTS simulation will fail to initialize due to a lack of generation or load leading to not enough synchronizing torque in the simulated network. Without the DRTS simulation initialized, the power interface will not be capable of reproducing the interface signals and therefore the HUT response cannot be synchronized. On the other hand, reproducing the interface signal during the initialization of DRTS is risky as the signal might not be suitable for reproduction or may be over the safety limits of the power amplifier and HUT.

- HUT affects voltage and frequency: Here, the HUT is not critical (the simulation can start without it connected) but still significant as to affect the frequency and voltage considerably triggering control actions from the components in the simulation, leading to a modified initial state of the system. This can also result in an impractical voltage and frequency levels for the initialization of the HUT.

2.2. Initialization of DRTS Simulation

- Detailed simulation of HUT: a detailed model of the HUT can be included as part of the simulation for establishing the initial conditions of the DRTS simulation. However, developing a detailed model of the HUT can be an arduous task, and considering that the expected power flows at the PCC can typically be estimated, simpler solutions can be utilized for the initialization process.

- AC voltage source: readily available in every power system simulation tool, voltage source models can be utilized to initialize the simulated test network for PHIL simulations, emulating the HUT. However, as AC voltage sources act as infinite sources, the power flow of the network at the PCC cannot be controlled. This would lead to, an unsuccessful initialization, as the state of the network is no longer the intended for the test scenario. Additionally, with the change in power flows, new stability analyses would need to be undertaken as the system state under which the HUT was intended to be connected is no longer the same, unless an adjustment of the power setpoints is performed until power exchange with the infinite bus is brought to zero.

- Synchronous generator: a synchronous generator model can control the active power at its output terminals for emulating the HUT required active power transfers at the PCC, this being controlled by means of a simple set-point. The reactive power of a synchronous generator is controlled by manipulating the excitation system. Either manual tuning of the voltage reference to the exciter or developing a simple PI control is required to attain the required reactive power flow at the PCC.

- AC Controlled Current Source: for the emulation of the HUT power transfer at the PCC, a controlled current source allows for a straightforward implementation with high accuracy. This implementation will only require the measured voltage and the P and Q set points at the PCC for generating the current signals as shown:where Id is the direct axis current, Iq is the quadrature axis current, Pref and Qref are the reference active and reactive powers to be injected at the PCC respectively, Vd is the direct axis voltage at the PCC and Vq is the quadrature axis voltage at PCC. The direct and quadrature axis voltages required can be obtained with Park’s transformation as:

2.3. Synchronization

- Detailed simulation of HUT: while this could be the best option for the purpose of initialization of PHIL, assuming an accurate enough model of HUT is available, for the purpose of synchronization, a dispatching algorithm to reduce the generation and load of the emulated HUT would be required to avoid the frequency going to abnormal values when the HUT is first connected. It can therefore be said that, utilizing a detailed model of the HUT is very challenging for initialization and synchronization of PHIL setups due to the requirement of developing dedicated HUT models and dispatch algorithms.

- AC voltage source: Apart from the fact that the AC voltage source is not the ideal approach for initialization due to its response as an infinite source, similarly, the power output of the voltage source cannot be controlled and the process can lead to an erroneous synchronization.

- Synchronous generator: In order to attain a smooth transition from the auxiliary emulated HUT (the synchronous generator) and the HUT, a complex control would be required (for governor and excitation system) to ensure least deviation in frequency and voltage during the process. This controller would be a generic solution that can be reused, however, would be limited to scenarios where the HUT effectively emulates generation.

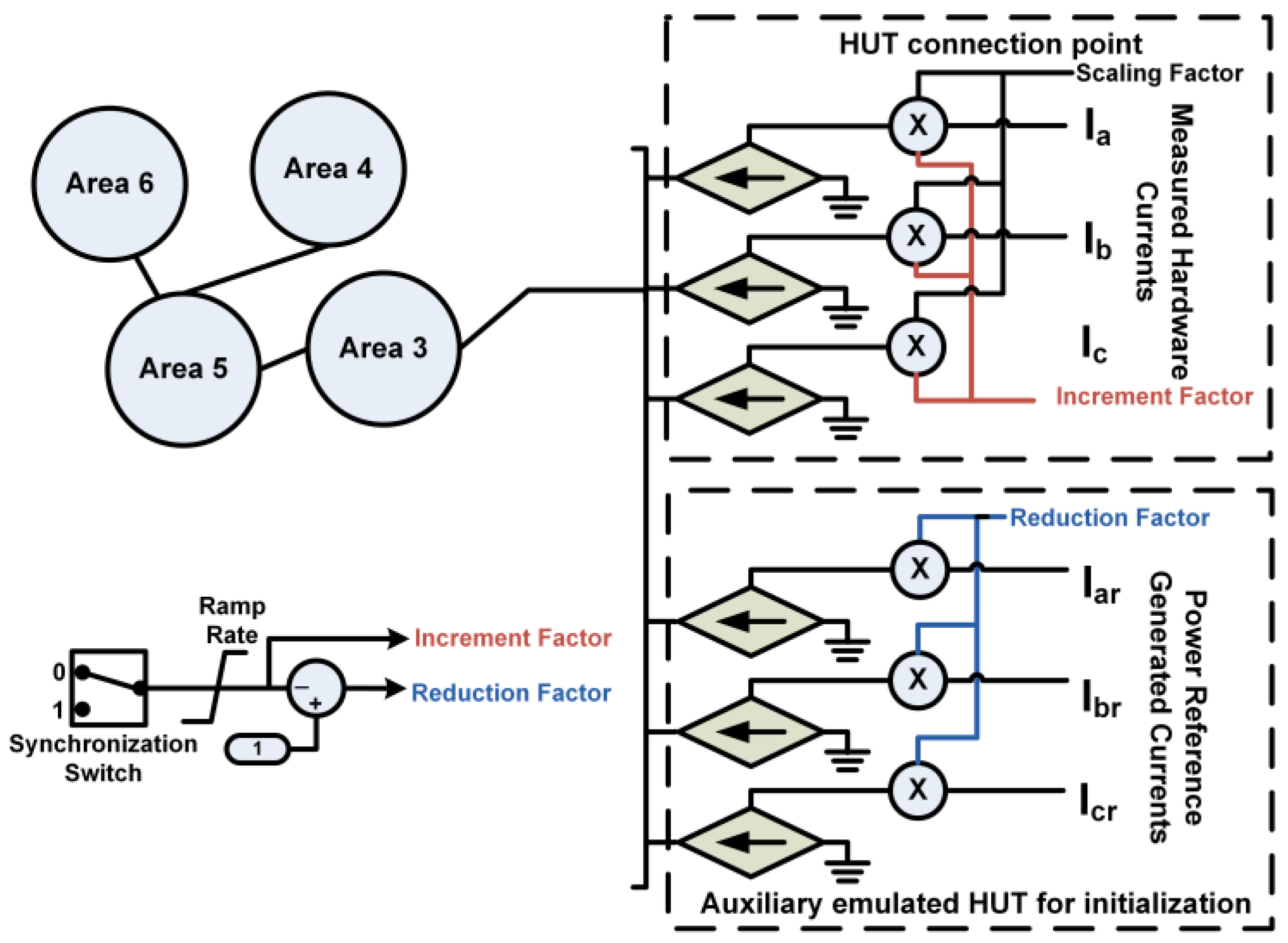

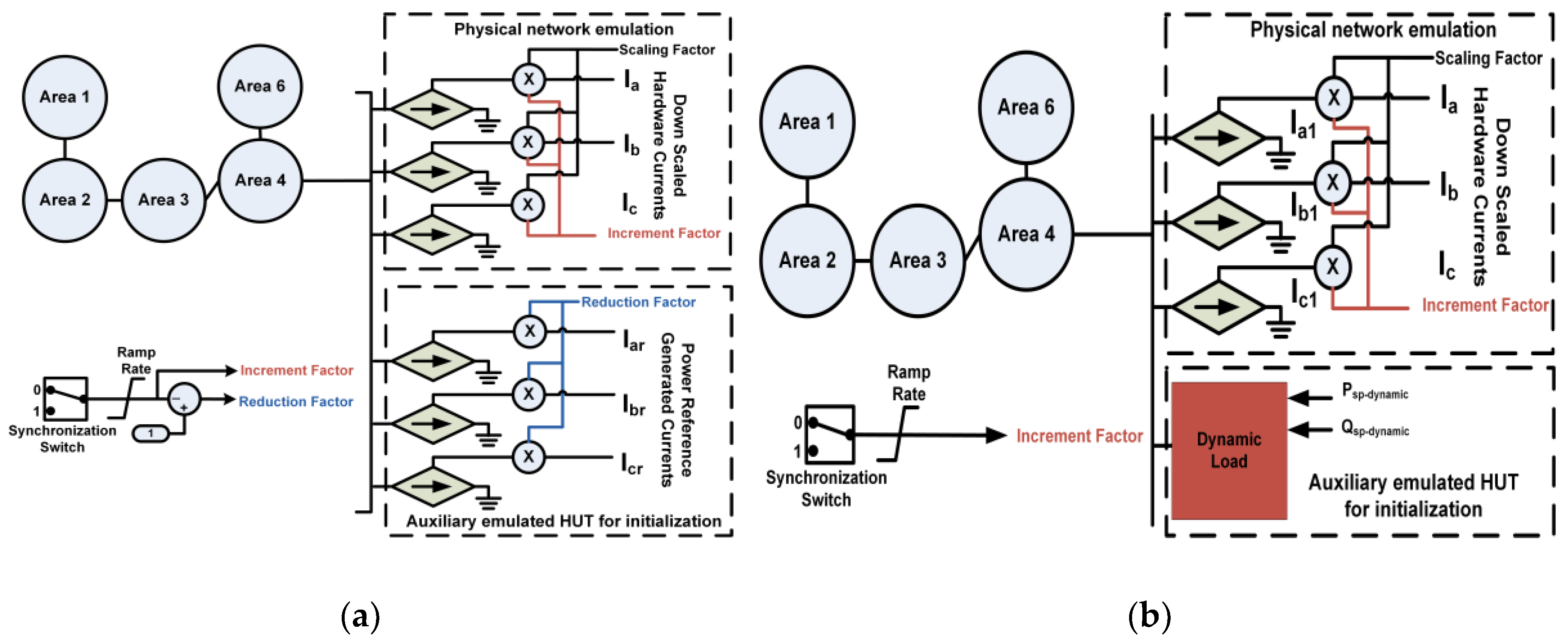

- AC Controlled Current Source: if a controlled current source is utilized, the synchronization can be achieved with a proposed simple logic as presented in Figure 2. The synchronization process is begun by means of a synchronization switch that inversely ramps up and down both controlled current sources. The ramp rate can be chosen such that it doesn’t create any oscillations or transients on the system, once the currents from the auxiliary emulated HUT are reduced to zero and the currents from the HUT are fully connected to the simulation, the system is synchronized.

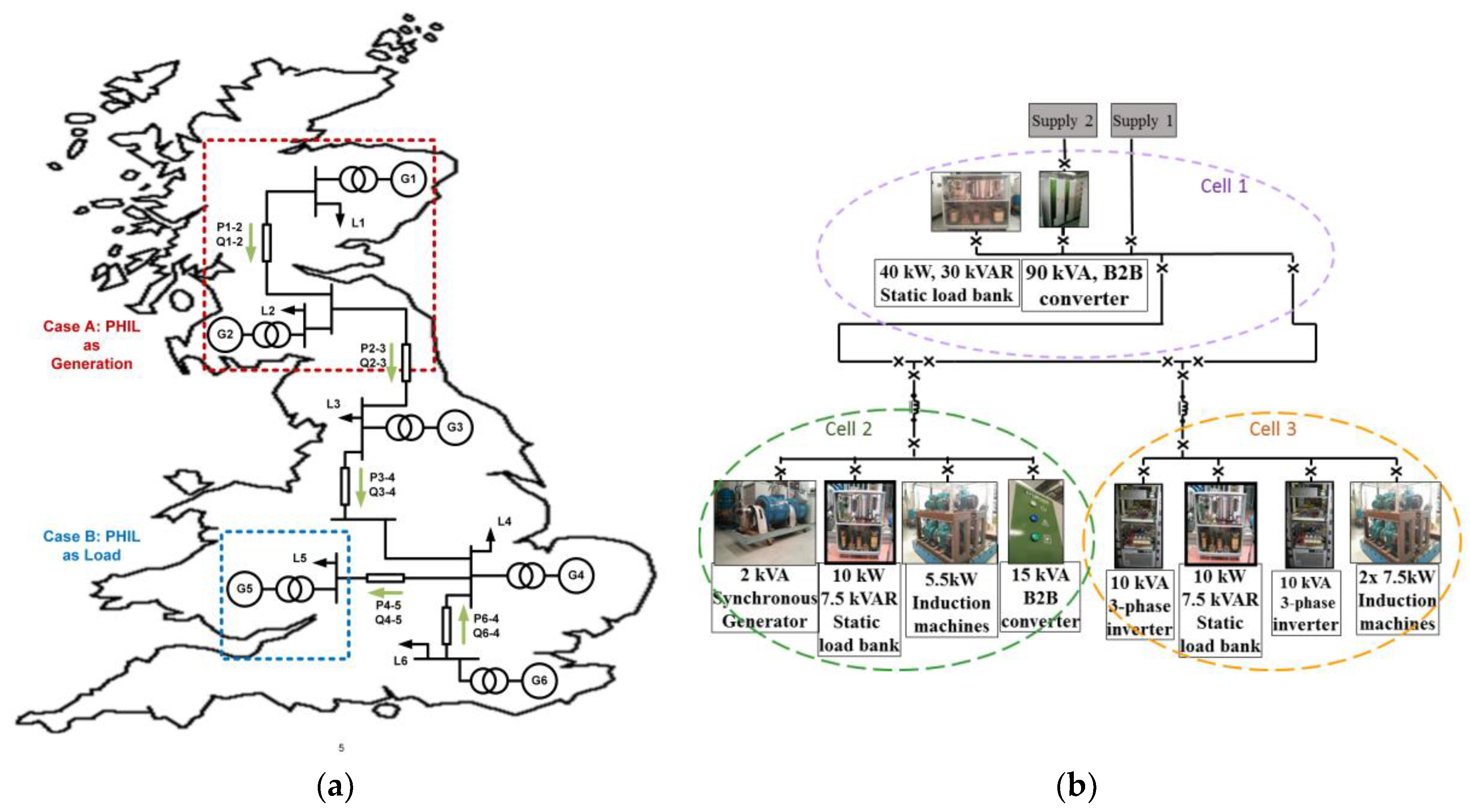

3. Experimental Setup for PHIL

3.1. GB Power System

3.2. Power Interface

3.3. HUT

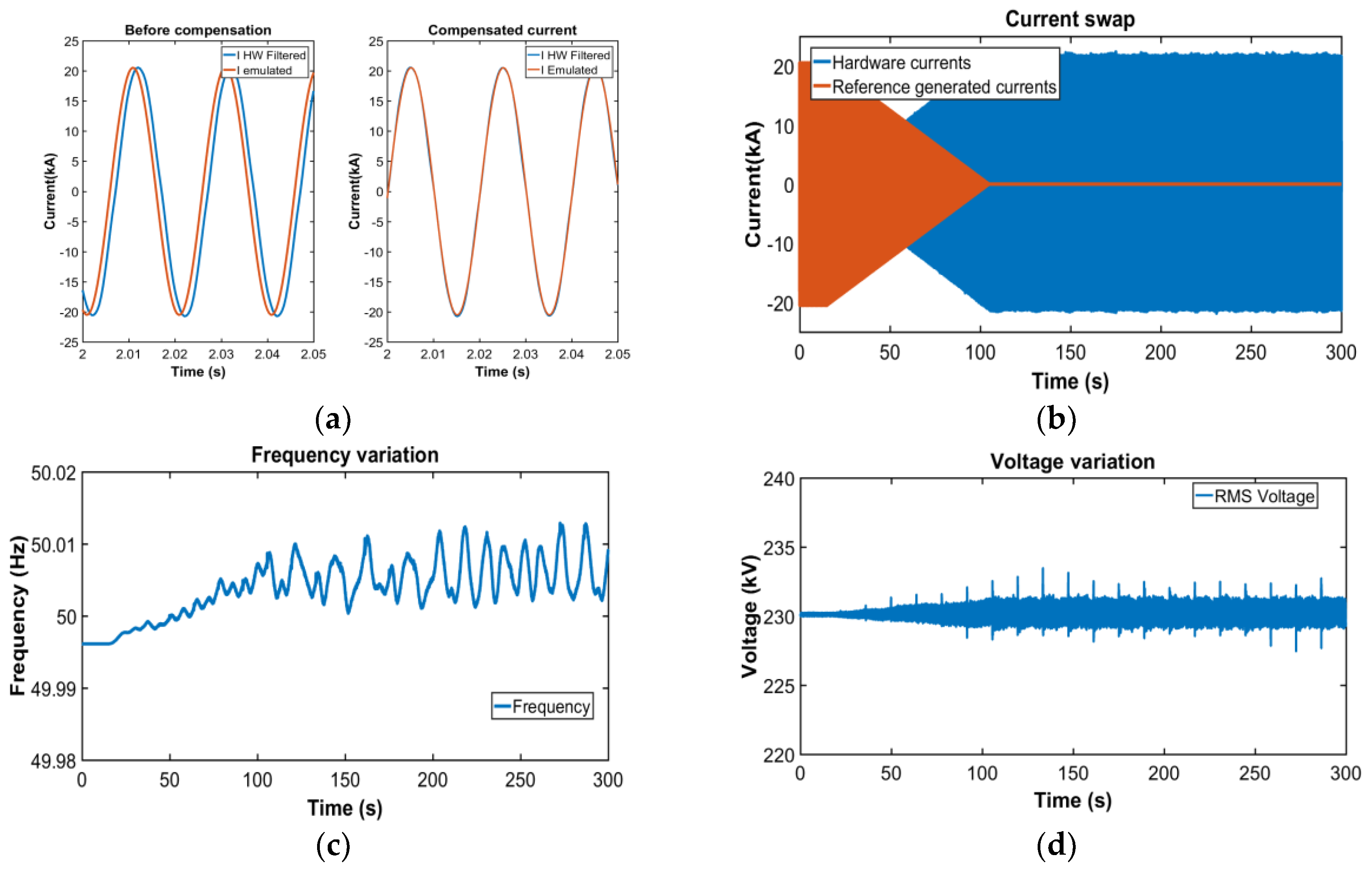

3.4. Time Delay Compensation

4. Experimental Assessment and Validation

5. Conclusions

Author Contributions

Acknowledgments

Conflicts of Interest

References

- Strasser, T.; Andrén, F.P.; Lauss, G.; Bründlinger, R.; Brunner, H.; Moyo, C.; Seitl, C.; Rohjans, S.; Lehnhoff, S.; Palensky, P.; et al. e & i Elektrotechnik und Informationstechnik; Springer: Vienna, Austria, 2017; Volume 134, pp. 71–77. [Google Scholar]

- Kotsampopoulos, P.C.; Lehfuss, F.; Lauss, G.F.; Bletterie, B.; Hatziargyriou, N.D. The Limitations of Digital Simulation and the Advantages of PHIL Testing in Studying Distributed Generation Provision of Ancillary Services. IEEE Trans. Ind. Electron. 2015, 62, 5502–5515. [Google Scholar] [CrossRef]

- Edrington, C.S.; Steurer, M.; Langston, J.; El-Mezyani, T.; Schoder, K. Role of Power Hardware in the Loop in Modeling and Simulation for Experimentation in Power and Energy Systems. Proc. IEEE 2015, 103, 2401–2409. [Google Scholar] [CrossRef]

- Kotsampopoulos, P.; Kleftakis, V.; Messinis, G.; Hatziargyriou, N. Design, development and operation of a PHIL environment for Distributed Energy Resources. In Proceedings of the IECON 2012—38th Annual Conference on IEEE Industrial Electronics Society, Montreal, QC, Canada, 25–28 October 2012; pp. 4765–4770. [Google Scholar]

- Ren, W.; Steurer, M.; Woodruff, S. Applying Controller and Power Hardware-in-the-Loop Simulation in Designing and Prototyping Apparatuses for Future All Electric Ship. In Proceedings of the 2007 IEEE Electric Ship Technologies Symposium, Arlington, VA, USA, 21–23 May 2007; pp. 443–448. [Google Scholar]

- Langston, J.; Schoder, K.; Steurer, M.; Faruque, O.; Hauer, J.; Bogdan, F.; Bravo, R.; Mather, B.; Katiraei, F. Power hardware-in-the-loop testing of a 500 kW photovoltaic array inverter. In Proceedings of the IECON 2012—38th Annual Conference on IEEE Industrial Electronics Society, Montreal, QC, Canada, 25–28 October 2012; pp. 4797–4802. [Google Scholar]

- Naeckel, O.; Langston, J.; Steurer, M.; Fleming, F.; Paran, S.; Edrington, C.; Noe, M. Power Hardware-in-the-Loop Testing of an Air Coil Superconducting Fault Current Limiter Demonstrator. IEEE Trans. Appl. Superconduct. 2015, 25, 1–7. [Google Scholar] [CrossRef]

- Kotsampopoulos, P.; Hatziargyriou, N.; Bletterie, B.; Lauss, G.; Strasser, T. Introduction of advanced testing procedures including PHIL for DG providing ancillary services. In Proceedings of the IECON 2013—39th Annual Conference of the IEEE Industrial Electronics Society, Vienna, Austria, 10–13 November 2013; pp. 5398–5404. [Google Scholar]

- Zhu, K.; Chenine, M.; Nordstrom, L. ICT Architecture Impact on Wide Area Monitoring and Control Systems’ Reliability. IEEE Trans. Power Deliv. 2011, 26, 2801–2808. [Google Scholar] [CrossRef]

- Lauss, G.F.; Faruque, M.O.; Schoder, K.; Dufour, C.; Viehweider, A.; Langston, J. Characteristics and Design of Power Hardware-in-the-Loop Simulations for Electrical Power Systems. IEEE Trans. Ind. Electron. 2016, 63, 406–417. [Google Scholar] [CrossRef]

- Ren, W.; Steurer, M.; Baldwin, T.L. Improve the Stability and the Accuracy of Power Hardware-in-the-Loop Simulation by Selecting Appropriate Interface Algorithms. IEEE Trans. Ind. Appl. 2008, 44, 1286–1294. [Google Scholar] [CrossRef]

- Viehweider, A.; Lauss, G.; Felix, L. Stabilization of Power Hardware-in-the-Loop Simulations of Electric Energy Systems. Simul. Model. Pract. Theory 2011, 19, 1699–1708. [Google Scholar] [CrossRef]

- Hatakeyama, T.; Riccobono, A.; Monti, A. Stability and accuracy analysis of power hardware in the loop system with different interface algorithms. In Proceedings of the 2016 IEEE 17th Workshop on Control and Modeling for Power Electronics (COMPEL), Trondheim, Norway, 27–30 June 2016; pp. 1–8. [Google Scholar]

- Dargahi, M.; Ghosh, A.; Ledwich, G. Stability synthesis of power hardware-in-the-loop (PHIL) simulation. In Proceedings of the 2014 IEEE PES General Meeting | Conference & Exposition, National Harbor, MD, USA, 27–31 July 2014; pp. 1–5. [Google Scholar]

- Brandl, R. Operational Range of Several Interface Algorithms for Different Power Hardware-In-The-Loop Setups. Energies 2017, 10, 1946. [Google Scholar] [CrossRef]

- Liegmann, E.; Riccobono, A.; Monti, A. Wideband identification of impedance to improve accuracy and stability of power-hardware-in-the-loop simulations. In Proceedings of the 2016 IEEE International Workshop on Applied Measurements for Power Systems (AMPS), Aachen, Germany, 28–30 September 2016; pp. 1–6. [Google Scholar]

- Lehfuss, F.; Lauss, G.; Strasser, T. Implementation of a multi-rating interface for Power-Hardware-in-the-Loop simulations. In Proceedings of the IECON 2012—38th Annual Conference on IEEE Industrial Electronics Society, Montreal, QC, Canada, 25–28 October 2012; pp. 4777–4782. [Google Scholar]

- Yu, M.; Roscoe, A.J.; Dyśko, A.; Booth, C.D.; Ierna, R.; Zhu, J.; Urdal, H. Instantaneous Penetration Level Limits of Non-Synchronous Devices in the British Power System. IET Renew. Power Gener. 2016, 11, 1211–1217. [Google Scholar] [CrossRef]

- National Grid. Electricity Ten Year Statement 2016; National Grid: Warwick, UK, 2016. [Google Scholar]

- Lentijo, S.; D’Arco, S.; Monti, A. Comparing the Dynamic Performances of Power Hardware-in-the-Loop Interfaces. IEEE Trans. Ind. Electron. 2010, 57, 1195–1207. [Google Scholar] [CrossRef]

- De Jong, E.; de Graff, R.; Vassen, P.; Crolla, P.; Roscoe, A.; Lefuss, F.; Lauss, G.; Kotsampopoulos, P.; Gafaro, F. European White Book on Real-Time Power Hardware in the Loop Testing; DERlab: Kassel, Germany, 2012. [Google Scholar]

- Guillo-Sansano, E.; Roscoe, A.J.; Burt, G.M. Harmonic-by-harmonic time delay compensation method for PHIL simulation of low impedance power systems. In Proceedings of the 2015 International Symposium on Smart Electric Distribution Systems and Technologies (EDST), Vienna, Austria, 8–11 September 2015; pp. 560–565. [Google Scholar]

| Capacity and Loading Conditions | Area 1 | Area 2 | Area 3 | Area 4 | Area 5 | Area 6 |

|---|---|---|---|---|---|---|

| Area wise generation capacity (MVA) | 11,000 | 20,000 | 9160 | 5500 | 15,500 | 2000 |

| Area wise active power load (MW) | 8468 | 12,548 | 8398 | 2150 | 26,852 | 100 |

| Area wise reactive power load (MVAr) | 4109 | 6077 | 4067 | 1041 | 13,005 | 500 |

| Inter-area active power flow (MW) | P1-2 | P2-3 | P3-4 | P4-5 | P6-4 |

| 2097 | 8900 | 9105 | 13,080 | 970 | |

| Inter-area reactive power flow (MVAr) | Q1-2 | Q2-3 | Q3-4 | Q4-5 | Q6-4 |

| 1328 | 4257 | 5025 | 7088 | 155 |

| Area | Component | P (W) | Q (Var) |

|---|---|---|---|

| Cell 2 | 15 kVA B2B Inverter | 7000 | 3600 |

| 2 kVA Synchronous Generator | 1500 | 0 | |

| Load Bank 2 | −1500 | 0 | |

| Cell 3 | 10 kVA Inverter | 6600 | 1100 |

| Load Bank 3 | −3300 | 0 |

| Area | Component | P (W) | Q (Var) |

|---|---|---|---|

| Cell 1 | Load Bank 1 | −14,000 | −7900 |

| Cell 2 | 15 kVA B2B Inverter | 4500 | −3000 |

| 2 kVA Synchronous Generator | 1000 | 0 | |

| Load Bank 2 | −9000 | −3500 | |

| Cell 3 | 10 kVA Inverter | 5200 | 0 |

| Load Bank 3 | −9000 | −3500 | |

| Induction motor | −4700 | −3000 |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Guillo-Sansano, E.; H. Syed, M.; J. Roscoe, A.; M. Burt, G. Initialization and Synchronization of Power Hardware-In-The-Loop Simulations: A Great Britain Network Case Study. Energies 2018, 11, 1087. https://doi.org/10.3390/en11051087

Guillo-Sansano E, H. Syed M, J. Roscoe A, M. Burt G. Initialization and Synchronization of Power Hardware-In-The-Loop Simulations: A Great Britain Network Case Study. Energies. 2018; 11(5):1087. https://doi.org/10.3390/en11051087

Chicago/Turabian StyleGuillo-Sansano, Efren, Mazheruddin H. Syed, Andrew J. Roscoe, and Graeme M. Burt. 2018. "Initialization and Synchronization of Power Hardware-In-The-Loop Simulations: A Great Britain Network Case Study" Energies 11, no. 5: 1087. https://doi.org/10.3390/en11051087

APA StyleGuillo-Sansano, E., H. Syed, M., J. Roscoe, A., & M. Burt, G. (2018). Initialization and Synchronization of Power Hardware-In-The-Loop Simulations: A Great Britain Network Case Study. Energies, 11(5), 1087. https://doi.org/10.3390/en11051087