The Impact of PLL Dynamics on the Low Inertia Power Grid: A Case Study of Bonaire Island Power System

Abstract

:1. Introduction

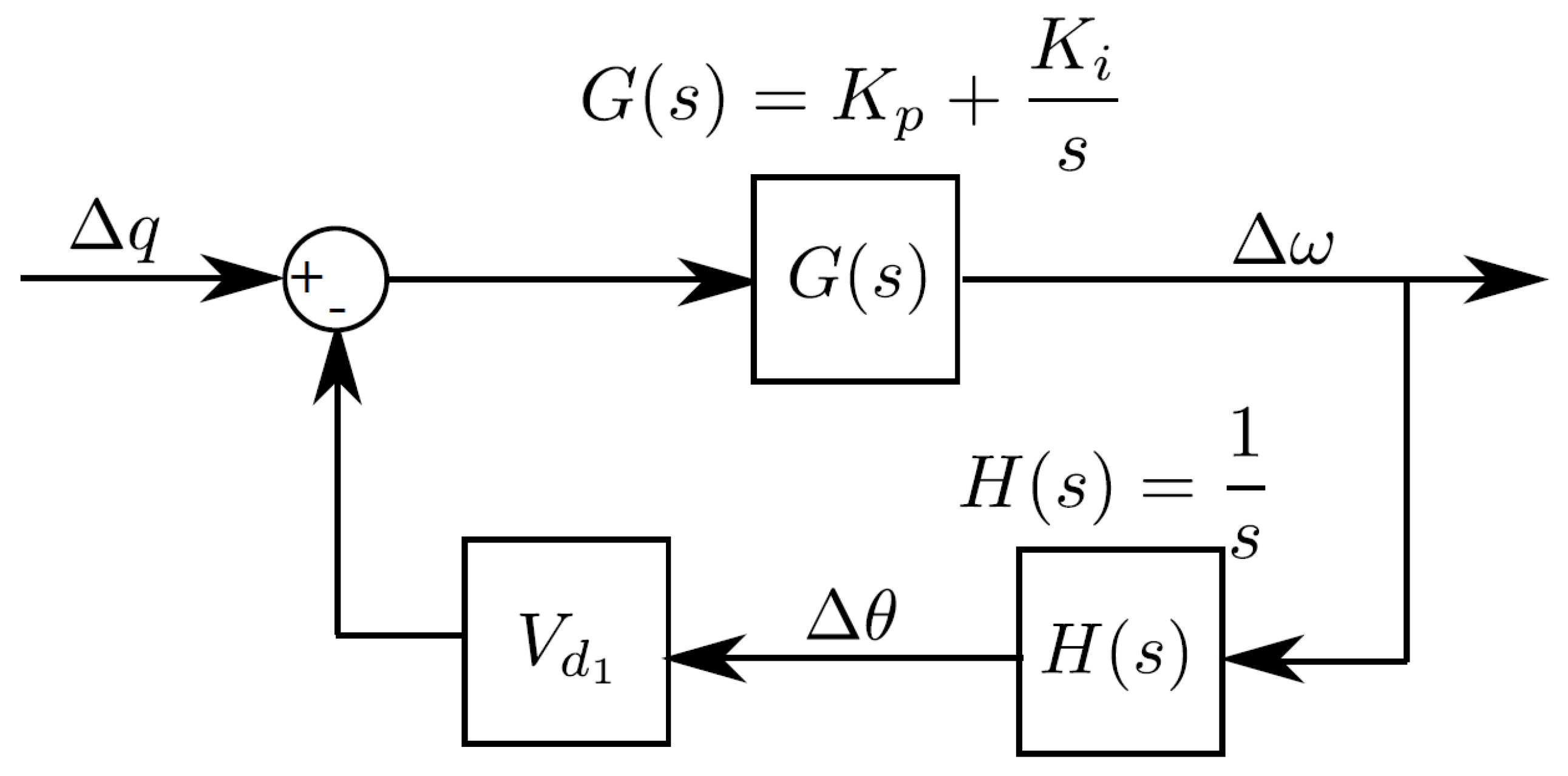

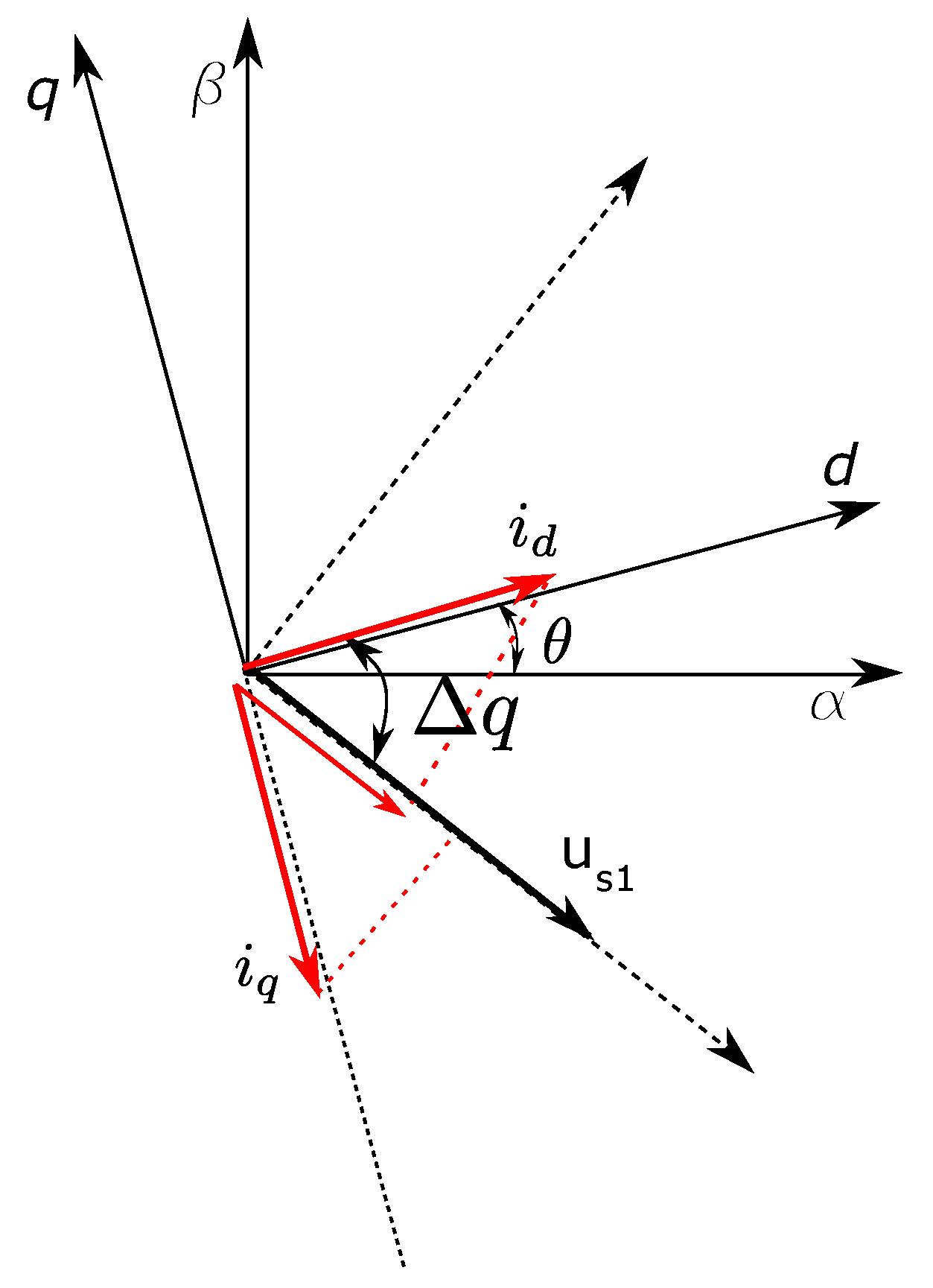

2. PLL Modelling and Analysis

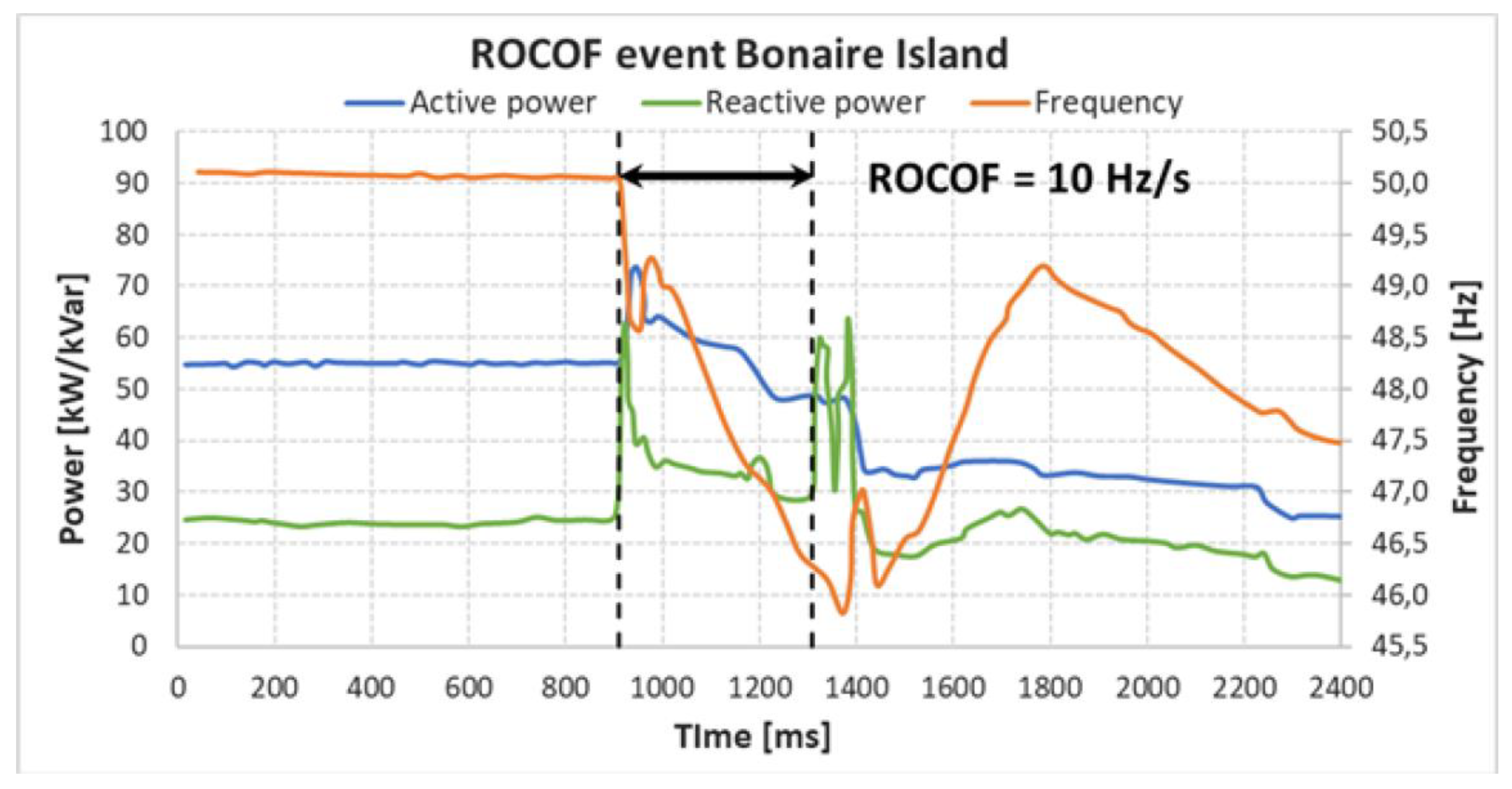

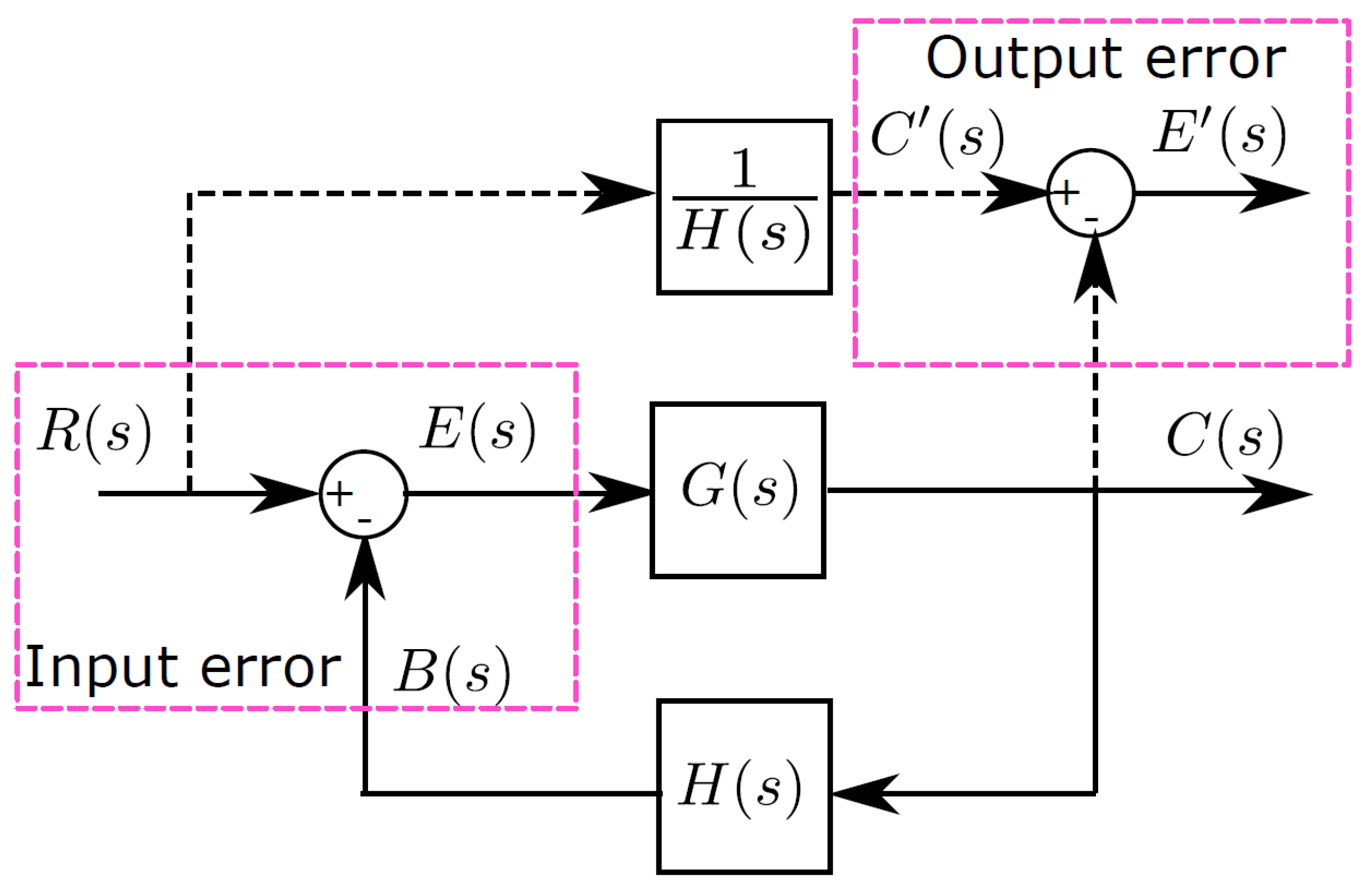

2.1. Feedback Control System Error

2.2. PLL Steady State Error

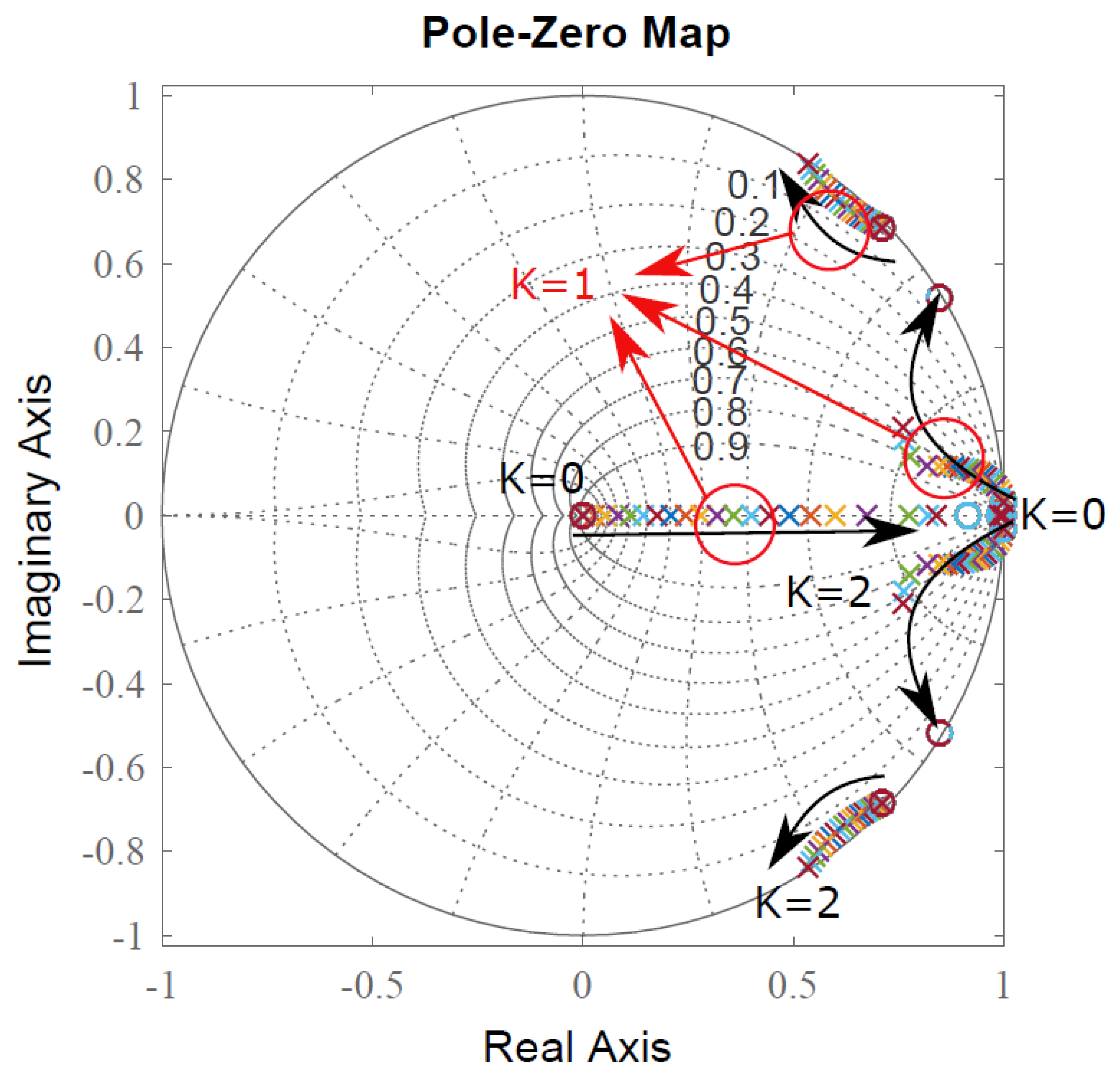

2.3. System Stability and PLL Controller Bandwidth

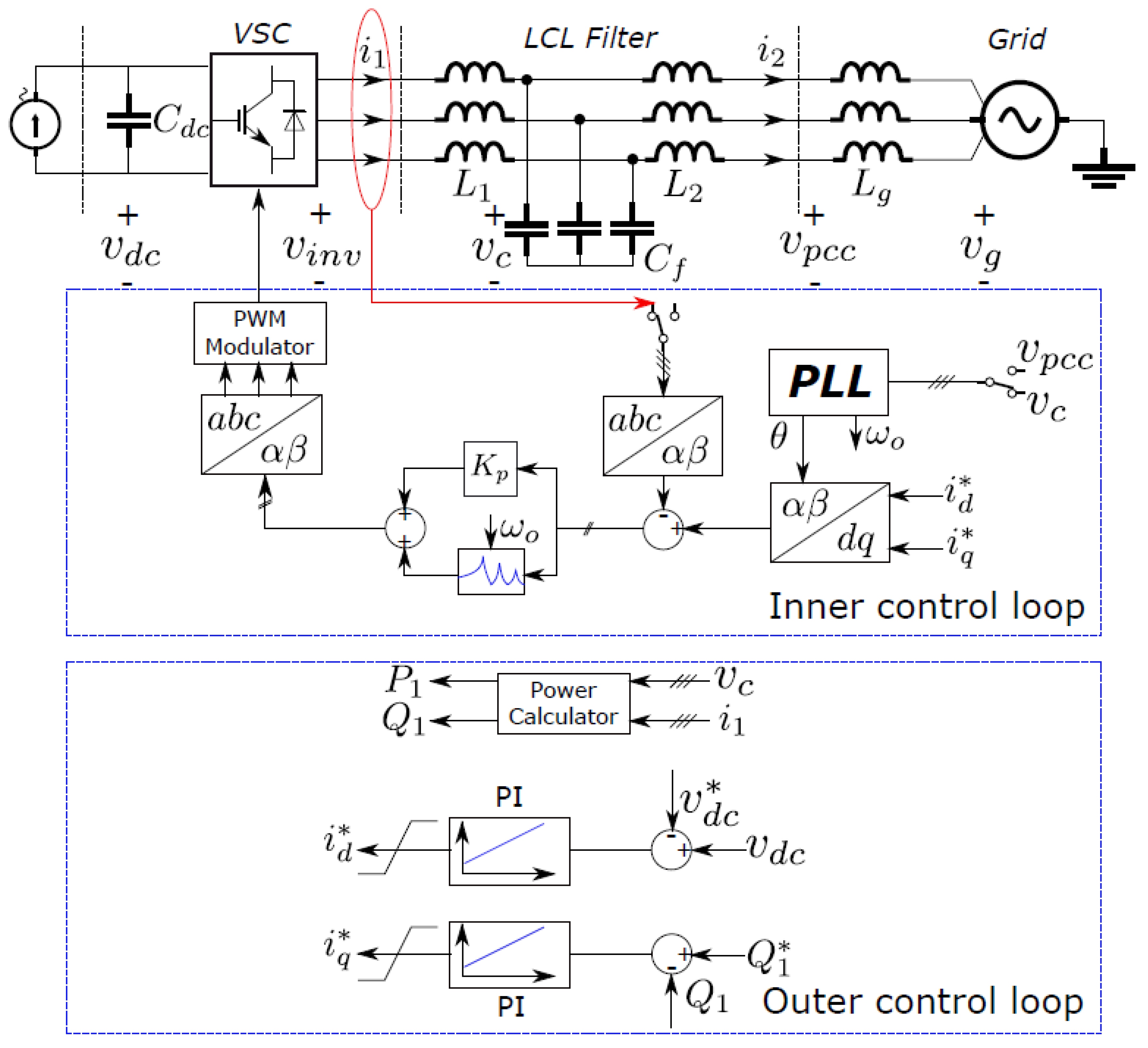

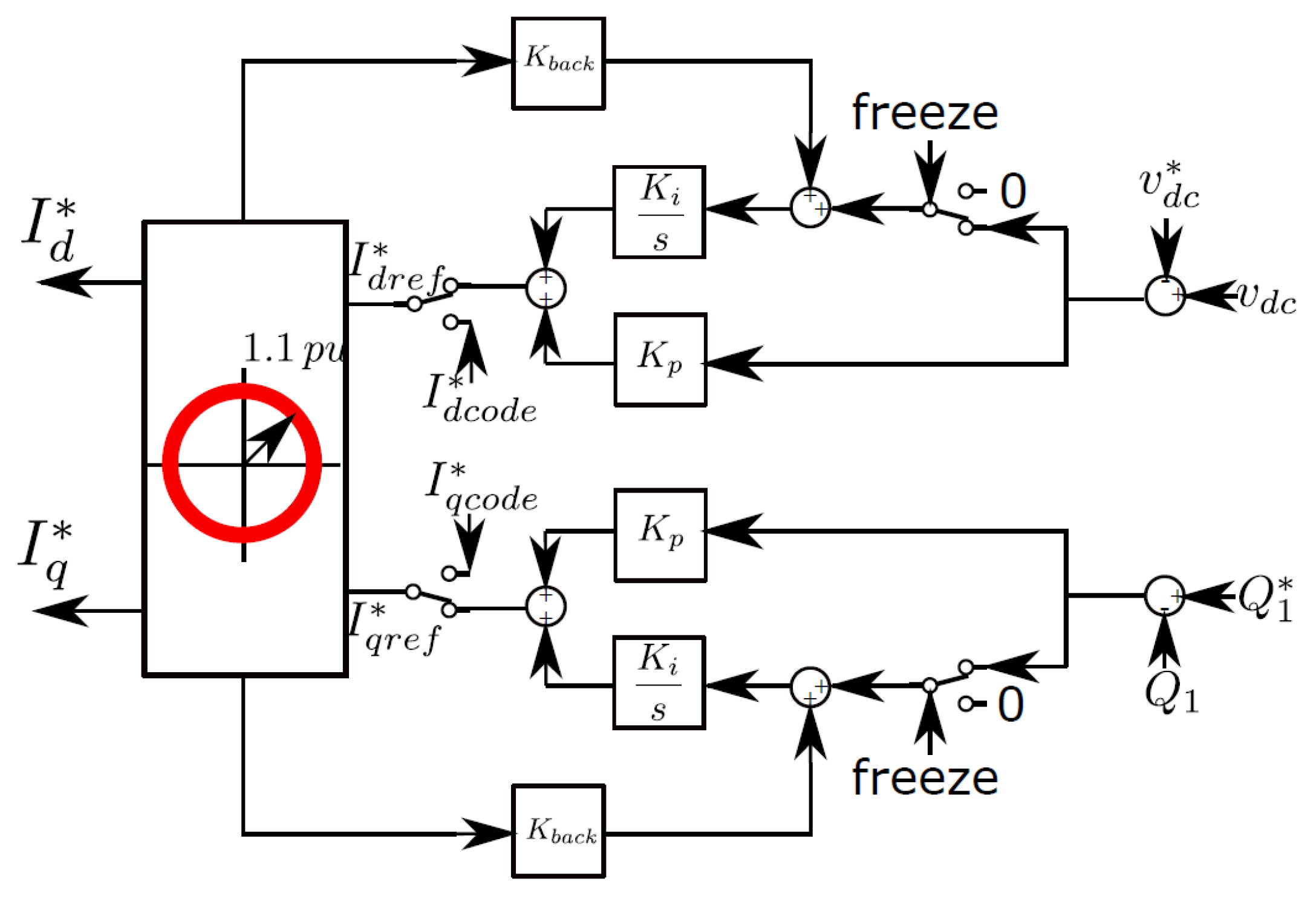

3. VSC Modelling and Analysis

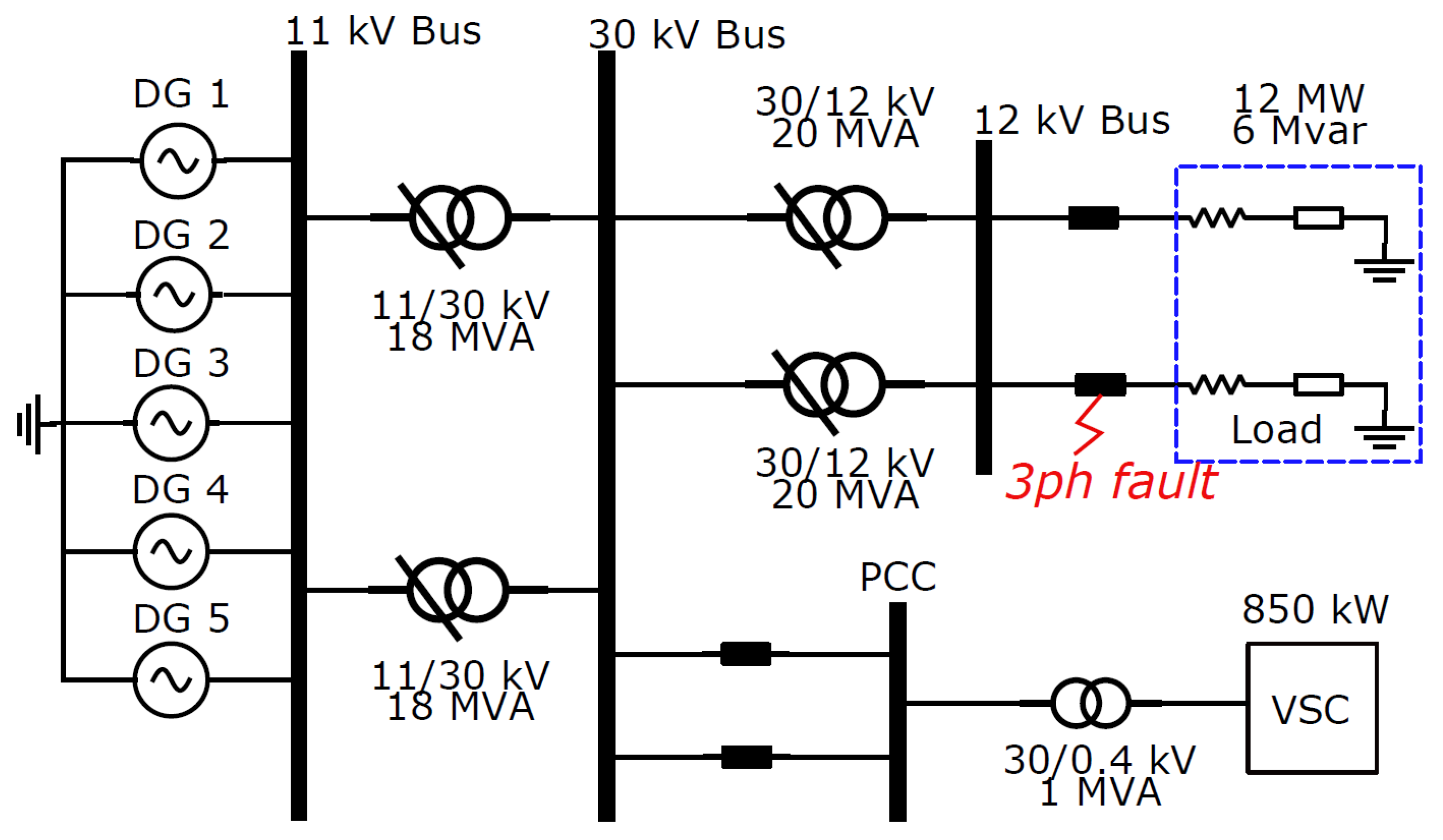

3.1. VSC Simulation Model

3.2. VSC Stability Analysis

4. Simulation and Experimental Results

4.1. Simulation Results—Simple Test Network

4.2. Simulation Results—Bonaire Island Power System

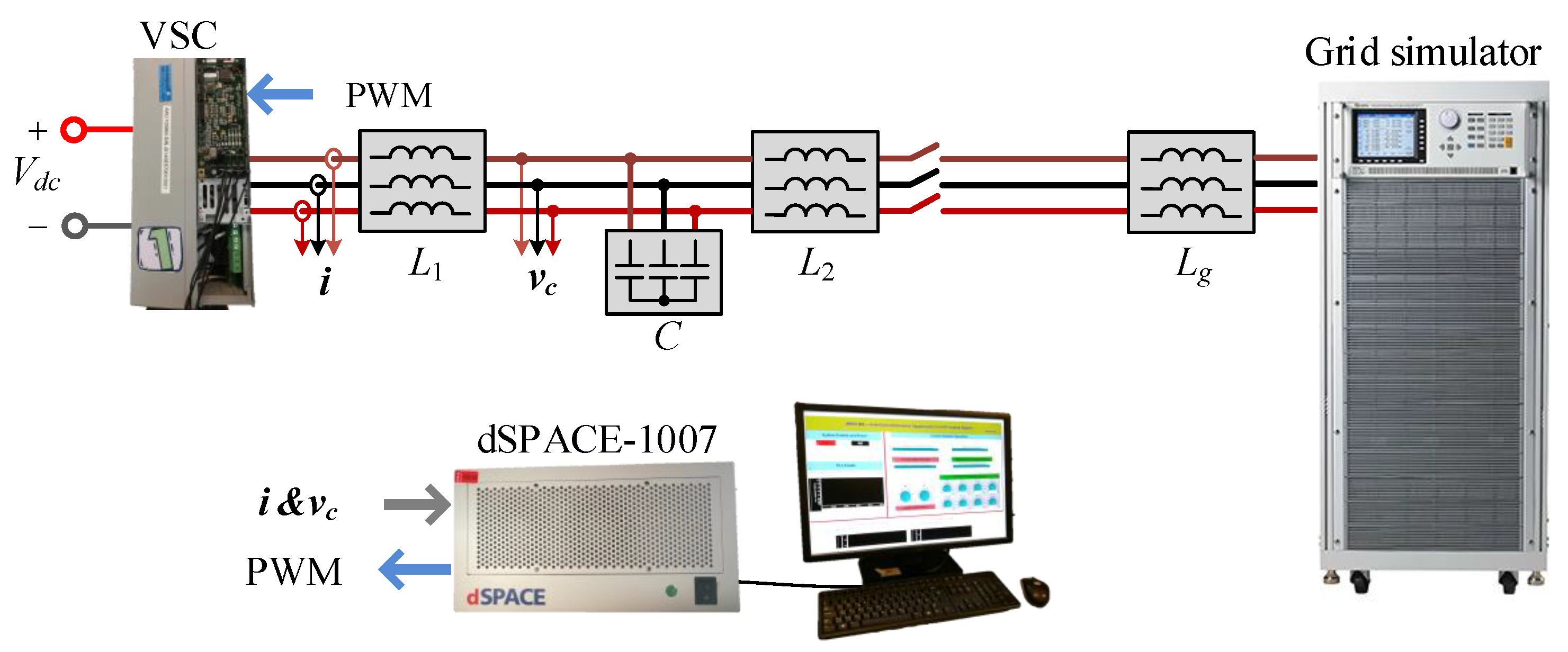

4.3. Experimental Results

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- IEEE Standard. IEEE Guide for Planning DC Links Terminating at AC Locations Having Low Short-Circuit Capacities; IEEE: Piscataway, NJ, USA, 1997. [Google Scholar]

- Durrant, M.; Werner, H.; Abbott, K.; Farag, A.; Durrant, M.; Wemer, H.; Abbottt, K. Model of a VSC HVDC Terminal Attached to a Weak AC System. In Proceedings of the 2003 IEEE Conference on Control Applications, Istanbul, Turkey, 25 June 2003; Volume 1, pp. 173–177. [Google Scholar]

- Kim, B.H.; Sul, S.K. Stability-Oriented Design of Frequency Drift Anti-Islanding and Phase-Locked Loop under Weak Grid. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 5, 760–774. [Google Scholar] [CrossRef]

- Zhou, P.; Yuan, X.; Hu, J.; Huang, Y. Stability of DC-link voltage as affected by phase locked loop in VSC when attached to weak grid. In Proceedings of the IEEE Power and Energy Society General Meeting, National Harbor, MD, USA, 27–31 July 2014; pp. 1–5. [Google Scholar]

- Huang, Y.; Yuan, X.; Hu, J.; Zhou, P.; Wang, D. DC-Bus Voltage Control Stability Affected by AC-Bus Voltage Control in VSCs Connected to Weak AC Grids. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 445–457. [Google Scholar] [CrossRef]

- Lu, S.; Xu, Z.; Xiao, L.; Jiang, W.; Bie, X. Evaluation and Enhancement of Control Strategies for VSC Stations under Weak Grid Strengths. IEEE Trans. Power Syst. 2017, PP, 1. [Google Scholar] [CrossRef]

- Huang, Y.; Wang, D.; Shang, L.; Zhu, G.; Tang, H.; Li, Y. Modeling and Stability Analysis of DC-Link Voltage Control in Multi-VSCs with Integrated to Weak Grid. IEEE Trans. Energy Convers. 2017, 32, 1127–1138. [Google Scholar] [CrossRef]

- Wu, G.; Liang, J.; Zhou, X.; Li, Y.; Egea-Alvarez, A.; Li, G.; Peng, H.; Zhang, X. Analysis and design of vector control for VSC-HVDC connected to weak grids. CSEE J. Power Energy Syst. 2017, 3, 115–124. [Google Scholar] [CrossRef]

- Givaki, K.; Xu, L. Stability analysis of large wind farms connected to weak AC networks incorporating PLL dynamics. In Proceedings of the International Conference on Renewable Power Generation (RPG 2015), Beijing, China, 17–18 October 2015; pp. 1–6. [Google Scholar]

- Fan, L.; Miao, Z. An Explanation of Oscillations Due to Wind Power Plants Weak Grid Interconnection. IEEE Trans. Sustain. Energy 2017, PP, 1–2. [Google Scholar] [CrossRef]

- Sun, Y. The Impact of Voltage-Source-Converters’ Control on the Power System: The Stability Analysis of a Power Electronics Dominant Grid. Ph.D. Thesis, Department of Electrical Engineering, Eindhoven, The Netherlands, 2018. [Google Scholar]

- Bifaretti, S.; Lidozzi, A.; Solero, L.; Crescimbini, F. Anti-islanding detector based on a robust PLL. IEEE Trans. Ind. Appl. 2015, 51, 398–405. [Google Scholar] [CrossRef]

- Freitas, W.; Xu, W.; Affonso, C.M.; Huang, Z. Comparative analysis between ROCOF and vector surge relays for distributed generation applications. IEEE Trans. Power Deliv. 2005, 20, 1315–1324. [Google Scholar] [CrossRef]

- Duckwitz, D.; Fischer, B. Modeling and Design of df/dt-based Inertia Control for Power Converters. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 5, 1553–1564. [Google Scholar] [CrossRef]

- Blaabjerg, F.; Teodorescu, R.; Liserre, M.; Timbus, A.V. Overview of control and grid synchronization for distributed power generation systems. IEEE Trans. Ind. Electron. 2006, 53, 1398–1409. [Google Scholar] [CrossRef]

- Josep, M.; Vasquez, J.C.; Golestan, S.; Member, S.; Guerrero, J.M. Three-Phase PLLs: A Review of Recent Advances. IEEE Trans. Power Electron. 2017, 32, 1894–1907. [Google Scholar]

- Wang, X.; Harnefors, L.; Blaabjerg, F. A Unified Impedance Model of Grid-Connected Voltage-Source Converters. IEEE Trans. Power Electron. 2017, 33, 1775–1787. [Google Scholar] [CrossRef]

- Franklin, G.F.; Powell, J.D.; Emami-Naeini, A. Feedback Control of Dynamic Systems, 6th ed.; Addison-Wesley: Reading, MA, USA, 1994. [Google Scholar]

- Chung, S.K. A phase tracking system for three phase utility interface inverters. IEEE Trans. Power Electron. 2000, 15, 431–438. [Google Scholar] [CrossRef]

- Sun, Y.; DeJong, E.C.W.; Kuijpers, W.G.; Wang, X.; Blaabjerg, F.; Cuk, V.; Cobben, J.F.G. PLL Dynamics in Low Inertia Weak Grid. In Proceedings of the 16th International Workshop on Large-Scale Integration of Wind Power into Power System as well as on Transmission Networks for Offshore Wind Power Plants (WIW 17), Berlin, Germany, 25–27 October 2017; p. 369. [Google Scholar]

- Sun, Y.; De Jong, E.; Cuk, V.; Cobben, S. 6MW solar plant integration feasibility study: Bonaire island case study. In Proceedings of the 2016 IEEE 17th Workshop on Control and Modeling for Power Electronics, COMPEL 2016, Trondheim, Norway, 27–30 June 2016. [Google Scholar]

- Alepuz, S.; Busquets-Monge, S.; Bordonau, J.; Martinez-Velasco, J.A.; Silva, C.A.; Pontt, J.; Rodriguez, J. Control strategies based on symmetrical components for grid-connected converters under voltage dips. IEEE Trans. Ind. Electron. 2009, 56, 2162–2173. [Google Scholar] [CrossRef]

- Ma, K.; Liserre, M.; Blaabjerg, F. Operating and loading conditions of a three-level neutral-point-clamped wind power converter under various grid faults. IEEE Trans. Ind. Appl. 2014, 50, 520–529. [Google Scholar]

| 8.4 | 100 | |

| 84 | 10,000 |

| Parameter | Value | Unit |

|---|---|---|

| Rated Power | 850 | kW |

| DC Link Voltage | 800 | Volts |

| DC Link Capacitor | 20 | mF |

| AC Voltage | 400 | Volts |

| Inverter Side Inductor | 80 | H |

| Resistance of | 0.001 | Ohm |

| Grid Side Inductor | 80 | H |

| Resistance of | 0.001 | Ohm |

| Filter Capacitor | 425 | F |

| ESR of | 0.01 | Ohm |

| Sampling Time | 100 | s |

| Switching Frequency | 5000 | Hz |

| PR Proportional Gain | 1 | p.u. |

| PR Integral Gain | 250 | p.u. |

| PR Bandwidth | 2 | p.u. |

| DC Proportional Gain | 1 | p.u. |

| DC Integral Gain | 100 | p.u. |

| Q Proportional Gain | 1 | p.u. |

| Q Integral Gain | 100 | p.u. |

| Parameter | Value | Unit |

|---|---|---|

| Rated Power | 2 | kW |

| Grid fundamental frequency | 50 | Hz |

| DC Link Voltage | 730 | Volts |

| DC Link Capacitor | 1500 | F |

| AC Voltage | 400 | Volts |

| Inverter side inductor | 1500 | H |

| Equivalent grid-side inductor () | 1500 | H |

| Filter capacitor | 5 | F |

| Inverter control sampling frequency | 10 | kHz |

| Inverter switching frequency | 10 | kHz |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Sun, Y.; de Jong, E.C.W.; Wang, X.; Yang, D.; Blaabjerg, F.; Cuk, V.; Cobben, J.F.G. The Impact of PLL Dynamics on the Low Inertia Power Grid: A Case Study of Bonaire Island Power System. Energies 2019, 12, 1259. https://doi.org/10.3390/en12071259

Sun Y, de Jong ECW, Wang X, Yang D, Blaabjerg F, Cuk V, Cobben JFG. The Impact of PLL Dynamics on the Low Inertia Power Grid: A Case Study of Bonaire Island Power System. Energies. 2019; 12(7):1259. https://doi.org/10.3390/en12071259

Chicago/Turabian StyleSun, Yin, E. C. W. (Erik) de Jong, Xiongfei Wang, Dongsheng Yang, Frede Blaabjerg, Vladimir Cuk, and J. F. G. (Sjef) Cobben. 2019. "The Impact of PLL Dynamics on the Low Inertia Power Grid: A Case Study of Bonaire Island Power System" Energies 12, no. 7: 1259. https://doi.org/10.3390/en12071259

APA StyleSun, Y., de Jong, E. C. W., Wang, X., Yang, D., Blaabjerg, F., Cuk, V., & Cobben, J. F. G. (2019). The Impact of PLL Dynamics on the Low Inertia Power Grid: A Case Study of Bonaire Island Power System. Energies, 12(7), 1259. https://doi.org/10.3390/en12071259