Modelling of Dynamic Properties of Silicon Carbide Junction Field-Effect Transistors (JFETs)

Abstract

1. Introduction

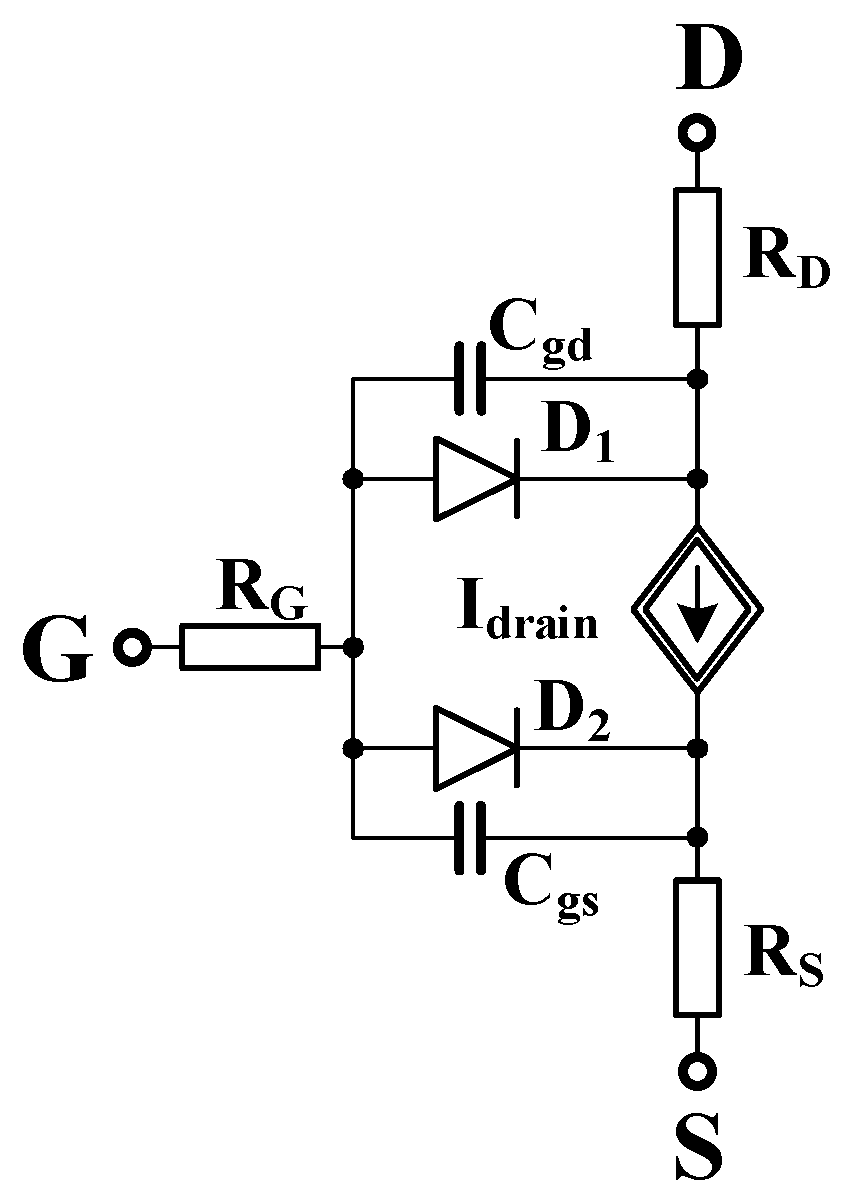

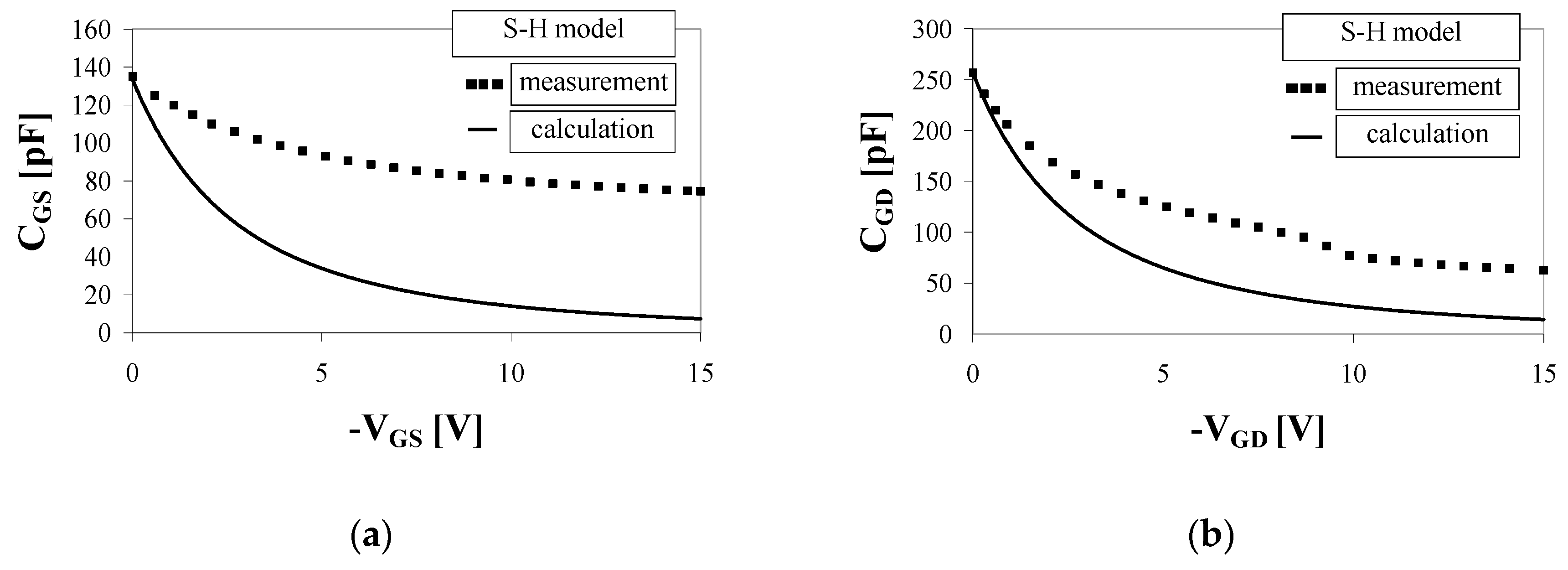

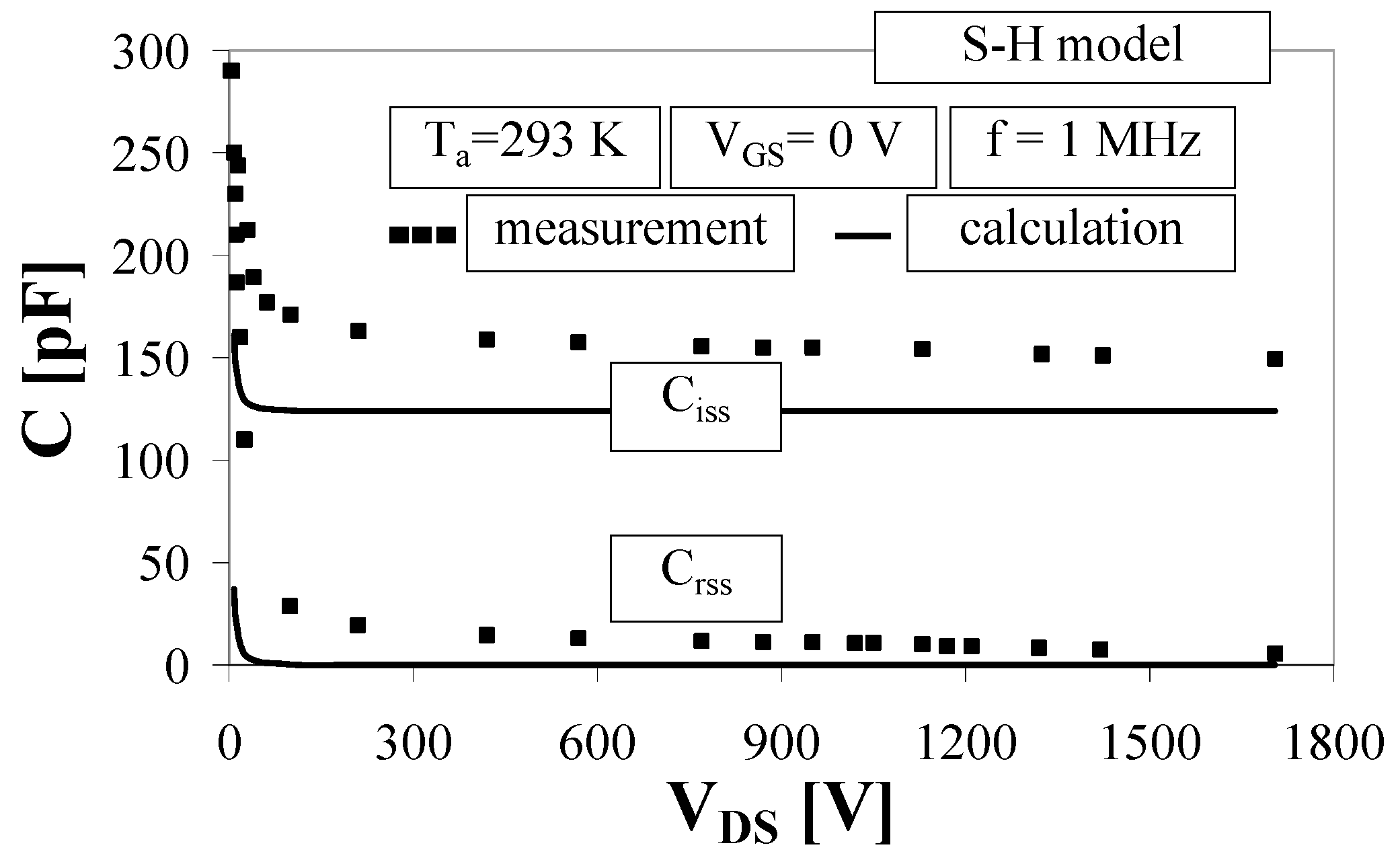

2. The Shichman–Hodges Model Form

- in the cut-off region (for VGS−VTO(T) < 0):

- in the linear region (for VDS ≤ VGS−VTO(T)):

- in the saturation region (for 0 < VGS−VTO(T) < VDS):where: VGS—gate-source voltage, VDS—drain-source voltage, LAMBDA—channel-length modulation coefficient, BETA(T)—temperature dependence of transconductance coefficient, VTO(T)—temperature dependence of the threshold voltage.

- for Vgs ≤ FC·PB

- for Vgs > FC·PB

- for Vgd ≤ FC·PB

- for Vgd > FC·PBwhere: FC—forward-bias depletion capacitance coefficient, PB—gate p–n potential, CGS, CGD—zero-bias gate–source and gate–drain junction capacitances, M—gate p–n grading coefficient.

3. Results of Simulations of the Shichman–Hodges Model

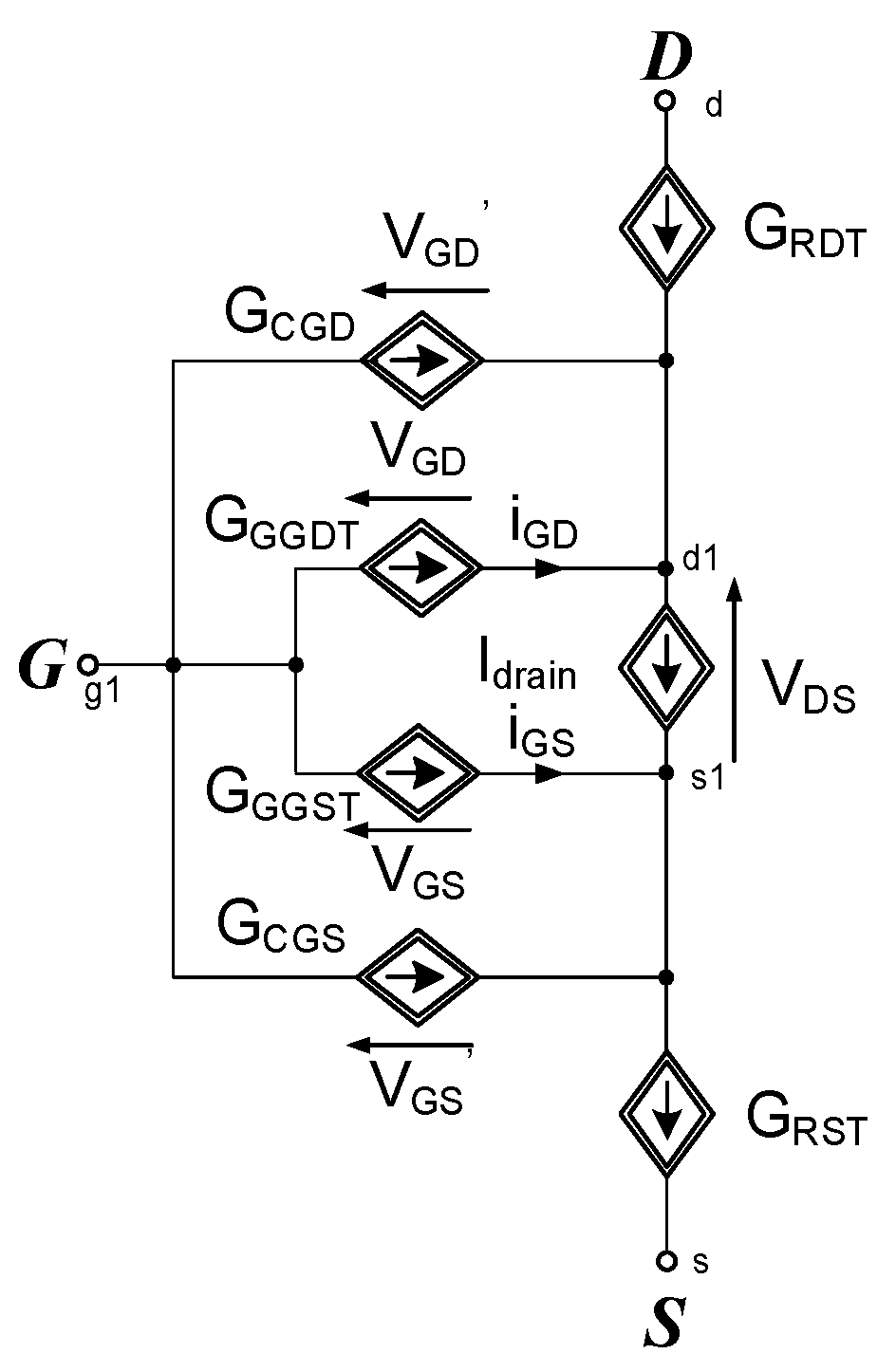

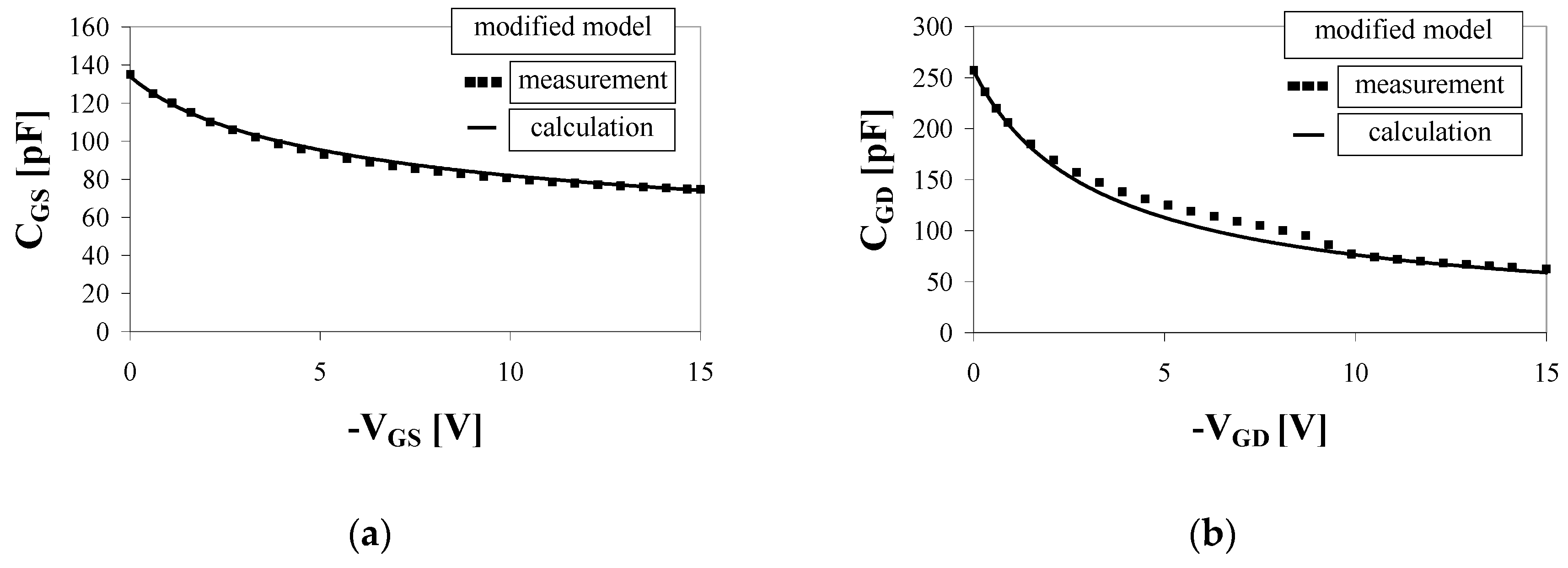

4. Modifications of the Shichman–Hodges Model

- for VGS ≤ FC1·PBCGS

- for VGS > FC1·PBCGS

- for VGD ≤ FC2·PBCGD

- for Vgd > FC2·PBCGDwhere: FC1, PBCGS, MGS, FC2, PBCGD, MGD represent a new set of model parameters.

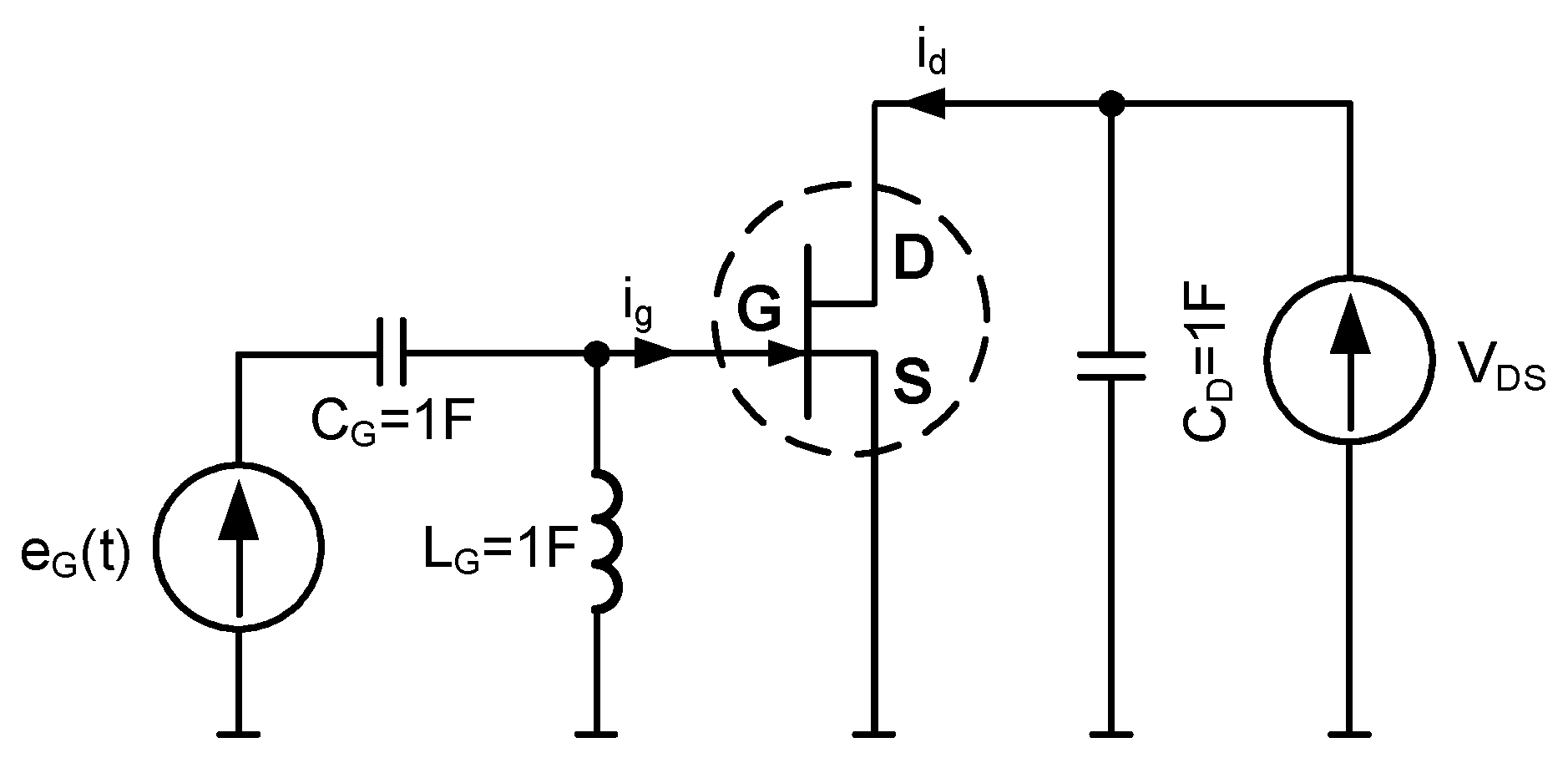

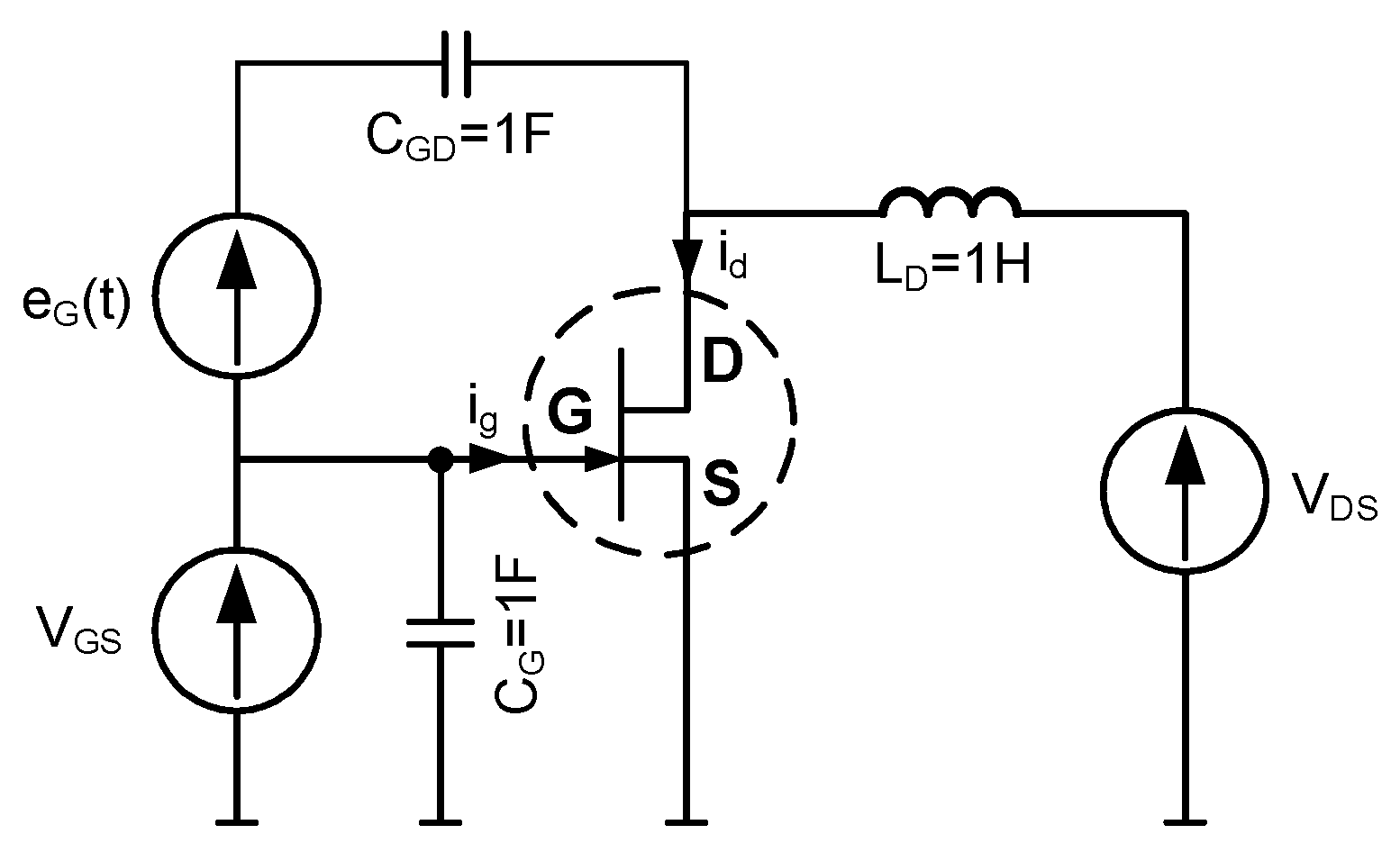

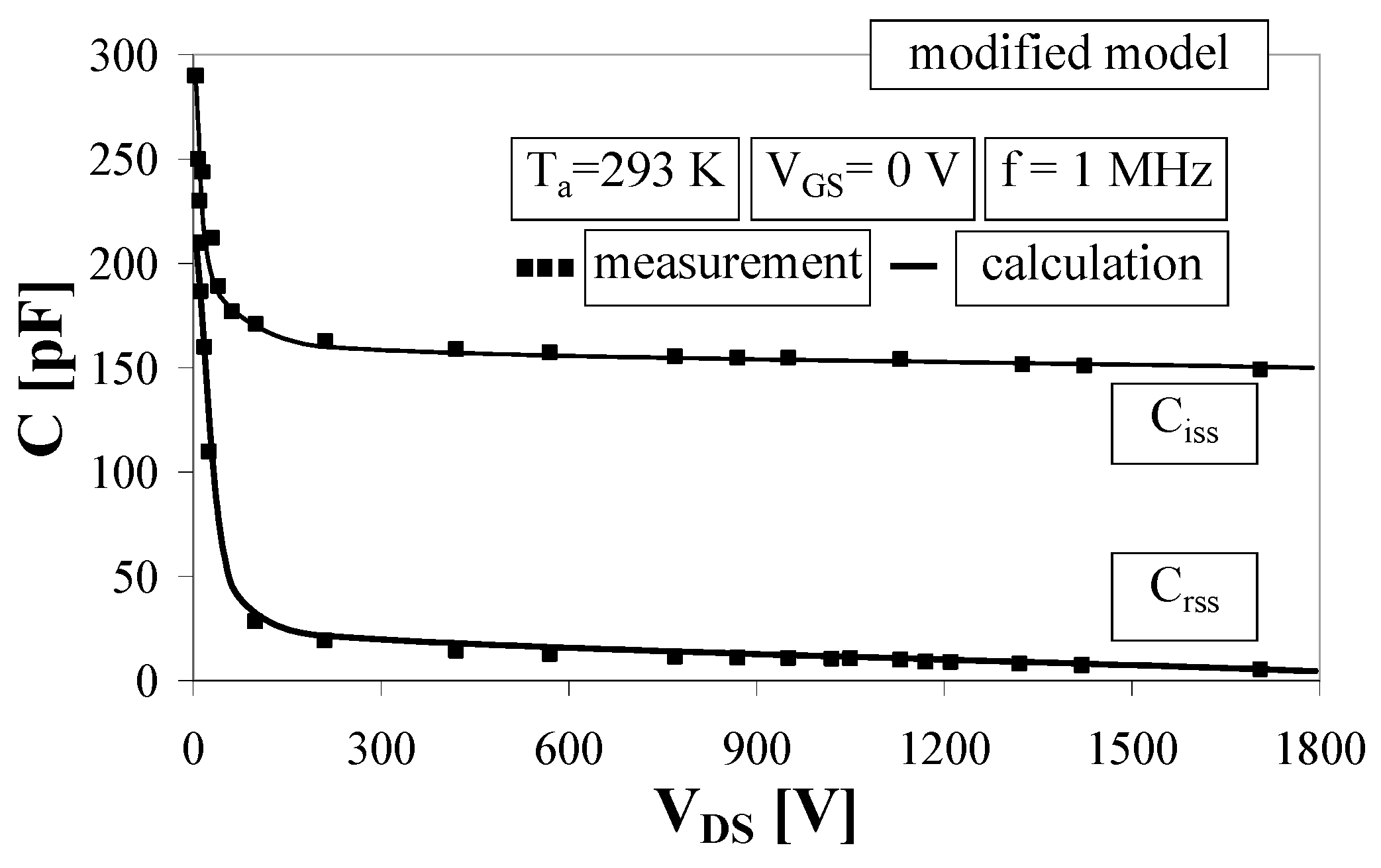

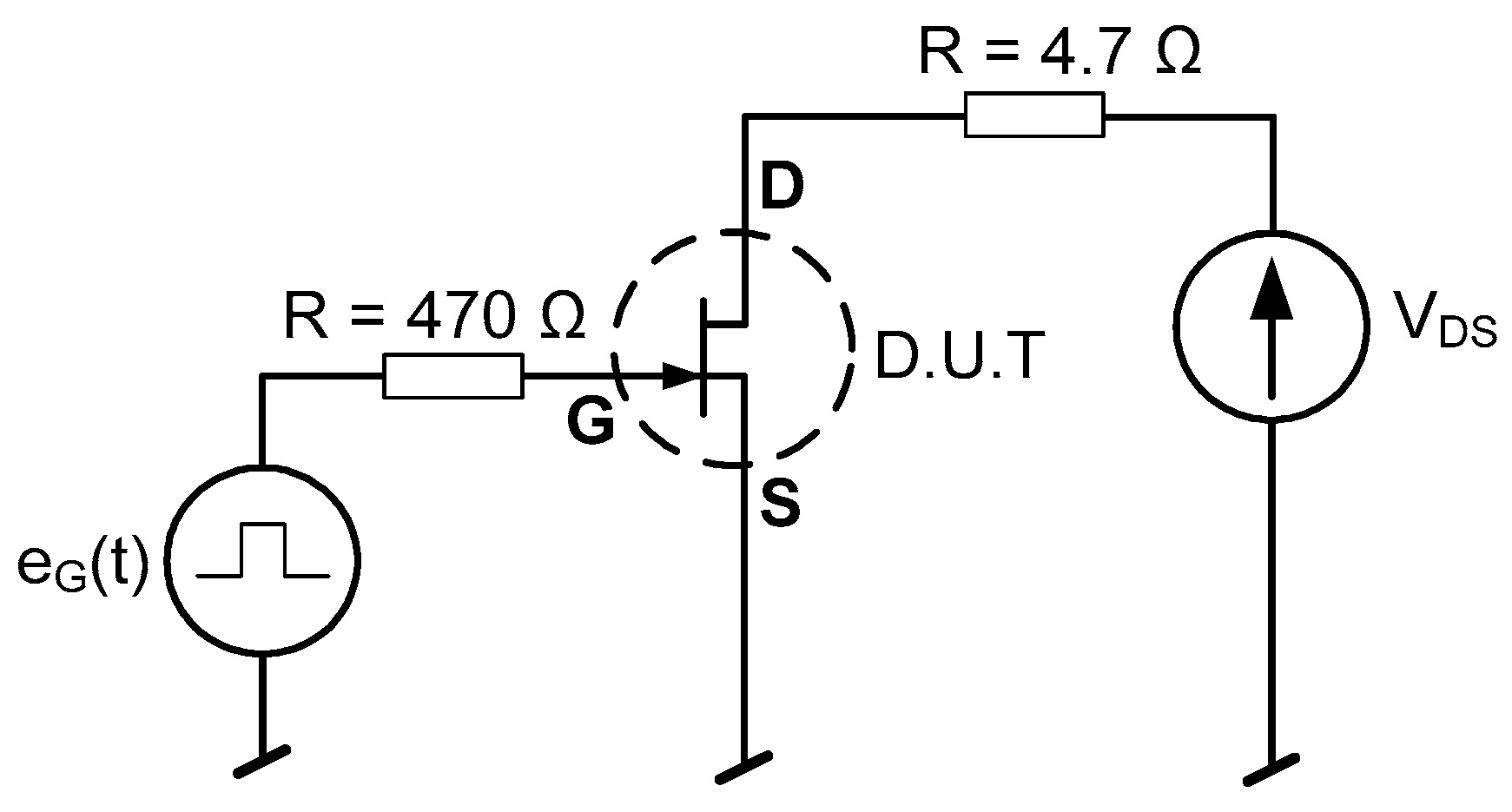

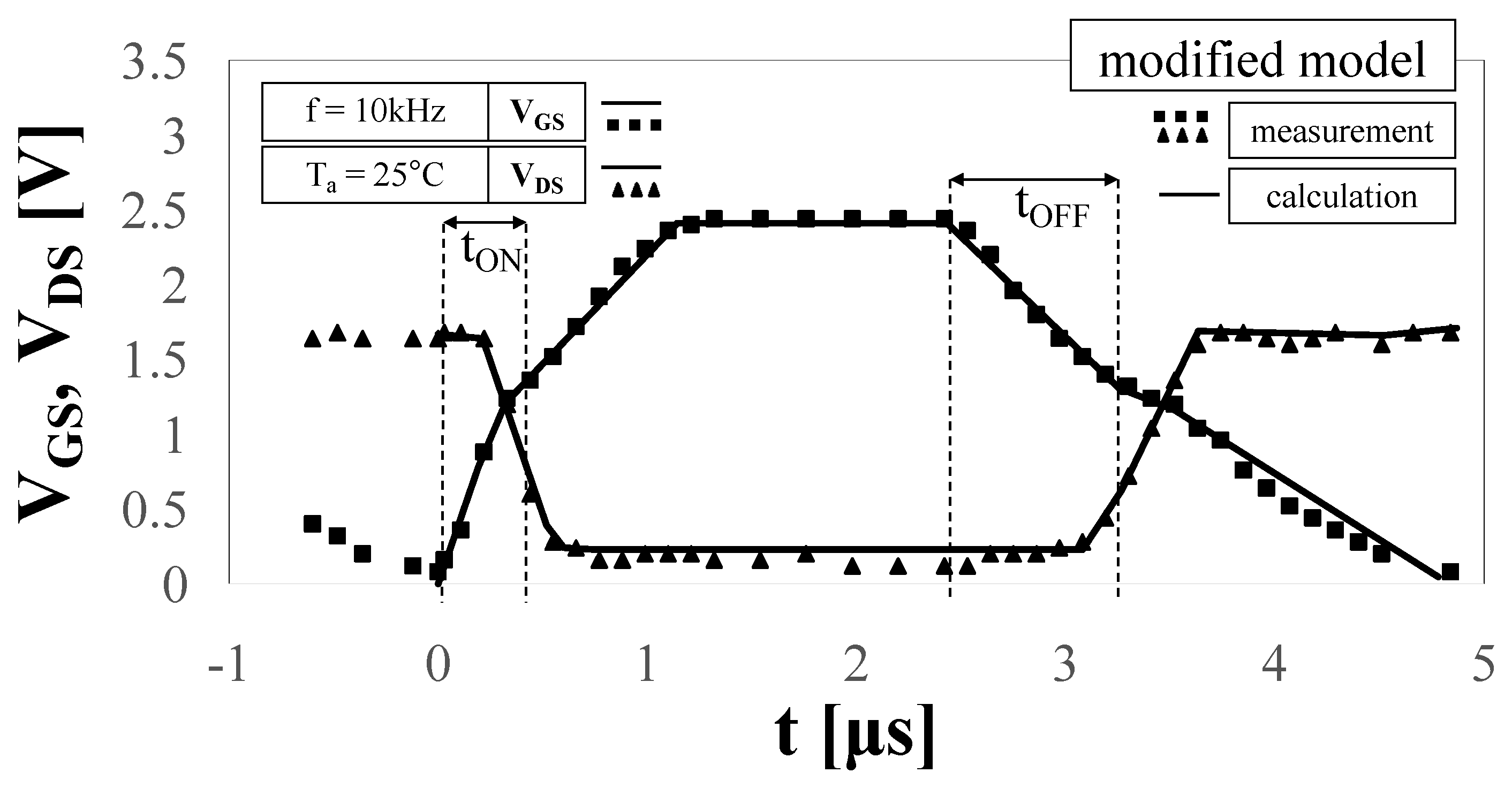

5. Simulation Results of Dynamic Characteristics of JFET

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Salah, T.B.; Khachroumi, S.; Morel, H. Characterization, Modeling and Design Parameters Identification of Silicon Carbide Junction Field Effect Transistor for Temperature Sensor Applications. Sensors 2010, 10, 388–399. [Google Scholar] [CrossRef] [PubMed]

- Wang, L.; Yang, J.; Ma, H.; Wang, Z.; Olanrewaju, K.O.; Kerrouche, K.D.E. Analysis and Suppression of Unwanted Turn-On and Parasitic Oscillation in SiC JFET-Based Bi-Directional Switches. Electronics 2018, 7, 126. [Google Scholar] [CrossRef]

- Fernández-Martínez, P.; Flores, D.; Hidalgo, S.; Jordà, X.; Perpiñà, X.; Quirion, D.; Ré, L.; Ullán, M.; Vellvehí, M. A New Vertical JFET Power Device for Harsh Radiation Environments. Energies 2017, 10, 256. [Google Scholar] [CrossRef]

- Yang, J. A Silicon Carbide Wireless Temperature Sensing System for High Temperature Applications. Sensors 2013, 13, 1884–1901. [Google Scholar] [CrossRef] [PubMed]

- She, X.; Huang, A.Q.; Lucía, Ó. Review of Silicon Carbide Power Devices and Their Applications. IEEE Trans. Ind. Electron. 2017, 64, 8193–8205. [Google Scholar] [CrossRef]

- Chinthavali, M.; Ning, P.; Cui, Y.; Tolbert, L.M. Investigation on the Parallel Operation of Discrete SiC BJTs and JFETs. In Proceedings of the 2011 26th Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Fort Worth, TX, USA, 6–11 March 2011. [Google Scholar] [CrossRef]

- Grekov, A.; Chen, Z.; Santi, E.; Hudgins, J.; Mantooth, A.; Sheridan, D.; Casady, J. Parameter Extraction Procedure for High Power SiC JFET. In Proceedings of the 2019 IEEE Energy Conversion Congress and Exposition, San Jose, CA, USA, 20–24 September 2009. [Google Scholar] [CrossRef]

- Funaki, T.; Kimoto, T.; Hikihara, T. Evaluation of capacitance-voltage characteristics for high voltage SiC-JFET. IEICE Electron. Express 2007, 4, 517–523. [Google Scholar] [CrossRef]

- Ding, H.; Liou, J.J.; Cirba, C.R.; Green, K. An improved junction capacintance model for junction field-effect transistors. Solid State Electron. 2006, 50, 1395–1399. [Google Scholar] [CrossRef]

- Bargieł, K.; Bisewski, D. Evaluation of Accuracy of SiC-JFET Macromodel. Computer Applications in Electrical Engineering. In Proceedings of the ITM Web Conference, Poznań, Poland, 23–24 April 2018; EDP Sciences: Julis, France, 2018; Volume 19, p. 01027. [Google Scholar] [CrossRef][Green Version]

- Wang, L.; Yang, J.; Ma, H.; Wang, Z.; Olanrewaju, K.O.; Wheeler, P. Analysis and Modeling of SiC JFET Bi-Directional Switches Parasitic Oscillation. IEEE Trans. Power Electron. 2018, 34, 8613–8625. [Google Scholar] [CrossRef]

- PSPICE A/D Reference Guide, version 10.0; Cadence Design Systems Inc.: San Jose, CA, USA, June 2003.

- Kong, M.; Hou, Y.; Yi, B.; Chen, X. A High Speed High Voltage Normally-off SiC Vertical JFET Power Device. In Proceedings of the 2019 IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), Xi’an, China, 12–14 June 2019. [Google Scholar] [CrossRef]

- Hsu, F.-J.; Yen, C.-T.; Hung, C.-C.; Lee, C.-Y.; Lee, L.-S.; Chu, K.-T.; Li, Y.-F. High Accuracy Large-Signal SPICE Model for Silicon Carbide MOSFET. In Proceedings of the 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, USA, 13–17 May 2018. [Google Scholar] [CrossRef]

- Wang, J.; Liang, S.; Deng, L.; Yin, X.; Shen, Z.J. An Improved SPICE Model of SiC BJT Incorporating Surface Recombination Effect. IEEE Trans. Power Electron. 2019, 34, 6794–6802. [Google Scholar] [CrossRef]

- Zarębski, J.; Górecki, K. Nonlinear Compact Thermal Model of Power Semicondactor Devices. IEEE Trans. Compon. Pack. Technol. 2010, 33, 643–647. [Google Scholar] [CrossRef]

- Szelągowska, J.; Zarębski, J. Measurement and Calculations of Capacitances of BJT and SJT Made of Silicon Carbide. Computer Applications in Electrical Engineering. In Proceedings of the ITM Web Conference, Poznań, Poland, 23–24 April 2018; EDP Sciences: Julis, France, 2018; Volume 19, p. 01026. [Google Scholar] [CrossRef][Green Version]

- Górecki, K.; Górecki, P. Modelling a Switching Process of IGBTs with Influence of Temperature Taken into Account. Energies 2019, 12, 1894. [Google Scholar] [CrossRef]

- Bargieł, K.; Bisewski, D. DC characteristics of power SiC-JFET. Prz. Elektrotechniczny 2018, 94, 63–66. [Google Scholar] [CrossRef]

- Bargieł, K.; Zarębski, J.; Bisewski, D. SPICE-Aided Modeling of High-Voltage Silicon Carbide JFETs. In Proceedings of the 39th International Microelectronics and Packaging Poland Conference (IMAPS), Gdansk, Poland, 20–23 September 2015; IOP Conference Series-Materials Science and Engineering. Curran Associates, Inc.: Red Hook, NY, USA, 2016; Volume 104. [Google Scholar] [CrossRef]

- Alonso, A.R.; Diaz, M.F.; Lamar, D.G.; Perez de Azpeitia, M.A.; Hernando, M.M.; Sebastian, J. Switching performance comparison of the SiC JFET and SiC JFET/Si MOSFET cascode configuration. IEEE Trans. Power Electron. 2014, 29, 2428–2440. [Google Scholar] [CrossRef]

- Rondon-Pinilla, E.; Morel, F.; Vollaire, C.; Schanen, J.-L. Modeling of buck converter with a SiC JFET to predict EMC conducted emissions. IEEE Trans. Power Electron. 2014, 29, 2246–2260. [Google Scholar] [CrossRef]

- Li-Gang, R.; Ping, Z.; Li, W. Data Driven Modeling and Verification for Silicon Carbide JFET with Thermal Effects. In Proceedings of the 2014 IEEE Applied Power Electronics Conference and Exposition—APEC, Fort Worth, TX, USA, 16–20 March 2014; pp. 2649–2653. [Google Scholar] [CrossRef]

- Cai, C.; Qu, Y.; Guo, Q.; Tao, W.; Sheng, K. Parameters Evaluation for SiC-JFET Modeling Considering Non-Uniformity by Fabrication. In Proceedings of the 2012 IEEE International Symposium on Industrial Electronics, Hangzhou, China, 28–31 May 2012; pp. 437–441. [Google Scholar] [CrossRef]

- Available online: http://www.farnell.com/datasheets/1696883.pdf (accessed on 22 December 2019).

- Bisewski, D. Parameters Estimation of SPICE Models for Silicon Carbide Devices. In Proceedings of the 2017 IEEE 21st European Microelectronics and Packaging Conference (EMPC) & Exhibition, Warsaw, Poland, 10–13 September 2017. [Google Scholar] [CrossRef]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bargieł, K.; Bisewski, D.; Zarębski, J. Modelling of Dynamic Properties of Silicon Carbide Junction Field-Effect Transistors (JFETs). Energies 2020, 13, 187. https://doi.org/10.3390/en13010187

Bargieł K, Bisewski D, Zarębski J. Modelling of Dynamic Properties of Silicon Carbide Junction Field-Effect Transistors (JFETs). Energies. 2020; 13(1):187. https://doi.org/10.3390/en13010187

Chicago/Turabian StyleBargieł, Kamil, Damian Bisewski, and Janusz Zarębski. 2020. "Modelling of Dynamic Properties of Silicon Carbide Junction Field-Effect Transistors (JFETs)" Energies 13, no. 1: 187. https://doi.org/10.3390/en13010187

APA StyleBargieł, K., Bisewski, D., & Zarębski, J. (2020). Modelling of Dynamic Properties of Silicon Carbide Junction Field-Effect Transistors (JFETs). Energies, 13(1), 187. https://doi.org/10.3390/en13010187