Quasi-3D Thermal Simulation of Integrated Circuit Systems in Packages

Abstract

:1. Introduction

2. State of the Art

2.1. BGA Packages

2.2. 3D-IC-TSV Packages

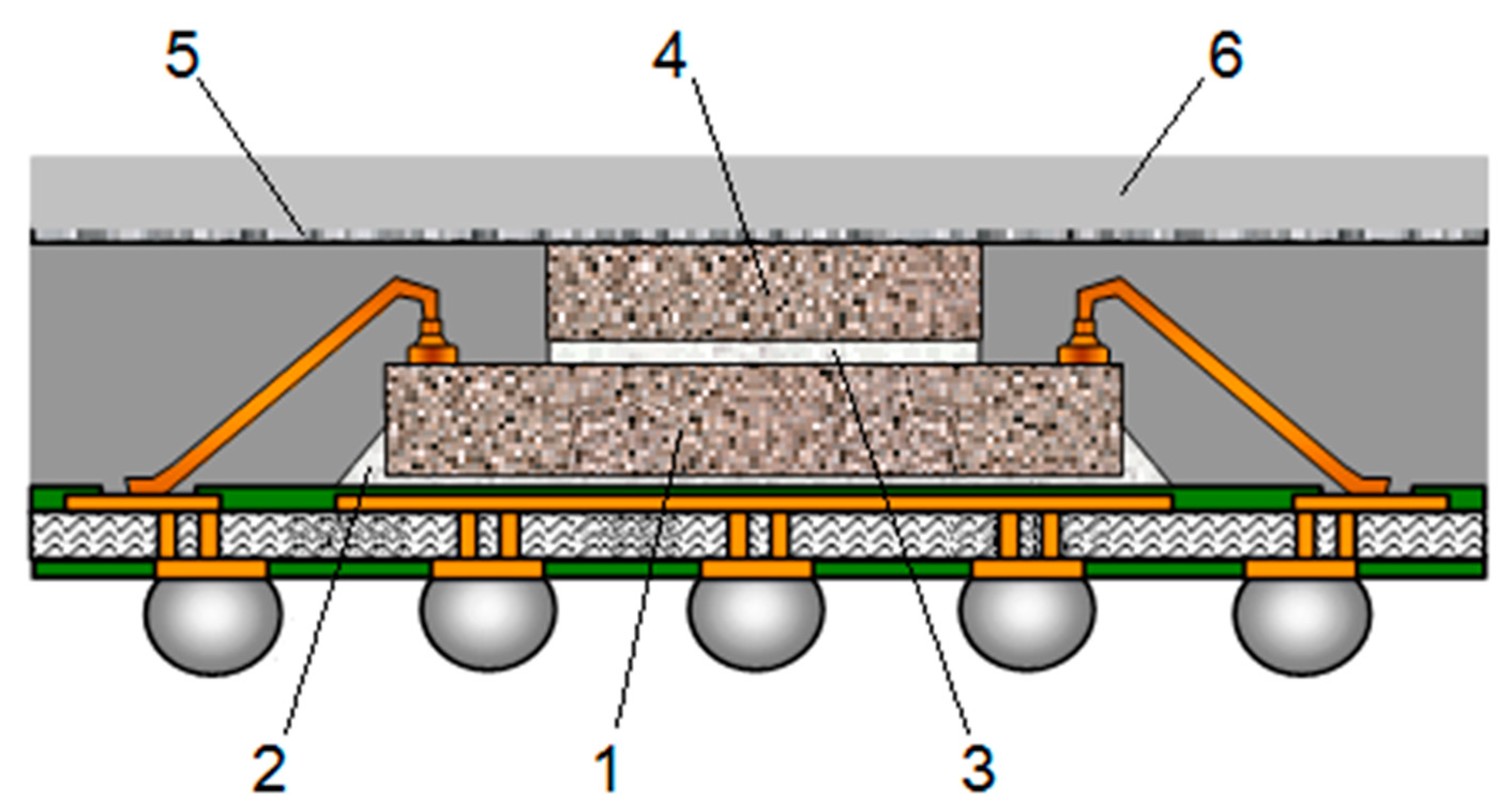

2.3. Embedded Die Packages

3. Quasi-3D Numerical Model of IC Packages

- convective heat transfer occurs on the top surface of the package

- for inner layerswhere Tξ(x,y) is the layer temperature; TAMB is the ambient temperature; P is the power density on die surface; α is the convective heat transfer coefficient; λξ and zξ are the thermal conductivity coefficient and thickness of the package structural layer ξ = 1,2, …, N; N is the quantity of package layers XS YS package horizontal sizes.

- Package structural parameters, i.e., the number of layers, type of layer, sizes, and physical parameters of the layer;

- The powers or power densities of the active dies;

- Computational parameters, i.e., difference network sizes MX × MY and accuracy of computations.

- Temperature arrays in network nodes for each layer Tξ(i,j), ξ = 1,2, …, N;

- The temperature distribution plots Tξ(i,j) in the x,y plane;

- Average TAV and maximal TMAX values of layer temperatures.

4. Simulation Results

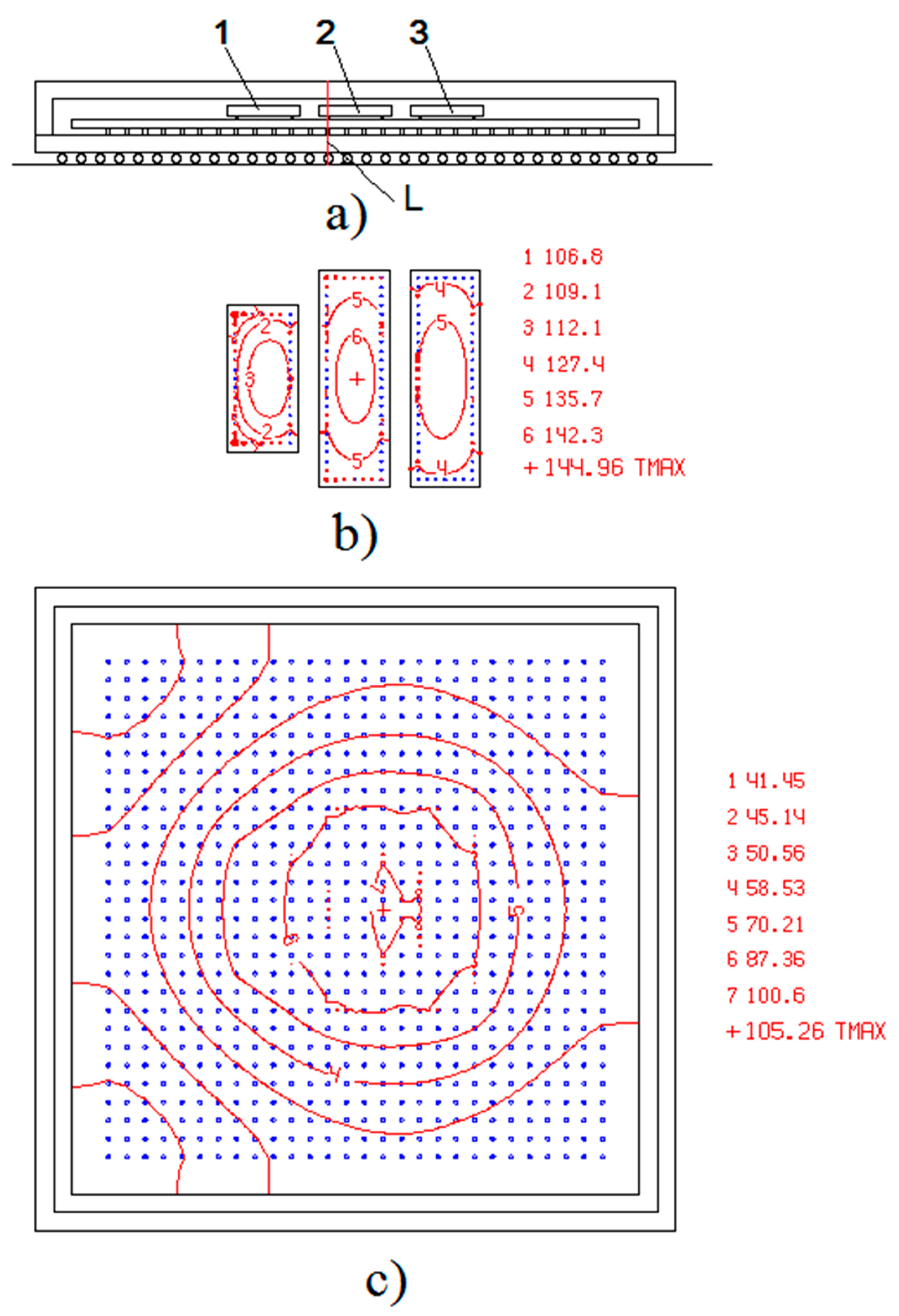

4.1. Stacked IC-TSV-BGA Module

4.2. Multi-Chip Stack Embedding Package

5. Validation of the Q3D Model

5.1. Comparison with Results Obtained Using Standard Fully-3D FEM Simulators

5.2. Comparison with Measured Thermal Resistances for Different Types of Packages

5.2.1. The Standard BGA Package

5.2.2. UltraScale FPBGA Package

5.3. High-Performance Flip-Chip BGA (HP-fcBGA)

6. Conclusions

- (a)

- 3D integration of ICs and board;

- (b)

- Large number of thinned layers of different materials;

- (c)

- Vertical z-axes interconnections.

Author Contributions

Funding

Conflicts of Interest

References

- Krishnamoorthi, S.; Chong, D.Y.R.; Anthony, Y.S. Thermal Management and Characterization of Flip Chip BGA Packages. In Proceedings of the 6th Electronics Packaging Technology Conference (EPTC 2004), Singapore, 8–10 December 2004; Institute of Electrical and Electronics Engineers (IEEE): Piscataway, NJ, USA, 2005; pp. 53–59. [Google Scholar]

- Smith, L. Package on Package (PoP). Applications, Requirements, Infrastructure and Technologies. SMTA OR Charter. March 2011. Available online: https://www.smta.org/chapters/files/Oregon_SMTA_OR_March_16_LSMIT.pdf (accessed on 30 March 2020).

- Madden, L.; Ramalingam, S.; Wu, X.; Wu, E.; Banijamanali, B.; Kim, N.; Abugharbieh, K. Xilinx Stacked Silicon Interconnect Technology Delivers Breakthrough FPGA Performance. Adv. Microelectron. 2013, 40, 6–11. [Google Scholar]

- Garrou, P. 2.5 and 3D IC–The Ultimate Evolution of Chip Packaging. Adv. Microelectron. 2013, 40, 5. [Google Scholar]

- Ostmann, A.; Manessis, D.; Stahr, J.; Beesley, M.; Cauwe, M.; De Baets, J. Industrial and technical aspects of chip embedding technology. In Proceedings of the 2008 2nd Electronics System-Integration Technology Conference, London, UK, 1–4 September 2008; Institute of Electrical and Electronics Engineers (IEEE): Piscataway, NJ, USA, 2008; pp. 315–320. [Google Scholar]

- Ma, Y.Y.; Chong, D.Y.R.; Wang, C.K.; Anthony, Y.S. Development of Ball Grid Array Packages with Improved Thermal Performance Sun. Available online: http://www.utacgroup.com/library/EPTC2005_F2.5_P0149_Thermal_XP-BGA.pdf (accessed on 26 April 2020).

- Amkor Technology. Technology Solutions Package-on-Package (PoP). 2019. Available online: https://c44f5d406df450f4a66b-1b94a87d576253d9446df0a9ca62e142.ssl.cf2.rackcdn.com/2018/02/PoP_DS586.pdf (accessed on 26 April 2020).

- Johansson, S.; Dzarnosski, J.; Itoi, K. Miniaturization of heating aid electronics using embedded die pack-aging. In Proceedings of the SMTA Intern, Rosemont, IL, USA, 25 September 2016; pp. 9–15. [Google Scholar]

- FloTHERM. Mentor Graphics (Deutschland) GmbH. Arnulfstr. 201 80634 München Germany. Available online: https://www.mentor.com/products/mechanical/flotherm/flotherm/ (accessed on 17 May 2020).

- Petrosyants, K.; Rjabov, N. Quasi–3D Approach for BGA Package Thermal Modeling. In Proceedings of the 18th International Workshop on Thermal Investigations of ICs and Systems (THERMINIC 2012), Budapest, Hungary, 25–27 September 2012; pp. 158–161. [Google Scholar]

- Day, R.; Tota, P. Thermal Analysis of a Small Outline Package Mounted on a PCB Using Computational Fluid Dynamics. Eng. Edge 2016, 5, 27–31. [Google Scholar]

- 3D ICs with TSVs–Design Challenges and Requirements. 2011 Cadence Design Systems, Inc. Available online: https://resources.pcb.cadence.com/sigrity-whitepapers/3d-ics-with-tsvs-design-challenges-and-requirements (accessed on 4 May 2020).

- Chien, H.-C.; Lau, J.H.; Chao, Y.-L.; Tain, R.-M.; Dai, M.-J.; Wu, S.-T.; Lo, W.-C.; Kao, M.-J. Thermal Performance of 3D IC Integration with Through-Silicon Via (TSV). J. Microelectron. Electron. Packag. 2012, 9, 97–103. [Google Scholar] [CrossRef]

- Swarup, S.; Tan, S.X.-D.; Liu, Z.; Swarup, S. Thermal characterization of TSV based 3D stacked ICs. In Proceedings of the 2012 IEEE 21st Conference on Electrical Performance of Electronic Packaging and Systems, Tempe, Arizona, USA, 21–24 October 2012; Institute of Electrical and Electronics Engineers (IEEE): Piscataway, NJ, USA, 2012; pp. 335–338. [Google Scholar]

- Vaddina, K.R.; Rahmani, A.-M.; Latif, K.; Liljeberg, P.; Plosila, J. Thermal modeling and analysis of advanced 3D stacked structures. Procedia Eng. 2012, 30, 248–257. [Google Scholar] [CrossRef] [Green Version]

- Petrosyants, K.O.; Ryabov, N.I. Quasi-3D Thermal Model of Stacked IC-TSV-BGA Package. In Proceedings of the 2019 25th International Workshop on Thermal Investigations of ICs and Systems (THERMINIC), Lecco, Italy, 25–27 September 2019; Institute of Electrical and Electronics Engineers (IEEE): Piscataway, NJ, USA, 2019; pp. 1–4. [Google Scholar]

- Im, S.; Banerjee, K. Full chip thermal analysis of planar (2-D) and vertically integrated (3-D) high performance ICs. In Proceedings of the International Electron Devices Meeting 2000. Technical Digest. IEDM (Cat. No.00CH37138), San Francisco, CA, USA, 10–13 December 2000; pp. 727–730. [Google Scholar] [CrossRef]

- Savidis, I. Characterization and Modeling of TSV Based 3-D Integrated Circuits. Ph.D. Thesis, University of Rochester, New York, NY, USA, 2013; p. 443. [Google Scholar]

- Oh, D.; Chen, C.C.P.; Hu, Y.H. Efficient Thermal Simulation for 3-D IC with Thermal through-Silicon Vias. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2012, 31, 1767–1771. [Google Scholar]

- Jain, A.; Jones, R.; Chatterjee, R.; Pozder, S. Analytical and Numerical Modeling of the Thermal Performance of Three-Dimensional Integrated Circuits. IEEE Trans. Compon. Packag. Technol. 2009, 33, 56–63. [Google Scholar] [CrossRef]

- Souare, P.M.; Coudrain, P.; Colonna, J.; Fiori, V.; Farcy, A.; De Crécy, F.; Borbély, A.; Ben-Jamaa, H.; Laviron, C.; Gallois-Garreignot, S.; et al. A comprehensive platform for thermal studies in TSV-based 3D integrated circuits. In Proceedings of the 2014 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2014; pp. 35.4.1–35.4.4. [Google Scholar] [CrossRef]

- Stahr, J.; Morianz, M.; Brizoux, M.; Grivon, A.; Maia, W. Simulation of Embedded Components in PCB Environment and Verification of Board Reliability. Available online: https://silo.tips/download/simulation-of-embedded-components-in-pcb-environment-and-verification-of-board-r (accessed on 26 April 2020).

- Battoy, C.; Martin, C.; Morel, F.; Caillaud, R.; Leslé, J.L.; Mrad, R.; Degrenne, N.; Mollov, S. Application of the PCB Embedding Technology in Power Electronics–State of the Art and Proposed Development. In Proceedings of the Second International Symposium on 3D Power Electronics Integration and Manufacturing (3D PIEM), College Park, MD, USA, 25–27 June 2018; pp. 1–12. [Google Scholar]

- ANSYS Chip-Package-System (CPS) Co-Design and Thermal Management of Electronics 2012. Available online: https://www.ansyscom/Ansys/corporate/resourcelibrary/precentation/chip-package-system-design1012-pres.pdf. (accessed on 10 March 2020).

- Patran Complete FEA Modeling Solution. Available online: https://www.mscsoftware.com/product/patran (accessed on 26 March 2020).

- Elkady, Y.A. Thermal Performance of Ball Grid Arrays and Thin Interface Materials. Ph.D. Thesis, Auburn University, Auburn, AL, USA, 8 August 2005; p. 176. [Google Scholar]

- Tatsuya Ito. Multi-Chip Embedded Circuit Board, “WABE”. SemiCon Taiwan 2016 07.09.2016–09.09.2016. Taipei Nangang Exhibition Center: Taipei, Taiwan. Available online: http://www.semicontaiwan.org/en/ (accessed on 20 March 2020).

- COMSOL. COMSOL, Inc. 100 District Avenue Burlington, MA 01803 USA. Available online: https://www.comsol.com (accessed on 17 May 2020).

- Mechanical and Thermal Design. Guidelines for Lidless Flip-Chip Packages. Application Note. XAPP1301 (v.1.4). 29 April 2019. Available online: https://www.xilinx.com/support/documentation/application_notes/xapp1301-mechanical-thermal-design-guidelines.pdf (accessed on 26 March 2020).

| Material | Constructive Element | Thermal Conductivity, K/W |

|---|---|---|

| Silicon | die, interposer | 150 |

| Solder | balls | 50 |

| Ceramic | substrate | 0.377 |

| Polyimide | constructive layers | 100 |

| Copper | via | 385 |

| Molding | constructive layers | 0.6 |

| Covar | lid | 17 |

| Temperature, °C | COMSOL [14] | Overheat-3D-IC (This Work) | Difference | |

|---|---|---|---|---|

| In °C | In % | |||

| TMAX for bottom layer in Figure 8a | 82 | 78.2 | 3.8 | 4.4 |

| TMAX for upper layer in Figure 8a | 76 | 73.4 | 2.6 | 3.4 |

| ΘJA, K/W | Average Temperature of Die, °C | |

|---|---|---|

| Measurement [26] | 23.3 | 41.6 |

| Q3D model | 23.9 | 40.8 |

| Thermal Resistance, K/W | Value from the Reference [29] | Calculated by Q3D Model |

|---|---|---|

| ΘJB | 0.004 | 0.005 |

| ΘJC | 0.219 … 0.292 | 0.246 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Petrosyants, K.O.; Ryabov, N.I. Quasi-3D Thermal Simulation of Integrated Circuit Systems in Packages. Energies 2020, 13, 3054. https://doi.org/10.3390/en13123054

Petrosyants KO, Ryabov NI. Quasi-3D Thermal Simulation of Integrated Circuit Systems in Packages. Energies. 2020; 13(12):3054. https://doi.org/10.3390/en13123054

Chicago/Turabian StylePetrosyants, Konstantin O., and Nikita I. Ryabov. 2020. "Quasi-3D Thermal Simulation of Integrated Circuit Systems in Packages" Energies 13, no. 12: 3054. https://doi.org/10.3390/en13123054

APA StylePetrosyants, K. O., & Ryabov, N. I. (2020). Quasi-3D Thermal Simulation of Integrated Circuit Systems in Packages. Energies, 13(12), 3054. https://doi.org/10.3390/en13123054