Design and Performance Evaluation of Multi-Gb/s Silicon Photonics Transmitters for High Energy Physics †

Abstract

:1. Introduction

2. Background

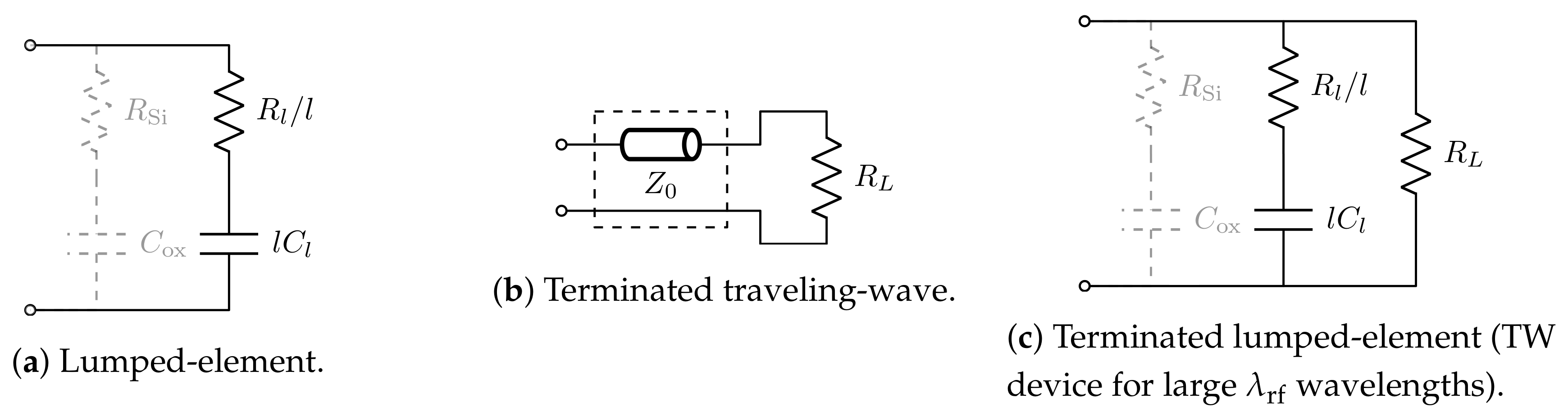

2.1. Silicon Photonics Modulators

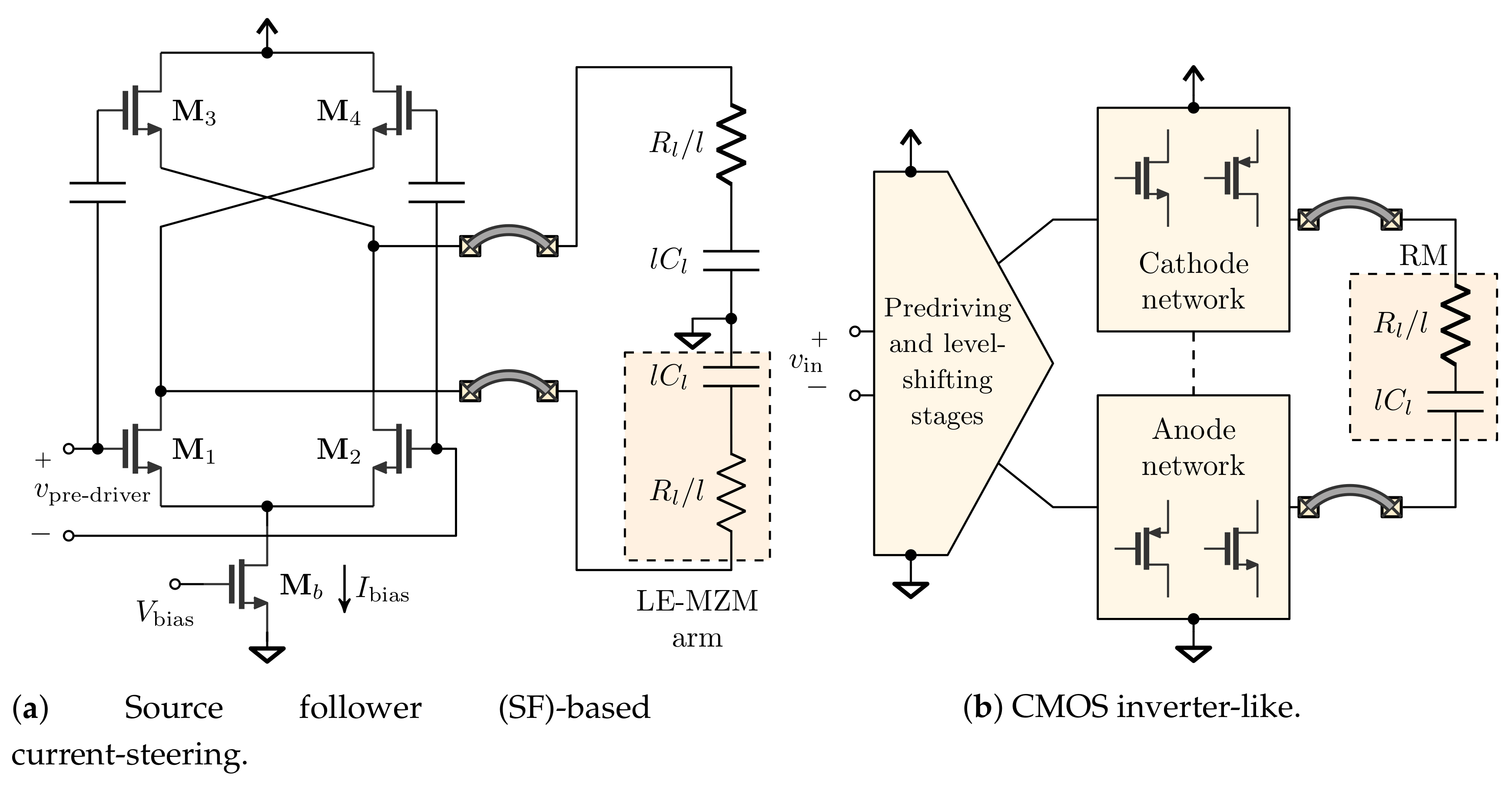

2.2. Driving Architectures

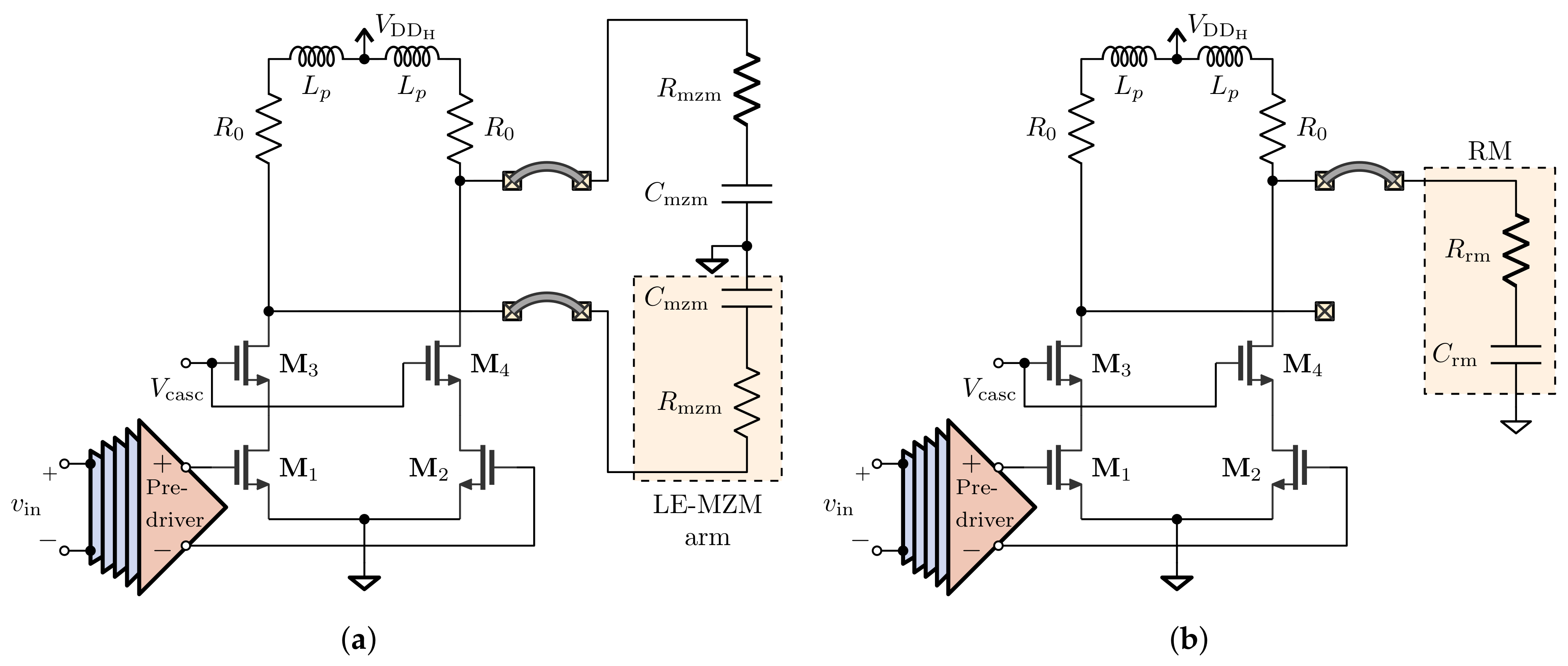

3. Proposed Driver Design

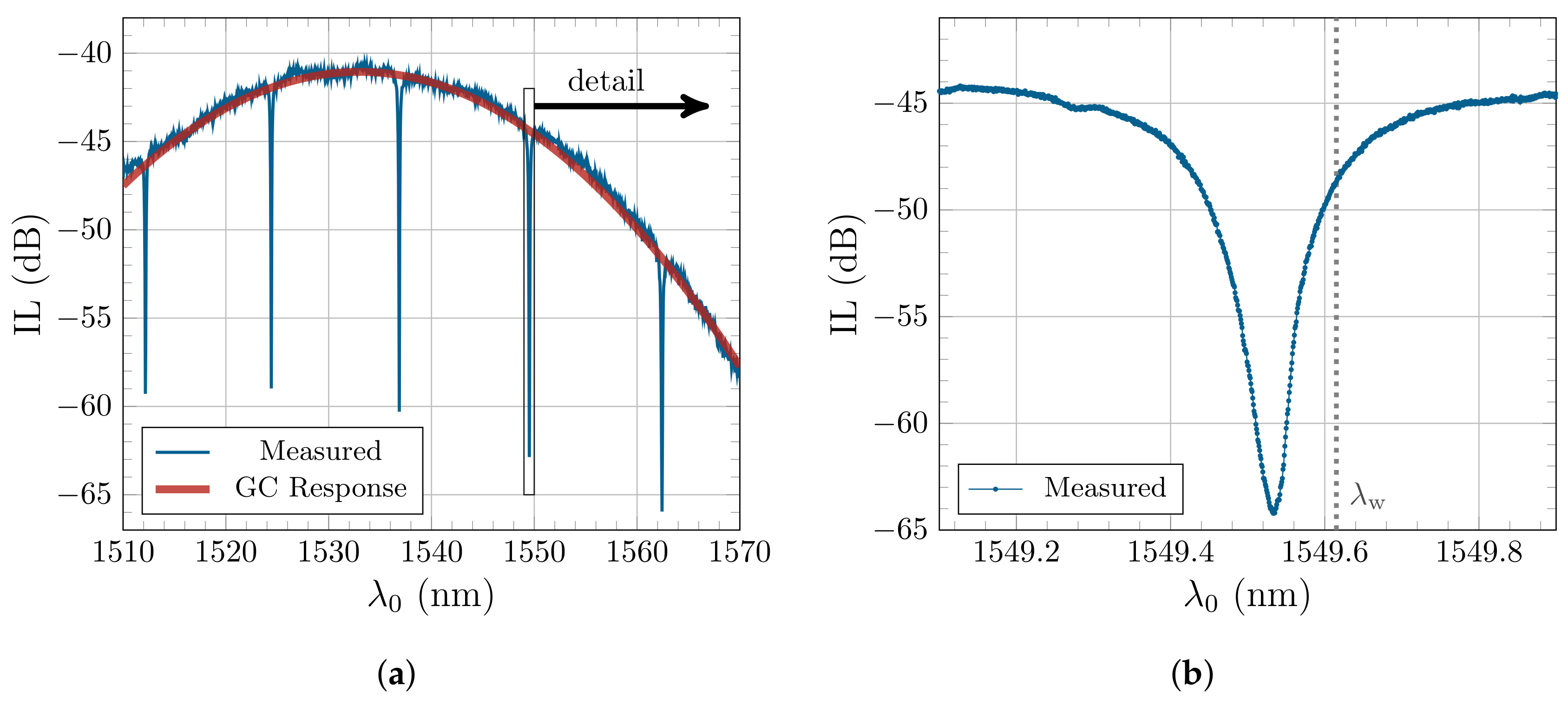

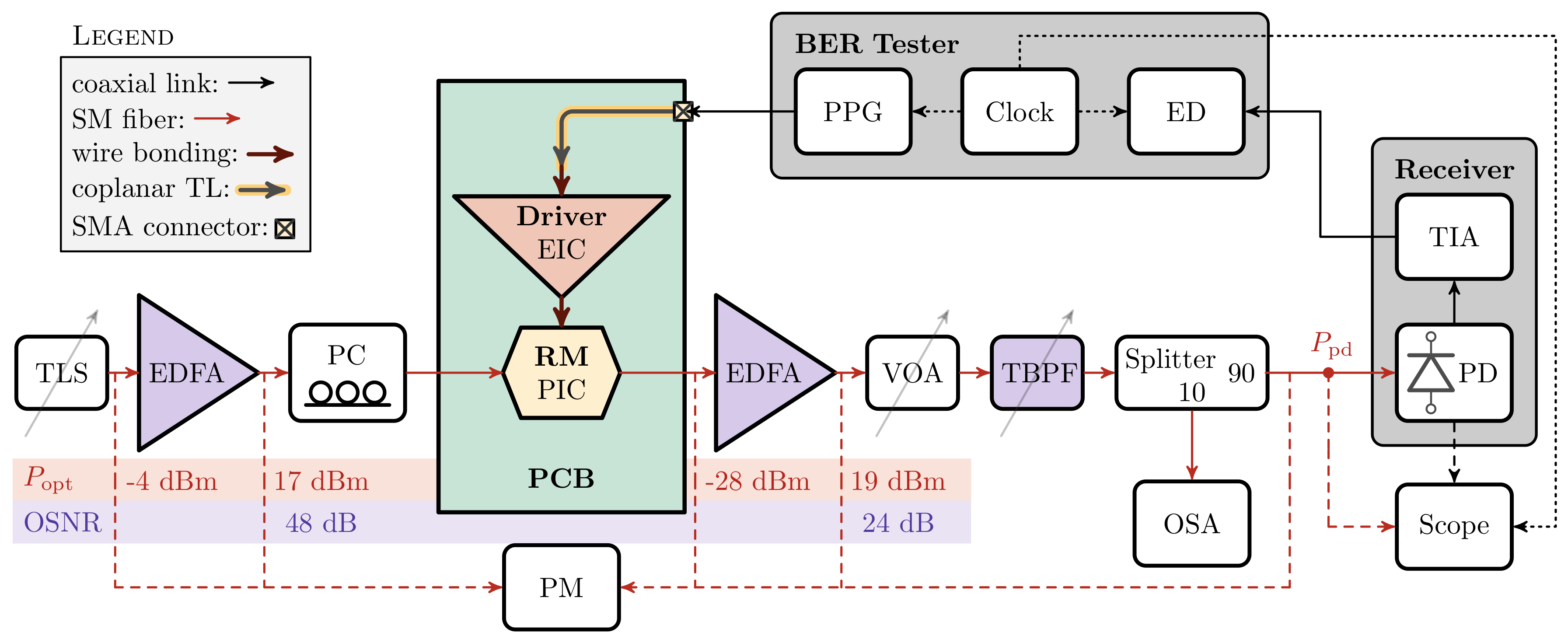

4. Experimental Setup

4.1. Samples

4.2. Measurement Procedures

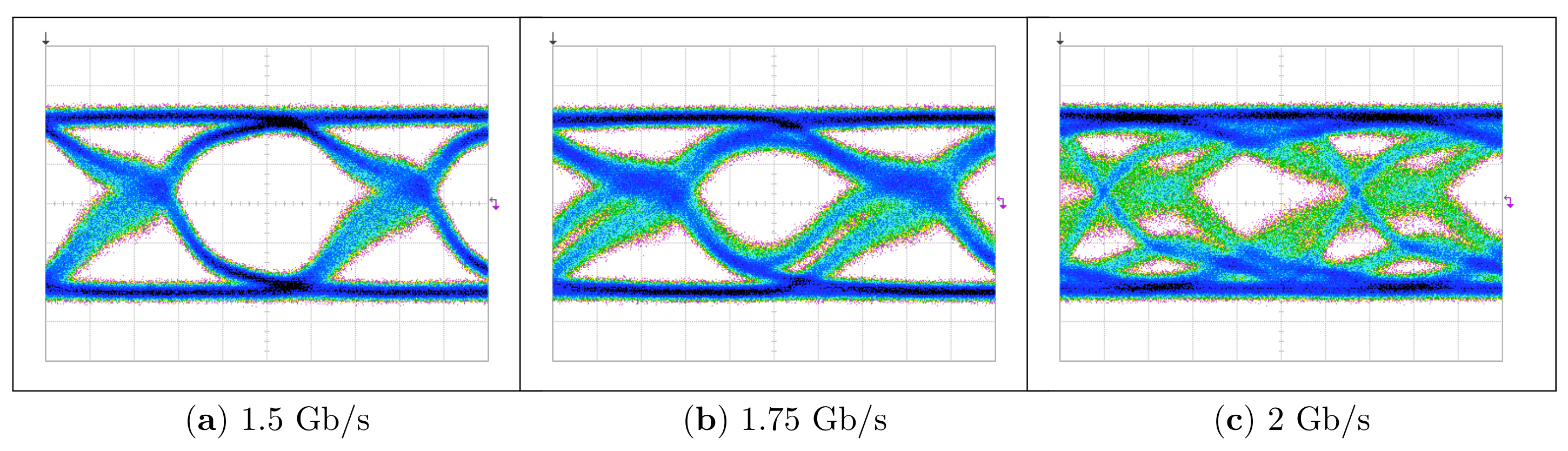

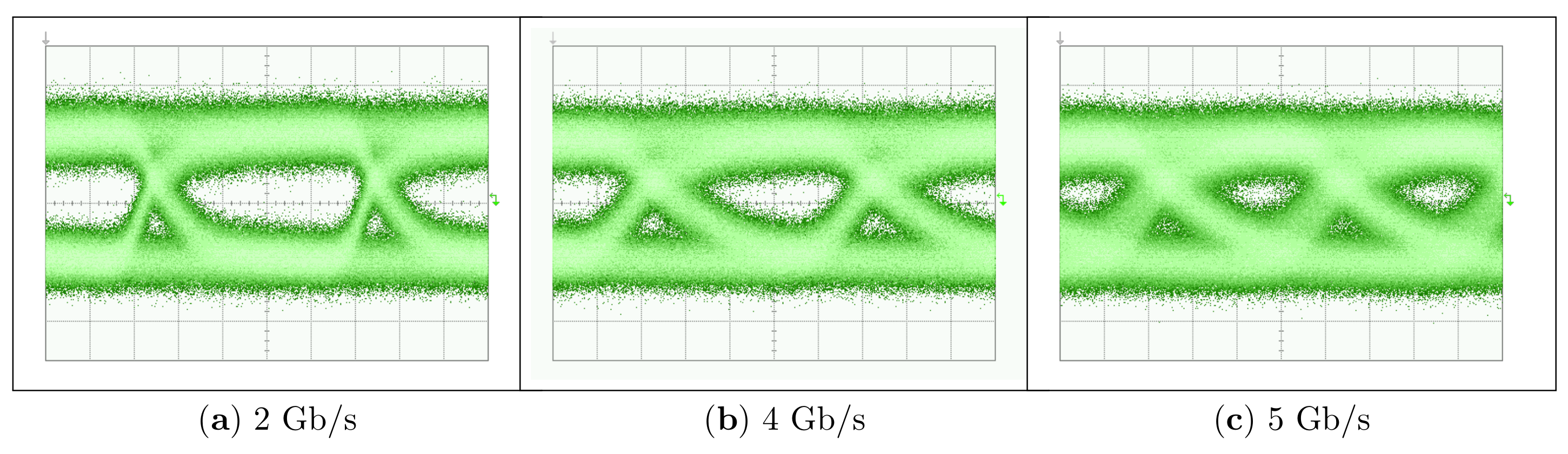

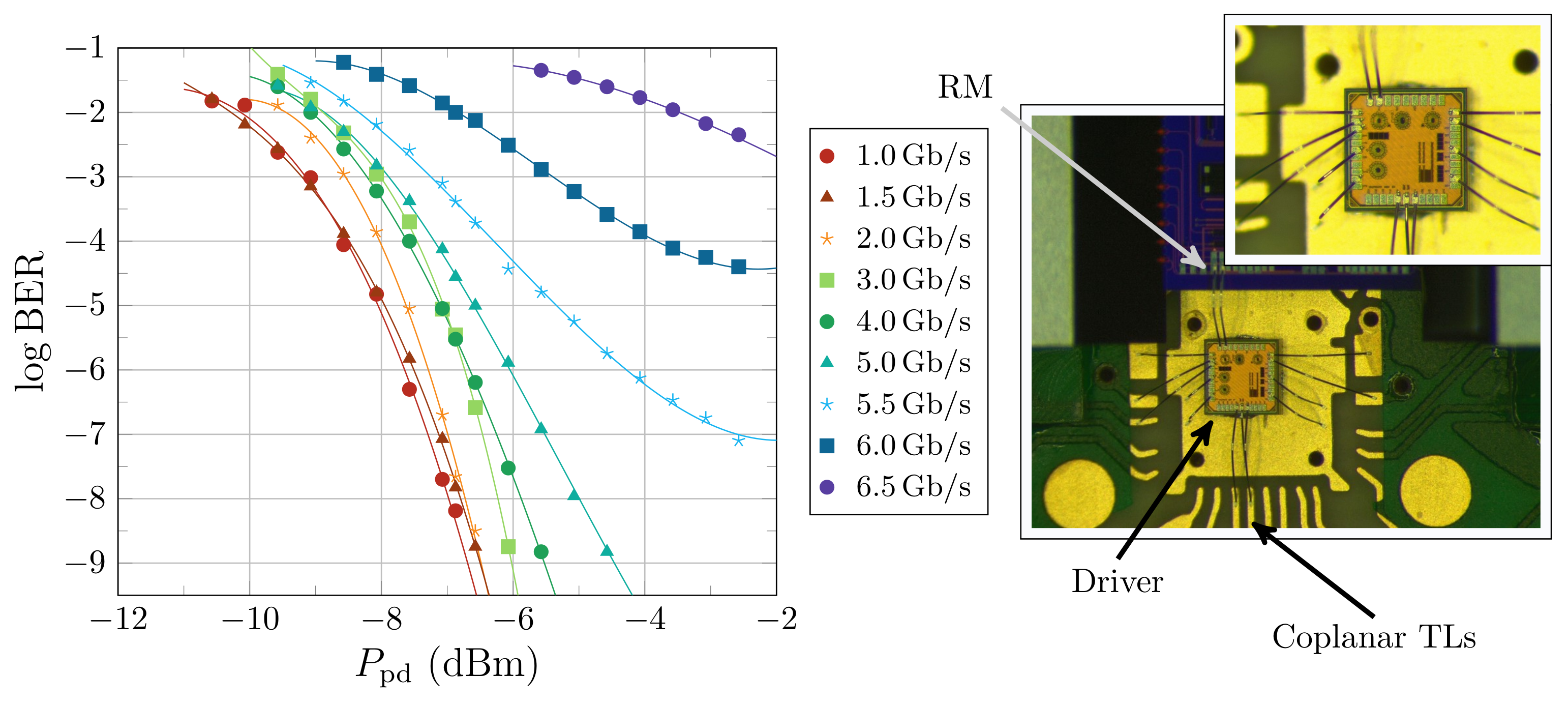

5. Results and Discussion

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Backhaus, M. The Upgrade of the CMS Inner Tracker for HL-LHC; Technical Report CMS-CR-2019-011; CERN: Geneva, Switzerland, 2019. [Google Scholar]

- Amaral, L.; Dris, S.; Gerardin, A.; Huffman, T.; Issever, C.; Pacheco, A.J.; Jones, M.; Kwan, S.; Lee, S.C.; Liang, Z.; et al. The versatile link, a common project for super-LHC. J. Instrum. 2009, 4, P12003. [Google Scholar] [CrossRef]

- Vasey, F.; Hall, D.; Huffman, T.; Kwan, S.; Prosser, A.; Soos, C.; Troska, J.; Weidberg, T.; Xiang, A.; Ye, J. The Versatile Link common project: Feasibility report. J. Instrum. 2012, 7, C01075. [Google Scholar] [CrossRef]

- Troska, J.; Detraz, S.; El Nasr-Storey, S.S.; Stejskal, P.; Sigaud, C.; Soos, C.; Vasey, F. Radiation Damage Studies of Lasers and Photodiodes for Use in Multi-Gb/s Optical Data Links. IEEE Trans. Nucl. Sci. 2011, 58, 3103–3110. [Google Scholar] [CrossRef] [Green Version]

- Mazza, G.; Rivetti, A.; Moreira, P.; Wyllie, K.; Soos, C.; Troska, J.; Gui, P. A radiation tolerant 5 Gb/s Laser Driver in 130 nm CMOS technology. J. Instrum. 2012, 7, C01052. [Google Scholar] [CrossRef]

- Seif El Nasr-Storey, S.; Boeuf, F.; Baudot, C.; Detraz, S.; Fedeli, J.M.; Marris-Morini, D.; Olantera, L.; Pezzullo, G.; Sigaud, C.; Soos, C.; et al. Effect of Radiation on a Mach–Zehnder Interferometer Silicon Modulator for HL-LHC Data Transmission Applications. IEEE Trans. Nucl. Sci. 2015, 62, 329–335. [Google Scholar] [CrossRef]

- Thomson, D.; Zilkie, A.; Bowers, J.E.; Komljenovic, T.; Reed, G.T.; Vivien, L.; Marris-Morini, D.; Cassan, E.; Virot, L.; Fédéli, J.M.; et al. Roadmap on silicon photonics. J. Opt. 2016, 18, 073003. [Google Scholar] [CrossRef]

- Oblakowska-Mucha, A. Radiation Hard Silicon Particle Detectors for Phase-II LHC Trackers. J. Instrum. 2017, 12, C02054. [Google Scholar] [CrossRef]

- Bogaerts, W.; Chrostowski, L. Silicon Photonics Circuit Design: Methods, Tools and Challenges. Laser Photonics Rev. 2018, 12, 1700237. [Google Scholar] [CrossRef]

- Nasr-Storey, S.E.; Détraz, S.; Olanterä, L.; Sigaud, C.; Soós, C.; Pezzullo, G.; Troska, J.; Vasey, F.; Zeiler, M. Neutron and X-ray irradiation of silicon based Mach-Zehnder modulators. J. Instrum. 2015, 10, C03040. [Google Scholar] [CrossRef] [Green Version]

- Zeiler, M.; El Nasr-Storey, S.S.; Detraz, S.; Kraxner, A.; Olantera, L.; Scarcella, C.; Sigaud, C.; Soos, C.; Troska, J.; Vasey, F. Radiation Damage in Silicon Photonic Mach–Zehnder Modulators and Photodiodes. IEEE Trans. Nucl. Sci. 2017, 64, 2794–2801. [Google Scholar] [CrossRef] [Green Version]

- Kraxner, A.; Detraz, S.; Olantera, L.; Scarcella, C.; Sigaud, C.; Soos, C.; Stile, C.; Troska, J.; Vasey, F. Radiation tolerance enhancement of silicon photonics for HEP applications. Proc. Sci. 2019, 17. [Google Scholar] [CrossRef]

- Rahim, A.; Spuesens, T.; Baets, R.; Bogaerts, W. Open-Access Silicon Photonics: Current Status and Emerging Initiatives. Proc. IEEE 2018, 106, 2313–2330. [Google Scholar] [CrossRef] [Green Version]

- Pantouvaki, M.; Srinivasan, S.A.; Ban, Y.; De Heyn, P.; Verheyen, P.; Lepage, G.; Chen, H.; De Coster, J.; Golshani, N.; Balakrishnan, S.; et al. Active Components for 50 Gb/s NRZ-OOK Optical Interconnects in a Silicon Photonics Platform. J. Lightw. Technol. 2017, 35, 631–638. [Google Scholar] [CrossRef]

- Mazza, G.; Tavernier, F.; Moreira, P.; Calvo, D.; De Remigis, P.; Olantera, L.; Soos, C.; Troska, J.; Wyllie, K. High-Speed, Radiation-Tolerant Laser Drivers in 0.13 μm CMOS Technology for HEP Applications. IEEE Trans. Nucl. Sci. 2014, 61, 3653–3659. [Google Scholar] [CrossRef]

- Zhang, Y.; Schneider, M.; Karnick, D.; Eisenblätter, L.; Kühner, T.; Weber, M. Key building blocks of a silicon photonic integrated transmitter for future detector instrumentation. J. Instrum. 2019, 14, P08021. [Google Scholar] [CrossRef]

- Ciarpi, G.; Cammarata, S.; Faralli, S.; Vehla, P.; Magazzù, G.; Palla, F.; Saponara, S. Design, Operation and BER Test of Multi-Gb/s Radiation-Hard Drivers in 65 nm Technology for Silicon Photonics Optical Modulators. In Applications in Electronics Pervading Industry, Environment and Society; Saponara, S., De Gloria, A., Eds.; Springer International Publishing: Cham, Switzerland, 2020; pp. 11–18. [Google Scholar]

- Reed, G.; Mashanovich, G.; Gardes, F.; Thomson, D. Silicon optical modulators [Review]. Nat. Photonics 2010, 4, 518–526. [Google Scholar] [CrossRef] [Green Version]

- Nedeljkovic, M.; Soref, R.; Mashanovich, G.Z. Free-Carrier Electrorefraction and Electroabsorption Modulation Predictions for Silicon Over the 1–14-μm Infrared Wavelength Range. IEEE Photonics J. 2011, 3, 1171–1180. [Google Scholar] [CrossRef]

- Witzens, J. High-Speed Silicon Photonics Modulators. Proc. IEEE 2018, 106, 2158–2182. [Google Scholar] [CrossRef]

- Fresi, F.; Malacarne, A.; Sorianello, V.; Meloni, G.; Velha, P.; Midrio, M.; Toccafondo, V.; Faralli, S.; Romagnoli, M.; Poti, L. Reconfigurable Silicon Photonics Integrated 16-QAM Modulator Driven by Binary Electronics. IEEE J. Select. Top. Quant. Electron. 2016, 22, 334–343. [Google Scholar] [CrossRef]

- Bogaerts, W.; De Heyn, P.; Van Vaerenbergh, T.; De Vos, K.; Kumar Selvaraja, S.; Claes, T.; Dumon, P.; Bienstman, P.; Van Thourhout, D.; Baets, R. Silicon microring resonators. Laser Photonics Rev. 2012, 6, 47–73. [Google Scholar] [CrossRef]

- Malacarne, A.; Gambini, F.; Faralli, S.; Klamkin, J.; Poti, L. High-Speed Silicon Electro-Optic Microring Modulator for Optical Interconnects. IEEE Photonics Technol. Lett. 2014, 26, 1042–1044. [Google Scholar] [CrossRef]

- Van Kerrebrouck, J.; De Keulenaer, T.; Pierco, R.; De Geest, J.; Sinsky, J.H.; Kozicki, B.; Yin, X.; Torfs, G.; Bauwelinck, J. NRZ, Duobinary, or PAM4?: Choosing Among High-Speed Electrical Interconnects. IEEE Microw. Mag. 2019, 20, 24–35. [Google Scholar] [CrossRef]

- Xiao, X.; Xu, H.; Li, X.; Hu, Y.; Xiong, K.; Li, Z.; Chu, T.; Yu, Y.; Yu, J. 25 Gbit/s silicon microring modulator based on misalignment-tolerant interleaved PN junctions. Opt. Express 2012, 20, 2507–2515. [Google Scholar] [CrossRef] [PubMed]

- Temporiti, E.; Ghilioni, A.; Minoia, G.; Orlandi, P.; Repossi, M.; Baldi, D.; Svelto, F. Insights Into Silicon Photonics Mach–Zehnder-Based Optical Transmitter Architectures. IEEE J. Solid-State Circ. 2016, 51, 3178–3191. [Google Scholar] [CrossRef]

- Zhou, S.; Ta Wu, H.; Sadeghipour, K.; Scarcella, C.; Eason, C.; Rensing, M.; Power, M.J.; Antony, C.; O’Brien, P.; Townsend, P.D.; et al. Optimization of PAM-4 transmitters based on lumped silicon photonic MZMs for high-speed short-reach optical links. Opt. Express 2017, 25, 4312–4325. [Google Scholar] [CrossRef] [PubMed]

- Li, K.; Thomson, D.J.; Liu, S.; Meng, F.; Shakoor, A.; Khokhar, A.; Cao, W.; Zhang, W.; Wilson, P.; Reed, G.T. Co-Design of Electronics and Photonics Components for Silicon Photonics Transmitters. In Proceedings of the 2018 European Conference on Optical Communication (ECOC), Rome, Italy, 23–27 September 2018; pp. 1–3. [Google Scholar] [CrossRef]

- Razavi, B. Design of Integrated Circuits for Optical Communications; Wiley: Hoboken, NJ, USA, 2012. [Google Scholar]

- Li, K.; Thomson, D.J.; Liu, S.; Wilson, P.; Reed, G.T. A 30 Gb/s CMOS driver integrated with silicon photonics MZM. In Proceedings of the 2015 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Phoenix, AZ, USA, 17–19 May 2015; pp. 311–314. [Google Scholar]

- Li, C.; Yu, K.; Rhim, J.; Zhu, K.; Qi, N.; Fiorentino, M.; Pinguet, T.; Peterson, M.; Saxena, V.; Palermo, S. A 3D-Integrated 56 Gb/s NRZ/PAM4 Reconfigurable Segmented Mach-Zehnder Modulator-Based Si-Photonics Transmitter. In Proceedings of the 2018 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), San Diego, CA, USA, 14–17 October 2018; pp. 32–35. [Google Scholar] [CrossRef]

- Rakowski, M.; Ryckaert, J.; Pantouvaki, M.; Yu, H.; Bogaerts, W.; de Meyer, K.; Steyaert, M.; Absil, P.P.; Van Campenhout, J. Low-Power, 10-Gbps 1.5-Vpp differential CMOS driver for a silicon electro-optic ring modulator. In Proceedings of the IEEE 2012 Custom Integrated Circuits Conference, San Jose, CA, USA, 9–12 September 2012; pp. 1–6. [Google Scholar] [CrossRef] [Green Version]

- Zhou, S.; Wu, H.; Sadeghipour, K.; Scarcella, C.; Eason, C.; Rensing, M.; Power, M.; Antony, C.; O’Brien, P.; Townsend, P.; et al. Driver circuit for a PAM-4 optical transmitter using 65 nm CMOS and silicon photonic technologies. Electron. Lett. 2016, 52, 1939–1940. [Google Scholar] [CrossRef]

- Cignoli, M.; Minoia, G.; Repossi, M.; Baldi, D.; Ghilioni, A.; Temporiti, E.; Svelto, F. 22.9 A 1310 nm 3D-integrated silicon photonics Mach-Zehnder-based transmitter with 275 mW multistage CMOS driver achieving 6 dB extinction ratio at 25 Gb/s. In Proceedings of the 2015 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 22–26 February 2015; pp. 1–3. [Google Scholar] [CrossRef]

- Liao, Q.; Qi, N.; Li, M.; Hu, S.; He, J.; Yin, B.; Shi, J.; Liu, J.; Chiang, P.Y.; Xiao, X.; et al. A 50-Gb/s PAM4 Si-Photonic Transmitter With Digital-Assisted Distributed Driver and Integrated CDR in 40-nm CMOS. IEEE J. Solid-State Circ. 2020, 55, 1282–1296. [Google Scholar] [CrossRef]

- Faccio, F.; Borghello, G.; Lerario, E.; Fleetwood, D.M.; Schrimpf, R.D.; Gong, H.; Zhang, E.X.; Wang, P.; Michelis, S.; Gerardin, S.; et al. Influence of LDD Spacers and H+ Transport on the Total-Ionizing-Dose Response of 65-nm MOSFETs Irradiated to Ultrahigh Doses. IEEE Trans. Nucl. Sci. 2018, 65, 164–174. [Google Scholar] [CrossRef]

- Bonaldo, S.; Mattiazzo, S.; Enz, C.; Baschilotto, A.; Fleetwood, D.M.; Paccagnella, A.; Gerardin, S. Ionizing-Radiation Response and Low-Frequency Noise of 28-nm MOSFETs at Ultra-High Doses. IEEE Trans. Nucl. Sci. 2020. [Google Scholar] [CrossRef]

- Bonaldo, S.; Gerardin, S.; Jin, X.; Paccagnella, A.; Faccio, F.; Borghello, G.; Fleetwood, D.M. Charge Buildup and Spatial Distribution of Interface Traps in 65-nm pMOSFETs Irradiated to Ultrahigh Doses. IEEE Trans. Nucl. Sci. 2019, 66, 1574–1583. [Google Scholar] [CrossRef]

- Ciarpi, G.; Saponara, S.; Magazzù, G.; Palla, F. Radiation Hardness by Design Techniques for 1 Grad TID Rad-Hard Systems in 65 nm Standard CMOS Technologies. In Applications in Electronics Pervading Industry, Environment and Society; Saponara, S., De Gloria, A., Eds.; Springer International Publishing: Cham, Switzerland, 2019; pp. 269–276. [Google Scholar]

- Snoeys, W.J.; Gutierrez, T.A.P.; Anelli, G. A new NMOS layout structure for radiation tolerance. IEEE Trans. Nucl. Sci. 2002, 49, 1829–1833. [Google Scholar] [CrossRef]

- Sedighi, B.; Christoph Scheytt, J. 40 Gb/s VCSEL driver IC with a new output current and pre-emphasis adjustment method. In Proceedings of the 2012 IEEE/MTT-S International Microwave Symposium Digest, Montreal, QC, Canada, 17–22 June 2012; pp. 1–3. [Google Scholar] [CrossRef]

- Zandieh, A.; Schvan, P.; Voinigescu, S.P. Linear Large-Swing Push–Pull SiGe BiCMOS Drivers for Silicon Photonics Modulators. IEEE Trans. Microw. Theory Tech. 2017, 65, 5355–5366. [Google Scholar] [CrossRef]

- Jeong, G.S.; Bae, W.; Jeong, D.K. Review of CMOS Integrated Circuit Technologies for High-Speed Photo-Detection. Sensors 2017, 17, 1962. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Ciarpi, G.; Magazzù, G.; Palla, F.; Saponara, S. Design, Implementation, and Experimental Verification of 5 Gbps, 800 Mrad TID and SEU-Tolerant Optical Modulators Drivers. IEEE Trans. Circ. Syst. I Regul. Pap. 2020, 67, 829–838. [Google Scholar] [CrossRef]

- Zeiler, M.; Detraz, S.; Olantera, L.; Pezzullo, G.; Nasr-Storey, S.S.E.; Sigaud, C.; Soos, C.; Troska, J.; Vasey, F. Design of Si-photonic structures to evaluate their radiation hardness dependence on design parameters. J. Instrum. 2016, 11, C01040. [Google Scholar] [CrossRef] [Green Version]

- Carroll, L.; Lee, J.S.; Scarcella, C.; Gradkowski, K.; Duperron, M.; Lu, H.; Zhao, Y.; Eason, C.; Morrissey, P.; Rensing, M.; et al. Photonic Packaging: Transforming Silicon Photonic Integrated Circuits into Photonic Devices. Appl. Sci. 2016, 6, 426. [Google Scholar] [CrossRef]

- Hui, R.; O’Sullivan, M. Optical System Performance Measurements. In Fiber Optic Measurement Techniques; Chapter 5; Hui, R., O’Sullivan, M., Eds.; Academic Press: New York, NY, USA, 2009; pp. 481–630. [Google Scholar] [CrossRef]

- Mazza, G.; Tavernier, F.; Moreira, P.; Rivetti, A.; Soos, C.; Troska, J.; Wyllie, K. The GBLD: A radiation tolerant laser driver for high energy physics applications. J. Instrum. 2013, 8, C01033. [Google Scholar] [CrossRef]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cammarata, S.; Ciarpi, G.; Faralli, S.; Velha, P.; Magazzù, G.; Palla, F.; Saponara, S. Design and Performance Evaluation of Multi-Gb/s Silicon Photonics Transmitters for High Energy Physics. Energies 2020, 13, 3569. https://doi.org/10.3390/en13143569

Cammarata S, Ciarpi G, Faralli S, Velha P, Magazzù G, Palla F, Saponara S. Design and Performance Evaluation of Multi-Gb/s Silicon Photonics Transmitters for High Energy Physics. Energies. 2020; 13(14):3569. https://doi.org/10.3390/en13143569

Chicago/Turabian StyleCammarata, Simone, Gabriele Ciarpi, Stefano Faralli, Philippe Velha, Guido Magazzù, Fabrizio Palla, and Sergio Saponara. 2020. "Design and Performance Evaluation of Multi-Gb/s Silicon Photonics Transmitters for High Energy Physics" Energies 13, no. 14: 3569. https://doi.org/10.3390/en13143569