An Analog Magnetic Isolator for Space Power Applications

Abstract

:1. Introduction

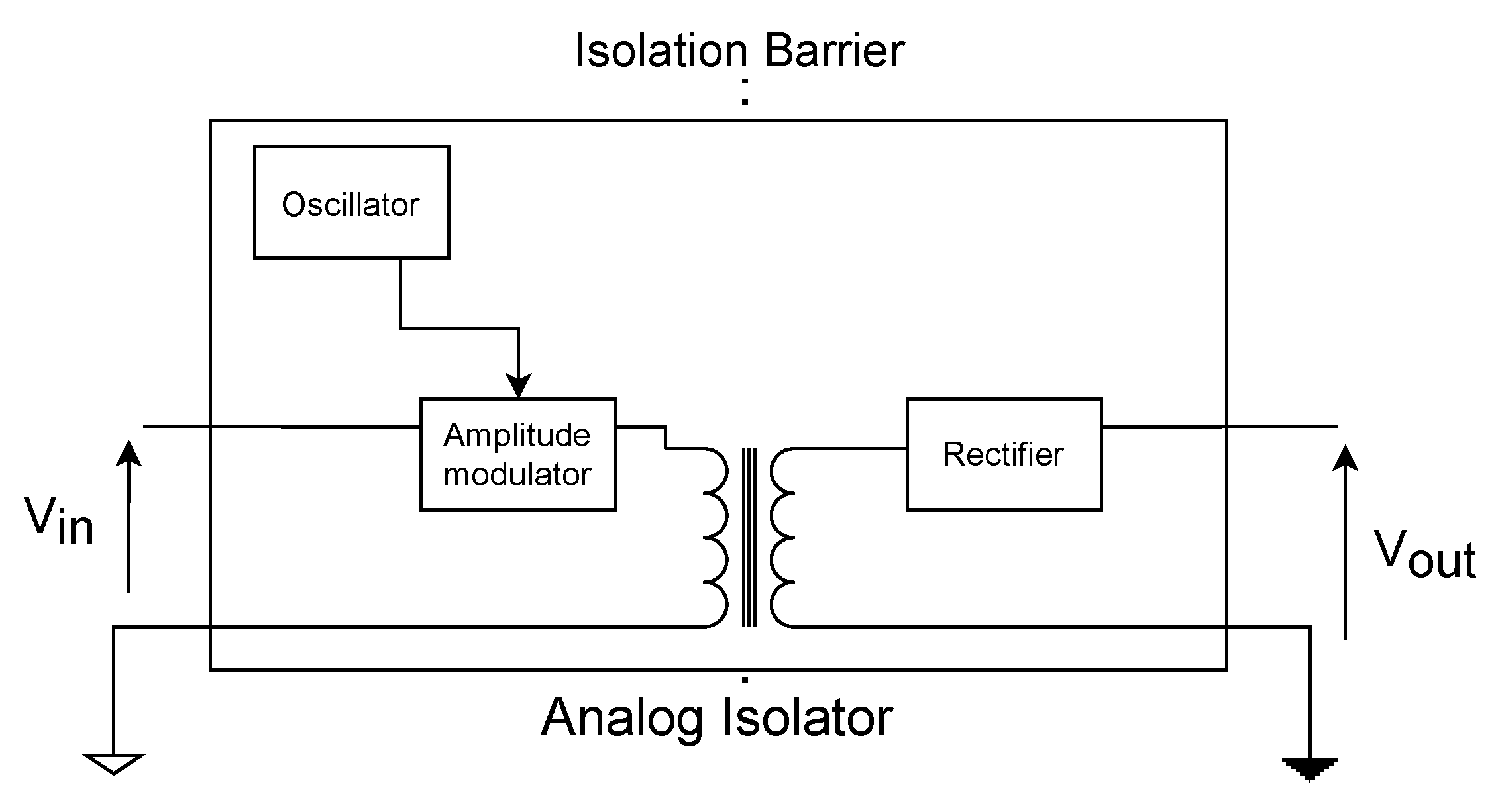

2. Design of the Analog Isolator

2.1. Concept and Reference Designs

2.2. Space Qualified Components’ Restrictions

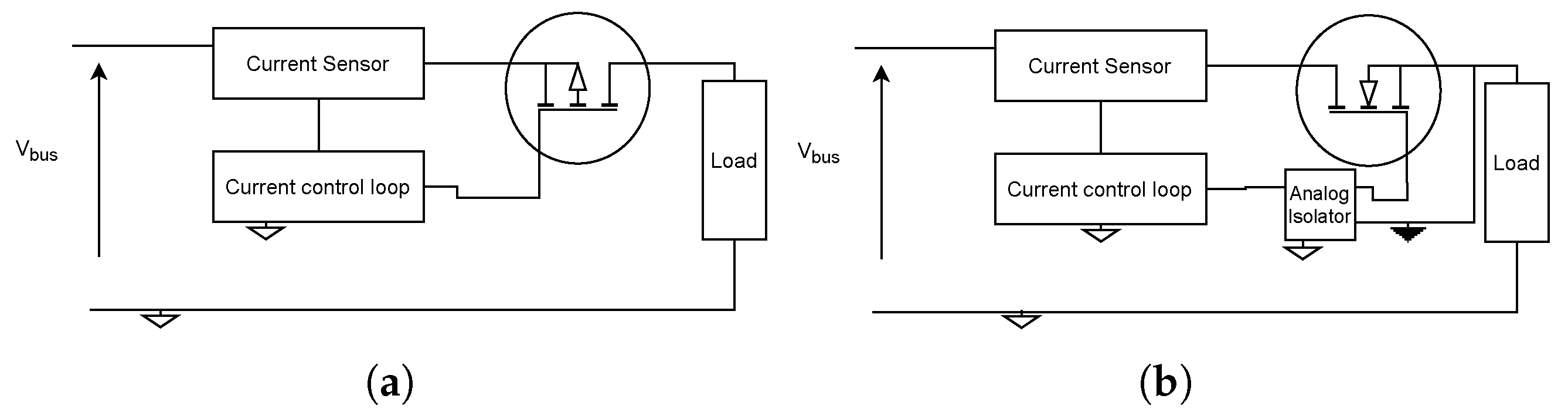

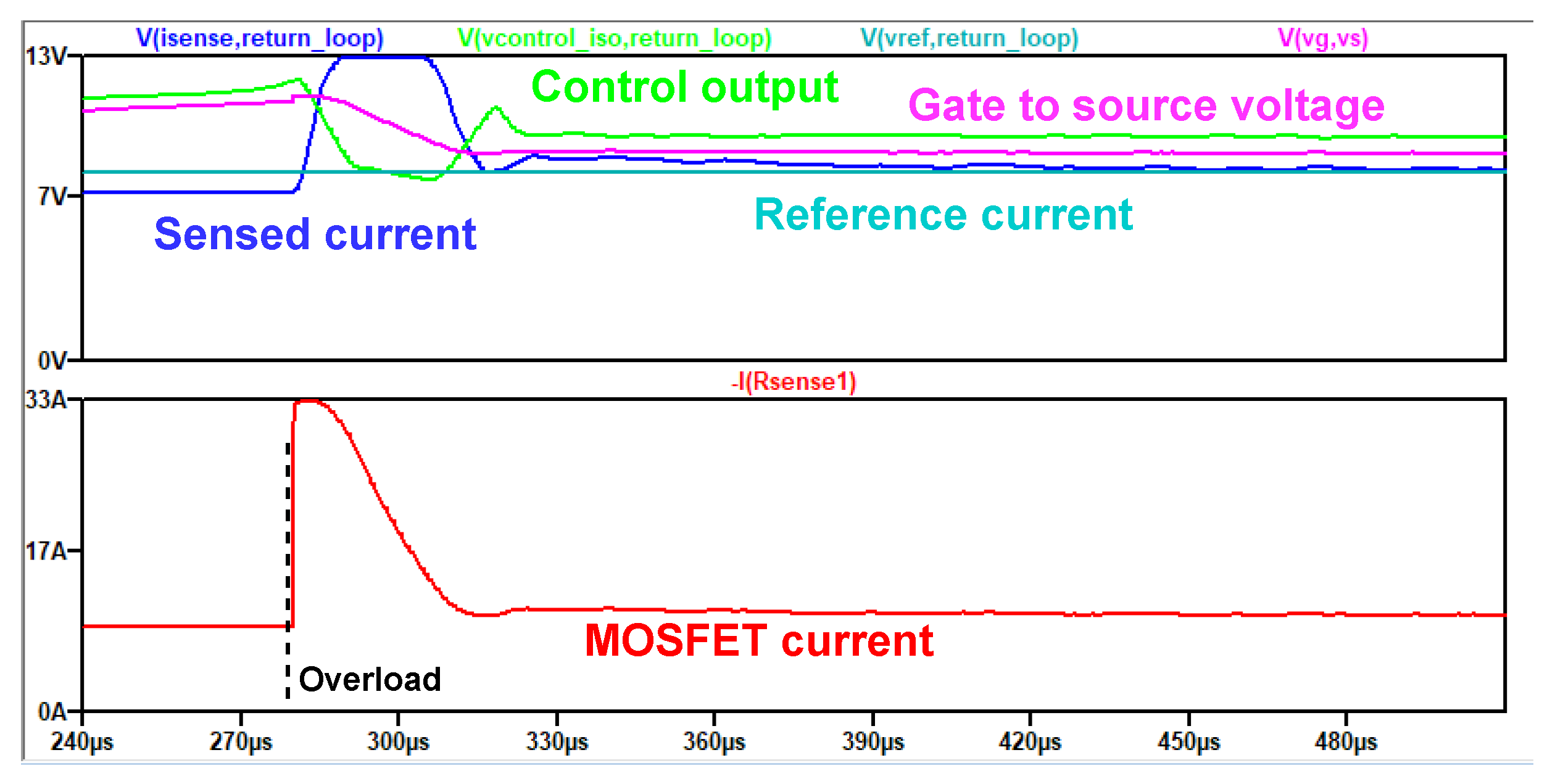

2.3. Application: Latching Current Limiters

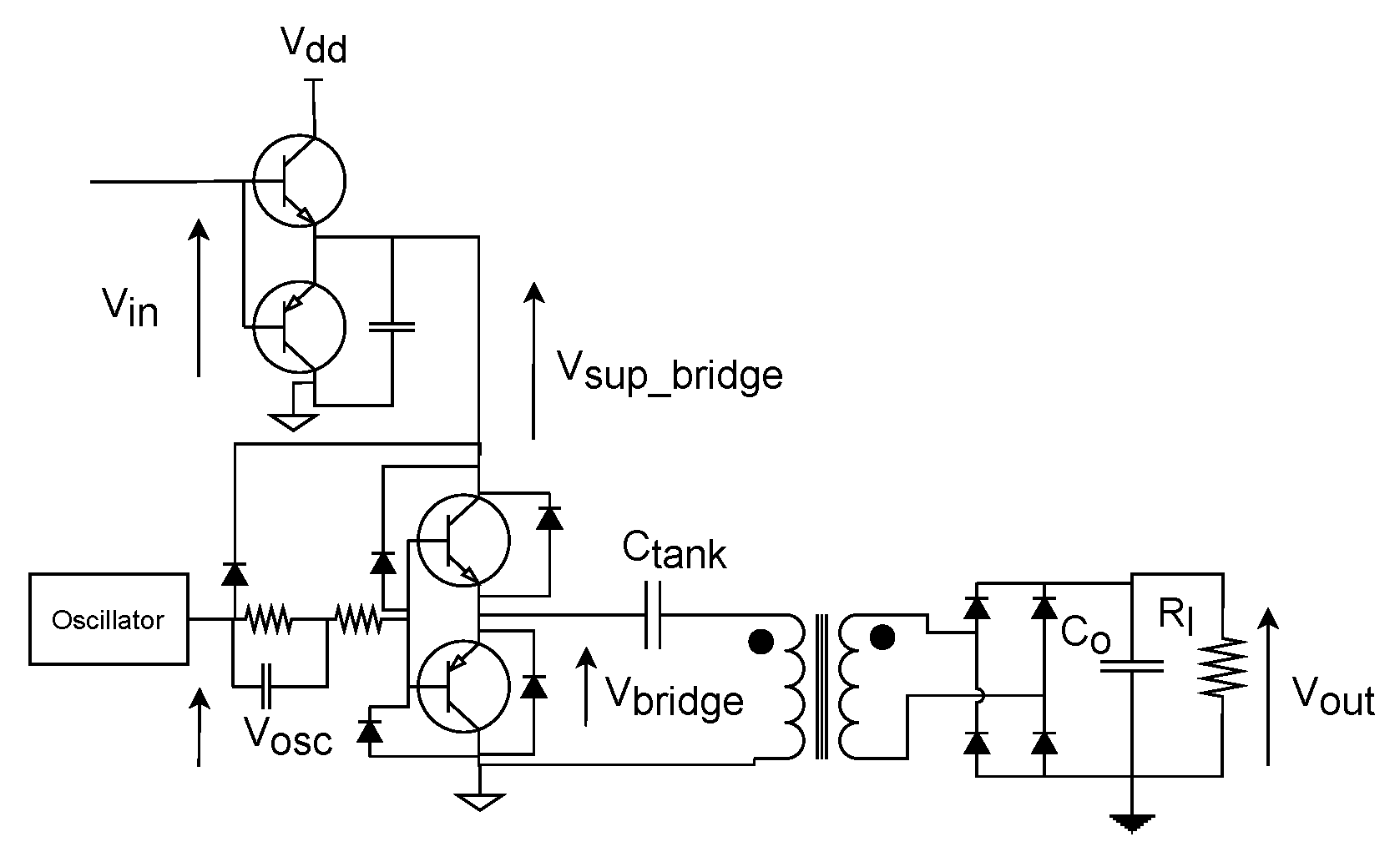

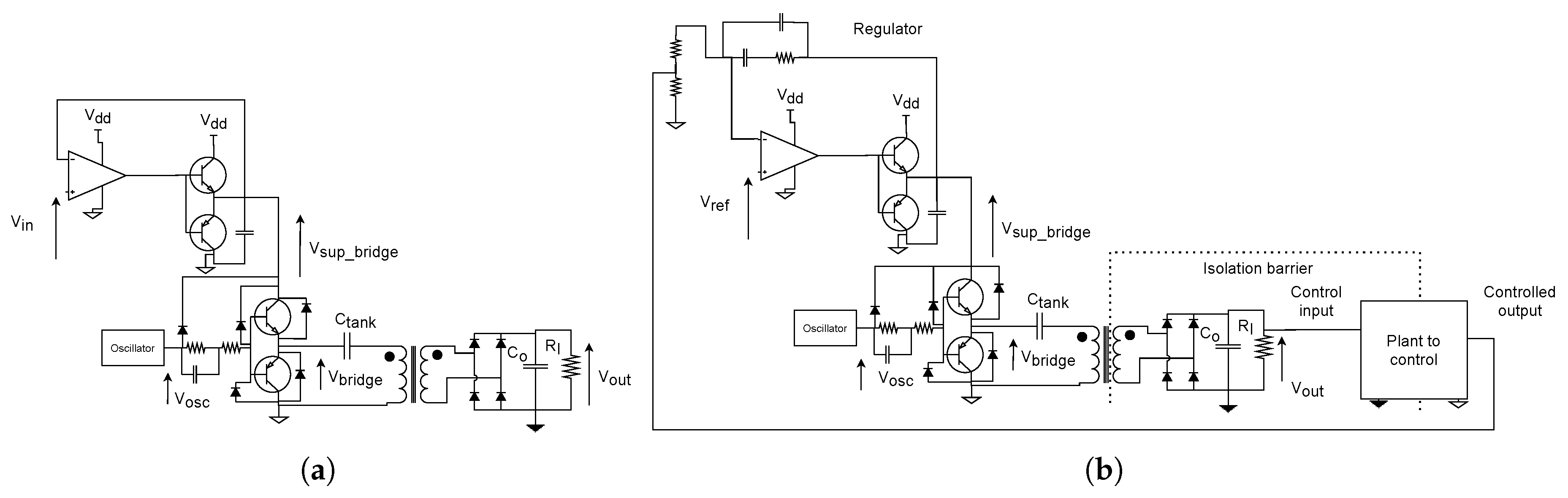

3. Proposed Design

3.1. Isolator Design Description

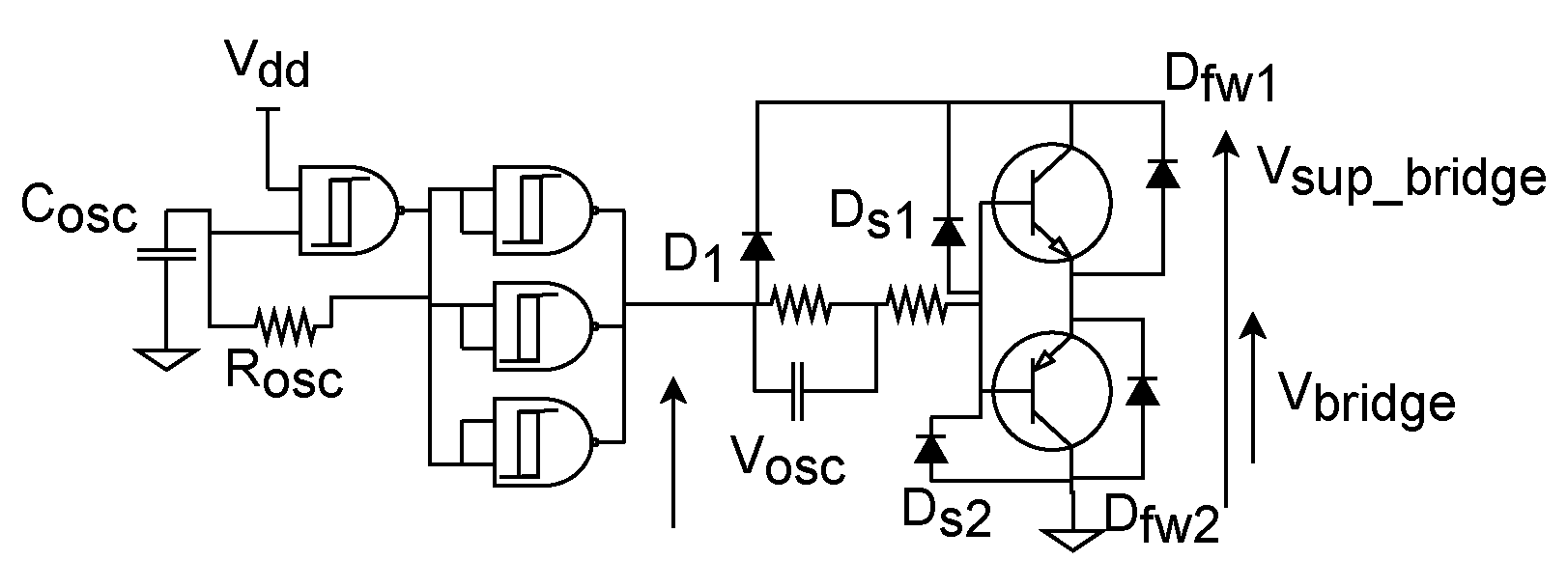

3.1.1. Oscillator and Transformer Driver

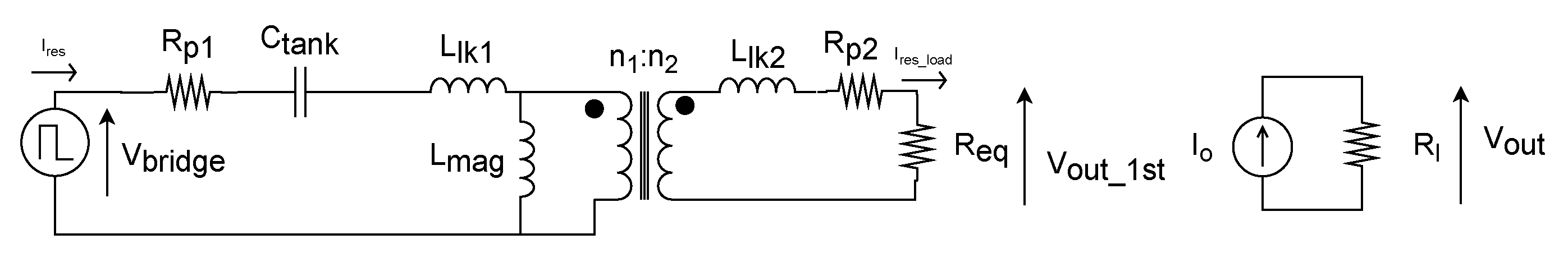

3.1.2. Resonant Network Design

4. Experimental Results

4.1. Design Procedure

- Choose a the switching frequency at least 10 times higher than the desired bandwidth. In this case, it was set to 4 MHz.

- Design a transformer. The turns ratio will be 1. This will fix the values of , and which can be obtained by measurement or by simulation through a finite element analysis software.

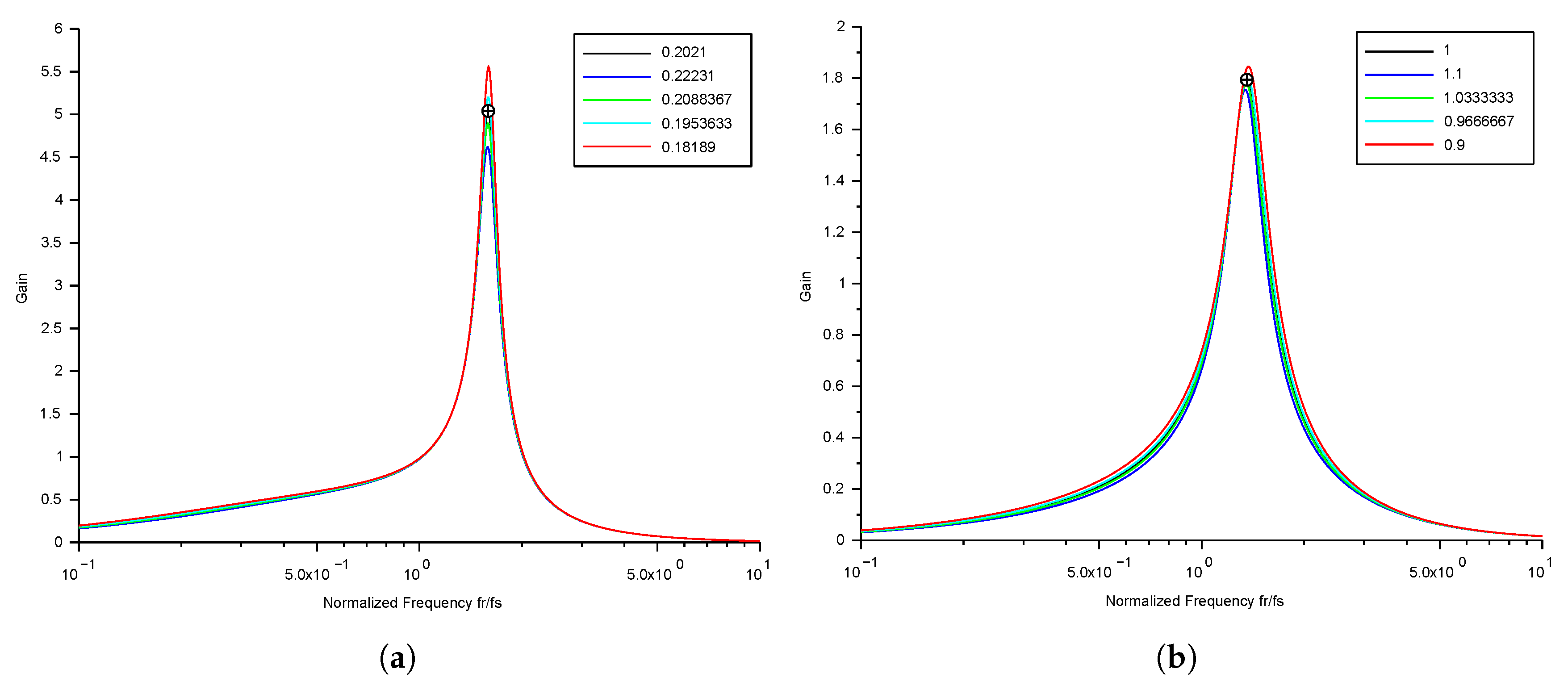

- Choose the desired and therefore . Plot Equation (10) with different ranges of and . The values of the resistances and can be approximated by the parasitic resistance of the windings plus the ESR of the resonant capacitor.

- With selected to achieve fix and . The latter with the selected determines .

- With and , select using Equation (7).

- With and , select that guarantees the desired using Equation (9).

- Transform to using Equation (1) to finish the design.

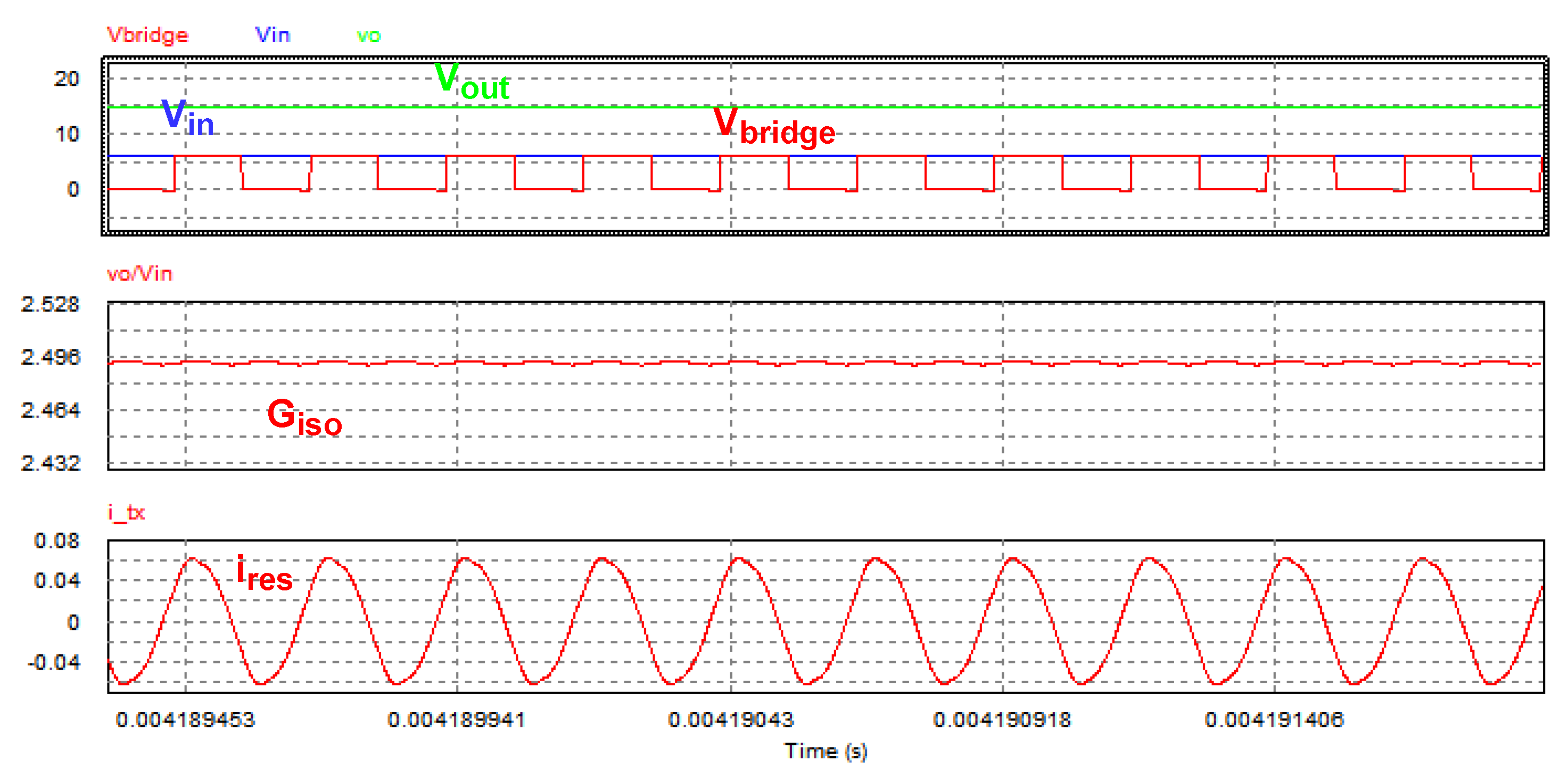

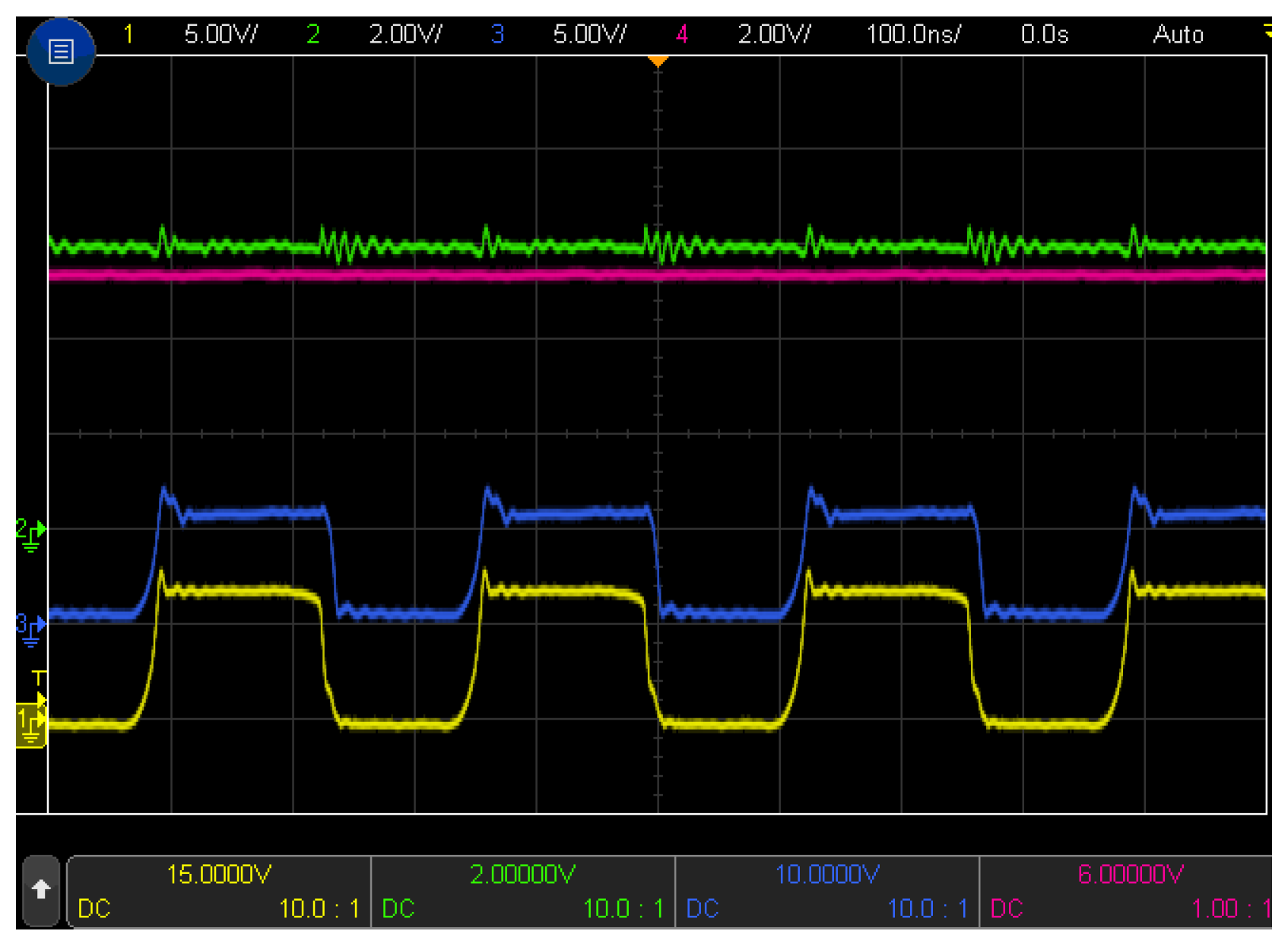

4.2. Prototype Measurements

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Reed, R.A.; Poivey, C.; Marshall, P.W.; LaBel, K.A.; Marshall, C.J.; Kniffin, S.; Barth, J.L.; Seidleck, C. Assessing the impact of the space radiation environment on parametric degradation and single-event transients in optocouplers. IEEE Trans. Nucl. Sci. 2001, 48, 2202–2209. [Google Scholar] [CrossRef]

- LaBel, K.A.; Kniffin, S.D.; Reed, R.A.; Kim, H.S.; Wert, J.L.; Oberg, D.L.; Normand, E.; Johnston, A.H.; Lum, G.K.; Koga, R.; et al. A compendium of recent optocoupler radiation test data. In Proceedings of the 2000 IEEE Radiation Effects Data Workshop, Workshop Record, Held in conjunction with IEEE Nuclear and Space Radiation Effects Conference (Cat. No.00TH8527), Reno, NV, USA, 24–28 July 2000; pp. 123–146. [Google Scholar]

- Microsemi. SA50-120-12S-B-P Rad Hard DC/DC Converter Datasheet. Available online: https://www.microsemi.com/document-portal/doc_view/134142-sb30-28-datasheet (accessed on 28 July 2020).

- U-94 The UC1901 Simplifies the Problem of Isolated Feedback in Switching Regulators; Technical Report; Unitrode: Merrimack, NH, USA, 1999.

- Irving, B.T.; Jovanovic, M.M. Analysis and Design Optimization of Magnetic-Feedback Control Using Amplitude Modulation. IEEE Trans. Power Electron. 2009, 24, 426–433. [Google Scholar] [CrossRef]

- Sayani, M.; White, R.; Nason, D.; Taylor, W. Isolated feedback for offline switching power supplies with primary-side control. In Proceedings of the APEC ’88 Third Annual IEEE Applied Power Electronics Conference and Exposition, New Orleans, LA, USA, 1–5 February 1988; pp. 203–211. [Google Scholar] [CrossRef]

- European Preferred Parts List ESCCC/RP/EPPL007-38. 2019. Available online: https://escies.org/download/webDocumentFile?id=67263 (accessed on 28 July 2020).

- Texas Instruments. UC1901 Datasheet; Texas Instruments: Dallas, TX, USA, 2010. [Google Scholar]

- Analog Devices. ADuM3190S Datasheet; Analog Devices: Norwood, MA, USA, 2019. [Google Scholar]

- Space Engineering-Electrical Design and Interface Requirements for Power Supply; ECSS: Noordwijk, The Netherlands, 2016.

- Space Engineering-Guidelines for Electrical Design and Interface Requirements for Power Supply; ECSS: Noordwijk, The Netherlands, 2016.

- Space Product Assurance—Derating—EEE Components; ECSS: Noordwijk, The Netherlands, 2011.

- De Simone, S.; Adragna, C.; Spini, C.; Gattavari, G. Design-oriented steady-state analysis of LLC resonant converters based on FHA. In Proceedings of the International Symposium on Power Electronics, Electrical Drives, Automation and Motion, SPEEDAM, Taormina, Italy, 23–26 May 2006; pp. 200–207. [Google Scholar] [CrossRef]

- Simone, S.D. LLC Resonant Half-Bridge Converter Design Guideline; STMicroelectronics: Coppell, TX, USA, 2007. [Google Scholar]

- Abdel-Rahman, S. Resonant LLC Converter: Operation and Design; Infineon: Neubiberg, Germany, 2012. [Google Scholar]

- Park, H.P.; Jung, J.H. Power Stage and Feedback Loop Design for LLC Resonant Converter in High-Switching-Frequency Operation. IEEE Trans. Power Electron. 2017, 32, 7770–7782. [Google Scholar] [CrossRef]

- Steigerwald, R. A Comparison of Half-Bridge Resonant Converter Topologies. IEEE Trans. Power Electron. 1988, 3, 174–182. [Google Scholar] [CrossRef]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

F. Miaja, P.; Lopez, A.; Arias, M. An Analog Magnetic Isolator for Space Power Applications. Energies 2020, 13, 4504. https://doi.org/10.3390/en13174504

F. Miaja P, Lopez A, Arias M. An Analog Magnetic Isolator for Space Power Applications. Energies. 2020; 13(17):4504. https://doi.org/10.3390/en13174504

Chicago/Turabian StyleF. Miaja, Pablo, Abraham Lopez, and Manuel Arias. 2020. "An Analog Magnetic Isolator for Space Power Applications" Energies 13, no. 17: 4504. https://doi.org/10.3390/en13174504

APA StyleF. Miaja, P., Lopez, A., & Arias, M. (2020). An Analog Magnetic Isolator for Space Power Applications. Energies, 13(17), 4504. https://doi.org/10.3390/en13174504