Simulation Test of a DC Fault Current Limiter for Fault Ride-Through Problem of Low-Voltage DC Distribution

Abstract

:1. Introduction

2. Fault of LVDC Distribution Network

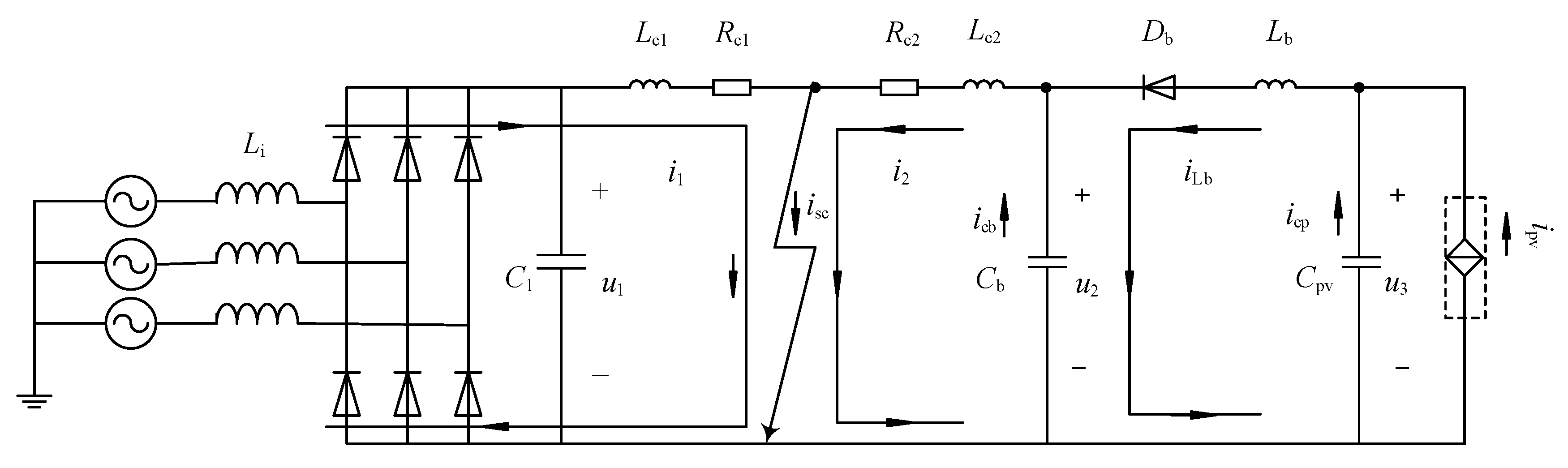

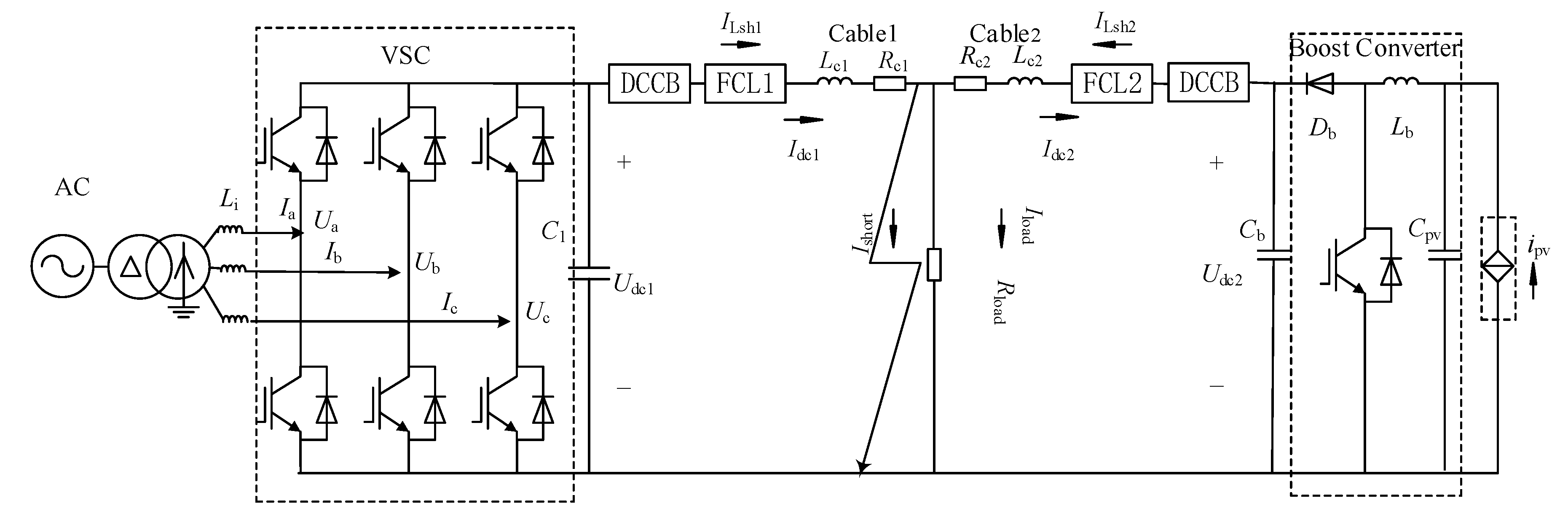

2.1. LVDC Distribution Network Structure and Fault Location

2.2. Fault Characteristics of LVDC Distribution Network with Photovoltaic Power System

- 1.

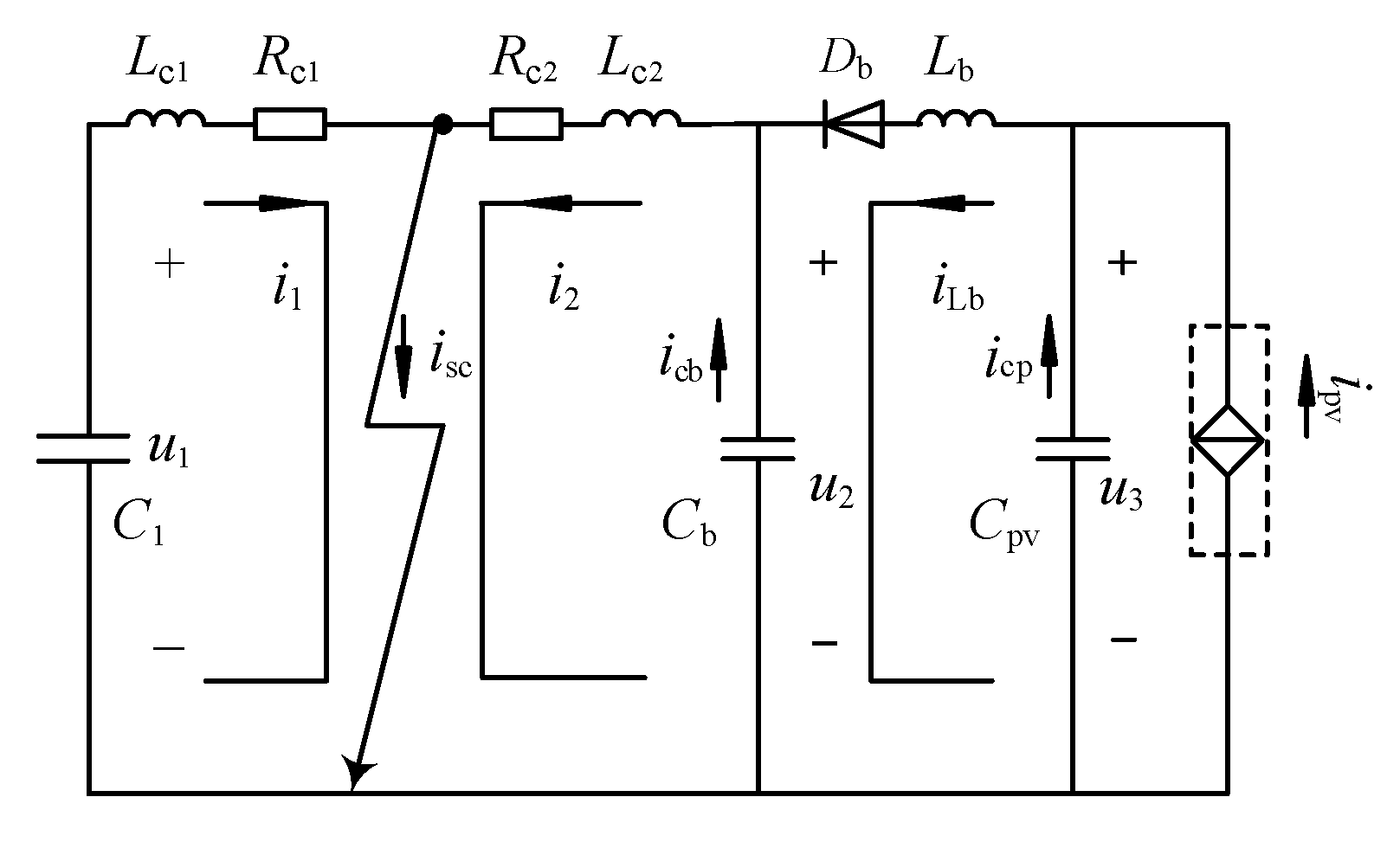

- The equivalent circuit of DC capacitance discharging stage is shown in Figure 3.

- ,

- ,

- ,

- .

- .

- 2.

- Free-conducting stage of diode: During the discharge process of C1, the electrical energy will change to electromagnetic energy and be stored in the DC side inductance. Its drive current of the reverse electromotive force flows through the VSC bridge commutating diodes of each phase. When the capacitor voltage C1 reaches zero, the equivalent circuit of the stage is demonstrated in Figure 4.

- 3.

- Steady state: When the inductance discharge on the DC side ends, the current on the grid side will flow through the diode into the DC side. The equivalent circuit of this state is shown in Figure 5.

2.3. Fault Analysis of LVDC Distribution Network with Photovoltaic Power System

- 1.

- Peak current and its arrival time

- 2.

- Continuity condition for three fault response

- 3.

- Countermeasures

3. Design of FCL

3.1. Structure of FCL

3.2. Parameter Design of FCL

- 1.

- Design of Lsh

- 2.

- Design of Rrse

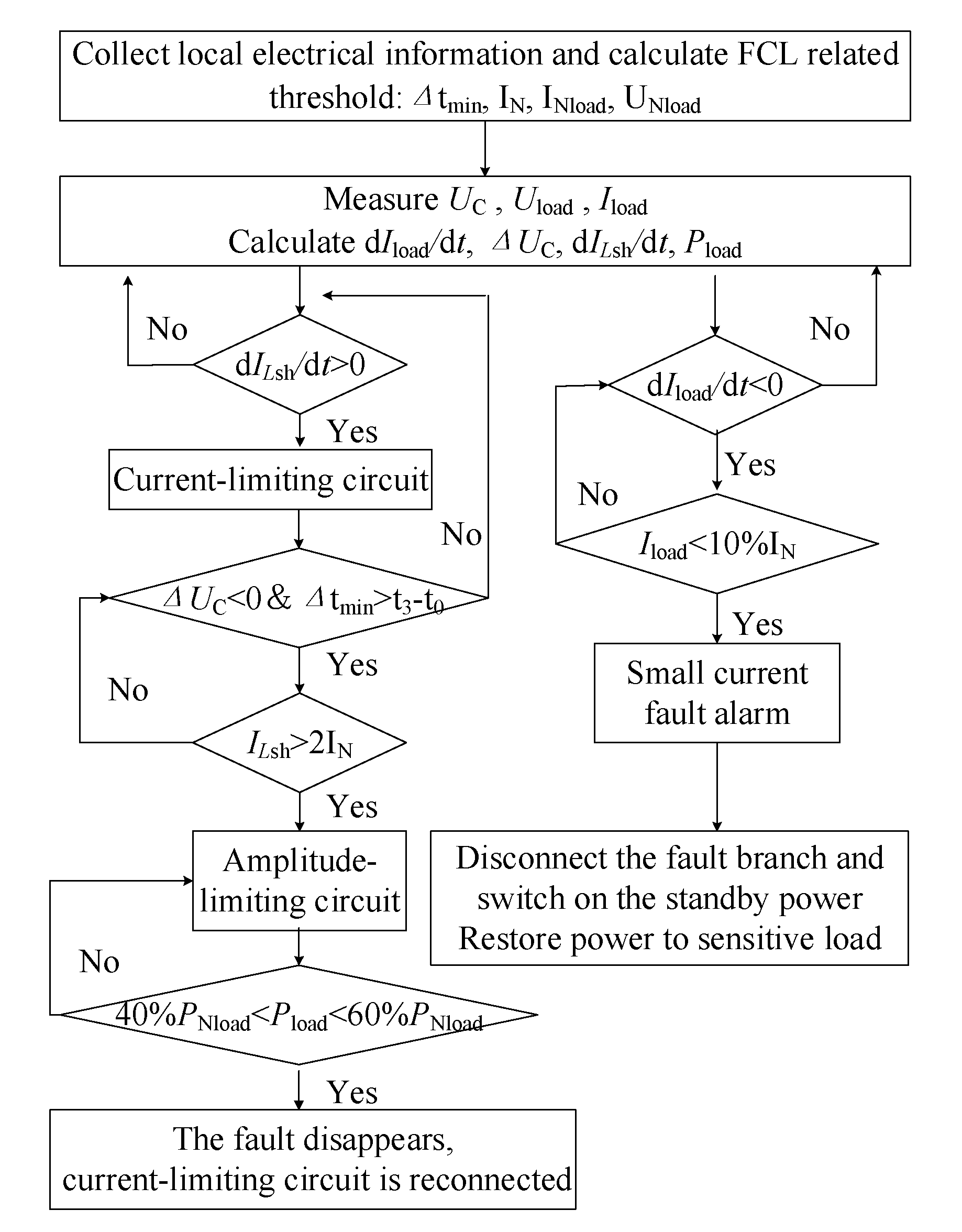

4. Fault Protection and Ride-Through Strategy Based on FCL

5. Simulation

5.1. Simulation Model

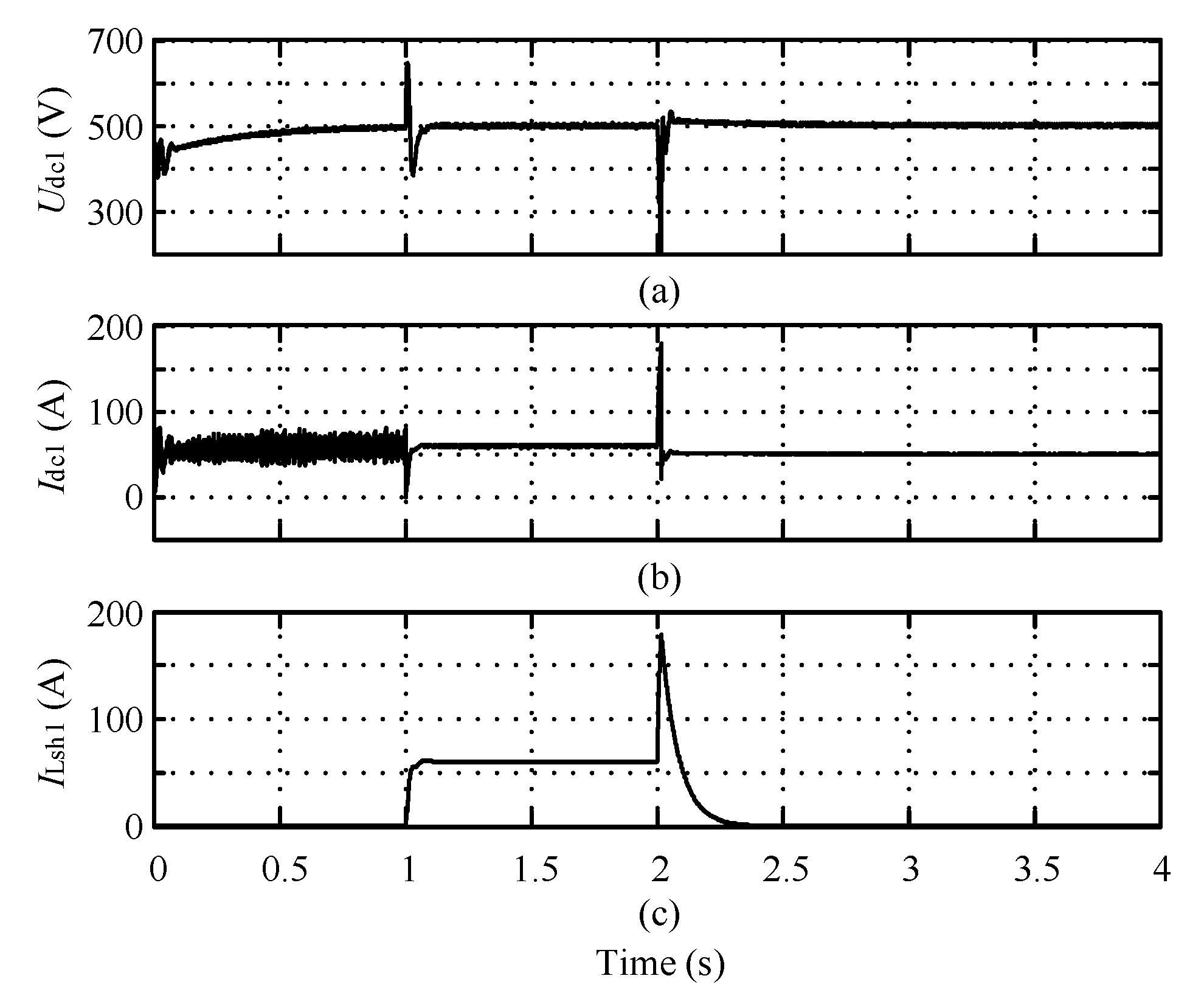

5.2. Bipolar Short Circuit Fault of Large Current Type

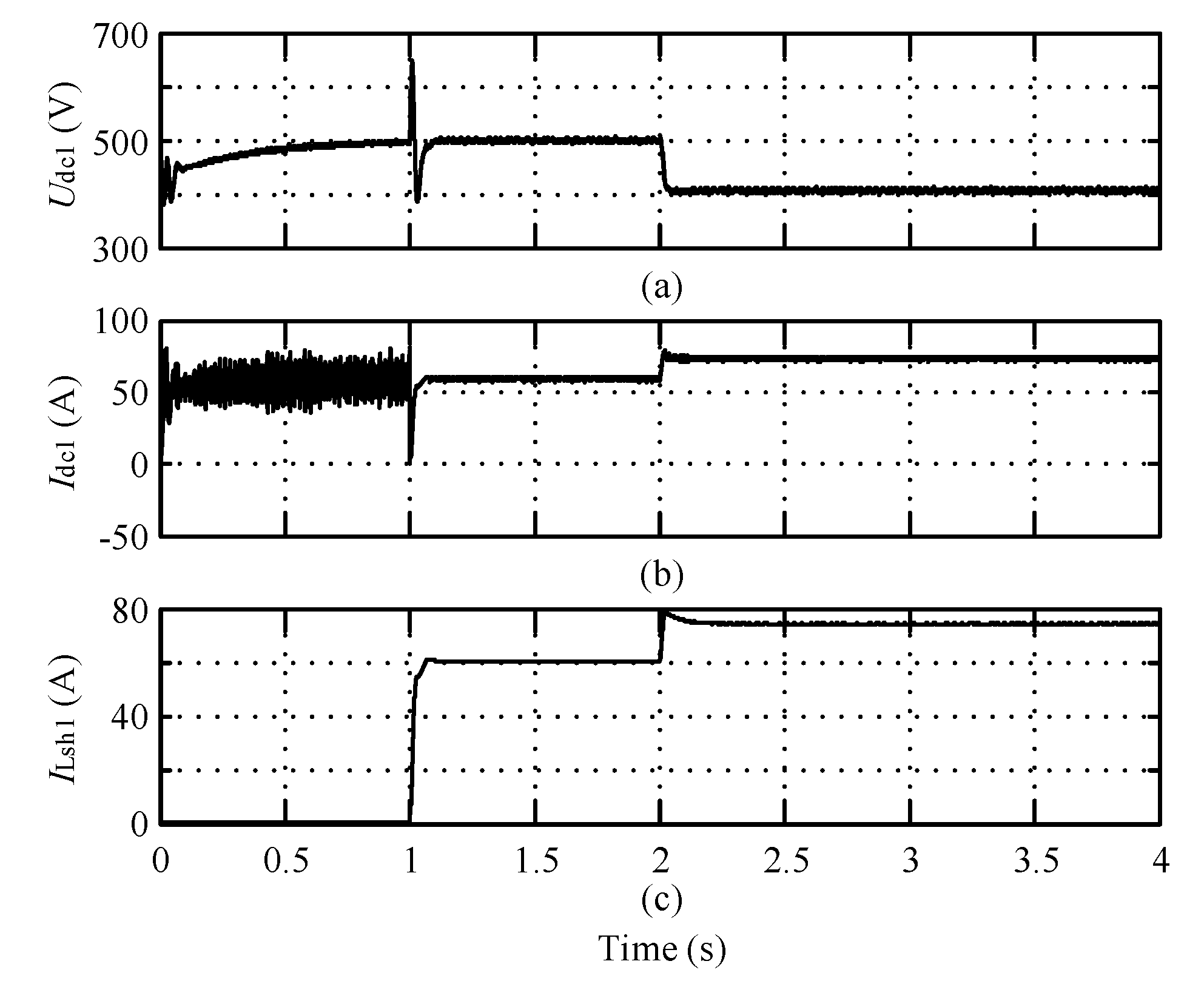

5.3. Bipolar Short Circuit Fault of Small Current Type

- 1.

- Simulation curve on VSC side

- 2.

- Simulation Curve on Boost Converter Side

6. Conclusions

- 1.

- The feasibility of the FCL connecting to the network was discussed in detail and the structure of the d FCL was given in detail; the principle of parameter design was discussed and presented.

- 2.

- To verify our proposed FCL, under the most serious conditions, a model was built and simulated. From the simulated results, we can see that FCL can reduce the fault current impact and limit fault current amplitude, which earns some time for fault detection, control, protection and ride-through action. After fault disappears, it will switch back to the current-limiting state and restore the normal operation. If the fault still exists, through cooperation with DCCB, the differential protection should be used as the backup protection of FCL. The identification of short-circuit fault of small current can be realized by monitoring the DC power at the load end.

Author Contributions

Funding

Conflicts of Interest

References

- Dragičević, T.; Lu, X.; Vasquez, J.C.; Guerrero, J.M. DC Microgrids—Part II: A Review of Power Architectures, Applications, and Standardization Issues. IEEE Trans. Power Electron. 2016, 31, 3528–3549. [Google Scholar]

- Justo, J.J.; Mwasilu, F.; Lee, J.; Jung, J.W. AC-microgrids versus DC microgrids with distributed energy resources: A review. Renew. Sustain. Energy Rev. 2013, 24, 387–405. [Google Scholar] [CrossRef]

- Chakraborty, C.; Iu, H.H.; Dah-Chuan Lu, D. Power converters, control, and energy management for distributed generation. IEEE Trans. Ind. Electron. 2015, 62, 4466–4470. [Google Scholar] [CrossRef]

- Dragičević, T.; Lu, X.; Vasquez, J.C.; Guerrero, J.M. DC Microgrids—Part I: A Review of Control Strategies and Stabilization Techniques. IEEE Trans. Power Electron. 2016, 31, 4876–4891. [Google Scholar]

- IEEE. IEEE Draft Standard for Interconnection and Interoperability of Distributed Energy Resources with Associated Electric Power Systems Interfaces; IEEE P1547/D7.3, December 2017; IEEE: Piscataway, NJ, USA, 2017; pp. 1–148. [Google Scholar]

- IEEE. IEEE Standard for Interconnection and Interoperability of Distributed Energy Resources with Associated Electric Power Systems Interfaces; IEEE Std 1547-2018.; IEEE: Piscataway, NJ, USA, 2018; pp. 1–138. [Google Scholar]

- Emhemed, A.A.S.; Burt, G.M. An Advanced Protection Scheme for Enabling an LVDC Last Mile Distribution Network. IEEE Trans. Smart Grid. 2014, 5, 2602–2609. [Google Scholar] [CrossRef] [Green Version]

- Chen, L.; Zhang, X.; Qin, Y.; Chen, H.; Shen, Q.; Xu, Y.; Ren, L.; Tang, Y. Application and Design of a Resistive-Type Superconducting Fault Current Limiter for Efficient Protection of a DC Microgrid. IEEE Trans. Appl. Superconduct. 2019, 29, 1–7. [Google Scholar] [CrossRef]

- Li, B.; He, J.; Li, Y.; Li, R. A Novel Solid-State Circuit Breaker with Self-Adapt Fault Current Limiting Capability for LVDC Distribution Network. IEEE Trans. Power Electron. 2019, 34, 3516–3529. [Google Scholar] [CrossRef]

- Rashid, G.; Ali, M.H. A Modified Bridge-Type Fault Current Limiter for Fault Ride-Through Capacity Enhancement of Fixed Speed Wind Generator. IEEE Trans. Energy Convers. 2014, 29, 527–534. [Google Scholar]

- Mahamedi, B.; Eskandari, M.; Fletcher, J.E.; Zhu, J. Sequence-Based Control Strategy with Current Limiting for the Fault Ride-Through of Inverter-Interfaced Distributed Generators. IEEE Trans. Sustain. Energy 2020, 11, 165–174. [Google Scholar] [CrossRef]

- Shabestary, M.M.; Mohamed, Y.A.I. Autonomous Coordinated Control Scheme for Cooperative Asymmetric Low-Voltage Ride-Through and Grid Support in Active Distribution Networks with Multiple DG Units. IEEE Trans. Smart Grid 2019. [Google Scholar] [CrossRef]

- Lin, L.; He, Z.; Hu, J.; He, Z.; Xu, K. Pole-to-ground fault ride through strategy for half-/full-bridge hybrid MMC-based radial multi-terminal HVDC systems with low-impedance grounded. IET Gener. Transm. Distrib. 2018, 12, 1038–1044. [Google Scholar] [CrossRef]

- Attya, A.B.; Comech, M.P.; Omar, I. Comprehensive study on fault-ride through and voltage support by wind power generation in AC and DC transmission systems. J. Eng. 2019, 2019, 5152–5157. [Google Scholar] [CrossRef]

- Vu, T.; Paran, S.; Diaz-Franco, F.; El-Mezyani, T.; Edrington, C.S. An Alternative Distributed Control Architecture for Improvement in the Transient Response of DC Microgrids. IEEE Trans. Ind. Electron. 2016, 64, 574–584. [Google Scholar] [CrossRef] [Green Version]

- Emhemed, A.; Fong, K.; Fletcher, S.; Burt, G.M. Validation of fast and selective protection scheme for an LVDC distribution network. IEEE Trans. Power Deliv. 2017, 32, 1432–1440. [Google Scholar] [CrossRef] [Green Version]

- Shuai, Z.; He, N.; Xiong, Z.; Lei, Z.; Shen, Z.J. Comparative Study of Short-Circuit Fault Characteristics for VSC-Based DC Distribution Networks with Different Distributed Generators. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 7, 528–540. [Google Scholar] [CrossRef]

- Monjo, L.; Mesas, J.J.; Sainz, L.; Pedra, J.; Monjo, L. Study of cable short circuit in VSC DC systems. In Proceedings of the 2015 International Symposium on Smart Electric Distribution Systems and Technologies (EDST), Vienna, Austria, 8–11 September 2015; Volume 33, pp. 230–234. [Google Scholar]

- Emhemed, A.; Burt, G.M. The effectiveness of using IEC61660 for characterising short-circuit currents of future low voltage DC distribution networks. In Proceedings of the 22nd International Conference and Exhibition on Electricity Distribution (CIRED 2013), Stockholm, Sweden, 10–13 June 2013; Volume 11, pp. 1–4. [Google Scholar]

- Yang, J.; Fletcher, J.E.; O’Reilly, J. Short-Circuit and Ground Fault Analyses and Location in VSC-Based DC Network Cables. IEEE Trans. Ind. Electron. 2011, 59, 3827–3837. [Google Scholar] [CrossRef] [Green Version]

- Nourmohamadi, H.; Nazari-Heris, M.; Sabahi, M.; Abapour, M. A Novel Structure for Bridge-Type Fault Current Limiter: Capacitor-Based Nonsuperconducting FCL. IEEE Trans. Power Electron. 2017, 33, 3044–3051. [Google Scholar] [CrossRef]

- Radmanesh, H.; Fathi, S.; Gharehpetian, G.B.; Heidary, A. Bridge-Type Solid-State Fault Current Limiter Based on AC/DC Reactor. IEEE Trans. Power Deliv. 2016, 31, 200–209. [Google Scholar] [CrossRef]

- Chen, S.; Li, P.; Ball, R.; De Palma, J.-F.; Lehman, B. Analysis of a Switched Impedance Transformer-Type Nonsuperconducting Fault Current Limiter. IEEE Trans. Power Electron. 2014, 30, 1925–1936. [Google Scholar] [CrossRef]

| Function | K1 | K2 | K3 | K4 |

|---|---|---|---|---|

| Start | 1 | 0 | 0 | 0 |

| Normal | 0 | 1 | 0 | 0 |

| Fault momentary | 0 | 1 | 0 | 0 |

| Initial failure | 0 | 1 | 0 | 0 |

| Failure period | 0 | 0 | 1 | 1 |

| Fault disappear | 0 | 1 | 0 | 0 |

| Parameter | Value |

|---|---|

| Rated DC voltage (V) | 500 |

| Rated DC current (A) | 60 |

| DC side busbar capacitance (F) | 0.002 |

| Load resistance (Ω) | 8.3 |

| DC line resistor (Ω⁄km) | 1 |

| DC line inductor (H⁄km) | 0.01 |

| Large current fault resistance (Ω) | 0.01 |

| Small current fault resistance (Ω) | 83 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Han, B.; Li, Y. Simulation Test of a DC Fault Current Limiter for Fault Ride-Through Problem of Low-Voltage DC Distribution. Energies 2020, 13, 1753. https://doi.org/10.3390/en13071753

Han B, Li Y. Simulation Test of a DC Fault Current Limiter for Fault Ride-Through Problem of Low-Voltage DC Distribution. Energies. 2020; 13(7):1753. https://doi.org/10.3390/en13071753

Chicago/Turabian StyleHan, Bing, and Yonggang Li. 2020. "Simulation Test of a DC Fault Current Limiter for Fault Ride-Through Problem of Low-Voltage DC Distribution" Energies 13, no. 7: 1753. https://doi.org/10.3390/en13071753